## 54S/74S258 54LS/74LS258

QUAD 2-INPUT MULTIPLEXER

(With 3-State Outputs)

**DESCRIPTION** — The '258 is a quad 2-input multiplexer with 3-state outputs. Four bits of data from two sources can be selected using a common data select input. The four outputs present the selected data in the complement (inverted) form. The outputs may be switched to a high impedance state with a HIGH on the common Output Enable (OE) Input, allowing the outputs to interface directly with bus oriented systems. It is fabricated with the Schottky barrier diode process for high speed.

- SCHOTTKY PROCESS FOR HIGH SPEED

- MULTIPLEXER EXPANSION BY TYING OUTPUTS TOGETHER

- INVERTING 3-STATE OUTPUTS

**ORDERING CODE:** See Section 9

| PKGS               | PIN | COMMERCIAL GRADE                                                                        | MILITARY GRADE                                                                                | PKG<br>TYPE |  |

|--------------------|-----|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|--|

|                    | оит | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to} + 70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to} + 125^{\circ}\text{ C}$ |             |  |

| Plastic<br>DIP (P) | А   | 74S258PC, 74LS258PC                                                                     |                                                                                               | 9B          |  |

| Ceramic<br>DIP (D) | A   | 74S258DC, 74LS258DC                                                                     | 54S258DM, 54LS258DM                                                                           | 6B          |  |

| Flatpak<br>(F)     | A   | 74S258FC, 74LS258FC                                                                     | 54S258FM, 54LS258FM                                                                           | 4L          |  |

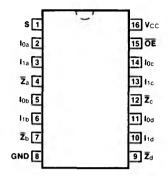

# CONNECTION DIAGRAM PINOUT A

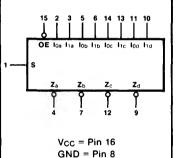

#### LOGIC SYMBOL

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. defintions

| PIN NAMES                                             | DESCRIPTION                              | <b>54/74S (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |

|-------------------------------------------------------|------------------------------------------|----------------------------------|----------------------------|

| S                                                     | Common Data Select Input                 | 2.5/2.5                          | 1.0/0.5                    |

| S_OE                                                  | 3-State Output Enable Input (Active LOW) | 1.25/1.25                        | 0.5/0.25                   |

| loa — lod                                             | Data Inputs from Source 0                | 1.25/1.25                        | 0.5/0.25                   |

|                                                       | Data Inputs from Source 1                | 1.25/1.25                        | 0.5/0.25                   |

| l <u>1a — I</u> 1d<br>Z <sub>a</sub> — Z <sub>d</sub> | Inverting Data Outputs                   | 162/12.5                         | 65/15                      |

|                                                       |                                          | (50)                             | (25)/(7.5)                 |

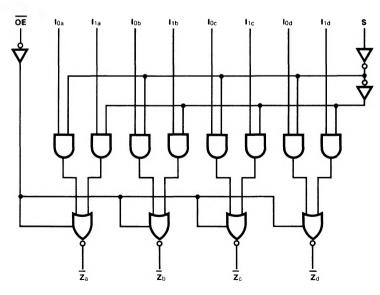

**FUNCTIONAL DESCRIPTION** — This device is a quad 2-input multiplexer with 3-state outputs. It selects four bits of data from two sources under control of a common Select input (S). When the Select input is LOW, the  $l_{0x}$  inputs are selected and when Select is HIGH, the  $l_{1x}$  inputs are selected. The data on the selected inputs appears at the outputs in inverted form. The '258 is the logic implementation of a 4-pole, 2-position switch where the position of the switch is determined by the logic levels supplied to the Select input. The logic equations for the outputs are shown below:

$$\begin{array}{lll} \overline{Z}_a = \overline{OE} \bullet (I_{1a} \bullet S + I_{0a} \bullet \overline{S}) & \overline{Z}_b = \overline{OE} \bullet (I_{1b} \bullet S + I_{0b} \bullet \overline{S}) \\ \overline{Z}_c = \overline{OE} \bullet (I_{1c} \bullet S + I_{0c} \bullet \overline{S}) & \overline{Z}_d = \overline{OE} \bullet (I_{1d} \bullet S + I_{0d} \bullet \overline{S}) \end{array}$$

When the Output Enable input (OE) is HIGH, the outputs are forced to a high impedance OFF state. If the outputs of the 3-state devices are tied together, all but one device must be in the high impedance state to avoid high currents that would exceed the maximum ratings. Designers should ensure that Output Enable signals to 3-state devices whose outputs are tied together are designed so there is no overlap.

TRUTH TABLE

| OUTPUT<br>ENABLE | SELECT<br>INPUT | DATA<br>INPUTS |    | OUTPUTS |

|------------------|-----------------|----------------|----|---------|

| ŌĒ               | S               | 10             | lı | Ī       |

| Н                | Х               | Х              | Х  | Z       |

| L                | н               | Х              | L  | н       |

| L                | н               | Х              | Н  | L       |

| L                | L               | L              | X  | н       |

| L                | L               | Н              | X  | L       |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

#### LOGIC DIAGRAM

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL  | PARAMETER Output Short Circuit Current |                                      | 54/74S |                | 54/74LS |                 | UNITS | CONDITIONS                                                                                                                                                                                                                                                                                 |

|---------|----------------------------------------|--------------------------------------|--------|----------------|---------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01.mb02 |                                        |                                      | Min    | Max            | Min     | Max             | Oilii | CONDITIONS                                                                                                                                                                                                                                                                                 |

| los     |                                        |                                      | -40    | -100           | -20     | -100            | mA    | V <sub>CC</sub> = Max                                                                                                                                                                                                                                                                      |

| lcc     | Power Supply<br>Current                | Outputs HIGH Outputs LOW Outputs OFF |        | 56<br>81<br>87 |         | 7.0<br>14<br>19 | mA    | $\begin{array}{c} V_{CC} = Max;  S,  I_{1x} = 4.5  V \\ \hline \overline{OE},  I_{0x} = Gnd \\ \hline V_{CC} = Max;  I_{1x} = 4.5  V \\ \hline \overline{OE},  I_{0x},  S = Gnd \\ \hline V_{CC} = Max;  S,  I_{0x} = Gnd \\ \hline \overline{OE} = I_{1x} = 4.5  V \\ \hline \end{array}$ |

### AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              | -                                           | 54/74S                                           | 54/74LS                | UNITS | CONDITIONS                                                                        |

|--------------|---------------------------------------------|--------------------------------------------------|------------------------|-------|-----------------------------------------------------------------------------------|

| SYMBOL       | PARAMETER                                   | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 280 Ω | C <sub>L</sub> = 15 pF |       |                                                                                   |

|              |                                             | Min Max                                          | Min Max                |       |                                                                                   |

| tpLH<br>tpHL | Propagation Delay $I_n$ to $\overline{Z}_n$ | 6.0<br>6.0                                       | 18<br>18               | ns    | Figs. 3-1, 3-4                                                                    |

| tPLH<br>tPHL | Propagation Delay<br>S to Zn                | 12<br>12                                         | 21<br>21               | ns    | Figs. 3-1, 3-4                                                                    |

| tpzh<br>tpzL | Output Enable Time                          | 19.5<br>21                                       | 30<br>30               | ns    | Figs. 3-3, 3-11, 3-12<br>$R_L = 2 \text{ k}\Omega \text{ ('LS258)}$               |

| tpHZ<br>tpLZ | Output Disable Time                         | 8.5<br>14                                        | 30<br>25               | ns    | Figs. 3-3, 3-11, 3-12<br>R <sub>L</sub> = 2 kΩ, C <sub>L</sub> = 5 pF<br>('LS258) |