# LINEAR INTEGRATED CIRCUITS

#### DESCRIPTION

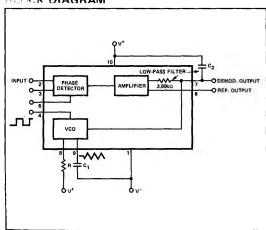

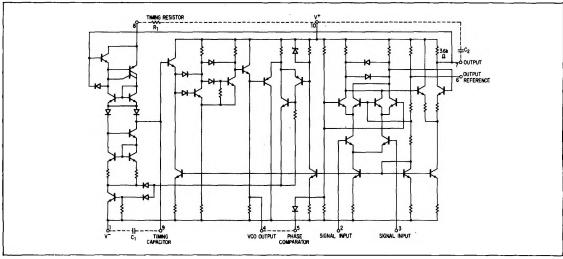

The SE/NE565 Phase-Locked Loop (PLL) is a selfcontained, adaptable filter and demodulator for the frequency range from 0.001 Hz to 500 kHz. The circuit comprises a voltage-controlled oscillator of exceptional stability and linearity, a phase comparator, an amplifier and a low-pass filter as shown in the block diagram. The center frequency of the PLL is determined by the free-running frequency of the VCO; this frequency can be adjusted externally with a resistor or a capacitor. The low-pass filter, which determines the capture characteristics of the loop, is formed by an internal resistor and an external capacitor.

#### PEATURES

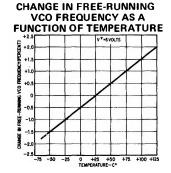

- EXTREME STABILITY OF CENTER FREQUENCY (200ppm/°C typ)

- WIDE RANGE OF OPERATING VOLTAGE (±5 to ±12 VOLTS) WITH VERY SMALL FREQUENCY DRIFT (100ppm/% typ)

- VERY HIGH LINEARITY OF DEMODULATED OUTPUT (0.2% typ)

- CENTER FREQUENCY PROGRAMMING BY MEANS OF A RESISTOR, CAPACITOR, VOLTAGE OR CUR-RENT

- TTL AND DTL COMPATIBLE SQUARE-WAVE OUT-PUT; LOOP CAN BE OPENED TO INSERT DIGITAL **FREQUENCY DIVIDER**

- HIGHLY LINEAR TRIANGLE WAVE OUTPUT

- REFERENCE OUTPUT FOR CONNECTION OF COMPARATOR IN FREQUENCY DISCRIMINATOR

- BANDPASS, ADJUSTABLE FROM <±1% to >±60%

- FREQUENCY ADJUSTABLE OVER 10 TO 1 RANGE WITH SAME CAPACITOR

#### HUNCK DIAGRAM

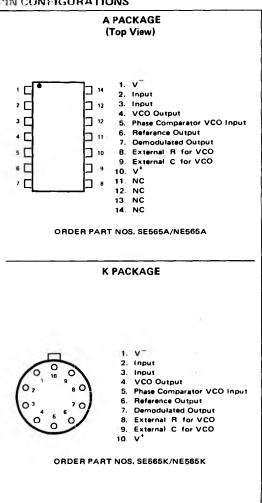

# TIN CONFIGURATIONS

**APPLICATIONS FREQUENCY SHIFT KEYING** MODEMS **TELEMETRY RECEIVERS** TONE DECODERS **SCA RECEIVERS** WIDEBAND FM DISCRIMINATORS **DATA SYNCHRONIZERS** TRACKING FILTERS SIGNAL RESTORATION FREQUENCY MULTIPLICATION & DIVISION

# ABSOLUTE MAXIMUM RATINGS (limiting values above which serviceability may be impaired)

Maximum Operating Voltage

26V

Storage Temperature Power Dissipation

-65°C to 150°C 300mW

ECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = ±6 Volts unless otherwise noted)

| PARAMETER                                                                                 | TEST CONDITIONS                                                                                                          |             | SE565                  |                          |            | NE565                  |             |                              |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|--------------------------|------------|------------------------|-------------|------------------------------|

|                                                                                           |                                                                                                                          | MIN         | TYP                    | MAX                      | MIN        | TYP                    | MAX         | UNITS                        |

| SUPPLY REQUIREMENTS Supply Voltage Supply Current                                         |                                                                                                                          | ±5          | 8                      | ±12<br>12.5              | ±5         | 8                      | ±12<br>12.5 | V<br>mA                      |

| INPUT CHARACTERISTICS Input Impedance Input Level Required                                | $4V \le V_2, V_3 \le +1V$<br>$f_0 = 50 \text{ kHz}$                                                                      | 7           | 10                     |                          | 5          | 10                     |             | kΩ                           |

| for Tracking                                                                              | ±10% frequency deviation                                                                                                 | 10          | 1                      |                          | 10         | 1                      |             | mVrms                        |

| VCO CHARACTERISTICS Center Frequency Maximum Value Distribution                           | $C_1 = 2.7 \text{ pF}$ Distribution taken about $f_0 \approx 50 \text{ kHz}$                                             | 300         | 500                    | +10                      | -30        | 500                    | +30         | kHz<br>%                     |

| Drift with Temperature<br>Drift with Supply Voltage                                       | $R_1 = 5.0k$ , $C_1 = 1200 pF$<br>$R_1 = 50 kHz$<br>$R_1 = 50 kHz$<br>$R_2 = 50 kHz$<br>$R_3 = 50 kHz$<br>$R_4 = 50 kHz$ | +75         | +100                   | +525                     | -30        | +200                   | 1.5         | %<br>ppm/°C<br>%/V           |

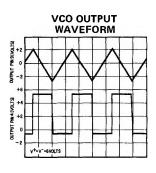

| Triangle Wave<br>Output Voltage Level<br>Amplitude<br>Linearity                           |                                                                                                                          | 2           | 0<br>2.4<br>0.2        | 3                        | 2          | 0<br>2.4<br>0.5        | 3           | ∨<br>Vp-p<br>%               |

| Square Wave Logical "1" Output Voltage Logical "0" Output                                 | f <sub>0</sub> = 50 kHz<br>V <sub>CC</sub> = ±6 Volts<br>f <sub>0</sub> = 50 kHz                                         | +4.9        | +5.2                   |                          | +4.9       | +5.2                   |             | v                            |

| Voltage Duty Cycle Rise Time Fall Time Output Current (sink)                              | V <sub>CC</sub> = ±6 Volts<br>f <sub>0</sub> = 50 kHz                                                                    | 0.6         | -0.2<br>50<br>20<br>50 | +0.2<br>55<br>100<br>200 | 40<br>0.6  | -0.2<br>50<br>20<br>50 | +0.2<br>60  | V<br>%<br>nsec<br>nsec<br>mA |

| Output Current (source)  DEMODULATED OUTPUT CHARACTERISTICS                               |                                                                                                                          | 5           | 10                     |                          | 5          | 10                     |             | mA                           |

| Output Voltage Level Maximum Voltage Swing Output Voltage Swing Total Harmonic Distortion | (pin 7) V <sub>CC</sub> = ±6 Volts<br>(pin 7)<br>±10% frequency deviation                                                | 4.25<br>250 | 4.5<br>2<br>300<br>0.2 | 0.75                     | 4.0<br>200 | 4.5<br>2<br>300<br>0.2 | 1.5         | V<br>Vp-p<br>mVp⊣<br>%       |

| Output Impedance Offset Voltage  V <sub>6</sub> -V <sub>7</sub>   vs Temperature (drift)  | T <sub>A</sub> = 25°C                                                                                                    | 30          | 3.6<br>30<br>50        | 100                      |            | 3.6<br>50<br>100       | 200         | kΩ<br>mV<br>μV/°C<br>dB      |

| Offset Voltage V6-V7                                                                      | T <sub>A</sub> = 25°C                                                                                                    | 30          | 30                     | 100                      |            | 50                     | 200         |                              |

## NOTES:

- 1. Both input terminals (pins 2 and 3) must receive identical dc bias. This bias may range from 0 volts to -4 volts.

- 2. The external resistance for frequency adjustment (R1) must have a value between  $2k\Omega$  and  $20k\Omega$ .

- 3. Output voltage swings negative as input frequency increases.

- 4. Output not buffered.

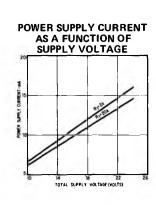

### TYPICAL PERFORMANCE CHARACTERISTICS

FREE-RUNNING VCO FREQ. AS A FUNCTION OF VOLTAGE BETWEEN PIN 7 & 10 (VCO CONVERSION GAIN)

AS A FUNCTION OF GAIN SETTING RESISTANCE (PIN 6-7)

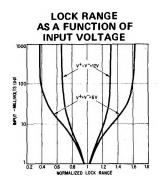

**LOCK RANGE**

### **CHEMATIC DIAGRAM**

#### **DESIGN FORMULAS**

Free-running frequency of VCO  $f_0 = \frac{1.2}{4R_1C_1}$  in Hz

Lock-range

$$f_L = \pm \frac{8f_0}{V_{CC}}$$

in Hz

Capture-range

$$f_C \simeq \pm \frac{1}{2\pi} \sqrt{\frac{2\pi f_L}{\tau}}$$

where  $\tau = (3.6 \times 10^3) \times C_2$

# DEFINITION OF TERMS FREE-RUNNING FREQUENCY (fo)

Frequency of VCO without input signal, both inputs grounded.

#### CAPTURE-RANGE

That range of frequencies about fo over which the loop will acquire lock with an input signal initially starting out of lock.

#### LOCK-RANGE OR TRACKING-RANGE

That range of frequencies in the vicinity of  $f_{\rm O}$  over which the VCO, once locked to the input signal, will remain locked.

# TYPICAL APPLICATIONS

#### **FM DEMODULATION**

The 565 Phase Locked Loop is a general purpose circuit designed for highly-linear FM demodulation. During lock, the average dc level of the phase comparator output signal is directly proportional to the frequency of the input signal. As the input frequency shifts, it is this output signal which causes the VCO to shift its frequency to match that of the input. Consequently, the linearity of the phase comparator output with frequency is determined by the voltage-to-frequency transfer function of the VCO.

Because of its unique and highly linear VCO, the 565 PLL can lock to and track an input signal over a very wide range (typically  $\pm 60\%$ ) with very high linearity (typically, within 0.5%).

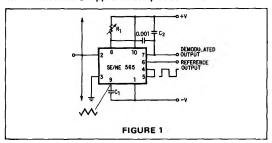

A typical connection diagram is shown in Figure 1. The VCO free-running frequency is given approximately by  $f_0 = \frac{1.2}{4R_1C_1}$  and should be adjusted to be at the center

of the input signal frequency range. C<sub>1</sub> can be any value, but R<sub>1</sub> should be within the range of 2000 to 20,000 ohms with an optimum value on the order of 4000 ohms. The source can be direct coupled if the dc resistances seen from pins 2 and 3 are equal and there is no dc voltage difference between the pins. A short between pins 4 and 5 connects the VCO to the phase comparator. Pin 6 provides a dc reference voltage that is close to the dc potential of the demodulated output (pin 7). Thus, if a resistance (R<sub>2</sub> in Figure 1) is connected between pins 6 and 7, the gain of the output stage can be reduced with little change in the dc voltage level at the output. This allows the lock range to be decreased with little change in the free-running frequency. In this manner the lock range can be decreased from ±60% of f<sub>0</sub> to approximately ±20% of f<sub>0</sub> (at ±6V).

A small capacitor (typically 0.001  $\mu$ F) should be connected between pins 7 and 8 to eliminate possible oscillation in the control current source.

A single-pole loop filter is formed by the capacitor C<sub>2</sub>, connected between pin 7 and positive supply, and an internal resistance of approximately 3600 ohms.

#### FREQUENCY SHIFT KEYING (FSK)

FSK refers to data transmission by means of carrier which is shifted between two preset frequencies. This frequency shift is usually accomplished by driving a VCO with the binary data signal so that the two resulting frequencies correspond to the "0" and "1" states (commonly called space and mark) of the binary data signal.

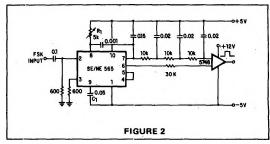

A simple scheme using the 565 to receive FSK signals of 1070 Hz and 1270 Hz is shown in Figure 2. As the signal appears at the input, the loop locks to the input frequency and tracks it between the two frequencies with a corresponding dc shift at the output.

The loop filter capacitor C<sub>2</sub> is chosen smaller than usual to eliminate overshoot on the output pulse, and a three-stage RC ladder filter is used to remove the carrier component from the output. The band edge of the ladder filter is chosen to be approximately half way between the maximum keying rate (in this case 300 baud or 150 Hz) and twice the input frequency (approximately 2200 Hz). The output signal can now be made logic compatible by connecting a voltage comparator between the output and pin 6 of the loop. The free-running frequency is adjusted with R<sub>1</sub> so as to result in a slightly-positive voltage at the output at fin = 1070 Hz.

The input connection is typical for cases where a dc voltage is present at the source and therefore a direct connection is not desirable. Both input terminals are returned to ground with identical resistors (in this case, the values are chosen to effect a 600-ohm input impedance).

#### FREQUENCY MULTIPLICATION

There are two methods by which frequency multiplication can be achieved using the 565:

- 1. Locking to a harmonic of the input signal.

- Inclusion of a digital frequency divider or counter in the loop between the VCO and phase comparator.

The first method is the simplest, and can be achieved by setting the free-running frequency of the VCO to a multiple of the input frequency. A limitation of this scheme is that the lock range decreases as successively higher and weaker harmonics are used for locking. If the input frequency is to be constant with little tracking required, the loop can generally be locked to any one of the first 5 harmonics. For higher orders of multiplication, or for cases where a large lock range is desired, the second scheme is more desirable. An example of this might be a case where the input signal varies over a wide frequency range and a large multiple of the input frequency is required.

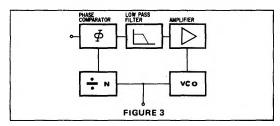

A block diagram of the second scheme is shown in Figure 3. Here the loop is broken between the VCO and the phase comparator, and a frequency divider is inserted. The funda-

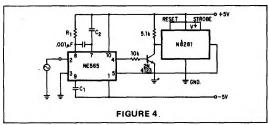

mental of the divided VCO frequency is locked to the input frequency in this case, so that the VCO is actually running at a multiple of the input frequency. The amount of multiplication is determined by the frequency divider. A typical connection scheme is shown in Figure 4. To set up the circuit, the frequency limits of the input signal must be determined. The free-running frequency of the VCO is then adjusted by means of R<sub>1</sub> and C<sub>1</sub> (as discussed under FM demodulation) so that the output frequency of the divider is midway between the input frequency limits. The filter capacitor, C2, should be large enough to eliminate variations in the demodulated output voltage (at pin 7), in order to stabilize the VCO frequency. The output can now be taken as the VCO squarewave output, and its fundamental will be the desired multiple of the input frequency (f<sub>1</sub>) as long as the loop is in lock.

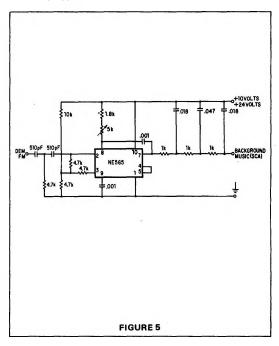

#### SCA (BACKGROUND MUSIC) DECODER

Some FM stations are authorized by the FCC to broadcast uninterrupted background music for commercial use. To do this a frequency modulated subcarrier of 67 kHz is used. The frequency is chosen so as not to interfere with the normal stereo or monaural program; in addition, the level of the subcarrier is only 10% of the amplitude of the combined signal.

The SCA signal can be filtered out and demodulated with the NE565 Phase Locked Loop without the use of any resonant circuits. A connection diagram is shown in Figure 5. This circuit also serves as an example of operation from a single power supply.

A resistive voltage divider is used to establish a bias voltage for the input (pins 2 and 3). The demodulated (multiplex) FM signal is fed to the input through a two-stage high-pass filter, both to effect capacitive coupling and to attenuate the strong signal of the regular channel. A total signal amplitude, between 80 mV and 300 mV, is required at the input. Its source should have an impedance of less than 10,000 ohms.

The Phase Locked Loop is tuned to 67 kHz with a 5000 ohm potentiometer; only approximate tuning is required, since the loop will seek the signal.

The demodulated output (pin 7) passes through a threestage low-pass filter to provide de-emphasis and attenuate the high-frequency noise which often accompanies SCA transmission. Note that no capacitor is provided directly at pin 7; thus, the circuit is operating as a first-order loop. The demodulated output signal is in the order of 50 mV and the frequency response extends to 7 kHz.