#### CONNECTION DIAGRAMS PINOUT A 9000 • 9001 9020 • 9022 JK FLIP-FLOPS ('00. '01) DUAL JK FLIP-FLOPS ('20, '22) JK 1 14 Vcc 13 C̄<sub>□</sub> S̄<sub>D</sub> 2 12 J<sub>3</sub> 11 K<sub>3</sub> J<sub>2</sub> 5 10 K<sub>2</sub> 9 CP Q 6 8 Q GND 7 **ORDERING CODE:** See Section 9 **COMMERCIAL GRADE MILITARY GRADE** PIN PKG **PKGS** $V_{CC} = +5.0 \text{ V } \pm 5\%$ $V_{CC} = +5.0 \text{ V} \pm 10\%$ OUT **TYPE** $J = A \cdot B \cdot C \cdot D$ $T_A = -55^{\circ} C \text{ to } +125^{\circ} C$ $T_A = 0$ °C to +75°C $K = A \cdot B \cdot C \cdot D$ 9000DC 9000DM Α 6A 9001DC 9001DM Ceramic В DIP (D) C 9020DC 9020DM 6B 9022DC 9022DM D 9000FC 9000FM Α 31 В 9001FC 9001FM Flatpak (F) C 9020FC 9020FM 4L 9022FC 9022FM D PINOUT B PINOUT C PINOUT D 16 Vcc 16 Vcc C<sub>D</sub> 1 CD 1 JK 1 14 Vcc 15 **C**<sub>D</sub> 15 CD CP 2 CP 2 13 CD S<sub>D</sub> 2 14 JK 14 JK J 3 J 3 12 J<sub>3</sub> K<sub>1</sub> 3 13 J **K** 4 13 J K<sub>2</sub> 4 J1 4 11 K<sub>3</sub> 12 K<sub>2</sub> S<sub>D</sub> 5 12 K K<sub>1</sub> 5 **J**<sub>2</sub> 5 10 K<sub>2</sub> 11 K<sub>1</sub> 11 SD Q 6 Q 6 Q 6 9 CP Q 7 10 Q Q 7 10 Q 8 Q GND 7 9 ā 9 Q GND 8 GND 8 $J = A \bullet \overline{B} \bullet C \bullet D$ $K = A \cdot B \cdot \overline{C} \cdot D$

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                     | DESCRIPTION        | <b>9000 (U.L.)</b><br>HIGH/LOW | <b>9001 (U.L.)</b><br>HIGH/LOW | 9020 (U.L.)<br>HIGH/LOW | <b>9022 (U.L.)</b><br>HIGH/LOW |

|-------------------------------|--------------------|--------------------------------|--------------------------------|-------------------------|--------------------------------|

| JK                            | JK Input           | 3.0/2.0                        | 3.0/2.0                        | 6.0/4.0                 | 6.0/4.0                        |

| $J_n$ , $K_n$ , $J_n$ , $R_n$ | Data Inputs        | 1.5/1.0                        | 1.5/1.0                        | 1.5/1.0                 | 1.5/1.0                        |

|                               | Clock Pulse Input  | 1.5/1.0                        | 1.5/1.0                        | 3.0/2.0                 | 3.0/2.0                        |

| CP<br>CD                      | Direct Clear Input | 4.0/2.7                        | 4.0/2.7                        | 4.0/2.7                 | 4.0/2.7                        |

| $\overline{S}_D$              | Direct Set Input   | 4.0/2.7                        | 4.0/2.7                        |                         | 4.0/2.7                        |

| Q, Ci                         | Outputs            | 30/8.8                         | 30/8.8                         | 30/8.8                  | 30/8.8                         |

|                               |                    | (7.8)                          | (7.8)                          | (7.8)                   | (7.8)                          |

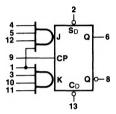

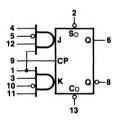

### LOGIC SYMBOLS

V<sub>CC</sub> = Pin 14 GND = Pin 7

# 9001

V<sub>CC</sub> = Pin 14 GND = Pin 7

### ASYNCHRONOUS OPERATION

| INP    | UTS    | OUTPUTS |                           |  |  |  |

|--------|--------|---------|---------------------------|--|--|--|

| SD     | CD     | a       | ā                         |  |  |  |

| L      | Н      | нн      | H                         |  |  |  |

| H<br>H | L<br>H |         | H<br>HRONOUS<br>S CONTROL |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

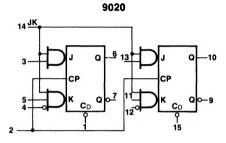

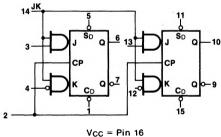

V<sub>CC</sub> = Pin 16 GND = Pin 8

### 9022

$V_{CC} = Pin 16$ GND = Pin 8

### **SYNCHRONOUS OPERATION**

| ВІ | EFORE C | AFTER | CLOCK |     |      |

|----|---------|-------|-------|-----|------|

| ΟÚ | TPUTS   | IN    | PUTS  | OUT | PUTS |

| Q  | ī       | J     | Κ     | Q   | a    |

| L  | H       | L,    | Х     | L   | Н    |

| L  | Н       | H*    | X     | Н   | L    |

| Н  | L       | Х     | L*    | н   | L    |

| Н  | L       | Х     | H*    | L   | Н    |

L\* = Input does not go HIGH at any time while the clock is

H\* = Input is HIGH at some time while the clock is LOW.

X = Immaterial

**FUNCTIONAL DESCRIPTION** — The TTL 9000 series has four flip-flops to satisfy the storage requirements of a logic system. All are master/slave JK designs and have the same high speed and high noise immunity as the rest of the 9000 series. As with the gates, all inputs have diode clamps to reduce ringing caused by long lines and impedance mismatches.

The JK type flip-flop was chosen for all flip-flop elements in this family because of its inherent logic power. The input function required to produce a given sequence of states for a JK flip-flop will, in general, contain more "don't care" conditions than the corresponding function for an RS flip-flop. These additional "don't care" conditions will, in most cases, reduce the amount of gating elements required to implement the input function.

The master/slave design offers the advantage of a dc threshold on the clock input initiating the transition of the outputs, so that careful control of clock pulse rise and fall times is not required.

Data is accepted by the master while the clock is in the LOW state. Refer to the truth tables for definition of HIGH and LOW data. Transfer from the master to the slave occurs on the LOW-to-HIGH transition of the clock. When the clock is HIGH, the J and K inputs are inhibited.

A joint (JK) input is provided for all flip-flops in this family. The common input removes the necessity of gating the clock signal with an external gate in many applications. This not only reduces package count, but also reduces the possibility of clock skew problems, since with internal gating provided, all flip-flops may be driven from a common clock line. Several TTL drivers may be used in parallel to drive this common clock line if the load exceeds the fan-out capability of the 9009 buffer.

The asynchronous inputs provide ability to control the state of the flip-flop independent of static conditions of the clock and synchronous inputs. Both asynchronous set and clear are provided on all flip-flops except the 9020, which because of a logic trade-off has only clear inputs. The set or clear pin being LOW absolutely guarantees that one output will be HIGH, but if opposing data is present at the synchronous inputs and the flip-flop is clocked, the LOW output may momentarily spike HIGH synchronous with a positive transition of the clock. If the LOW output of the flip-flop is connected to other flip-flop inputs clocked from the same line, the spike will be masked by the clock. If the clock is suspended during the time when the asynchronous inputs are activated, no spike will occur. When the spikes can cause problems, a simple solution is to common the joint JK inputs with the synchronous set or reset signal.

Synchronous Operation — The truth table defines the next state of the flip-flop after a LOW-to-HIGH transition of the clock pulse. The next state is a function of the present state and the J and K inputs as shown in the table. The J and K inputs in the table refer to the basic flip-flop J and K inputs as indicated on the logic symbols. These internal inputs are for every flip-flop the result of a logic operation on the external J and K inputs. This operation is represented symbolically by AND gates in the logic symbol for each flip-flop. Logic symbols are in accordance with MIL Standard 806B.

The L' symbol in the J and K input column is defined as meaning that input does not go HIGH at any time while the clock is LOW.

The H\* symbol in the J or K input column is defined as meaning that the input is HIGH at some time while the clock is LOW.

The X symbol indicates that the condition of that input has no effect on the next state of the flip-flop.

The H and L symbols refer to steady state HIGH and LOW voltage levels, respectively.

Unused Inputs — The 9001, 9020 and 9022 all have active level LOW synchronous inputs. When not in use they must be grounded. All other unused inputs, including asynchronous, should be tied HIGH for maximum operating speed.

| IDC AND AC CHARACTERISTICS OVER COMMERCIAL TEMPERATURE RANGE: $V_{\rm CC}$ = $+5.0$ V $\pm 5\%$ | DC AND | AC CHARACTERISTICS | OVER COMMERCIAL | <b>TEMPERATURE RANGE: V</b> | $cc = \pm 5.0 \text{ V } \pm 5\%$ |

|-------------------------------------------------------------------------------------------------|--------|--------------------|-----------------|-----------------------------|-----------------------------------|

|-------------------------------------------------------------------------------------------------|--------|--------------------|-----------------|-----------------------------|-----------------------------------|

| SYMBOL | PARAMETER                                                                                                                                     | 0   | 0°C                              |     | 25°C                             |     | °C                               | UNITS | CONDITIONS                                                                                                     |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|----------------------------------|-----|----------------------------------|-------|----------------------------------------------------------------------------------------------------------------|--|

|        | TANAMETER.                                                                                                                                    | Min | Max                              | Min | Max                              | Min | Max                              | 0.0.0 | CONDITIONS                                                                                                     |  |

| Viн    | Input HIGH Voltage                                                                                                                            | 1.9 |                                  | 1.8 |                                  | 1.6 |                                  | >     | Guaranteed<br>Input HIGH<br>Threshold                                                                          |  |

| ViL    | Input LOW Voltage                                                                                                                             |     | 0.85                             |     | 0.85                             |     | 0.85                             | >     | Guaranteed<br>Input LOW<br>Threshold                                                                           |  |

| VoL    | Output LOW Voltage                                                                                                                            |     | 0.45                             |     | 0.45                             |     | 0.45                             | ٧     | V <sub>CC</sub> = 4.75 V,<br>I <sub>OL</sub> = 14.1 mA<br>V <sub>CC</sub> = 5.25 V,<br>I <sub>OL</sub> = 16 mA |  |

| 1      | Input LOW Current All J, K Inputs CP Inputs 9000, 9001 JK Inputs 9000, 9001 CP Inputs 9020, 9022 JK inputs 9020, 9022 SD, CD (all Flip-flops) |     | -1.60<br>-3.20<br>-6.40<br>-4.32 |     | -1.60<br>-3.20<br>-6.40<br>-4.32 |     | -1.60<br>-3.20<br>-6.40<br>-4.32 | mA    | V <sub>CC</sub> = 5.25 V<br>V <sub>IN</sub> = 0.45 V<br>5.25 V on<br>Other Inputs                              |  |

| lıL    | Input LOW Current All J, K Inputs CP Inputs 9000, 9001 JK Inputs 9000, 9001 CP Inputs 9020, 9022 JK Inputs 9020, 9022 SD, CD (all Flip-flops) |     | -1.41<br>-2.82<br>-5.64<br>-3.78 |     | -1.41<br>-2.82<br>-5.64<br>-3.78 |     | -1.41<br>-2.82<br>-5.64<br>-3.78 | mA    | $V_{CC} = 4.75 \text{ V}$ $V_{IN} = 0.45 \text{ V}$ 5.25 V on Other Inputs                                     |  |

| lcc    | Power Supply Current<br>9000<br>9001<br>9020, 9022 each Flip-flop                                                                             |     | 28<br>33<br>30                   | **  | 28<br>33<br>30                   |     | 28<br>33<br>30                   | mA    | S <sub>D</sub> at Gnd<br>S <sub>D</sub> at Gnd<br>C <sub>D1</sub> , C <sub>D2</sub> at Gn                      |  |

### DC AND AC CHARACTERISTICS OVER MILITARY TEMPERATURE RANGE: $V_{CC} = +5.0 \text{ V} \pm 10\%$

| SYMBOL | PARAMETER          | -5  | -55°C |     | 25°C |     | 5°C | UNITS | CONDITIONS                                                                                                   |

|--------|--------------------|-----|-------|-----|------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------|

|        |                    | Min | Max   | Min | Max  | Min | Max | 00    | 301121113113                                                                                                 |

| ViH    | Input HIGH Voltage | 2.0 |       | 1.7 |      | 1.4 |     | ٧     | Guaranteed<br>Input HIGH<br>Threshold                                                                        |

| VIL    | Input LOW Voltage  |     | 0.8   |     | 0.9  |     | 0.8 | ٧     | Guaranteed<br>Input LOW<br>Threshold                                                                         |

| VoL    | Output LOW Voltage |     | 0.4   |     | 0.4  |     | 0.4 | V     | V <sub>CC</sub> = 4.5 V,<br>I <sub>OL</sub> = 12.4 mA<br>V <sub>CC</sub> = 5.5 V,<br>I <sub>OL</sub> = 16 mA |

| DO AND AC CHA | DACTEDISTICS OVED | MILITARY TEMPERATUR | DE PANGE: (Contid) |

|---------------|-------------------|---------------------|--------------------|

| SYMBOL      | PARAMETER                                                                                                                                     | -5  | -55°C                            |     | °C                               | 12  | 5°C                              | UNITS    | CONDITIONS                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|----------------------------------|-----|----------------------------------|----------|----------------------------------------------------------------------------------------------|

|             | TAILAINE LEIT                                                                                                                                 | Min | Max                              | Min | Max                              | Min | Max                              | 014      | 001100                                                                                       |

| <b>I</b> IL | Input LOW Current All J, K Inputs CP Inputs 9000, 9001 JK Inputs 9000, 9001 CP Inputs 9020, 9022 JK Inputs 9020, 9022 SD, CD (all Flip-flops) |     | -1.60<br>-3.20<br>-6.40<br>-4.32 |     | -1.60<br>-3.20<br>-6.40<br>-4.32 |     | -1.60<br>-3.20<br>-6.40<br>-4.32 | <u> </u> | Vcc = 5.5 V<br>V <sub>IN</sub> = 4.5 V<br>5.5 V on<br>Other Inputs                           |

| "L          | Input LOW Current All J, K Inputs CP Inputs 9000, 9001 JK Inputs 9000, 9001 CP Inputs 9020, 9022 JK Inputs 9020, 9022 SD, CD (all Flip-flops) |     | -1.24<br>-2.48<br>-4.96<br>-3.35 |     | -1.24<br>-2.48<br>-4.96<br>-3.75 |     | -1.24<br>-2.48<br>-4.96<br>-3.35 | mA       | V <sub>CC</sub> = 4.5 V<br>V <sub>IN</sub> = 0.4 V<br>5.5 V on<br>Other Inputs               |

| lcc         | Power Supply Current<br>9000<br>9001<br>9020, 9022 each Flip-flop                                                                             |     | 24<br>28<br>27                   |     | 24<br>28<br>27                   |     | 24<br>28<br>27                   | mA       | S <sub>D</sub> at Gnd<br>S <sub>D</sub> at Gnd<br>C <sub>D1</sub> , C <sub>D2</sub> , at Gno |

### **SWITCHING CHARACTERISTICS** ( $T_A = 25^{\circ}$ C, $V_{CC} = 5.0$ V, $C_L = C_1 = 15$ pF of all flip-flops unless otherwise noted)

| SYMBOL                           | PARAMETER                             |        |                  |                           |           | IITS       | UNITS    | CONDITIONS                  |  |

|----------------------------------|---------------------------------------|--------|------------------|---------------------------|-----------|------------|----------|-----------------------------|--|

| 51.II.50E                        |                                       |        |                  |                           |           | Max        | 00       |                             |  |

| tPLH                             | Clock to Outpu                        |        |                  |                           |           | 20<br>20   | ns       | Fine a b                    |  |

| tphL                             | Clock to Output<br>Sp or Cp to Output |        |                  |                           |           | 30<br>35   | ns       | Figs. a, b, c               |  |

|                                  | J, K or JK                            |        | 9000XM<br>9000XC |                           | 30<br>35  |            | ns       | Figs. a, c                  |  |

| tsetup                           | T. 20                                 | 9001XC |                  | KM, 9022XM<br>XC, 9022XC  | 10<br>15  |            | ns       | Figs. a, b, c               |  |

|                                  | J or K Data Entry                     |        |                  |                           | 17        |            |          | Fire                        |  |

| trelease                         | J, K or JK J or K Data En             | try    | 9001             | 9000 only<br>, 9020, 9022 |           | 1.0<br>4.0 | ns<br>ns | Figs. a, c<br>Figs. a, b, c |  |

| Pulse                            |                                       | 9000   | ) only           | Positive<br>Negative      |           | 0*<br>5*   | ns       | Figs. a, c                  |  |

| Widths                           | Clock                                 | 9001,  | 9020,<br>9022    | Negative                  | ] 1       | 0 <b>.</b> | ns       | Figs. a, b, c               |  |

| S <sub>D</sub> or C <sub>D</sub> |                                       |        |                  | Negative                  | <b></b> - | 5*         |          | .,                          |  |

|                                  | Toggle Freque                         | 201    |                  | 9000 only<br>9001, 9020,  | 2         | 0.         | MHz      | Figs. a, c                  |  |

|                                  | Toggle Freque                         |        |                  | 9022                      | 5         | 0*         | MHz      | Figs. a, b, c               |  |

<sup>\*</sup>Typical Value

#### SWITCHING TEST NOTES

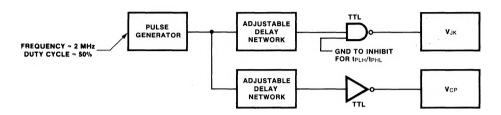

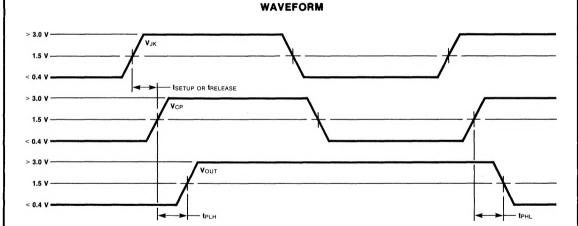

### tplh and tphl

- 1. V.ik should be kept at the HIGH level when performing tplh/tphl test.

- 2. Drive the clock pulse input with a suitable pulse source, tplH and tpHL delays are as defined in the waveforms.

### RECOMMENDED INPUT PULSE SOURCES

DTL9932 gates with adjustable capacitors connected from extender inputs to ground make suitable delay elements.

#### tsetup

- 1. t<sub>setup</sub> is defined as the minimum time required for a HIGH to be present at a synchronous logic input at any time during the LOW state of the clock in order for the flip-flop to respond to the data.

- 2. The test for t<sub>setup</sub> is performed by adjusting the timing relationship between the V<sub>CP</sub> and V<sub>JK</sub> inputs to the t<sub>setup</sub> minimum value. A device that passes the test will have the output waveform shown. The output of a device that does not pass the t<sub>setup</sub> test will remain at a static logic level (no switching will occur).

### trelease

- 1. trelease is defined as the maximum time allowed for a HIGH to be present at a synchronous logic input at any time during the LOW state of the clock and not be recognized.

- 2. The test for trelease is performed by adjusting the timing relationship between V<sub>CP</sub> and V<sub>JK</sub> to the trelease maximum value. The outputs of devices that pass will remain at static logic levels. In order to check both J and K sides of the flip-flop it is necessary to perform the test with the flip-flop in each of its two possible states, i.e., set and clear. This can be accomplished by making use of the appropriate direct inputs to establish the state before a test. The outputs of devices that do not pass the trelease test will exhibit pulses instead of static levels.

#

$V_{CC}$  = Pin 5.0 V R = 2.0 k $\Omega$  C<sub>I</sub> = C<sub>L</sub> = 15 pF including probe and jig capacitance

Fig. c