## 9322 93L22

## **QUAD 2-INPUT MULTIPLEXER**

**DESCRIPTION** — The '22 quad 2-input digital multiplexers consist of four multiplexing circuits with common select and enable logic; each circuit contains two inputs and one output.

- MULTIFUNCTION CAPABILITY

- ON-CHIP SELECT LOGIC DECODING

- FULLY BUFFERED OUTPUTS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | L GRADE MILITARY GRADE                                                                     |             |  |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|--|--|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V, } \pm 10\%,$ $T_A = -55^{\circ}\text{C to } +125^{\circ}\text{C}$ | PKG<br>TYPE |  |  |  |

| Plastic<br>DIP (P) | A   | 9322PC, 93L22PC                                                                          |                                                                                            | 9B          |  |  |  |

| Ceramic<br>DIP (D) | A   | 9322DC, 93L22DC                                                                          | 9322DM, 93L22DM                                                                            | 6B          |  |  |  |

| Flatpak<br>(F)     | Α   | 9322FC, 93L22FC                                                                          | 9322FM, 93L22FM                                                                            | 4L          |  |  |  |

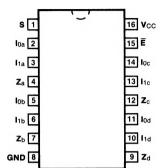

# CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                          | DESCRIPTION                                      | 93XX (U.L.)<br>HIGH/LOW | 93L (U.L.)<br>HIGH/LOW |

|----------------------------------------------------|--------------------------------------------------|-------------------------|------------------------|

| S<br>E                                             | Common Select Input<br>Enable Input (Active LOW) | 1.0/1.0<br>1.0/1.0      | 0.5/0.25<br>0.5/0.25   |

| loa — lod }<br>l <sub>1a</sub> — l <sub>1d</sub> } | Multiplexer Inputs                               | 1.0/1.0                 | 0.5/0.25               |

| $Z_a - Z_d$                                        | Multiplexer Outputs                              | 20/10                   | 10/5.0<br>(3.0)        |

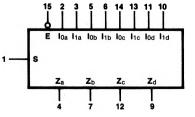

#### **LOGIC SYMBOL**

V<sub>CC</sub> = Pin 16 GND = Pin 8 **FUNCTIONAL DESCRIPTION** — The '22 quad 2-input multiplexer provides the ability to select four bits of either data or control from two sources, in one package. The Enable input (E) is active LOW. When not activated all outputs  $(Z_n)$  are LOW regardless of all other inputs.

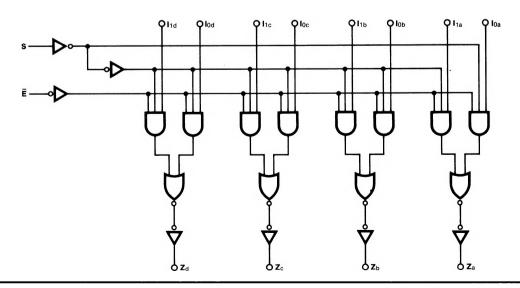

The '22 quad 2-input multiplexer is the logical implementation of a four-pole, two position switch, with the position of the switch being set by the logic levels supplied to the one select input. The logic equations for the outputs are shown below:

$$\begin{split} Z_a &= E \bullet (I_{1a} \bullet S + I_{0a} \bullet \overline{S}) \\ Z_c &= E \bullet (I_{1c} \bullet S + I_{0c} \bullet \overline{S}) \end{split} \qquad \begin{aligned} Z_b &= E \bullet (I_{1b} \bullet S + I_{0b} \bullet \overline{S}) \\ Z_d &= E \bullet (I_{1d} \bullet S + I_{0d} \bullet \overline{S}) \end{aligned}$$

A common use of the '22 is the moving of data from a group of registers to four common output busses. The particular register from which the data comes is determined by the state of the select input. A less obvious use is as a function generator. The '22 can generate four functions of two variables with one variable common. This is useful for implementing random gating functions.

TRUTH TABLE

|   | INF | PUTS | OUTPUT |    |

|---|-----|------|--------|----|

| Ē | S   | lon  | Iın    | Zn |

| Н | Х   | Х    | Х      | L  |

| L | Н   | Х    | L      | L  |

| L | н   | Х    | Н      | н  |

| L | L   | L    | Χ      | L  |

| L | L   | Н    | Х      | н  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

#### LOGIC DIAGRAM

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL    | PARAMETER                    |     | 93XX |     | 3L   | UNITS | CONDITIONS                                    |

|-----------|------------------------------|-----|------|-----|------|-------|-----------------------------------------------|

| 0.1111502 | Anameren                     | Min | Max  | Min | Мах  | OMITO | 001121110110                                  |

| los       | Output Short Circuit Current | -20 | -70  |     |      | mA    | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0 V |

| lcc       | Power Supply Current         |     | 47   |     | 13.2 | mA    | V <sub>CC</sub> = Max                         |

## AG CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                                                         | 93XX                                | 93L                    | UNITS | CONDITIONS      |

|--------------|-------------------------------------------------------------------------|-------------------------------------|------------------------|-------|-----------------|

| SYMBOL       | PARAMETER                                                               | $C_L = 15 pF$<br>$R_L = 400 \Omega$ | C <sub>L</sub> = 15 pF |       |                 |

|              |                                                                         | Min Max                             | Min Max                |       |                 |

| tpLH<br>tpHL | Propagation Delay<br>S to Z <sub>n</sub>                                | 23<br>27                            | 36<br>49               | ns    | Figs. 3-1, 3-20 |

| tpLH<br>tpHL | Propagation Delay<br>I <sub>0</sub> or I <sub>1</sub> to Z <sub>n</sub> | 14<br>14                            | 22<br>30               | ns    | Figs. 3-1, 3-5  |

| tpLH<br>tpHL | Propagation Delay<br>E to Z <sub>n</sub>                                | 20<br>21                            | 27<br>27               | ns    | Figs. 3-1, 3-4  |