## 9348

## 12-INPUT PARITY CHECKER/GENERATOR

**DESCRIPTION** — The '48 is a 12-input parity checker/generator generating odd and even parity outputs. It can be used in high speed error detection applications.

- BOTH ODD AND EVEN PARITY OUTPUTS PROVIDED

- GENERATES A PARITY BIT FOR UP TO 12 BITS

- CHECKS FOR PARITY ON UP TO 12 BITS

- EASILY EXPANDABLE

**ORDERING CODE:** See Section 9

| PKGS               | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                 | PKG<br>TYPE |  |

|--------------------|-----|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------|--|

|                    | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} +125^{\circ} \text{ C}$ |             |  |

| Plastic<br>DIP (P) | A   | 9348PC                                                                                   |                                                                                                | 9B          |  |

| Ceramic<br>DIP (D) | А   | 9348DC                                                                                   | 9348DM                                                                                         | 6B          |  |

| Flatpak<br>(F)     | A   | 9348FC                                                                                   | 9348FM                                                                                         | 4L          |  |

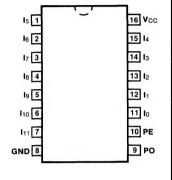

# CONNECTION DIAGRAM PINOUT A

### INPUT LOADING/FAN-OUT

| PIN NAMES          | DESCRIPTION        | <b>93XX (U.L.)</b><br>HIGH/LOW |  |

|--------------------|--------------------|--------------------------------|--|

| lo l <sub>11</sub> | Parity Inputs      | 2.0/2.0                        |  |

| PO                 | Odd Parity Output  | 20/10                          |  |

| PE                 | Even Parity Output | 20/10                          |  |

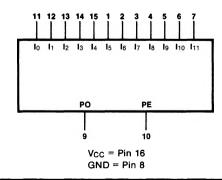

#### LOGIC SYMBOL

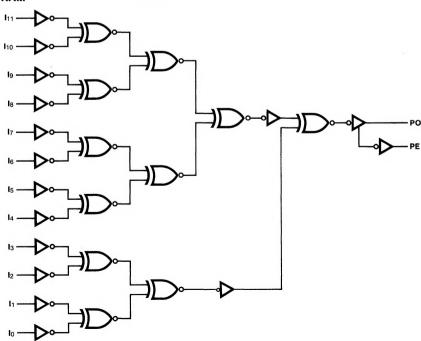

**FUNCTIONAL DESCRIPTION** — The '48 is a 12-input parity generator. It provides odd and even parity for up to 12 data bits. The Even Parity output (PE) will be HIGH if an even number of logic ones are present on the inputs. The Odd Parity output (PO) will be HIGH if an odd number of logic ones are present on the inputs. The logic equations for the outputs are shown below.

$$\mathsf{PO} = \mathsf{I_0} \, \oplus \, \mathsf{I_1} \, \oplus \, \mathsf{I_2} \, \oplus \, \mathsf{I_3} \, \oplus \, \mathsf{I_4} \, \oplus \, \mathsf{I_5} \, \oplus \, \mathsf{I_6} \, \oplus \, \mathsf{I_7} \, \oplus \, \mathsf{I_8} \, \oplus \, \mathsf{I_9} \, \oplus \, \mathsf{I_{10}} \, \oplus \, \mathsf{I_{11}}$$

$$PE = I_0 \oplus I_1 \oplus I_2 \oplus I_3 \oplus I_4 \oplus I_5 \oplus I_6 \oplus I_7 \oplus I_8 \oplus I_9 \oplus I_{10} \oplus I_{11}$$

NOTE: Less through delay is encounted from the 10, 11, 12, and 13 inputs than 14 thru 111 inputs. Therefore, if some signals are slower than others, the slower signals should be applied to these four inputs for maximum speed.

**TRUTH TABLE**

| IN         | OUTPUTS     |    |   |

|------------|-------------|----|---|

| lo         | РО          | PE |   |

| All Twelve | Inputs LOW  | L  | Н |

| Any One    | Input HIGH  | н  | L |

| Any Two    | Inputs HIGH | L  | Н |

| Any Three  | Inputs HIGH | н  | L |

| Any Four   | Inputs HIGH | L  | н |

| Any Five   | Inputs HIGH | н  | L |

| Any Six    | Inputs HIGH | L  | Н |

| Any Seven  | Inputs HIGH | Н  | L |

| Any Eight  | Inputs HIGH | L  | Н |

| Any Nine   | Inputs HIGH | Н  | L |

| Any Ten    | Inputs HIGH | L  | н |

| Any Eleven | Inputs HIGH | н  | L |

| Any Twelve | Inputs HIGH | L  | Н |

H = HIGH Voltage Level L = LOW Voltage Level

#### LOGIC DIAGRAM

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 93XX |     | UNITS | CONDITIONS            |

|--------|----------------------|------|-----|-------|-----------------------|

|        |                      | Min  | Max | 00    |                       |

| Icc    | Power Supply Current |      | 82  | mA    | V <sub>CC</sub> = Max |

## AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25°C (See Section 3 for waveforms and load configuration)

|              |                               | 9:                                              | 93XX     |       | CONDITIONS                                                                                                                             |

|--------------|-------------------------------|-------------------------------------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL       | PARAMETER                     | AMETER $C_L = 15 \text{ pF}$ $R_L = 400 \Omega$ |          | UNITS |                                                                                                                                        |

|              |                               | Min                                             | Max      |       |                                                                                                                                        |

| tplH<br>tpHL | Propagation Delay             |                                                 | 46<br>42 | ns    | l <sub>2</sub> , l <sub>3</sub> , l <sub>7</sub> , l <sub>8</sub> = Gnd; Other<br>Inputs (exc. l <sub>4</sub> ) HIGH<br>Figs. 3-1, 3-4 |

| tpLH<br>tpHL | Propagation Delay             |                                                 | 51<br>48 | ns    | l <sub>2</sub> , l <sub>3</sub> , l <sub>7</sub> , l <sub>8</sub> = Gnd; Other<br>Inputs (exc. l <sub>4</sub> ) HIGH<br>Figs. 3-1, 3-5 |

| tpLH         | Propagation Delay             |                                                 | 27       | ns    | I <sub>7</sub> = HIGH; Other Inputs<br>(exc. I <sub>3</sub> ) = Gnd<br>Figs. 3-1, 3-4                                                  |

| tphL         | Propagation Delay<br>I4 to PO |                                                 | 25       | ns    | All Inputs (exc. I <sub>4</sub> ) = Gnd<br>Figs. 3-1, 3-5                                                                              |