# High Accuracy, 18-Bit **Digital-to-Analog Converter**

**FEATURES** 18-Bit Resolution **Low Nonlinearity**

Differential: ± 1/2LSB max Integral: ±1/2LSB max

**High Stability**

Differential TC: ±1ppm/°C max Integral TC: ±1/2ppm/°C max

Gain TC (with Reference): ±4ppm/°C max

**Fast Settling**

Full Scale:  $40\mu s$  to  $\pm 0.00019\%$ LSB:  $6\mu s$  to  $\pm 0.00019\%$

Small Hermetic 32-Lead Triple DIP Package

**Low Cost**

**APPLICATIONS Automatic Test Equipment Scientific Instrumentation Beam Positioners Digital Audio**

## **GENERAL DESCRIPTION**

The AD1139 is the first DAC offering 18-bit resolution (1 part in 262,144) and true 18-bit accuracy in a component size hybrid package. A proprietary bit switching technique provides high accuracy, speed and stability without compromising small size

The AD1139 is a complete DAC with precision internal reference, latched data inputs and a quality output voltage amplifier. The analog output voltage ranges are pin programmable to +5V, +10V,  $\pm 5V$  and  $\pm 10V$ . Current output is also provided for use with external amplifiers. The internal precision - 10V reference has a low ±3ppm/°C maximum temperature coefficient and is available for ratiometric applications.

The AD1139K is a true 18-bit accurate DAC with  $\pm 1/2$ LSB maximum differential and integral nonlinearity. The differential and integral nonlinearity temperature stability is guaranteed at  $\pm 1$ ppm/°C maximum and  $\pm 1/2$ ppm/°C maximum, respectively.

The AD1139 settles to within  $\pm 1/2$ LSB at 18 bits ( $\pm 0.00019\%$ ) in 40µs for a full-scale step (10V). The glitch energy is a low 400mV × 500ns for a major carry, and wideband output noise is only 15µV.

The AD1139 operates from  $\pm$  15V dc and  $\pm$  5V dc power supplies. Digital inputs are 5V CMOS compatible with binary input coding for unipolar output ranges and offset binary coding for bipolar ranges.

#### **PRODUCT HIGHLIGHTS**

- 1. Eighteen-bit resolution with  $\pm 1/2$ LSB maximum differential and integral nonlinearity in a hermetic 32-lead triple DIP

- 2. Complete DAC with internal reference, stable low-noise output amplifier, latched DAC inputs, reference output and internal application resistors for programmable output voltage

- 3. Temperature compensated internal precision reference with  $\pm 0.1\%$  maximum initial accuracy and  $\pm 3$ ppm/°C maximum

- 4. Four pin programmable output voltage ranges (+5V, +10V, $\pm$  5V,  $\pm$  10V) and current output available (-1mA,  $\pm 0.5$ mA).

- 5. The 18-bit parallel input latch assists in microprocessor

- 6. Accurate measurements of the DAC's output are unusually simple since the AD1139 does not suffer from code dependent ground current errors.

- 7. True analog output remote sense capability.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way; P. O. Box 9106; Norwood, MA 02062-9106 Tel: 617/329-4700 **West Coast**

714/641-9391

Central 214/231-5094 TWX: 710/394-6577 Atlantic 215/643-7790

# SPECIFICATIONS (typical @ +25°C and rated supplies unless otherwise specified)

| Model                                                             | AD1139J                        | AD1139K                                                     |

|-------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------|

| RESOLUTION                                                        | 18 Bits                        | *                                                           |

| ACCURACY                                                          |                                |                                                             |

| Differential Nonlinearity                                         | ± 1LSB max                     | ± 1/2LSB max                                                |

| Incomed Montinearity                                              | (= ±0.00038% max)<br>±1LSB max | $(= \pm 0.00019\% \text{ max})$<br>$\pm 1/2 \text{LSB max}$ |

| Integral Nonlinearity                                             | $(= \pm 0.00038\%max)$         | $\pm 1/2$ LSB max $(= \pm 0.00019\% \text{ max})$           |

| Monotonicity (18 Bits)                                            | Guaranteed                     | *                                                           |

| Initial Errors <sup>1</sup>                                       |                                |                                                             |

| Unipolar Gain Error                                               | ±0.01%<br>±0.02%               | l <b>:</b>                                                  |

| Bipolar Gain Error<br>Offset Error                                | ± 0.02%<br>± 0.01%             | *                                                           |

| Bipolar Offset Error                                              | ±0.01%                         | *                                                           |

| STABILITY (ppm FSR <sup>2</sup> /°C)                              |                                |                                                             |

| Differential Nonlinearity <sup>3</sup>                            | ±1 max                         | $\pm 0.5$ typ, $\pm 1$ max                                  |

| Integral Nonlinearity <sup>3</sup>                                | ±0.5 max                       | *                                                           |

| Gain (Including V <sub>REF</sub> ) Offset                         | ±4 max                         | l <b>"</b>                                                  |

| Unipolar Mode                                                     | ±1 max                         | *                                                           |

| Bipolar Mode                                                      | ± 1 max                        | *                                                           |

| STABILITY (Long Term, ppm FSR <sup>2</sup> /1000 hour)            |                                |                                                             |

| Differential Nonlinearity <sup>4</sup>                            | ±0.5                           | *                                                           |

| Gain (Including V <sub>REF</sub> )                                | ±15                            | *                                                           |

| Offset<br>Bisseles Offset                                         | ±1                             | 1:                                                          |

| Bipolar Offset<br>Reference Output Voltage                        | ±2<br>±15                      | *                                                           |

| WARMUPTIME (MINIMUM)                                              | 15 minutes                     | *                                                           |

|                                                                   | 13 minutes                     |                                                             |

| REFERENCE VOLTAGE (V <sub>REF</sub> ) Output Voltage (@ 5 mA max) | ~ 10V ( ± 0.1% max)            |                                                             |

| Noise (BW = 0.1-10Hz)                                             | 20μV pk-pk                     | 10μV pk-pk                                                  |

| Noise $(BW = 100kHz)$                                             | 50μV rms                       | * ' ' '                                                     |

| Тетрсо                                                            | 3ppm/°C max                    | *                                                           |

| DYNAMIC PERFORMANCE                                               |                                |                                                             |

| Settling Time to 1/2LSB (@ 18 Bits) <sup>5</sup>                  |                                |                                                             |

| Voltage                                                           | 40µs                           |                                                             |

| Unipolar (10V Step)<br>Bipolar (20V Step)                         | 60μs                           |                                                             |

| Unipolar (LSB Step)                                               | биз                            |                                                             |

| Bipolar (LSB Step)                                                | 8µs                            | <b>*</b>                                                    |

| Slew Rate                                                         | 2V/μs                          | *                                                           |

| Current <sup>6</sup> Full-Scale Step                              | 10μs                           | *                                                           |

| LSB Step                                                          | 6µs                            | *                                                           |

| Glitch Energy (Major Carry                                        |                                |                                                             |

| (a) 20MHz Bandwidth 0-to-10V Range)                               | 400mV (500ns Duration)         | *                                                           |

| DIGITAL INPUTS (5V CMOS Compatible)                               |                                |                                                             |

| V <sub>IL</sub>                                                   | ≤0.8V<br>≥3.5V                 | 🖫                                                           |

| V <sub>IH</sub><br>Unipolar Code                                  | Binary (BIN)                   | *                                                           |

| Bipolar Code                                                      | Offset Binary (OBN)            | *                                                           |

| ANALOGOUTPUT                                                      |                                |                                                             |

| Current <sup>4</sup>                                              | $-1mA$ , $\pm 0.5mA$           | *                                                           |

| Voltage (Pin Programmable)                                        | $+5V, +10V, \pm 5V, \pm 10V$   | *                                                           |

| Noise (Includes $V_{REF}$ )<br>$BW = 0.1-10Hz(\mu V pk-pk)$       | 2×FSR                          | 1×FSR                                                       |

| BW = 100kHz (Unipolar)                                            | 15µV rms                       | *                                                           |

| BW = 100kHz(Bipolar)                                              | 45µV rms                       | *                                                           |

| VOLTAGECOMPLIANCE                                                 | ± 10mV                         | *                                                           |

| Source Resistance                                                 | 1                              |                                                             |

| Unipolar                                                          | 3.3kΩ                          | 1:                                                          |

| Bipolar<br>Source Capacitance                                     | 2.85kΩ<br>10pF                 | l ÷                                                         |

| POWER SUPPLY REQUIREMENTS                                         | Topi                           |                                                             |

| +5Vdc(±5%)                                                        | 100μΑ                          |                                                             |

| ± 15V dc (±5%)                                                    | + 25mA, - 30mA                 | *                                                           |

| POWER SUPPLY REJECTION                                            |                                |                                                             |

| $(\pm 15 \text{V dc})$                                            |                                |                                                             |

| Gain                                                              | ± 2.5ppm/%                     | 1:                                                          |

| Offset Reference Output                                           | ± 0.3ppm/%<br>± 2.5ppm/%       | ·                                                           |

| (+5V dc)                                                          | _ 2.5ppm //                    |                                                             |

| Differential Nonlinearity                                         | ±0.15ppm/%                     | *                                                           |

| TEMPERATURE RANGE                                                 |                                |                                                             |

|                                                                   | 0 to + 70℃                     | *                                                           |

| Operating (Rated Performance)                                     |                                | 1                                                           |

| Operating (Rated Performance) Storage                             | -40°C to +85°C                 |                                                             |

| Operating (Rated Performance)                                     |                                | \$450                                                       |

# DOT INDICATES PIN 1, POSITION 1.707 (43.41) 1.743 (44.27) 0.095 (2.41) 0.105 (2.67)

1.079 (27.41) 1.101 (27.97)

0.192 (4.88) 0.158 (4.01)

**OUTLINE DIMENSIONS** Dimensions shown in inches and (mm).

CAUTION: OBSERVE PROPER PLUG-IN POLARITY TO PREVENT DAMAGE TO CONVERTER

# **PIN DESIGNATIONS**

| PIN | DESCRIPTION           | PIN | DESCRIPTION |

|-----|-----------------------|-----|-------------|

| 1   | SIGNAL GND            | 32  | GAIN TRIM   |

| 2   | <b>BIPOLAR OFFSET</b> | 31  | REFOUT      |

| 3   | lout                  | 30  | – 15V       |

| 4   | AMPIN                 | 29  | + 15V       |

| 5   | 20V SPAN              | 28  | +5V         |

| 6   | 10V SPAN              | 27  | POWER GND   |

| 7   | AMP OUT               | 26  | WR          |

| 8   | DB17 (MSB)            | 25  | DB0 (LSB)   |

| 9   | DB16                  | 24  | DB1         |

| 10  | DB15                  | 23  | DB2         |

| 11  | DB14                  | 22  | DB3         |

| 12  | DB13                  | 21  | DB4         |

| 13  | DB12                  | 20  | DB5         |

| 14  | DB11                  | 19  | DB6         |

| 15  | DB10                  | 18  | DB7         |

| 16  | DB9                   | 17  | DB8         |

FSR means Full-Scar Range.

Temperature stability of linearity is guaranteed to a 1% AQL, 1 MIL-STD-105.

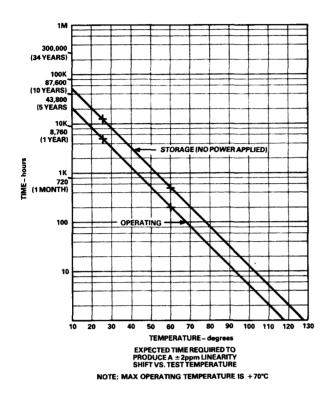

See Figure 7 for typical long-term linearity stability vs. tempen BURN-IN section on page 6 for caution against preconditional for the condition of the con . urity is guaranteed to a 1% AQL, Level II sampling plan per

Figure 9 provides typical LSB and full-scale settling time to within 1/2LSB at 12-to 18-bit resolutions.

\*Current Output Operation is structured for input to the summing junction of an amplifier.

Specifications subject to change without notice.

-2-

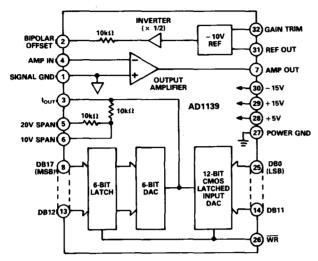

AD1139 Functional Block Diagram

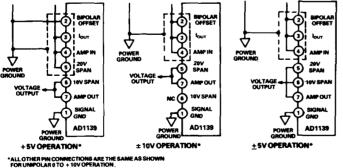

#### ANALOG OUTPUT RANGE

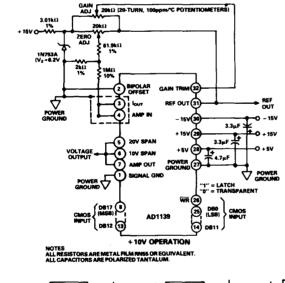

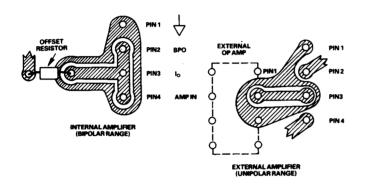

The AD1139 is pin programmable to provide a variety of analog outputs, either current or voltage. A unipolar output current of 0 to -1 mA is available at Pin 3 and can be offset by 0.5mA (connect Pin 2 to Pin 3) for a biolar output of  $\pm 0.5 \text{mA}$ . Output voltage ranges (+5 V, +10 V,  $\pm 5 \text{V}$  and  $\pm 10 \text{V}$ ) are available at Pin 7 by connecting the current output (Pin 3) to the amplifier input (Pin 4) and the appropriate internal feedback resistors to the amplifier output (Pin 7) as shown in Figure 1.

Figure 1. Output Voltage and Trim Configuration

## **OFFSET & GAIN CALIBRATION**

Initial offset and gain errors can be adjusted to zero by potentiometers as shown in Figure 1. The offset adjust range is plus 0.03% to minus 0.02% of full scale range (wiper of potentiometer to REF OUT equals plus 0.03%). The gain adjust range is plus 0.06% to minus 0.08% of full scale range (wiper to REF OUT equals plus 0.06%). Measurement instruments used should be capable of resolving  $1\mu V$  at plus full scale for the chosen output range and within  $1\mu V$  of zero.

#### Procedure:

#### UNIPOLAR MODE

- 1. Apply a digital input of all "0s."

- Adjust the offset potentiometer until a 0.000000V output is obtained.

- 3. Apply a digital input of all "1s."

- 4. Adjust the gain potentiometer until plus full-scale output is obtained (see Table I for exact value).

#### **BIPOLAR MODE**

- 1. Apply a digital input of 100 . . . . . 000.

- Adjust the offset potentiometer until a 0.000000V output is obtained.

- 3. Apply a digital input of all "1s."

- 4. Adjust the gain potentiometer until plus full-scale output is obtained (see Table I for exact value).

|                    | Code 000 00 | Code 111 11 | 1           |

|--------------------|-------------|-------------|-------------|

| Unipolar + 5V      | 0.000000V   | +4.999981V  |             |

| + 10V              | 0.000000V   | +9.999962V  |             |

|                    | Code 100 00 | Code 11111  | Code 00000  |

| Bipolar ± 5V ± 10V | 0.000000V   | +4.999962V  | - 5.000000V |

|                    | 0.000000V   | +9.999924V  | -10.000000V |

Table I. Full-Scale and Offset Calibration Voltages

| Symbol          | Parameter         | Requirement |

|-----------------|-------------------|-------------|

| t <sub>DS</sub> | Data Setup Time   | 160ns min   |

| t <sub>DH</sub> | Data Hold Time    | 120ns min   |

| t <sub>WR</sub> | Write Pulse Width | 200ns min   |

Table II. Timing Requirements

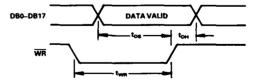

# TIMING DIAGRAM & LATCH CONTROL

Timing requirements for the AD1139 are shown in Table II. The timing diagram is shown in Figure 2. The WRite line controls an 18-bit wide data input latch. This latch is transparent when the WRite line is LOW, allowing all bits to be accessed directly. When the WRite line is activated HIGH, the data present at the inputs is held in the latch and the appropriate analog voltage is seen at the output.

Figure 2. AD1139 Timing Diagram

#### **GROUNDING & GUARDING**

The current from measurement ground (Pin 1) is small and independent of the digital input code to the DAC. This greatly simplifies making error free analog measurements. Connect this high quality ground to the system's or application's high quality ground. Connect the DAC's power ground (Pin 27) to the system return, also connect the system's high quality ground to the system return. It is most important that the measurement ground (Pin 1) and power ground (Pin 27) be connected externally for proper circuit operation.

The current output pin (I<sub>OUT</sub>, Pin 3) is sensitive to external noise sources, such as digital input lines. This pin and any components connected to this pin should be surrounded by a grounded guard as shown in Figure 3.

Figure 3. Guarding Recommendations

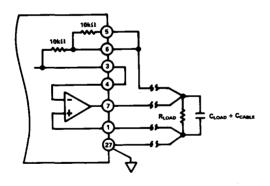

## REMOTE SENSE APPLICATION

The AD1139's remote sense capability allows driving heavy loads or long cables without the usual, accompanying gain errors. By sensing at the load, as described in Figure 4, the load current will pass through the amplifier's output and the power ground, but not through the sense lines. The potential gain errors that would be induced by this load current are therefore minimized. The load should not exceed  $\pm 10\text{mA}$  or 2 nanofarads to insure proper operation of the AD1139's internal output amplifier.

Figure 4. Remote Sensing

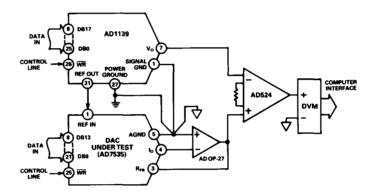

#### RATIOMETRIC DAC TESTING APPLICATION

The AD1139's highly stable reference output can be conveniently used in the testing of other high resolution DACs. Figure 5 describes how the REF OUT (Pin 31) is used as the external reference input to a device-under-test. The gain of the device-under-test will now accurately track the AD1139's gain and eliminate reference contribution to gain error.

When used as a reference DAC to test the integral and differential linearity of 14- and 16-bit DACs, the AD1139 provides a measurement capability with just 1/16LSB of uncertainty at 14 bits.

Gain and offset errors of the device-under-test (D.U.T.) may be accounted for in software. Once zeroed, the integral linearity error can be measured as the difference between the reference DAC (AD1139) and the D.U.T. as seen at the digital voltmeter.

The differential linearity error is then determined by incrementing or decrementing the D.U.T. digital input by 1LSB, and comparing the new output at the DVM with the previous output. The difference between these two measurements should be exactly one ideal LSB. The amount of disagreement from one ideal LSB is the differential linearity error.

Figure 5. Ratiometric DAC Testing

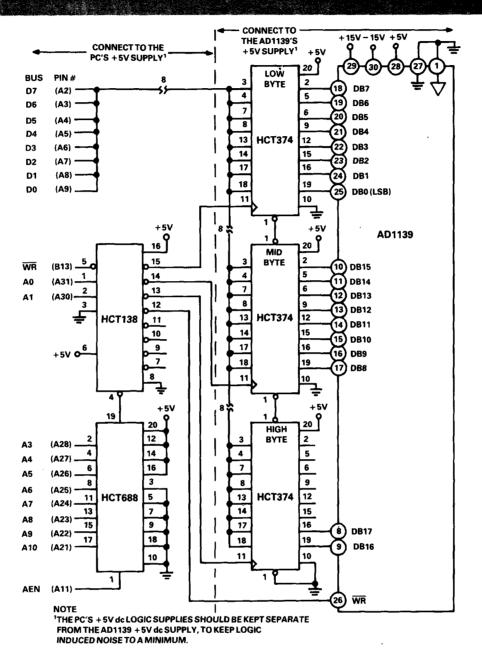

# IBM\* PC INTERFACE

Figure 6 illustrates a typical IBM personal computer interface which uses three 8-bit external latches and two decoder chips. The three HCT374 latches are connected to the data bus (D0 through D7). The HCT138 decoder chip decodes the address bus and enables each latch, including the AD1139's internal DAC latch, to see the appropriate digital word. The HCT688 chip and the HCT138 decoder define the I/O address space where the four latches will reside. In the Figure 6 example, they reside in the address space as shown in Table III.

| I/O Address  | Selected Latch | Data Bits  |

|--------------|----------------|------------|

| 380H         | Low Byte       | DB0-DB7    |

| 381 <b>H</b> | Mid Byte       | DB8-DB15   |

| 382H         | High Byte      | DB16, DB17 |

| 383H         | AD1139 Latch   | DB0-DB17   |

Table III. IBM Interface Address Locations

<sup>\*</sup>IBM is a trademark of International Business Machines Corp.

Figure 6. AD1139 to IBM PC Compatible Interface

# LONG-TERM STABILITY VS. TEMPERATURE

Adjusting the linearity of any DAC after it is installed in the application is often difficult or impossible. It is preferable to maintain some specified accuracy over the useful working life of the product (commonly 5 to 10 years). Stable linearity performance over time can, therefore, be a very important parameter for the DAC.

Accelerated testing to determine the expected linearity stability over time can be accomplished by two different methods. Linearity is first measured at  $+25^{\circ}$ C. The DAC is then operated at a fixed elevated temperature for an extended period of time. The DAC is then retested at  $+25^{\circ}$ C, and the change in linearity error vs. time is calculated. The ARRHENIUS EQUATION (used in reliability calculations) can be used to determine what the acceleration factor is from  $+25^{\circ}$ C to the elevated test tem-

perature. Knowing the acceleration factor and the linearity error vs. time at the elevated temperature, one could calculate the expected long-term stability of linearity at nominal temperatures.

A second test method determines how long it will take for the linearity to shift by a specific error band (we chose  $\pm 2$ ppm for our example) at any specified temperature. The first step is to measure the linearity at a moderately elevated temperature (e.g.,  $+85^{\circ}$ C) and then monitor how long it takes at this temperature to reach the error band limit. The second step is to perform the same test at a much higher elevated temperature (e.g.,  $+125^{\circ}$ C). The two resulting time vs. temperature points are then plotted on semilog paper. A line drawn through the two points allows extrapolation to the length of time expected to reach the error band ( $\pm 2$ ppm) at other temperatures, including  $+25^{\circ}$ C.

Figure 7 shows how long it would take for the AD1139's linearity to drift  $\pm 2$ ppm (1/2LSB) at any operating temperature. The uppermost plot shows stability under storage conditions (no power), and the lower plot shows the AD1139's operating stability (under power). The *operating vs. storage* difference is due to the  $10^{\circ}$ C temperature rise when the AD1139 is powered.

Figure 7. Nonlinearity vs. Time/Temperature

# **BURN-IN**

All AD1139s undergo a 168 hour, powered burn-in @125°C, prior to laser trimming. This burn-in produces the optimum stability for the resistor network and eliminates infancy defects.

As shown in Figure 7, exposure to elevated temperatures produces an acceleration of the normal aging process. Preconditioning/burnin employed by the user will lead to premature linearity shifts outside of the initial guaranteed specifications. The ADI warranty will not cover DACs that exhibit this type of *forced* premature specification degradation.

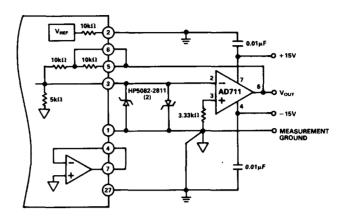

# EXTERNAL AMPLIFIER FOR HIGH SPEED OR HIGH OUTPUT CURRENT

The AD1139's internal output amplifier is optimized for very low noise, dc stable applications with moderate settling time. Applications requiring higher speed or more output current can use an external amplifier, such as shown in Figure 8. The AD711 settles to within 16 bits in only  $6\mu s$  for a unipolar full scale step. Other amplifiers may be chosen for differing tradeoffs. The noise gain seen by the output amplifier, depends on the output voltage range selected (see Table IV). The amplifier selected must be stable at the noise gain corresponding to the output range.

Figure 8. External Amplifier for High Speed

| Output Voltage Range | Noise Gain |

|----------------------|------------|

| 0 to +5V             | 2          |

| 0  to + 10 V         | 3          |

| ±5 <b>V</b>          | 4          |

| ± 10V                | 7          |

Table IV. Noise Gain vs. Output Voltage Range

#### SETTLING TIME

The LSB step and full-scale step typical settling times, to within  $\pm 1/2$ LSB at 18 bits, are shown in the Specification Table. Figure 9 graphically presents the typical settling times to within  $\pm 1/2$ LSB at resolutions from 12 to 18 bits.

NOTE

'LSB SETTLING TIMES SHOWN WILL ONLY BE ACHIEVED WITH

CLAMPING DIODES FROM THE DAC'S AMP IN (PIN 4) TO

GROUND PER FIGURE 1.

Figure 9. Settling Time vs. Resolution