# PCI SoundComm<sup>®</sup> DC '97 Digital Controller

AD1818

### **FEATURES**

Single-Chip 5 V PCI Digital Controller for Audio and Communications Acceleration Applications

64-Stream DirectSound® Hardware Mixer with Hardware Rate Conversion

Supports Full Duplex Capture and Playback Operation at Different Sample Rates

Supports Multiple Sample Rates Simultaneously Sample Rates from 1 Hz to 48 kHz

Windows® 98 WDM® Drivers Provided with the AD1818 "Digital Ready" PCI Bus Redirection Supports USB and IEEE 1394 Audio Peripherals

Integrated Large Memory 66 MIPS ADSP-21csp11 DSP Core Supports:

64-Voice Downloadable Sounds Wavetable Synthesizer

3D Sound Localization

5.1 Channel Dolby Digital® AC-3 Decompression with Virtual Home Theater Processing

**Telephony Applications**

V.34 and 56 kbps Voice Modem

**V.17 Fax**

V.70 DSVD

V.80 Video Conferencing Support

Full Duplex Speakerphone with Acoustic Echo Cancellation

**G.72x Voice Codecs**

Serial Interface to Audio Codec '97 (AC '97)

Support for Up to Four ADCs and Six DACs on the AC Link Serial Bus

PCI Bus Master/Target Interface with Scatter-Gather DMA Capability

On-Chip OPL3® Compatible Music Synthesizer MPU-401®-Compatible MIDI UART

Advanced Power Management Modes and PME# Signal Support ACPI, PCM-PM and On Now®

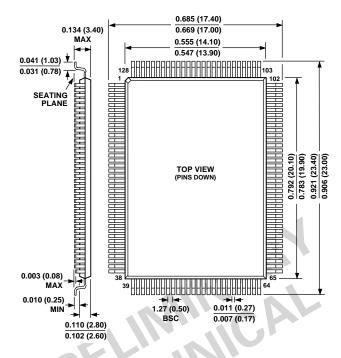

128-Terminal PQFP Package

Complete Set of Development Tools Available Including ICE, C Compiler, Assembler and Debugger

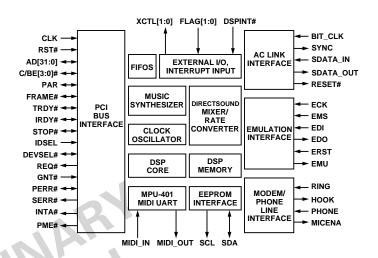

# FUNCTIONAL BLOCK DIAGRAM

# INTRODUCTION

The AD1818 5 V PCI SoundComm DC '97 Digital Controller is a full-featured DirectSound and telephony accelerator. In addition to processing DirectSound3D® coefficients locally, the AD1818 supports a 64-voice downloadable sounds wavetable engine, a music synthesizer, a 33.6 kbps V.34/56 kbps V.PCM voice modem data pump/controller (with 14400 bps fax) and a Dolby Digital AC-3 decoder. The AD1818 provides an integrated audio and telephony solution for Windows 98 DirectSound 5.0 audio/TAPI® telephony multimedia applications.

SoundComm is a registered trademark of Analog Devices, Inc. All other trademarks are the property of their respective holders.

# REV. 0

| TABLE OF CONTENTS                    |

|--------------------------------------|

| FEATURES 1                           |

| INTRODUCTION 1                       |

| Ordering Guide                       |

| Pin Configuration 3                  |

| Pin Function Descriptions 4          |

| ARCHITECTURAL OVERVIEW 6             |

| Block Diagram 6                      |

| INTEGRATING THE AD1818 INTO A TARGET |

| SYSTEM 7                             |

| SOFTWARE DRIVER SUPPORT 7            |

| AUDIO SOURCES 7                      |

| DirectSound                          |

| DirectSound Mixer 8                  |

| Extended DirectSound Mixer 8         |

| Sample Rate Converter 8              |

| MUSIC SYNTHESIS 9                    |

| MPU-401-COMPATIBLE MIDI UART 9       |

| DSP SECTION                          |

| DSP Boot                             |

| DSP INTERFACE REGISTERS 10           |

| DMA Transfer Count Register          |

| DMA Control Register                 |

| DSP Mailbox Registers                |

| PCI Memory Organization              |

| Wavetable Music Synthesis            |

| DSP to Mixed FIFOs on the AD1818     |

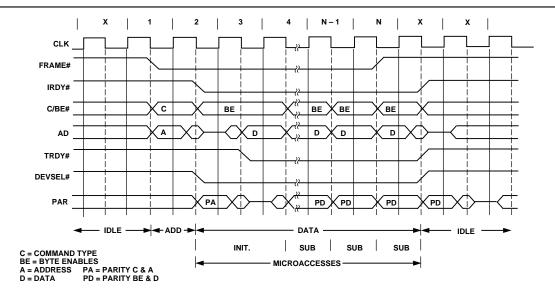

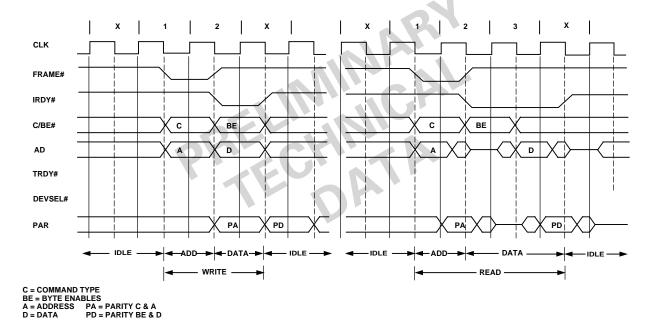

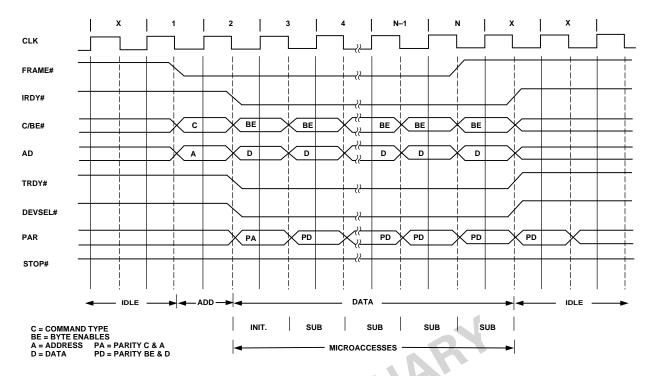

| PCI INTERFACE                                | 14 |

|----------------------------------------------|----|

| THE AD1818 LOGICAL DEVICE                    | 14 |

| SCATTER-GATHER DMA ON THE AD1818             | 14 |

| PCI Configuration Space Organization for the |    |

| AD1818                                       | 14 |

| CONFIGURATION SPACE REGISTER DEFINITION      | 15 |

| PCI MEMORY SPACE REGISTER DEFINITION         | 15 |

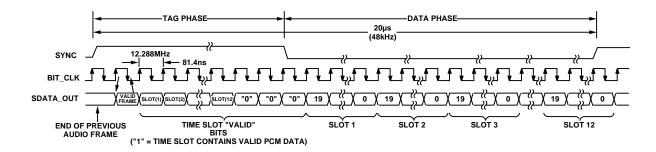

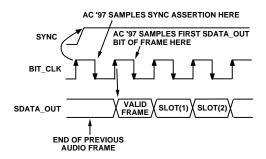

| ANALOG/DIGITAL INTERFACE                     | 19 |

| Analog/Digital AC '97 Protocol               | 19 |

| AC Link Audio Output Stream (SDATA_OUT)      | 19 |

| AC Link Audio Input Stream (SDATA_IN)        | 20 |

| Analog Codec Interface Control               |    |

| ELECTRICAL SPECIFICATIONS                    | 22 |

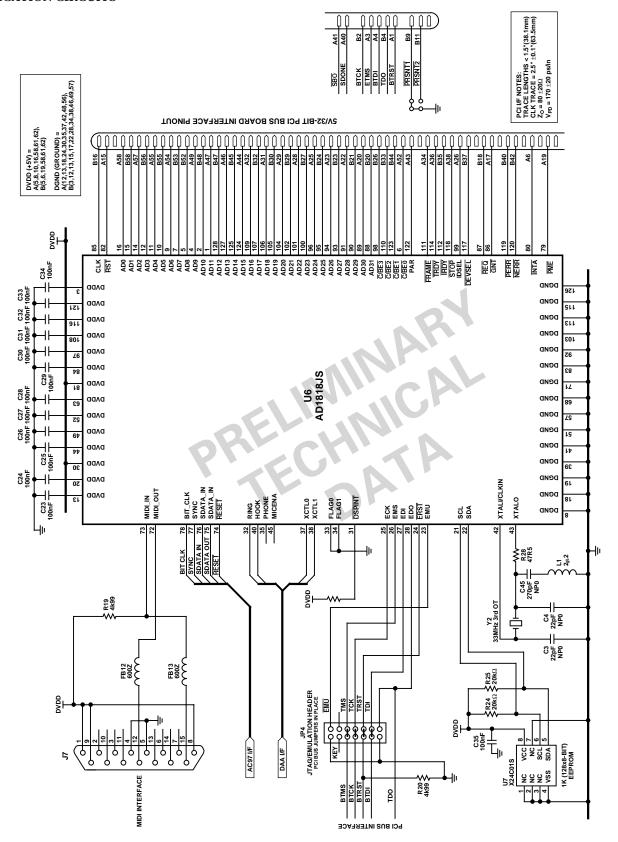

| APPLICATION CIRCUITS                         | 26 |

# **ORDERING GUIDE**

| Model    | Temperature<br>Range |                   | Package<br>Option* |

|----------|----------------------|-------------------|--------------------|

| AD1818JS | 0°C to +70°C         | 128-Terminal PQFP | S-128A             |

\*S = Plastic Quad Flatpack

# CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1818 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-2- REV. 0

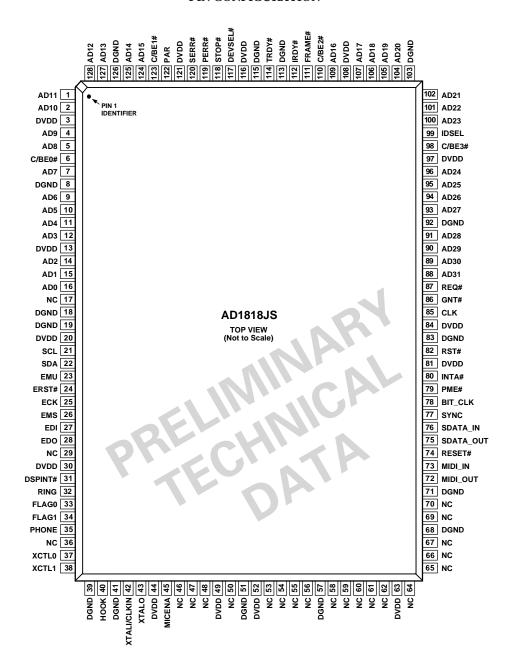

# PIN CONFIGURATION

REV. 0 \_3\_

# PIN FUNCTION DESCRIPTIONS

| T | $\alpha$ | -    | T .   | •    |

|---|----------|------|-------|------|

| 1 |          | KIIC | Inter | けつへん |

|   | $\sim$   | Dus  | IIII  | lace |

| Pin Name   | PQFP                                          | I/O | Description                        |

|------------|-----------------------------------------------|-----|------------------------------------|

| CLK        | 85                                            | I   | Clock                              |

| RST#       | 82                                            | I   | Reset                              |

| AD[31:0]   | 88, 89, 90, 91, 93, 94, 95, 96, 100, 101,     |     |                                    |

|            | 102, 104, 105, 106, 107, 109, 124, 125, 127,  |     |                                    |

|            | 128, 1, 2, 4, 5, 7, 9, 10, 11, 12, 14, 15, 16 | I/O | Address/Data Bus                   |

| C/BE[3:0]# | 98, 110, 123, 6                               | I/O | Command/Byte Enables               |

| PAR        | 122                                           | I/O | Parity                             |

| FRAME#     | 111                                           | I/O | Cycle Frame                        |

| TRDY#      | 114                                           | I/O | Target Ready                       |

| IRDY#      | 112                                           | I/O | Initiator (Master) Ready           |

| STOP#      | 118                                           | I/O | Stop                               |

| IDSEL      | 99                                            | I   | Initialization Device Select       |

| DEVSEL#    | 117                                           | I/O | Device Select                      |

| REQ#       | 87                                            | 0   | Request                            |

| GNT#       | 86                                            | I   | Grant                              |

| PERR#      | 119                                           | I/O | Parity Error                       |

| SERR#      | 120                                           | 0   | System Error                       |

| INTA#      | 80                                            | 0   | Interrupt A                        |

| PME#       | 79                                            | 0   | Power Management Event.            |

|            |                                               | AX  | Signal Changes in Power Management |

|            |                                               |     | State. Requested by AD1818, e.g.,  |

|            |                                               |     | Modem Wake-Up On Ring.             |

| AC Link    |                                               |     |                                    |

| TO AT      | DOED                                          | TIO | D                                  |

# **AC Link**

| Pin Name                        | PQFP           | I/O | Description                                 |

|---------------------------------|----------------|-----|---------------------------------------------|

| BIT_CLK<br>SYNC                 | 78<br>77<br>76 | O   | Serial Clock Frame Sync Serial Data Out     |

| SDATA_IN<br>SDATA_OUT<br>RESET# | 76<br>75<br>74 | 0 0 | Serial Data Out Serial Data In AC '97 Reset |

# **MIDI Interface**

| Pin Name | PQFP | I/O | Description     |

|----------|------|-----|-----------------|

| MIDI_IN  | 73   | I   | RxD MIDI Input  |

| MIDI_OUT | 72   | O   | TxD MIDI Output |

# **Emulation Interface**

| Pin Name | PQFP | I/O | Description          |

|----------|------|-----|----------------------|

| ECK      | 25   | I   | Emulator Clock       |

| EMS      | 26   | I   | Emulator Mode Select |

| EDI      | 27   | I   | Emulator Data Input  |

| EDO      | 28   | 0   | Emulator Data Output |

| ERST#    | 24   | I   | Emulator Logic Reset |

| EMU      | 23   | O   | Emulator Event Pin   |

# **EEPROM Interface**

| Pin Name | PQFP | I/O | Description  |

|----------|------|-----|--------------|

| SCL      | 21   | O   | Serial Clock |

| SDA      | 22   | I/O | Serial Data  |

REV. 0

|  | M | odem/l | Phone | Line | Interface |

|--|---|--------|-------|------|-----------|

|--|---|--------|-------|------|-----------|

| Pin Name | PQFP | I/O | Description                     |

|----------|------|-----|---------------------------------|

| RING     | 32   | I   | Ring Indicator from DAA         |

| HOOK     | 40   | 0   | On/Off Hook Control to DAA      |

| PHONE    | 35   | I   | Phone Pickup Indicator from DAA |

| MICENA   | 45   | О   | Microphone/Line Source Select   |

# Miscellaneous

| Pin Name                          | PQFP                   | I/O | Description                                 |

|-----------------------------------|------------------------|-----|---------------------------------------------|

| XCTL[1:0]<br>FLAG[1:0]<br>DSPINT# | 38, 37<br>34, 33<br>31 | O   | External Controls Input Flags DSP Interrupt |

# Crystal/Clock

| Pin Name    | PQFP | I/O | Description                      |

|-------------|------|-----|----------------------------------|

| XTALI/CLKIN | 42   | I   | 33 MHz Crystal Input/Clock Input |

| XTALO       | 43   | O   | 33 MHz Crystal Output            |

# Power Supplies/No Connects

| Pin Name | PQFP                                 | I/O     | Description                 |

|----------|--------------------------------------|---------|-----------------------------|

| DGND     | 8, 18, 19, 39, 41, 51, 57, 68, 71, 8 | 3, 92,  |                             |

|          | 103, 113, 115, 126                   | I       | Digital Ground              |

| DVDD     | 3, 13, 20, 30, 44, 49, 52, 63, 81, 8 | 4, 97,  |                             |

|          | 108, 116, 121                        | I       | +5 V Digital Supply Voltage |

| NC       | 17, 29, 36, 46, 47, 48, 50, 53, 54,  | 55, 56, | No Connect. Do Not Connect. |

|          | 58, 59, 60, 61, 62, 64, 65, 66, 67,  | 69, 70  |                             |

|          | PRIECH                               | ATA     |                             |

REV. 0 -5-

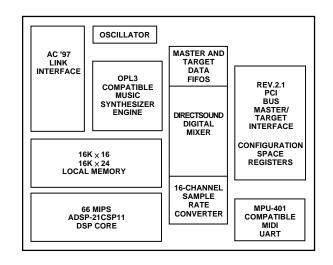

# ARCHITECTURAL OVERVIEW

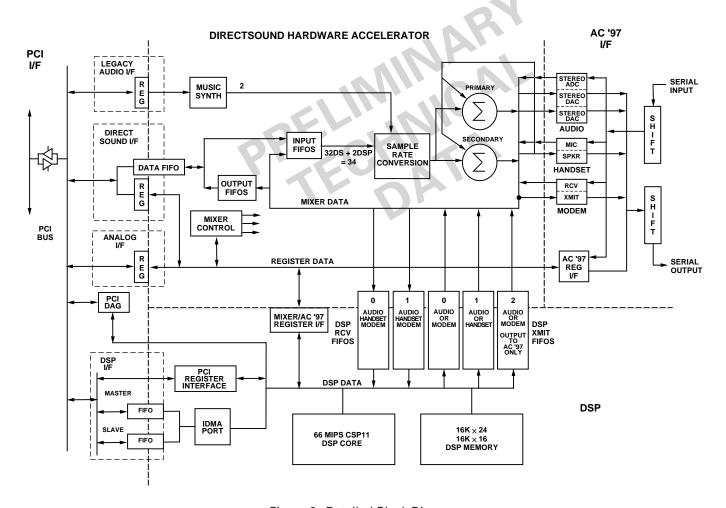

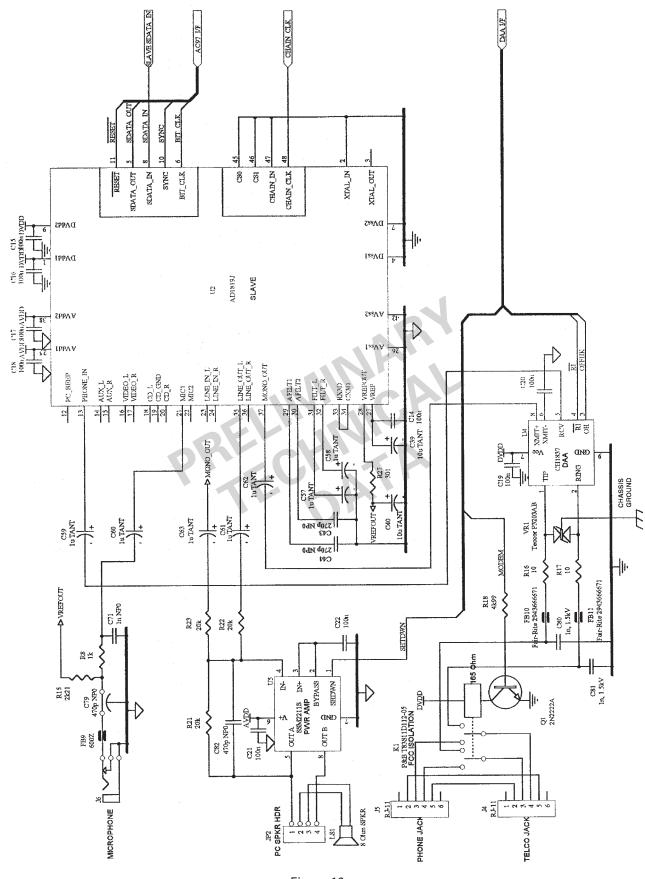

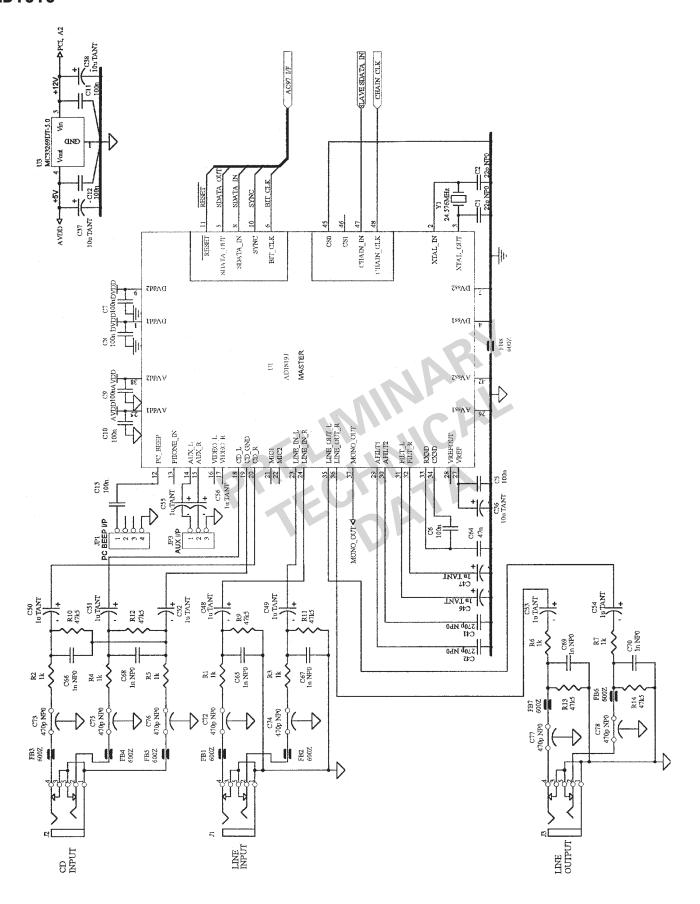

Figure 1 shows the functional blocks that make up the AD1818. The AD1818's design is focused to accelerate DirectSound and telephony algorithms. The PCI bus master/bus target interface provides the path for moving DirectSound data from host memory into the AD1818 for further acceleration. The 64-stream digital mixer and sample rate converters, combined with the internal DSP, accelerate mixing, sample rate conversion and 3D localization in hardware. The DSP may also be used to execute wavetable algorithms and Dolby Digital AC-3 decoding functions, and as a telephony data pump/controller. Figure 2 shows a detailed view of the AD1818 internal structure.

Figure 1. Block Diagram

Figure 2. Detailed Block Diagram

-6- REV. 0

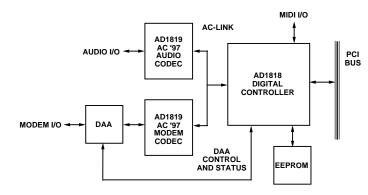

# **INTEGRATING THE AD1818 INTO A TARGET SYSTEM**

The system block diagram shows the essential features of an AD1818 design. The AD1818 acts as a master to the AC '97 audio codec providing digital processing for DirectSound audio data as well as communications data streams.

The AC '97 industry standard codec interface provides a direct connection point for an AC '97 compatible codec such as the AD1819 from Analog Devices.

Figure 3. System Block Diagram

# SOFTWARE DRIVER SUPPORT

The AD1818 Windows 98 DirectSound WDM drivers play a critical role in arbitrating AD1818 and system resources. Any algorithm or acceleration function such as digital mixing may be locally processed on the AD1818, the host or a combination of both.

A real-time operating system kernel runs on the DSP and performs several functions. These include:

Algorithm Loading

Algorithm Initialization

Algorithm Execution

Algorithm Termination

AD1818 Resource Sharing (Algorithm Cooperation)

Real-Time Task Scheduling and Execution Preemption

Clock and Timer Functions

# **AUDIO SOURCES**

### **DirectSound**

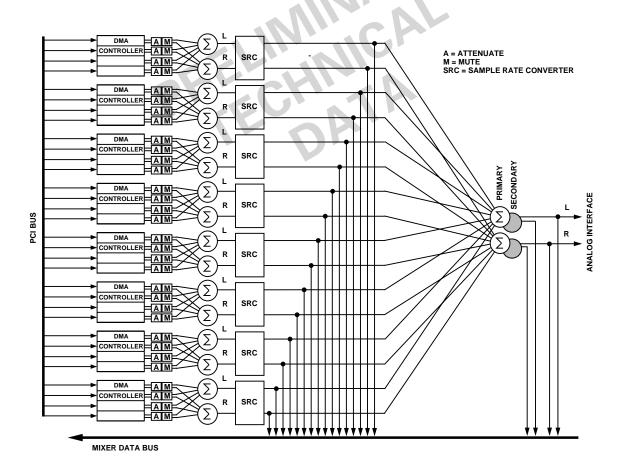

The AD1818 contains a 64-stream digital mixer block for DirectSound buffers. Four output channels are produced from the mixer, two of which are the primary audio left and right outputs. Each of the four channels can be optionally transferred back to the host for further processing.

Figure 4. Basic DirectSound Digital Mixer and Sample Rate Converters

REV. 0 -7-

# **DirectSound Mixer**

One of the principal features of DirectSound is mixing. Most games open between three to eight sound buffers and mix them simultaneously. A buffer contains either a mono or a stereo source. When multiple sounds are mixed in software, CPU utilization increases and system latency may cause sounds and visual cues to become unsynchronized. In order to allow games to run faster and more smoothly, the AD1818 has a built-in hardware mixer capable of mixing and sample rate converting up to 64 digital streams. The stereo output of the mixer may be sent the analog interface, the DSP for digital processing as in DirectSound 3D and effects, or returned to the host via the PCI Bus.

The AD1818's 32-channel PCI DMA Controller interface transfers either 32 stereo channels (64 streams) or 32 mono streams into the hardware mixer. The DMA controller directs the playing or stopping of a sample buffer and is capable of automatically looping to the start of a buffer. The DMA controller counts the number of bytes transferred and can stop playing a sample after a specified number of bytes have been transferred. If the number of bytes is greater than the length of the buffer, the buffer automatically loops back to the beginning.

After initiating a DMA transfer, the sample data enters the AD1818 mixer. Attenuation blocks (A) control the volume of a sample from 0 dB to –94.5 dB in 1.5 dB steps for the left and right channel of each stream, or the stream can be completely muted (M). Panning is supported by a combination of the left and right attenuation blocks, making the sound move across a sound field.

The streams are then summed together in blocks of four. Every four streams of left channel data (must be at the same sample rate) are summed together as well as every four streams of right channel data (same sample rate) producing eight separate samples of left and right data. The eight stereo samples then enter the sample rate converter block (SRC). Eight independent programmable SRC blocks convert the summed samples from a

user-specified sample rate to the AC '97 standard sample rate of 48 kHz. The input sample rate ranges from 1 Hz to 48 kHz in 1 Hz increments. The resulting left data may be returned to the Mixer Data Bus or summed to produce one left output stream. Right digital data may be returned to the Mixer Data Bus or summed to produce one right output stream completing the stereo sample pair of the Primary Summer. The stereo output of the Primary Summer may be sent to either the Mixer Data Bus or the Analog Interface. The Secondary Summer provides an additional stereo output for the Mixer Data Bus, which may be sent to the DSP for effects processing or routed back to the PCI bus.

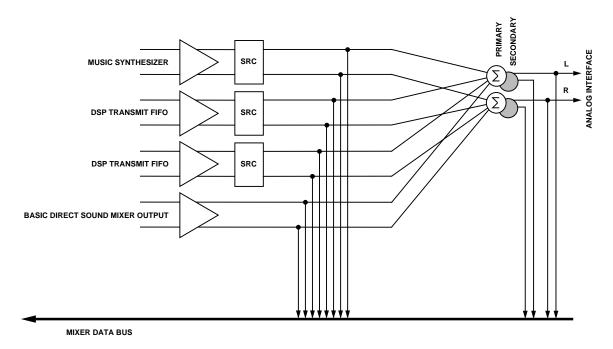

### **Extended DirectSound Mixer**

In addition to the AD1818's Basic DirectSound Mixer, an Extended Mixer and SRC stage handles streams sent to the Mixer Data Bus from the DSP and the internal Music Synthesizer.

The Extended Mixer allows for further processing and remixing of data. For example, data handled by the Basic Mixer may be sent to the DSP for effects processing and then mixed with the AD1818's output to generate effects such as echo and reverberation or DirectSound3D.

# Sample Rate Converter

The sample rate converter (SRC) blocks attached to the basic and extended DirectSound audio streams are variable interpolating SRCs. Each converter accepts samples at the rate of 1 Hz to 48 kHz and interpolates the samples to a common rate of 48 kHz. In addition, a variable decimation SRC is included to accept a single stereo channel of audio data at 48 kHz and decimate the sample to any rate between 1 Hz and 48 kHz.

Utilizing Analog Devices' variable sample rate technology, each SRC employs a scalable anti-aliasing or anti-imaging filter to properly filter the rate converted data. The result is a high performance multiple format and multiple sample rate mixer.

Given the high resolution of the SRCs, the mixer can be used to accelerate the pitch shifting operation for digital effect or music

Figure 5. Extended DirectSound Digital Mixer and Sample Rate Converters

REV. 0

generation. Since the interpolated data has a –90 dB SNR performance, the pitch shifting performed by the SRCs has no audible artifacts common in a lower quality pitch shifting algorithms. To shift the pitch, simply program the sample rate register of an audio stream to a different value. For example, to double the pitch of an 8 kHz prerecorded audio sample, program the sample rate register to 16000. Note that the valid range of the frequency register is 1 Hz to 48000 Hz. Sampled data cannot be pitch shifted beyond 48 kHz.

The variable decimation SRC provides a means to reduce audio data storage size by reducing the sample rate cleanly. For example, a 10 second recording of stereo audio data can be acquired at the AC Link as a 1.92 Mbyte file, or resampled and reformatted in real time with the SRC to a 80 kbyte mono, µlaw compressed, 8 kHz file.

### **MUSIC SYNTHESIS**

The AD1818 includes an embedded music synthesizer that emulates industry standard OPL3 FM synthesizer chips and delivers 20-voice polyphony. The internal synthesizer generates digital music data at 22.05 kHz. The Music Synthesizer's output is summed with the output stream. The Music Synthesizer on the AD1818 has register readback capability to facilitate power-down save and restore.

The music synthesizer has been developed by Euphonics, a research and development company that specializes in audio processing and electronic music synthesis.

### MPU-401-COMPATIBLE MIDI UART

The primary interface for communicating MIDI data to and from the host PC is the hardware MPU-401 compatible interface. The MPU-401 compatible interface includes a built-in FIFO for communicating to the host bus.

# **External EEPROM**

Pins SCL and SDA on the AD1818 are available to provide an interface to a serial EEPROM. When a serial EEPROM is connected to the AD1818, the Subsystem Vendor ID and Subsystem Device ID configuration space registers are loaded from the EEPROM. Loading of these registers occurs when the part exits reset. The four bytes are read starting at byte address 0, with the upper byte of the Subsystem Device ID read first followed by the lower byte of the Subsystem Device ID, upper byte of the Subsystem Vendor ID and, lastly, the lower byte of the Subsystem Vendor ID.

The 2-wire interface requires serial EEPROMs such as the X24C01 from Xicor. For the interface to be activated, external pullups are required on the SCL and SDA pins. If the SCL pin is pulled low upon reset, then the interface is automatically disabled and the default values remain in the Subsystem Vendor ID and Subsystem Device ID registers.

# **DSP SECTION**

The DSP in the AD1818 is based on the Analog Devices ADSP-21csp11 processor. Please refer to the ADSP-21csp11 Concurrent Signal Processor data sheet (Analog Devices publication C2180-8-10/96) for additional information on the ADSP-21csp11 core, memory and peripheral features and functions. This 16-bit DSP is optimized for concurrent signal processing and other high speed numeric processing applications. It combines high performance, high bandwidth, 32K words of on-chip memory and fast task switching support to provide efficient multisignal or multichannel processing.

The DSP base architecture consists of computational units, data address generators, a program sequencer and an instruction cache. The DSP on the AD1818 also has a programmable timer, extensive interrupt capabilities and 32K words of on-chip memory. The memory is organized into a single, unified memory space containing two memory blocks with 16K locations in each block. One block is  $16K \times 24$  bits and can be used to store instructions or data, while the other is  $16K \times 16$  bits and can be used to store data.

Additions to the DSP for the AD1818 include a high speed DMA interface to the PCI bus. As a PCI target, the DSP exposes its on-chip memory to the bus, allowing burst transfers via a FIFO to or from the DSP memory. As a bus master, the PCI interface can transfer DMA data between system memory and the DSP. The control registers for these transfers are available both to the host (in PCI memory space) and to the DSP.

Five FIFOs have also been added to interface the DSP to the audio and telephony data streams on the AD1818. The two receive and three transmit FIFOs are each eight words deep and 16 bits wide. Each FIFO has independent control, allowing a DSP interrupt to be generated when any number of words have been added to or taken from the FIFOs. Optionally, the on-chip DMA engine can be programmed to automatically transfer data between the FIFOs and DSP memory.

The DSP also has access to various control registers within the mixer and the analog interface.

The on-chip DSP operates at 66 MHz with a 16 ns instruction cycle time. With its large memory and on-chip instruction cache, the processor can execute most instructions in a single cycle.

The DSP's flexible architecture and comprehensive instruction set supports a high degree of parallelism. In one cycle the DSP can execute all of the following operations:

Perform a Computation

Perform One or Two Data Moves

Update One or Two Data Address Pointers

Generate a Program Address

Fetch an Instruction

Decode an Instruction

The operations take place while the processor continues to complete the following tasks:

Receive and Transmit Data through One or More of the FIFOs Receive or Transmit Data from the PCI Bus Decrement the Timer

# **DSP** Boot

Following power-up, the DSP core is held in idle, waiting to be booted. Boot code is downloaded from the PCI bus; there is no other method of booting the AD1818's DSP. During the boot code download process, the host is the PCI bus master and the AD1818 is a slave target. The DSP memory is mapped to PCI address space. This mapping is controlled through Base Address Register 4 in AD1818 PCI configuration space. This register controls the mapping of the on-chip  $16K \times 24$  DSP memory, which is nominally used for program memory. There is a separate register (Base Address Register 5 in AD1818 PCI configuration space) that maps the on-chip  $16K \times 16$  DSP memory, nominally used for data memory.

After the host is finished filling the DSP with boot code, the host must set the "Clear DSP Boot Mode" (Bit 3) in the DSP DMA Control Register (offset 0x1803-0x1802 from the AD1818 base

address). Setting this bit takes the DSP out of idle, and causes the DSP to start program execution from location 0x0000.

# **DSP INTERFACE REGISTERS**

# **DMA Transfer Count Register**

A 16-bit register contains the number of words to be transferred between PCI address space and the DSP internal memory. The word size refers to the width of transfers into the DSP internal memory. The word width may be 32 bits or 16 bits, depending on the state of the DSP Pack Mode bit in the DSP Control Register.

When the Transfer Count register reaches zero during a DMA transfer, the DMA channel is disabled. The Transfer Count register must be manually reinitialized before another DMA transfer may begin.

# **DMA Control Register**

This register contains bits used to control and observe the state of DMA transfers to the DSP core. The control bits are read/write bits. The status bits are read-only.

# **Control Bits**

# Bit # Description

- Master DMA Enable. When asserted enables, PCI master DMA on the DSP DMA channel. Must be toggled off, then on to restart when DMA is disabled via the PCI address generation logic or the Transfer Count register.

- 1 Master DMA Write/Not Read. When asserted, specifies DMA to write to PCI address space.

- 2 Flush Master DMA FIFO. When asserted, discards the current contents of the DMA Master FIFO and associated logic.

- 3 Clear DSP Boot Mode. When asserted, forces the DSP core to begin executing instructions from the DSP internal memory. This function is valid after DSP reset.

- 4 Master DMA Pack Mode. Specifies the DSP internal word width for DMA transfers (1 = 32-bit words). This bit alters the semantics of the Transfer Count register.

- D3 State Power-Down Enable. When set, allows a change to PCI power management state D3 to put the AD1818 into power-down.

- 6–7 Reserved.

# **Status Bits**

# Bit # Description

- 8 Master DMA FIFO empty. This bit is set to one when there is no data is in the Master DMA channel FIFO or packing logic.

- 9 Master DMA Halt Status. This bit is set to one when the Master DMA channel is disabled by the PCI address generation logic.

- 15-10 Reserved

# **DSP** Mailbox Registers

The DSP Mailbox registers are designed to allow the user to construct an efficient communications protocol between the PCI device driver and the DSP code. The mailbox functions consist of an InBox, OutBox and a control/status register.

### InBox

The incoming mailbox (InBox) is 32 bits wide. It may be read or written by either the PCI device or the DSP core. The PCI device may access any or all bytes at one time. The DSP core may only access 16 bits at one time. PCI writes to the InBox may generate DSP interrupts. DSP reads of InBox may generate PCI interrupts.

# **OutBox**

The outgoing mailbox (OutBox) is 32 bits wide. It may be read or written by either the PCI device or the DSP core. The PCI device may access any or all bytes at one time. The DSP core may only access 16 bits at one time. DSP writes to the OutBox may generate PCI interrupts. PCI reads from the OutBox may generate DSP interrupts.

### Control|Status

This register consists of read/write control bits and read/write-one-clear status bits (denoted R/W and R/WC respectively). A read/write-one-clear (R/WC) bit is cleared when a one is written to it. Writing a zero has no effect.

| Bit # | Type | Description                                                                                                                                                                                      |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–0   | R/WC | InBox Byte Data Valid. A one in these bits means valid data has been written into the corresponding InBox bytes. The bits are cleared when they are written with ones, or when InBox is read.    |

| 7–4   | R/WC | OutBox Byte Data Valid. A one in these bits means valid data has been written into the corresponding OutBox bytes. The bits are cleared when they are written with ones, or when OutBox is read. |

| 11-8  | R/O  | Reserved.                                                                                                                                                                                        |

| 12    | R/WC | InBox PCI Interrupt Pending. This bit is set when the DSP reads valid data from the InBox.                                                                                                       |

| 13    | R/WC | OutBox PCI Interrupt Pending. This bit is set when the DSP writes valid data to the OutBox.                                                                                                      |

| 14    | R/WC | InBox DSP Interrupt Pending. This bit is set when the PCI writes valid data to the InBox.                                                                                                        |

| 15    | R/WC | OutBox DSP Interrupt Pending. This bit is set when the PCI reads valid data from the OutBox.                                                                                                     |

| 16    | R/W  | InBox PCI Interrupt Enable. When asserted, allows the corresponding Interrupt Pending bit to be set.                                                                                             |

| 17    | R/W  | OutBox PCI Interrupt Enable. When asserted, allows the corresponding Interrupt Pending bit to be set.                                                                                            |

| 18    | R/W  | InBox DSP Interrupt Enable. When asserted, allows the corresponding Interrupt Pending bit to be set.                                                                                             |

| 19    | R/W  | OutBox DSP Interrupt Enable. When asserted, allows the corresponding Interrupt Pending bit to be set.                                                                                            |

| 31-20 |      | Reserved.                                                                                                                                                                                        |

# **PCI Memory Organization**

As mentioned above, the AD1818 on-chip memory is mapped to the PCI address space. Because one of the AD1818 memory

-10- REV. 0

|    |          |          | ESS SPACE | -        |               |

|----|----------|----------|-----------|----------|---------------|

| 31 | 24       | 23 16    | 15 8      | 7 0      | <u>OFFSET</u> |

|    | BYTE 3   | BYTE 2   | BYTE 1    | BYTE 0   | 0X0000 0000   |

|    | UNUSED   | USED     | USED      | USED     | 0X0000 0004   |

|    | •        | •        | . •       | •        | _             |

|    | UNUSED   | USED     | USED      | USED     | 0X0000 FFFC   |

|    | RESERVED | RESERVED | RESERVED  | RESERVED | 0X0001 0000   |

|    | RESERVED | RESERVED | RESERVED  | RESERVED | 0X0001 0004   |

|    | •        | •        | •         | •        | _             |

|    | RESERVED | RESERVED | RESERVED  | RESERVED | 0X0001 FFFC   |

Figure 6. Footprint of AD1818 "Unpacked"  $16K \times 24$  DSP Memory in PCI Address Space

|          |          | ESS SPACE | -        | OFFSET      |

|----------|----------|-----------|----------|-------------|

| 31 2     | 24 23 16 | 15 8      | 7 0      |             |

| BYTE 3   | BYTE 2   | BYTE 1    | BYTE 0   | 0X0000 0000 |

| USED     | USED     | USED      | USED     | 0X0000 0004 |

| •        | •        | •         | •        | •           |

| USED     | USED     | USED      | USED     | 0X0000 7FFC |

| RESERVED | RESERVED | RESERVED  | RESERVED | 0X0000 8000 |

| RESERVED | RESERVED | RESERVED  | RESERVED | 0X0000 8004 |

| •        | •        | •         | •        |             |

| RESERVED | RESERVED | RESERVED  | RESERVED | 0X0000 FFFC |

Figure 7. Footprint of AD1818 "Packed" 16K × 16 DSP Memory in PCI Address Space

0x4A

AC '97 Mic Input Attenuation

|         |                            | and the other AD 1010 memory block is        | 1   | UX4A        | AC 91 Mic Input Attenuation             |

|---------|----------------------------|----------------------------------------------|-----|-------------|-----------------------------------------|

| 16 bits | wide, there are            | two different "footprints" in PCI address    | 1   | 0x4C        | AC '97 Audio Input Attenuation          |

| space.  | The 16K by 24              | -bit DSP memory requests 128K bytes of       | 1   | 0x4E        | Reserved                                |

|         |                            | mory. Of this, 64K bytes are reserved (for   | 1   | 0x7E-0x50   | Reserved                                |

|         |                            | as of the AD1818 in the future), 48K bytes   | 1   | 0x80        | Mixer Channel 0 Input Sample Rate       |

|         |                            | es are unused. This footprint is illustrated | 1   | 0x82        | Mixer Channel 1 Input Sample Rate       |

| in Figu | •                          |                                              |     |             |                                         |

| _       |                            |                                              | 1   | 0x8E        | Mixer Channel 7 Input Sample Rate       |

|         |                            | P memory requests 64K bytes of "packed"      | 1   | 0x90        | Reserved                                |

|         |                            | 32K bytes are reserved (for larger memory    | 1   | 0x92        | Reserved                                |

|         |                            | 8 in the future) and 32K bytes are used.     |     | 0x94        | DSP Channel 0 Input Sample Rate         |

| This fo | otprint is illust          | rated in Figure 7.                           | 1   | 0x96        | DSP Channel 1 Input Sample Rate         |

| Interna | al DSP I/O Aco             | cess Addresses                               | 1   | 0x98        | Reserved                                |

|         | I/O                        |                                              | 1   | 0x9C-0x9A   | Reserved                                |

| Page    | Address                    | DirectSound Mixer Control Register           | 1   | 0x9E        | Reserved                                |

| 0       | 0x00                       | DMA Input Channel 0–3 Mixer Control          | 2   | 0x00        | Audio Output Channel Select Register    |

| 0       | 0x02                       | DMA Input Channel 4–7 Mixer Control          | 2   | 0x02        | Host/DSP Output Channel Select Register |

| U       |                            | Divin input Chamier 4–7 white Control        | 2   | 0x1E-0x04   | Reserved                                |

| 0       | 0x0E                       | DMA Input Channel 28–31 Mixer Control        | 2   | 0x20        | Output Channel 0 (Variable Output)      |

| 0       | 0x1E-0x10                  | Reserved                                     |     |             | Sample Rate                             |

| 0       | 0x12 - 0x10<br>0x22 - 0x20 | DMA Input Channel Enable Register            | 9–3 | 0xFE-0x00   | Reserved                                |

| 0       | 0x3E-0x24                  | Reserved                                     | A   | 0x43 - 0x40 | DSP DMA Output Channel Base Address/    |

| 0       | 0x40                       | DMA Output Channel 0 Mixer Control           |     |             | SGD Table Pointer                       |

| 0       | 0x42                       | DMA Output Channel 1 Mixer Control           | A   | 0x47 - 0x44 | DSP DMA Output Channel Current          |

| O       |                            | Divir output Ghanner i ivincer Gontroi       |     |             | Address/SGD CUR Pointer Address         |

| 0       | 0x46                       | DMA Output Channel 3 Mixer Control           | A   | 0x4B-0x48   | DSP DMA Output Channel Base Count/      |

| 0       | 0x48                       | DMA Output Channel Enable Register           |     |             | SGD Pointer                             |

| 0       | 0x7E-0x4A                  | Reserved                                     | A   | 0x4E-0x4C   | DSP DMA Output Channel Current Count    |

| 0       | 0x80                       | Reserved                                     | A   | 0xFE-0x50   | Reserved                                |

| 0       | 0xFF-0x82                  | Reserved                                     | C–B |             | Reserved                                |

| 1       | 0x00                       | DMA Input Channel 0 Attenuation              | D   | 0x22-0x20   | DSP DMA Output Channel Interrupt Count  |

| 1       | 0x02                       | DMA Input Channel 1 Attenuation              | D   | 0x26-0x24   | DSP DMA Output Channel Interrupt Base   |

|         |                            | •                                            | -   |             | Count                                   |

| 1       | 0x3E                       | DMA Input Channel 31 Attenuation             | D   | 0xFE-0x24   | Reserved                                |

| 1       | 0x40                       | Reserved                                     | F   | 0x18-0x00   | Reserved                                |

| 1       | 0x42                       | Reserved                                     | F   | 0x22-0x20   | DSP DMA Output Channel PCI Control      |

| 1       | 0x44                       | DSP Output Channel 0 Attenuation             |     | 0 FF 0 0:   | Status                                  |

| 1       | 0x46                       | DSP Output Channel 1 Attenuation             | F   | 0xFF-0x24   | Reserved                                |

|         |                            |                                              |     |             |                                         |

REV. 0 -11-

0x48

Music Synthesis Attenuation

blocks is 24 bits wide, and the other AD1818 memory block is

# AC '97 Interface Registers

| Page  | Address   | Register                              |

|-------|-----------|---------------------------------------|

| 10    | 0x7E-0x00 | Register Set                          |

| 10    | 0x80      | Analog Codec Interface Control/Status |

| 17-11 |           | Reserved                              |

# **DSP** Control Registers

| Page | Address     | Register               |

|------|-------------|------------------------|

| 18   | 0x00        | DMA Transfer Count     |

| 18   | 0x02        | DMA Control            |

| 18   | 0x06-0x04   | Mailbox Control/Status |

| 18   | 0x0A - 0x08 | Incoming Mailbox       |

| 18   | 0x0E-0x0C   | Outgoing Mailbox       |

### Wavetable Music Synthesis

Wavetable music synthesis algorithms are run on the internal DSP. The software wavetable engine will perform the necessary pitch shifting and envelope generation prior to mixing the channel back into the output streams.

System (PCI) memory is used for the storage of wavetable samples while the wavetable engine is in use. During application initialization, the wavetable driver will load the wavetable samples into memory for use by the AD1818. The samples need not be in contiguous memory; instead, they will be accessed by the AD1818 via scatter-gather DMA transfers. The standard DLS downloadable sounds format is supported by the AD1818 wavetable driver.

The AD1818 wavetable driver provides all of the control required for the chip to perform the necessary sample rate conversion, envelope generation and effects processing. This includes MIDI command interpretation, location of note samples in memory and passing parameters to the AD1818 for note events.

The wavetable synthesizer has been developed by Euphonics, a research and development company that specializes in audio processing and electronic music synthesis.

# INTERRUPT STRUCTURE

Various flag input and output and interrupt pins within the DSP core are assigned to particular functions within the AD1818. The assignments are as follows:

| 112 1010, 1110 | 40018 | and the second of the second o |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWD            | -     | Power-Down Interrupt. Connected to bit in the PCI DSP Control register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IRQ3           | -     | PCI Mailbox Interrupt. Writing to the incoming mailbox register or reading from the outgoing mailbox register via the PCI bus can generate this interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IRQ2           | _     | Ring. Connected to the RING pin on the AD1818. This is an active-HIGH interrupt. Also connected without inversion to FLAGIN[3]. Used to connect to the RING signal from the DAA for modem operation. If modem is not used, can be a general purpose interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IRQ1           | -     | Connected to external pin. General purpose interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IRQ0           | -     | 48 kHz SYNC. Connects AD1818 DSP core to the start of frame signal. Used to time data transfers to the core for audio effects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| USER1          | -     | FIFO2 Transmit. Connected to the transmit interrupt for the third, transmit-only FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| USER0          | - | PCI D1 Power-Up. Connected to the PCI power management control. Used to bring the DSP out of Idle while in the D1 power state.                                                                              |

|----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLAGIN0-1      | _ | General Purpose signals from pins.                                                                                                                                                                          |

| FLAGIN3        | - | Ring. See above. Brought to FLAGIN for ring counting.                                                                                                                                                       |

| FLAGIN2        | _ | Phone. From DAA.                                                                                                                                                                                            |

| FLAGIN4        | _ | Reserved.                                                                                                                                                                                                   |

| FLAGIN5        | - | Analog Interface Ready. Signals that the analog front-end is ready.                                                                                                                                         |

| FLAGIN6-7      | _ | Reserved.                                                                                                                                                                                                   |

| FLAGOUT0-1     | _ | General Purpose Signals to output pins.                                                                                                                                                                     |

| FLAGOUT2       | - | Hook. Signal to DAA to connect to phone line. Can be used as a general purpose pin output signal.                                                                                                           |

| FLAGOUT3       | - | MICENB. Signal to enable microphone. Can be used as a general purpose pin output signal.                                                                                                                    |

| FLAGOUT4       | _ | PME Power-Up Request. Signal to request a PME event on the PCI bus to wake up the bus. A PME event will occur if the PME_En bit is set in the PCI configuration PMCSR register and this signal is asserted. |

| EL A COLUETE E |   | D 1                                                                                                                                                                                                         |

FLAGOUT5-7 - Reserved.

Table I. Interrupt Vector Table for the AD1818

| Bit | Pri | Interrupt                | Vector Address |

|-----|-----|--------------------------|----------------|

| 0   | 1   | Reset (Nonmaskable)      | 0x00           |

| 1   | 2   | Power-Down (Nonmaskable) | 0x04           |

| 2 3 | 3 4 | User Interrupt 3         | 0x08           |

| 3   | 4   | PCI Mailbox (IRQ3)       | 0x0C           |

| 4 5 | 5   | Timer                    | 0x10           |

| 5   | 6   | User Interrupt 2         | 0x14           |

| 6   | 7   | Ring (IRQ2)              | 0x18           |

| 7   | 8   | IDMA                     | 0x1C           |

| 8   | 9   | IRQ1                     | 0x20           |

| 9   | 10  | FIFO0 Transmit           | 0x24           |

| 10  | 11  | FIFO0 Receive            | 0x28           |

| 11  | 12  | FIFO1 Transmit           | 0x2C           |

| 12  | 13  | FIFO1 Receive            | 0x30           |

| 13  | 14  | 48 kHz SYNC (IRQ0)       | 0x34           |

| 14  | 15  | FIFO2 Transmit           | 0x38           |

| 15  | 16  | PCI D1 Power-Up (User 0) | 0x3C           |

|     |     |                          |                |

# **DSP** to Mixer FIFOs on the AD1818

Five FIFOs provide an interface on the AD1818 between the DSP and the mixer data bus in the AD1818 core. Two of the FIFOs are inputs FIFOs, receiving data from the mixer data bus into the DSP. The other three FIFOs are transmit FIFOs, sending data from the DSP to the mixer. Each of the FIFOs are eight words deep and 16 bits wide. Interrupts to the DSP can be generated when some (programmable) number of words have been received in the input FIFOs or when some (programmable) number of words are empty in the transmit FIFOs.

The interface to the FIFOs on the DSP is simply a register interface to the IDMD bus. Tx0, Rx0, Tx1, and Rx1 are the primary FIFO registers in the universal register map of the DSP. STCTL0-2, SRCTL0-1, Tx2 and ABFCTL0-2 are the FIFO control registers and are located in the memory-mapped register space of the DSP. The FIFOs can be used to generate interrupts to the DSP based upon FIFO transactions or can initiate DMA

-12- REV. 0

requests. FIFO2 uses the DMA3 controller and the USER-1 (#14) DSP interrupt.

The interface to the FIFOs on the mixer side is via the mixer address and data bus. Each of the transmit FIFOs is assigned two addresses on the mixer bus, one for left data and one for right data. Upon reset or when the transmit FIFO is disabled, zeros are driven to the mixer bus when the FIFO is addressed. When the FIFO is in mono mode, both left and right will get the same data. FIFO2 always transmits stereo data. If the transmit FIFOs run out of data then the last data shipped will continue to be sent when addressed.

The transmit FIFOs can also be used to ship data to the modem output on the analog codec (AC '97) interface. When modem mode is enabled in the transmit FIFO, it responds to the modem\_out address on the mixer data bus instead of the dsp\_in addresses (this applies to FIFO0 or FIFO2 only). Zeros are shipped to the mixer in modem mode. Handset audio is handled similarly. While FIFO0 or FIFO2 support modem\_out, FIFO1 handles handset out.

On the receive side, the receiver will respond to addresses that are programmed into its receive control register. Thus the receive FIFOs can collect any of the data that is sent on the mixer data bus. If stereo is enabled in the receive FIFOs, then both left and right data will be collected. In mono mode, only the left data will be collected. The data input can be from any of the rate converted output streams or from the analog codec (AC '97) interface.

Table II shows the register format for each FIFO.

### Table II.

# STCTL0/1 Transmit Control and Status Register

| Rit | <b>Function</b> | When | Rit C | at to 61 | ,, |

|-----|-----------------|------|-------|----------|----|

| DIL | runction        | wnen | DIL 3 | et to "T |    |

- 0 Tx Enable

- Tx Stereo Enable 1

- Modem Output Enable on Mixer Channel 36 (FIFO0) 2 Handset/Speaker Output Enable on Channel 54 (FIFO1)

- Reserved

- Bits 4 through 11 Reserved . . .

- Reserved 12

- Transmit FIFO Full (Read Only) 13

- Transmit FIFO Empty (Read Only) 14

- Transmitter Empty (Read Only)

Default State After Reset: 0x00

# STCTL2 Transmit-Only FIFO Control and Status Register

# Bit Function When Bit Set to "1"

- Tx Enable (by Itself: Enables Channels 44/45) 0

- 1 Reserved

- 2 Modem Output Enable (On Channel 36)

- 4-Channel (with Tx Enable, Enables Channels 46/47) 3

- 4 6-Channel (with Tx Enable, Enables Channels 52/53)

- 5 Reserved

- Bits 6 through 11 Reserved

- Reserved 12

- Transmit FIFO Full (Read Only) 13

- Transmit FIFO Empty (Read Only) 14

- 15 Transmitter Empty (Read Only)

Default State After Reset: 0x00

# SRCTL0/1 Transmit-Only FIFO Control and Status Register

# Function When Bit Set to "1"

- 0 Rx Enable

- 1 Rx Stereo Enable

- 2 Rx Select Address (LSB)

- Rx Select Address

- Rx Select Address

- 5 Rx Select Address

- Rx Select Address (MSB) 6

- Reserved

- Bits 8 through 11 Reserved

- Reserved 12

- 13 Receive FIFO Full (Read Only)

- 14 Receive FIFO Empty (Read Only)

- 15 Receiver Full (Read Only)

Default State After Reset: 0x00

# ABFCTL0/1 DMA and FIFO Control Register

# Function When Bit Set to "1"

- 0 Tx FIFO Enable

- Rx FIFO Enable 1

- Reserved

- Reserved

- Tx FIFO Interrupt Position (LSB)

- Tx FIFO Interrupt Position

- Tx FIFO Interrupt Position (MSB)

- Reserved

- Rx FIFO Interrupt Position (LSB)

- Rx FIFO Interrupt Position

- 10 Rx FIFO Interrupt Position (MSB)

- Reserved 11

- 12 Tx DMA Enable

- Reserved 13

- 14 Rx DMA Enable

- Reserved

Default State After Reset: 0x00

# ABFCTL2 DMA and FIFO Control Register

#### Function When Bit Set to "1" Bit

- 0 Tx FIFO Enable

- Reserved 1

- Reserved

- 3 Reserved

- 4 Tx FIFO Interrupt Position (LSB)

- 5 Tx FIFO Interrupt Position

- 6 Tx FIFO Interrupt Position (MSB)

- Reserved

- Bits 8 through 10 Reserved

- Reserved 11

- 12 Tx DMA Enable

- 13 Reserved

- 14 Reserved

- 15 Reserved

The FIFOs also use the DSP core registers Tx buffer and Rx buffer. FIFO2's Tx register is a sysctll register, reg (0xlA) = reg(tx2). There is a total of 4 "memory-mapped" registers per DSP serial port (SPORT).

DirectSound Output Channel to Select Channel Matching

| Select | Data Stream    | Transaction Source       | Data Source       |

|--------|----------------|--------------------------|-------------------|

| 0      | DS[0]          | Rate Converter/48 kHz    | Rate Converter    |

| 1      | DS[1]          | Rate Converter/48 kHz    | Rate Converter    |

| 2      | DS[2]          | Rate Converter/48 kHz    | Rate Converter    |

| 3      | DS[3]          | Rate Converter/48 kHz    | Rate Converter    |

| 4      | DS[4]          | Rate Converter/48 kHz    | Rate Converter    |

| 5      | DS[5]          | Rate Converter/48 kHz    | Rate Converter    |

| 6      | DS[6]          | Rate Converter/48 kHz    | Rate Converter    |

| 7      | DS[7]          | Rate Converter/48 kHz    | Rate Converter    |

| 8      | Reserved       |                          |                   |

| 9      | Reserved       |                          |                   |

| A      | dsp_out[0]     | Rate Converter/48 kHz    | Rate Converter    |

| В      | dsp_out[1]     | Rate Converter/48 kHz    | Rate Converter    |

| C      | Music Synth    | Rate Converter/48 kHz    | Rate Converter    |

| D      | var_out        | Rate Converter/Variable  | Rate Converter    |

| E      | audio out      | Rate Converter/48 kHz    | Rate Converter    |

| F      | hdsp_out       | Rate Converter/48 kHz    | Rate Converter    |

| 10     | audio_in       | AC '97/48 kHz            | AC '97            |

| 11     | modem_in       | AC '97/Variable          | AC '97            |

| 12     | modem_out      | AC '97/Variable          | AC '97            |

| 13     | mic_in         | AC '97/Variable          | AC '97            |

| 14     | dsp_from[0]    | Rate Converter/Variable  | DSP               |

| 15     | dsp_from[1]    | Rate Converter/Variable  | DSP               |

| 16     | dsp_2_acif[0]  | AC '97/Variable          | DSP               |

| 17     | dsp_2_acif[1]  | AC '97/Variable          | DSP               |

| 18     | reserved       |                          |                   |

| 19     | reserved       |                          |                   |

| 1A     | dsp_2_acif[2]  | AC '97/Variable          | DSP               |

| 1B     | handset        | AC '97/ Variable         | DSP               |

| 1C     | music synth_in | Rate Converter/22.05 kHz | Music Synthesizer |

| 1D     | Reserved       |                          | AVY               |

| 1E     | Reserved       |                          | W                 |

| 1F     | Reserved       |                          |                   |

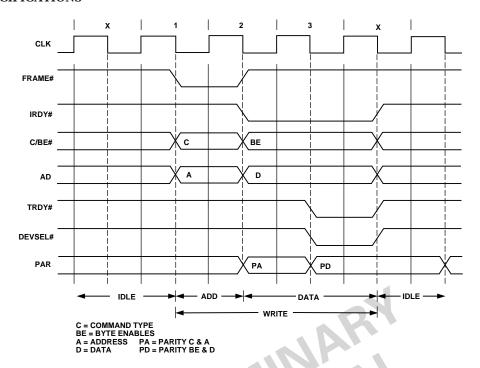

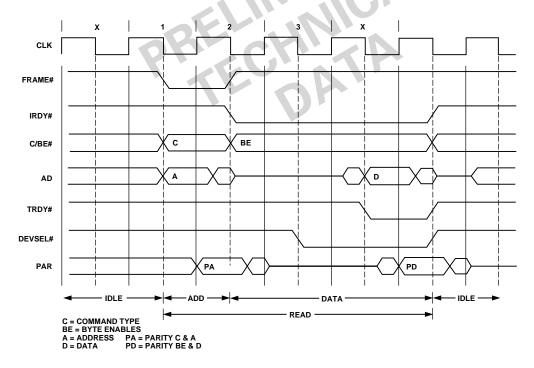

# **PCI INTERFACE**

In order to support the high data throughput required for concurrent audio and telephony algorithms, the AD1818 includes a 33 MHz, 32-bit bus master 5 V PCI interface. The interface is compliant with revision 2.1 of the PCI specification, and the AD1818 is memory-mapped to the PCI bus.

# THE AD1818 LOGICAL DEVICE

The DirectSound Mixer block provides the PCI interface necessary for the 64-stream Mixer block. This interface supports the use of system memory for storage of wavetable samples and envelopes. On-chip FIFOs provide the buffering needed to support high throughput on the PCI bus and samples as needed for the wavetable synthesizer. Scatter-gather capability is provided for each DMA channel. A MIDI MPU-401 interface to the MIDI IN and MIDI OUT pins is also provided by this logical device.

The AC '97 interface is the primary interface to the main analog codec front-end. A FIFO buffers data to and from the serial codec interface.

The PCI interface to the on-chip DSP provides both master and slave burst capability between system memory and the on-chip DSP memory. Separate target addressing is provided for the 24-bit DSP program memory space and the 16-bit DSP data memory space. Bus master DMA can be controlled by either the DSP through an internal interface or the host via the PCI interface. Separate data FIFOs exist for target and master transfers.

### **SCATTER-GATHER DMA ON THE AD1818**

When Direct Memory Access (DMA) is active, it will "steal" one cycle from the DSP core for each transfer that takes place. During the DMA transfer, no other DSP core activity occurs. When transferring audio samples to the wavetable engine or the codec engine, the DMA transfer can be programmed to perform scatter-gather DMA. This mode allows the audio samples to be split up in memory, and yet able to be transferred to and from the AD1818 without processor intervention. In Scatter-Gather mode, the DMA controller can read the memory address and word count from an array of buffer descriptors called the Scatter-Gather Descriptor (SGD) table. This allows the DMA engine to sustain DMA transfers until all buffers in the Scatter-Gather Descriptor table are transferred.

To initiate a Scatter-Gather transfer between memory and the AD1818, the following steps are involved:

- 1. Software driver prepares a SGD table in system memory. Each Scatter-Gather Descriptor (SGD) is eight bytes long and consists of an address pointer to the starting address and the transfer count of the memory buffer to be transferred. In any given SGD table, two consecutive SGDs are offset by eight bytes and are aligned on a 4-byte boundary. Each SGD contains:

- a. Memory Address (Buffer Start) 4 Bytes

- b. Byte Count (Buffer Size) 3 Bytes

- c. End of Linked List (EOL) 1 Bit (MSB)

- d. Flag 1 Bit

- 2. Initialize DMA control registers with transfer specific information such as bit width, compression mode, etc.

- 3. Software driver initializes the hardware pointer to the SGD table.

- 4. Engage Scatter-Gather DMA by writing the Start value to the Scatter-Gather Command register.

- 5. The AD1818 will then pull in samples as pointed to by the Scatter-Gather descriptors as needed by the audio synthesis engine. When the End of Linked List (EOL) is reached, a status bit will be set and the DMA will end if the sample is not to be looped. If looping is to occur, DMA transfers will continue from the beginning of the sample until a Stop command is received in the Scatter-Gather command register.

- 6. Bits in the Scatter-Gather command register control whether or not an interrupt occurs when the End of Linked List is reached or when the flag bit is set.

# PCI Configuration Space Organization for the AD1818

The AD1818 contains a single Configuration Space with six separate address spaces pointed to by address registers in that configuration space. The function is logical device 0. All of the AD1818 address spaces (including the Configuration Space) are memory-mapped to the PCI bus.

-14- REV. 0

# **CONFIGURATION SPACE REGISTER DEFINITION** Configuration Space Register Map

| Address           | Register                                | Comments                      |

|-------------------|-----------------------------------------|-------------------------------|

| 0x01-0x00         | Vendor ID                               | Hardwired – 0x11D4            |

| 0x03-0x02         | Device ID                               | Hardwired – 0x1818            |

| 0x05-0x04         | Command Register                        | Reset to 0, See Note (a)      |

| 0x07 - 0x06       | Status Register                         | See Note (b)                  |

| 0x08              | Revision ID                             | Hardwired – 0x00              |

| 0x0B-0x09         | Class Code                              | Hardwired – 0x040100          |

| 0x0C              | Cache Line Size                         | Unimplemented                 |

| 0x0D              | Latency Timer                           | R/W, Reset to 0               |

| 0x0E              | Header Type                             | Hardwired to 0                |

| 0x0F              | BIST                                    | Unimplemented                 |

| 0x13-0x10         | Base Address 0                          | 8K Bytes Prefetchable         |

|                   |                                         | DirectSound, Codec, DSF       |

|                   |                                         | Registers                     |

| 0x17 - 0x14       | Base Address 1                          | 16 Bytes Nonprefetchable      |

|                   |                                         | Music Synthesis Registers     |

| 0x1B-0x18         | Base Address 2                          | 16 Bytes Nonprefetchable      |

|                   |                                         | MIDI MPU-401 Interface        |

| 0x1F-0x1C         | Base Address 3                          | 16 Bytes Nonprefetchable      |

|                   |                                         | Legacy Control Interface      |

| 0x23-0x20         | Base Address 4                          | 128K Bytes Prefetchable       |

|                   |                                         | 24-Bit DSP Memory             |

| 0x27 - 0x24       | Base Address 5                          | 64K Bytes Prefetchable.       |

| 0 AD 0 A0         | O II OTO D :                            | 16-bit DSP Memory             |

| 0x2B-0x28         | Cardbus CIS Pointer                     | Unimplemented                 |

| 0x2D-0x2C         | Subsystem Vendor ID                     | Reset to 0x11D4               |

| 0x2F-0x2E         | Subsystem ID                            | Reset to 0x1818               |

| 0x33-0x30         | Expansion ROM                           | Unimplemented                 |

| 024               | Base Address                            | Hardwind O-DC                 |

| 0x34              | Capability Pointer Reserved in PCI Spec | Hardwired – 0xDC              |

| 0x3B-0x35<br>0x3C | Interrupt Line                          | Unimplemented R/W, Reset to 0 |

| 0x3C<br>0x3D      | Interrupt Pin                           | Hardwired – 0x01 (Uses        |

| UX3D              | interrupt Pin                           | INTA#)                        |

| 0x3E              | Min_Gnt Register                        | Hardwired – 0x01              |

| 0x3F              | Max_Lat Register                        | Hardwired – 0x0A              |

| 0xDB-0x40         | _ 0                                     | Unimplemented                 |

| 0xDC              | Capability ID                           | Hardwired – 0x01              |

| 0xDD              | Next_Cap_Ptr                            | Hardwired – 0x00              |

| 0xDF-0xDE         | Power Management Cap                    | Hardwired – 0x1321            |

| 0xE1-0xE0         | Power Mgmt. Ctrl/Stat                   | Reset to 0                    |

| 0xE2              | Power Mgmt. Bridge                      | Hardwired to 0                |

| 0xE3              | Power Mgmt. Data                        | Hardwired to 0                |

| 0xFF-0xE4         | Configuration Space                     |                               |

# **Configuration Space Notes**

(a) Command Register Bits:

15-10

| , | Command Register Dits.    |                               |

|---|---------------------------|-------------------------------|

|   | 0 – I/O Space Enable      | Hardwired to 0, All Accesses  |

|   |                           | Are via Memory Space          |

|   | 1 – Memory Space Enable   | Reset to 0                    |

|   | 2 – Bus Master Enable     | Reset to 0                    |

|   | 3 – Special Cycle Enable  | Hardwired to 0                |

|   | 4 – MWI Enable            | Unimplemented, Hardwired to 0 |

|   | 5 – VGA Palette Snoop     | Unimplemented, Hardwired to 0 |

|   | 6 - Parity Error Response | Reset to 0                    |

|   | 7 – Address/Data Stepping | Hardwired to 0                |

|   | 8 – SERR# Enable          | Reset to 0                    |

|   | 9 - Fast Back-to-Back     | Reset to 0                    |

| (b) Statu | Register | Bits: |

|-----------|----------|-------|

|-----------|----------|-------|

| 3–0                          | Hardwired to 0           |

|------------------------------|--------------------------|

| 4 – Capabilities List        | Hardwired to 1           |

| 5 – 66 MHz Capable           | Hardwired to 0           |

| 6 - UDF Supported            | Hardwired to 0           |

| 7 – Fast B2B Capable         | Hardwired to 1           |

| 8 – Data Parity Error Detect | Implemented, Reset to 0  |

| 10-9 - Devsel Timing         | Hardwired to 01 - Medium |

|                              | Speed                    |

| 11 – Signaled Target Abort   | Implemented, Reset to 0  |