SBAS558B - DECEMBER 2012-REVISED JANUARY 2013

# Dual-Channel, 14-Bit, 250-MSPS Ultralow-Power ADC with Analog Input Buffer

Check for Samples: ADS42B49

## **FEATURES**

- Maximum Sample Rate: 250 MSPS

- Ultralow Power:

- 850-mW Total Power at 250 MSPS

- Integrated Analog Input Buffer:

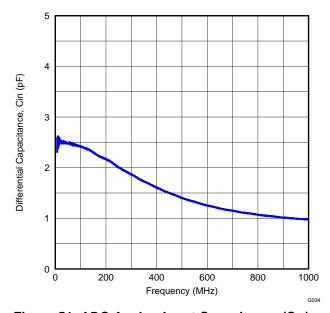

- Input Capacitance: 2.2 pF at 170 MHz

- Input Resistance: 1.1 kΩ at 170 MHz

- High Dynamic Performance:

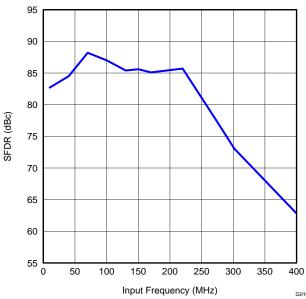

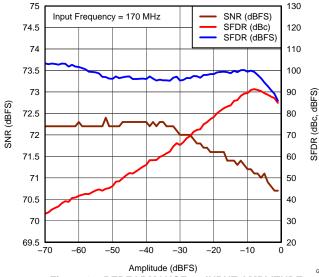

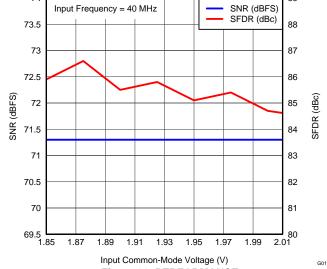

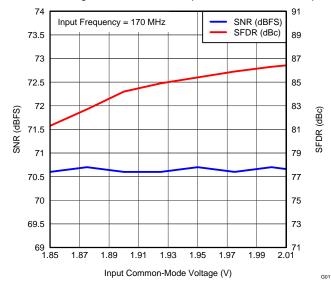

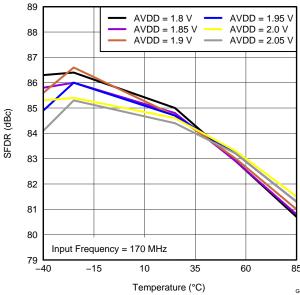

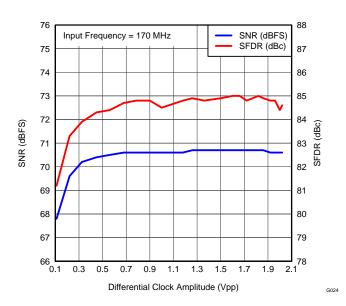

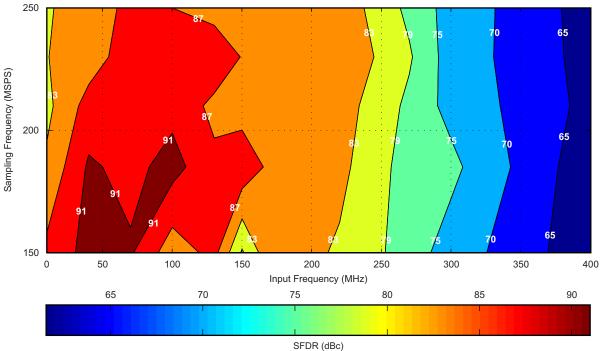

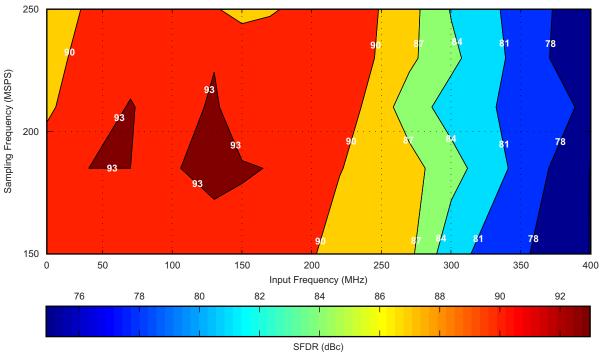

- 85-dBc SFDR at 170 MHz

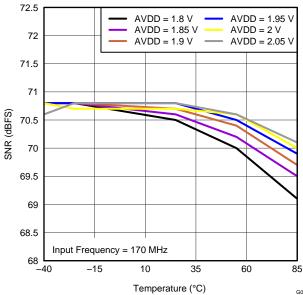

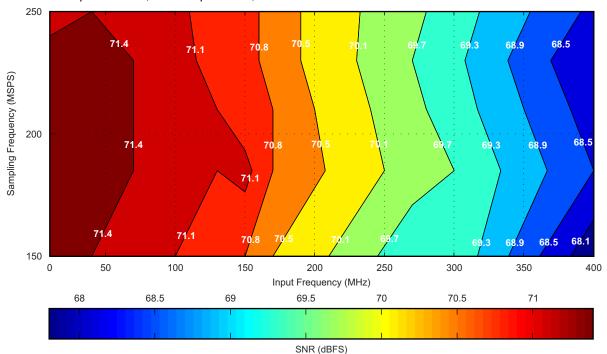

- 70.7-dBFS SNR at 170 MHz

- Crosstalk: > 85 dB at 185 MHz

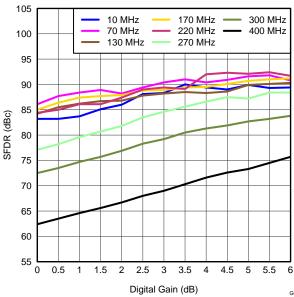

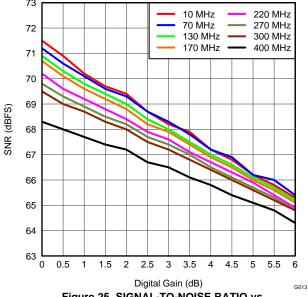

- Programmable Gain Up to 6 dB for SNR and SFDR Trade-off

- DC Offset Correction

- Output Interface Options:

- 1.8-V Parallel CMOS Interface

- Double Data Rate (DDR) LVDS with Programmable Swing:

- Standard Swing: 350 mV

- Low Swing: 200 mV

- Supports Low Input Clock Amplitude Down to 200 mV<sub>PP</sub>

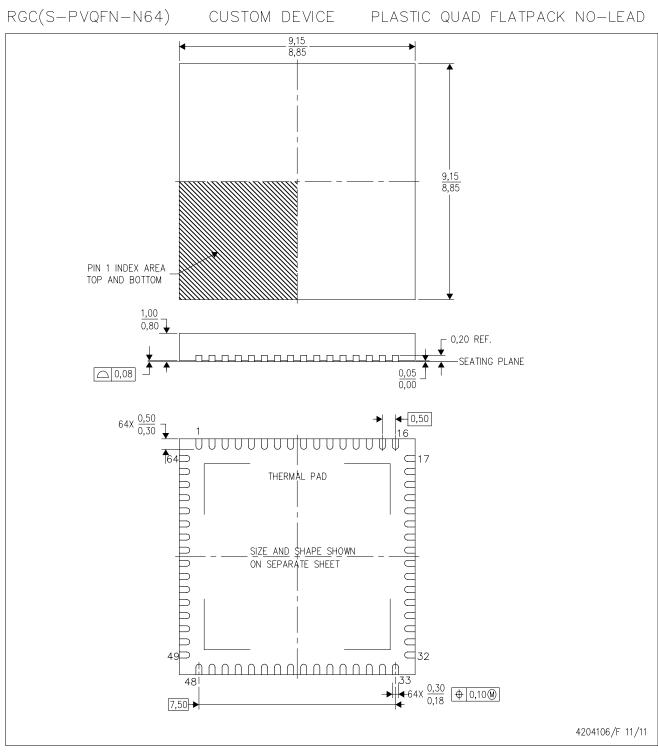

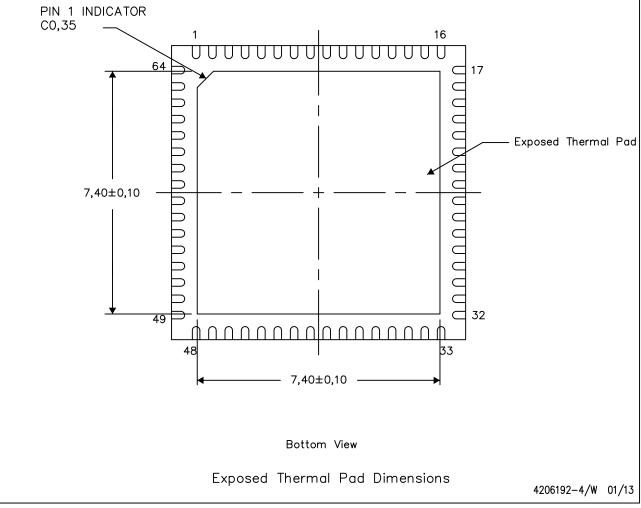

- Package: 9-mm x 9-mm, 64-Pin Quad Flat No-Lead (QFN) Package

#### **APPLICATIONS**

- Wireless Communications Infrastructure

- Software Defined Radio

- Power Amplifier Linearization

#### DESCRIPTION

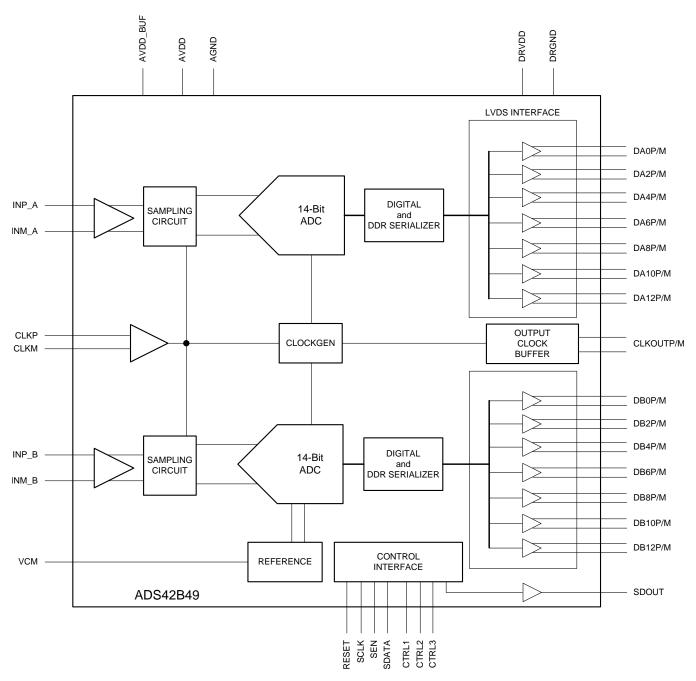

The ADS42B49 is an ultralow-power dual-channel, 14-bit analog-to-digital converter (ADC) featuring integrated analog input buffers. It uses innovative design techniques to achieve high dynamic performance, while consuming extremely low power. The presence of analog input buffers makes this device easy to drive and helps achieve high performance over a wide frequency range. The ADS42B49 is well-suited for multi-carrier, wide bandwidth communications applications.

The ADS42B49 has gain options that can be used to improve SFDR performance at lower full-scale input ranges. This device also includes a dc offset correction loop that can be used to cancel the ADC offset. Both DDR LVDS and parallel CMOS digital output interfaces are available in a compact QFN-64 PowerPAD™ package.

The device includes internal references while the traditional reference pins and associated decoupling capacitors have been eliminated. The ADS42B49 is specified over the industrial temperature range (-40°C to +85°C).

## ADS424x and ADS422x Family Comparison(1)

|                          | 65 MSPS | 125 MSPS | 160 MSPS | 250 MSPS                                            |

|--------------------------|---------|----------|----------|-----------------------------------------------------|

| ADS422x<br>12-bit family | ADS4222 | ADS4225  | ADS4226  | ADS4229                                             |

| ADS424x<br>14-bit family | ADS4242 | ADS4245  | ADS4246  | ADS4249,<br>ADS42B49 (with analog<br>input buffers) |

(1) See Table 1 for details on migrating from the ADS62P49 family.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| PRODUCT  | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | ECO PLAN <sup>(2)</sup> | LEAD AND BALL<br>FINISH | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA |

|----------|------------------|-----------------------|-----------------------------------|-------------------------|-------------------------|--------------------|--------------------|-----------------|

| ADS42B49 | QFN-64           | RGC                   | -40°C to +85°C                    | GREEN (RoHS,            | Cu/NiPdAu               | AZ42B49            | ADS42B49IRGCT      | Tape and Reel   |

| AD542B49 | QFN-64           | RGC                   | -40°C 10 +85°C                    | no Sb/Br)               | Cu/NIPdAu               | AZ42D49            | ADS42B49IRGCR      | Tape and Reel   |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

- (2) Eco Plan is the planned eco-friendly classification. Green (RoHS, no Sb/Br): TI defines *Green* to mean Pb-Free (RoHS compatible) and free of Bromine- (Br) and Antimony- (Sb) based flame retardants. Refer to the Quality and Lead-Free (Pb-Free) Data web site for more information.

The ADS42B49 is pin-compatible with the previous generation ADS62P49 data converter; this similar architecture enables easy migration. However, there are some important differences between the two device generations, summarized in Table 1.

Table 1. Migrating from the ADS62P49 and ADS4249

| ADS62P49                                               | ADS4249                                        | ADS42B49                                                                                   |

|--------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

| PINS                                                   | , , , , , , , , , , , , , , , , , , ,          | 7.55.25.3                                                                                  |

| Pin 22 is NC (not connected).<br>Must float.           | Pin 22 is AVDD (1.8 V)                         | Pin 22 is AVDD (1.9 V)                                                                     |

| Pin 34 is AVDD (3.3 V)                                 | Pin 34 is AVDD (1.8 V)                         | Pin 34 is AVDD_BUF (3.3 V)                                                                 |

| Pin 38 is DRVDD (1.8 V)                                | Pin 38 is NC. Must float.                      | Pin 38 is DRVDD (1.8 V)                                                                    |

| Pin 39 is DRGND                                        | Pin 39 is NC. Must float.                      | Pin 39 is DRGND                                                                            |

| Pin 58 is DRVDD (1.8 V)                                | Pin 58 is NC. Must float.                      | Pin 58 is DRVDD (1.8 V)                                                                    |

| Pin 59 is DRGND                                        | Pin 59 is NC. Must float.                      | Pin 59 is DRGND                                                                            |

| SUPPLY                                                 |                                                |                                                                                            |

| AVDD is 3.3 V                                          | AVDD is 1.8 V                                  | AVDD is 1.9 V                                                                              |

| DRVDD is 1.8 V                                         | DRVDD is 1.8 V                                 | DRVDD is 1.8 V                                                                             |

|                                                        |                                                | AVDD_BUF is 3.3 V                                                                          |

| INPUT COMMON-MODE VOLTAGE                              |                                                |                                                                                            |

| CM is 1.5 V                                            | CM is 0.95 V                                   | CM is 1.9 V                                                                                |

| BIASING FOR INPUT PINS (INP, IN                        | M)                                             |                                                                                            |

| INP and INM must be externally biased at 1.5 V         | NP and INM must be externally biased at 0.95 V | INP and INM do not require external biasing. Device internally biases these pins to 1.9 V. |

| EXTERNAL REFERENCE                                     |                                                |                                                                                            |

| Supported                                              | Not supported                                  | Not supported                                                                              |

| PARALLEL CONFIGURATION                                 |                                                |                                                                                            |

| SCLK pin controls internal and external reference mode | SCLK pin enables low-speed mode                | SCLK pin enables low-speed mode                                                            |

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS**(1)

|                                      |                                                 |      | VALUE                          |      |

|--------------------------------------|-------------------------------------------------|------|--------------------------------|------|

|                                      |                                                 | MIN  | MAX                            | UNIT |

|                                      | AVDD                                            | -0.3 | 2.1                            | V    |

| Supply voltage range                 | AVDD_BUF                                        | -0.3 | 3.6                            | V    |

|                                      | DRVDD                                           | -0.3 | 2.1                            | V    |

|                                      | AGND and DRGND                                  | -0.3 | 0.3                            | V    |

| Valta as hatusan                     | AVDD to DRVDD<br>(when AVDD leads DRVDD)        | -2.4 | 2.4                            | V    |

| Voltage between:                     | DRVDD to AVDD (when DRVDD leads AVDD)           | -2.4 | 2.4                            | V    |

|                                      | AVDD_BUF to DRVDD and AVDD                      | -3.9 | 3.9                            | V    |

|                                      | INP, INM                                        | -0.3 | Minimum<br>(3, AVDD_BUF + 0.3) | V    |

| Voltage applied to                   | CLKP, CLKM <sup>(2)</sup>                       | -0.3 | AVDD + 0.3                     | V    |

|                                      | RESET, SCLK, SDATA, SEN,<br>CTRL1, CTRL2, CTRL3 | -0.3 | 3.9                            | V    |

|                                      | Operating free-air, T <sub>A</sub>              | -40  | +85                            | °C   |

| Temperature range                    | Operating junction, T <sub>J</sub>              |      | +125                           | °C   |

|                                      | Storage, T <sub>stg</sub>                       | -65  | +150                           | °C   |

| Electrostatic discharge (ESD) rating | Human body model (HBM)                          |      | 2                              | kV   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

## THERMAL INFORMATION

|                  |                                              | ADS42B49 |      |

|------------------|----------------------------------------------|----------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                | RGC      | UNIT |

|                  |                                              | 64 PINS  |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 23.9     |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 10.9     |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 4.3      | °C/W |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.1      | C/VV |

| ΨЈВ              | Junction-to-board characterization parameter | 4.4      |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.6      |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> When AVDD is turned off, TI recommends switching off the input clock (or ensuring the voltage on CLKP, CLKM is less than |0.3 V|). This configuration prevents the ESD protection diodes at the clock input pins from turning on.

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range, unless otherwise noted.

|                   | PARAMET                                  | ΓER                                                     | MIN  | NOM      | MAX  | UNIT     |

|-------------------|------------------------------------------|---------------------------------------------------------|------|----------|------|----------|

| SUPPLIES          |                                          |                                                         |      |          |      |          |

| AVDD              | Analog supply voltage                    |                                                         | 1.8  | 1.9      | 2    | V        |

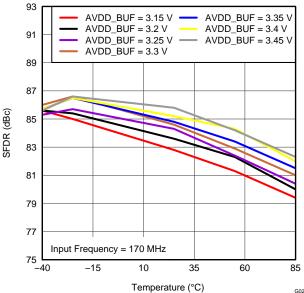

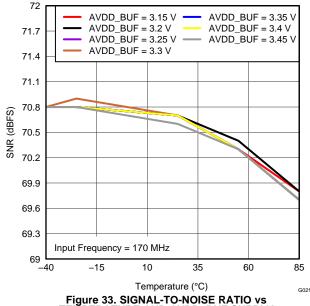

| AVDD_BUF          | Analog buffer supply voltage             |                                                         | 3.15 | 3.3      | 3.45 | V        |

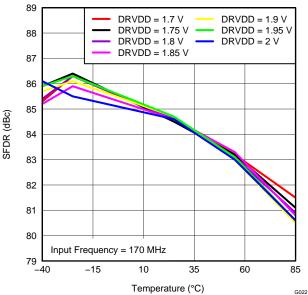

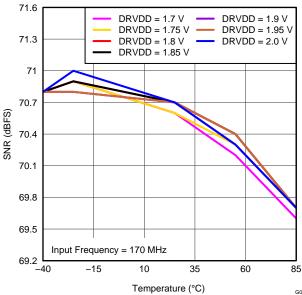

| DRVDD             | Digital supply voltage                   |                                                         | 1.7  | 1.8      | 2    | V        |

| ANALOG INPL       | JTS                                      |                                                         |      |          |      |          |

| V <sub>ID</sub>   | Differential input voltage range         |                                                         |      | 2        |      | $V_{PP}$ |

| V <sub>ICR</sub>  | Input common-mode voltage                |                                                         | VCN  | l ± 0.05 |      | V        |

|                   | Maximum analog input frequency v         | with 2-V <sub>PP</sub> input amplitude <sup>(1)</sup>   |      | 400      |      | MHz      |

|                   | Maximum analog input frequency v         | with 1.6-V <sub>PP</sub> input amplitude <sup>(1)</sup> |      | 500      |      | MHz      |

| CLOCK INPUT       | Г                                        |                                                         |      |          | ,    |          |

| Input clock sa    | imple rate                               |                                                         |      |          |      |          |

|                   | Low-speed mode enabled <sup>(2)</sup>    |                                                         | 1    |          | 80   | MSPS     |

|                   | Low-speed mode disabled (2) (by de       | efault after reset)                                     | 80   |          | 250  | MSPS     |

|                   |                                          | Sine wave, ac-coupled                                   | 0.2  | 1.5      |      | $V_{PP}$ |

|                   | Input clock amplitude differential       | LVPECL, ac-coupled                                      |      | 1.6      |      | $V_{PP}$ |

|                   | (V <sub>CLKP</sub> – V <sub>CLKM</sub> ) | LVDS, ac-coupled                                        |      | 0.7      |      | $V_{PP}$ |

|                   |                                          | LVCMOS, single-ended, ac-coupled                        |      | 1.5      |      | V        |

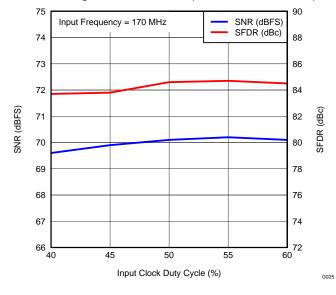

| Input clock du    | ıty cycle                                |                                                         |      |          | ,    |          |

|                   | Low-speed mode disabled                  |                                                         | 45   | 50       | 55   | %        |

|                   | Low-speed mode enabled                   |                                                         | 40   | 50       | 60   | %        |

| DIGITAL OUT       | PUTS                                     |                                                         |      |          |      |          |

| C <sub>LOAD</sub> | Maximum external load capacitano         | e from each output pin to DRGND                         |      | 3.3      |      | pF       |

| R <sub>LOAD</sub> | Differential load resistance betwee      | n the LVDS output pairs (LVDS mode)                     |      | 100      |      | Ω        |

| T <sub>A</sub>    | Operating free-air temperature           |                                                         | -40  |          | +85  | °C       |

<sup>(1)</sup> See the Analog Input section in the Application Information.

## HIGH-PERFORMANCE MODES (1)(2)

| PARAMETER              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| High-performance modes | Set the HIGH PERF MODE[0] to improve SNR in CMOS mode by approximately 0.5 dB at 170 MHz.  Register Address = 03h, data = 02h  Set the HIGH PERF MODE[1:11] bits to obtain best performance across input signal frequencies.  Register Address = 06h, data = 06h  Register Address = BAh, data = 08h  Register Address = D5h, data = 20h  Register Address = D9h, data = 22h  Register Address = DBh, data = E0h  Register Address = DCh, data = 22h |  |  |  |  |  |  |

<sup>(1)</sup> TI recommends using these modes to obtain best performance.

<sup>(2)</sup> See the Serial Interface Configuration section for details on programming the low-speed mode.

<sup>(2)</sup> See the Serial Interface Configuration section for details on register programming.

## **ELECTRICAL CHARACTERISTICS: ADS42B49 (250 MSPS)**

Typical values are at +25°C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, -1-dBFS differential analog input, LVDS interface, and 0-dB gain, unless otherwise noted. Minimum and maximum values are across the full temperature range:

$T_{MIN} = -40$  °C to  $T_{MAX} = +85$  °C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, and DRVDD = 1.8 V.

|                                         | PARAMETER                            | TEST CONDITIONS                                                         | MIN | TYP  | MAX | UNIT |

|-----------------------------------------|--------------------------------------|-------------------------------------------------------------------------|-----|------|-----|------|

|                                         | Resolution                           |                                                                         |     |      | 14  | Bits |

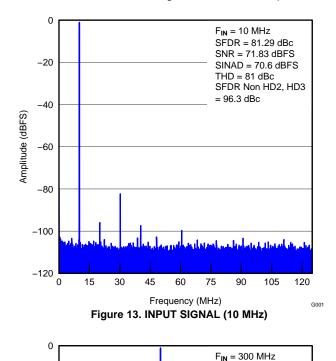

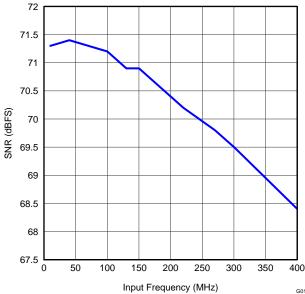

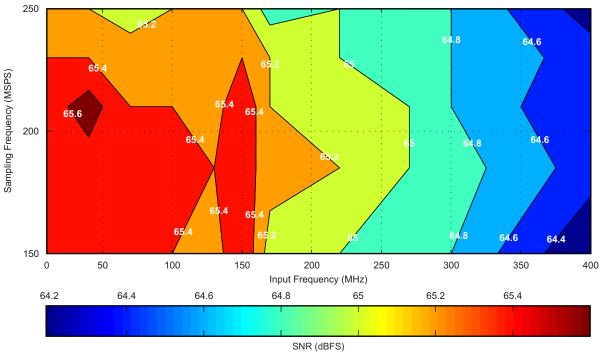

|                                         |                                      | $f_{IN} = 10 \text{ MHz}$                                               |     | 71.3 |     | dBFS |

|                                         |                                      | $f_{IN} = 70 \text{ MHz}$                                               |     | 71.2 |     | dBFS |

| SNR                                     | Signal-to-noise ratio                | f <sub>IN</sub> = 100 MHz                                               |     | 71.1 |     | dBFS |

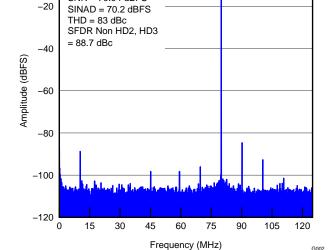

| SINIX                                   | Signal-to-hoise ratio                | $f_{IN}$ = 170 MHz, 0-dB gain                                           | 68  | 70.7 |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    |     | 67.8 |     | dBFS |

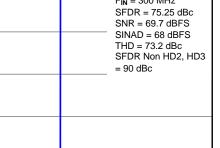

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 69.5 |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 71   |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 70 MHz                                                |     | 71   |     | dBFS |

|                                         | Signal-to-noise and                  | f <sub>IN</sub> = 100 MHz                                               |     | 70.9 |     | dBFS |

| SINAD                                   | distortion ratio                     | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 67  | 70.4 |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    |     | 67.7 |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 67.7 |     | dBFS |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 83   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 70 MHz                                                |     | 87   |     | dBc  |

|                                         | Spurious-free dynamic                | f <sub>IN</sub> = 100 MHz                                               |     | 86   |     | dBc  |

| SFDR                                    | range                                | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 73  | 85   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    |     | 89   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 73   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 82   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 70 MHz                                                |     | 84   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 100 MHz                                               |     | 85   |     | dBc  |

| ΓHD                                     | Total harmonic distortion            | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 70  | 83   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    | 70  | 86   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 72   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 95   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 70 MHz                                                |     | 93   |     | dBc  |

|                                         | 0 11 1                               | f <sub>IN</sub> = 100 MHz                                               |     | 98   |     | dBc  |

| HD2                                     | Second-harmonic distortion           | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 73  | 89   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    | 73  | 94   |     | dBc  |

|                                         |                                      |                                                                         |     | 80   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     |      |     |      |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 83   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 70 MHz                                                |     | 87   |     | dBc  |

| HD3                                     | Third-harmonic distortion            | f <sub>IN</sub> = 100 MHz                                               | 70  | 86   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 73  | 85   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    |     | 89   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 73   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 10 MHz                                                |     | 100  |     | dBc  |

|                                         | Worst and                            | f <sub>IN</sub> = 70 MHz                                                |     | 100  |     | dBc  |

|                                         | Worst spur<br>(other than second and | f <sub>IN</sub> = 100 MHz                                               |     | 100  |     | dBc  |

|                                         | third harmonics)                     | f <sub>IN</sub> = 170 MHz, 0-dB gain                                    | 84  | 95   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 170 MHz, 3-dB gain                                    |     | 97   |     | dBc  |

|                                         |                                      | f <sub>IN</sub> = 300 MHz                                               |     | 94   |     | dBc  |

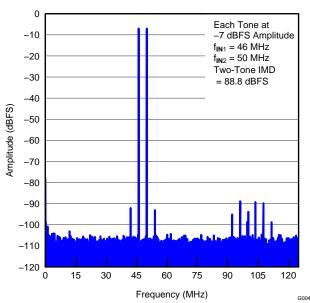

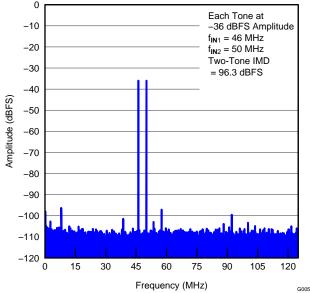

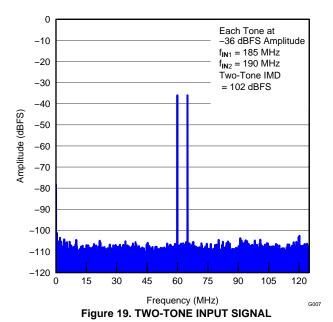

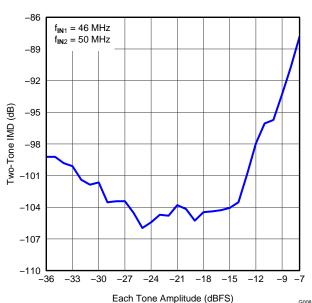

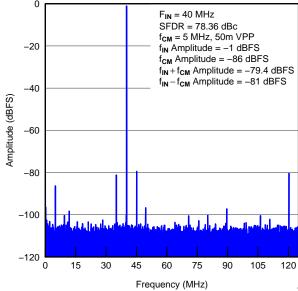

| MD                                      | Two-tone intermodulation             | $f_1$ = 46 MHz, $f_2$ = 50 MHz,<br>each tone at –7 dBFS                 |     | 88   |     | dBFS |

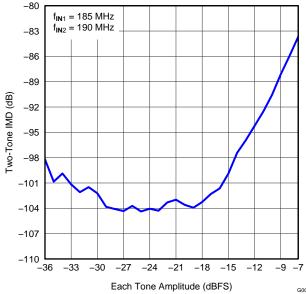

| MD I wo-tone intermodulation distortion |                                      | $f_1 = 185 \text{ MHz}, f_2 = 190 \text{ MHz},$<br>each tone at -7 dBFS |     | 83   |     | dBFS |

Copyright © 2012–2013, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS: ADS42B49 (250 MSPS) (continued)**

Typical values are at +25°C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, -1-dBFS differential analog input, LVDS interface, and 0-dB gain, unless otherwise noted. Minimum and maximum values are across the full temperature range:

$T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, and DRVDD = 1.8 V.

|      | PARAMETER                       | TEST CONDITIONS                                                                                      | MIN | TYP  | MAX | UNIT        |

|------|---------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|-------------|

|      | Crosstalk                       | 10-MHz full-scale signal on channel under observation;<br>170-MHz full-scale signal on other channel |     | > 85 |     | dB          |

|      | Input overload recovery         | Recovery to within 1% (of full-scale) for 6-dB overload with sine-wave input                         |     | 1    |     | Clock cycle |

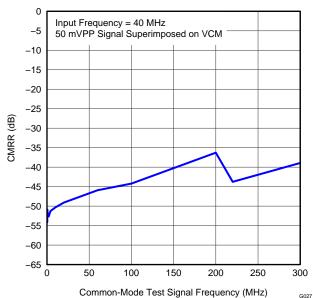

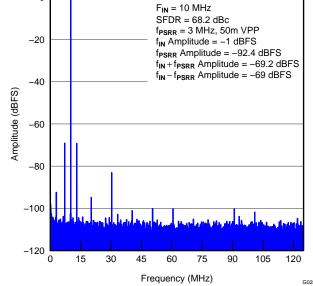

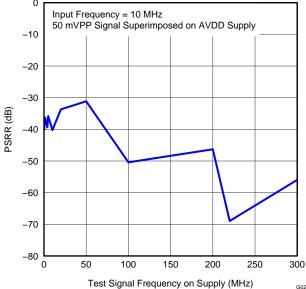

| PSRR | AC power-supply rejection ratio | For 50-mV <sub>PP</sub> signal on AVDD supply                                                        |     | 30   |     | dB          |

| ENOB | Effective number of bits        | f <sub>IN</sub> = 170 MHz                                                                            |     | 11.4 |     | LSBs        |

### **ELECTRICAL CHARACTERISTICS: GENERAL**

Typical values are at +25°C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, and -1-dBFS differential analog input, unless otherwise noted. Minimum and maximum values are across the full temperature range:  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, and DRVDD = 1.8 V.

|                    |                                                       | PARAMETER                                                                                               | MIN | TYP                | MAX | UNIT            |

|--------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-----------------|

| ANALOG INPU        | JTS                                                   |                                                                                                         |     |                    | '   |                 |

| V <sub>ID</sub>    | Differential input voltage range                      |                                                                                                         |     | 2                  |     | V <sub>PP</sub> |

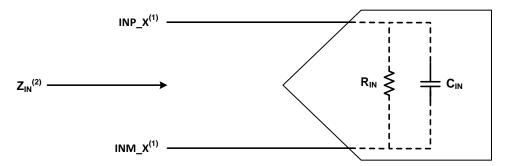

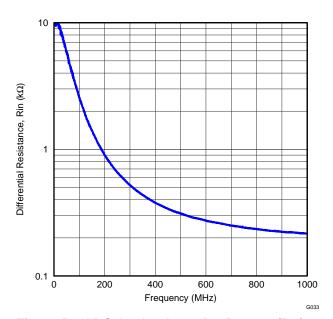

|                    | Differential input resistance (at                     | 170 MHz)                                                                                                |     | 1.2                |     | kΩ              |

|                    | Differential input capacitance (a                     | at 170 MHz)                                                                                             |     | 2.2                |     | pF              |

|                    | Analog input bandwidth (with 50-Ω source impedance, a | Analog input bandwidth (with $50-\Omega$ source impedance, and $50-\Omega$ termination)                 |     |                    |     | MHz             |

| VCM                | Common-mode output voltage                            |                                                                                                         |     | 1.9 <sup>(1)</sup> |     | V               |

|                    | VCM output current capability                         |                                                                                                         |     | 10                 |     | mA              |

| DC ACCURAC         | Y                                                     |                                                                                                         |     |                    | '   |                 |

|                    | Offset error                                          |                                                                                                         | -20 | 3                  | 20  | mV              |

| E <sub>GREF</sub>  | Gain error as a result of interna                     | Il reference inaccuracy alone                                                                           | -2  |                    | 2   | %FS             |

| E <sub>GCHAN</sub> | Gain error of channel alone                           |                                                                                                         |     | -5                 |     | %FS             |

|                    | Temperature coefficient of E <sub>GCI</sub>           | HAN                                                                                                     |     | 0.005              |     | Δ%/°C           |

| POWER SUPP         | LY                                                    |                                                                                                         |     |                    | •   |                 |

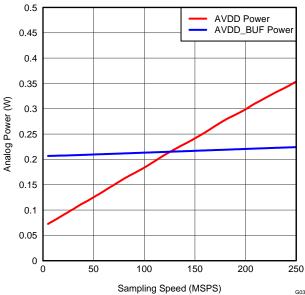

| IAVDD              | Analog supply current                                 |                                                                                                         |     | 186                | 225 | mA              |

| IAVDD_BUF          | Analog buffer supply current                          |                                                                                                         |     | 67                 | 90  | mA              |

| IDRVDD             | O. to . t b. #                                        | LVDS interface, 350-mV swing with 100- $\Omega$ external termination, $f_{\text{IN}} = 2.5 \text{ MHz}$ |     | 151                | 180 | mA              |

| IDRVDD             | Output buffer supply current                          | CMOS interface, 8-pF external load capacitance, $f_{\text{IN}} = 2.5 \text{ MHz}^{(2)}$                 |     | 128                |     | mA              |

|                    | Analog power                                          |                                                                                                         |     | 353                |     | mW              |

|                    | Analog buffer power                                   |                                                                                                         |     | 224                |     | mW              |

|                    | Digital power, LVDS interface,                        | 350-mV swing with 100-Ω external termination, $f_{IN} = 2.5 \text{ MHz}$                                |     | 272                |     | mW              |

|                    | Digital power, CMOS interface,                        | 8-pF external load capacitance, (2) f <sub>IN</sub> = 2.5 MHz                                           |     | 230                |     | mW              |

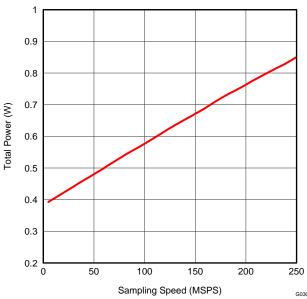

|                    | Total power, LVDS interface, 3                        | 50-mV swing with 100-Ω external termination, f <sub>IN</sub> = 2.5 MHz                                  |     | 850                | 925 | mW              |

|                    | Global power-down                                     |                                                                                                         |     |                    | 20  | mW              |

<sup>(1)</sup> After the HIGH PERF MODE[10:0] bits are set.

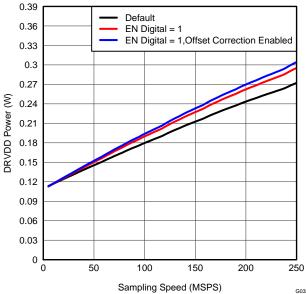

<sup>(2)</sup> In CMOS mode, the DRVDD current scales with the sampling frequency, the load capacitance on output pins, input frequency, and the supply voltage (see the CMOS Interface Power Dissipation section in the Application Information).

www.ti.com

#### **DIGITAL CHARACTERISTICS**

At AVDD = 1.9 V, AVDD\_BUF = 3.3 V, and DRVDD = 1.8 V, unless otherwise noted. DC specifications refer to the condition where the digital outputs do not switch, but are permanently at a valid logic level '0' or '1'.

|                  | PARAMETE                      | R                                      | TEST CONDITIONS                    | MIN            | TYP   | MAX  | UNIT |

|------------------|-------------------------------|----------------------------------------|------------------------------------|----------------|-------|------|------|

| DIGITAL          | INPUTS (RESET, SCLK, SDAT     | A, SEN, CTRL1, CTRL2,                  | CTRL3) <sup>(1)</sup>              |                |       |      |      |

| V <sub>IH</sub>  | High-level input voltage      | High-level input voltage               |                                    | 1.3            |       |      | V    |

| V <sub>IL</sub>  | Low-level input voltage       |                                        | 1.8-V and 3.3-V CMOS logic levels  |                |       | 0.4  | V    |

|                  | I link lavel in a decomposit  | SDATA, SCLK <sup>(2)</sup>             | V <sub>HIGH</sub> = 1.8 V          |                | 10    |      | μA   |

| I <sub>IH</sub>  | High-level input current      | SEN <sup>(3)</sup>                     | V <sub>HIGH</sub> = 1.8 V          |                | 0     |      | μA   |

|                  | Low level input ourrent       | SDATA, SCLK                            | V <sub>LOW</sub> = 0 V             |                | 0     |      | μA   |

| I <sub>IL</sub>  | Low-level input current       | SEN                                    | $V_{LOW} = 0 V$                    |                | 10    |      | μΑ   |

| DIGITAL          | OUTPUTS, CMOS INTERFACE       | E (DA[13:0], DB[13:0], CL              | KOUT, SDOUT)                       |                |       |      |      |

| V <sub>OH</sub>  | High-level output voltage     |                                        |                                    | DRVDD -<br>0.1 | DRVDD |      | V    |

| V <sub>OL</sub>  | Low-level output voltage      |                                        |                                    |                | 0     | 0.1  | V    |

| Co               | Output capacitance (intern    | al to device)                          |                                    |                |       |      | pF   |

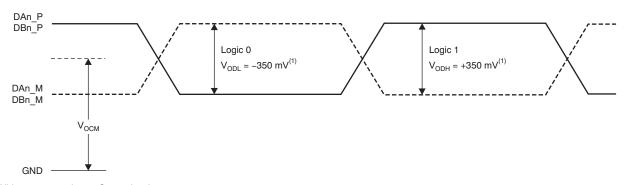

| DIGITAL          | OUTPUTS, LVDS INTERFACE       |                                        |                                    |                |       |      |      |

| V <sub>ODH</sub> | High-level output differentia | High-level output differential voltage |                                    | 275            | 350   | 425  | mV   |

| V <sub>ODL</sub> | Low-level output differentia  | al voltage                             | With an external 100-Ω termination | -425           | -350  | -275 | mV   |

| V <sub>OCM</sub> | Output common-mode volt       | age                                    |                                    | 0.9            | 1.05  | 1.25 | V    |

<sup>1)</sup> SCLK, SDATA, and SEN function as digital input pins in serial configuration mode.

Product Folder Links: ADS42B49

<sup>(2)</sup> SDATA and SCLK have an internal 150-kΩ pull-down resistor.

<sup>(3)</sup> SEN has an internal 150-kΩ pull-up resistor to AVDD. Because the pull-up resistor is weak, SEN can also be driven by 1.8-V or 3.3-V CMOS buffers.

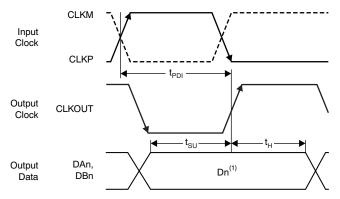

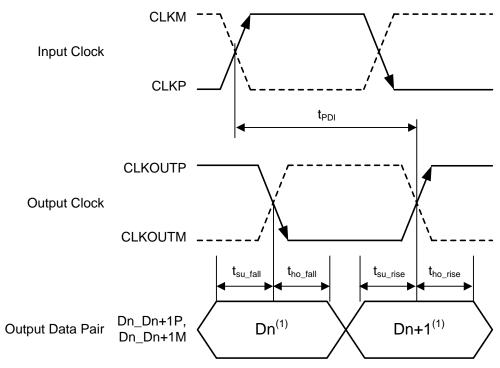

## TIMING REQUIREMENTS: LVDS and CMOS Modes

Typical values are at +25°C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, DRVDD = 1.8 V, sampling frequency = 250 MSPS, sine wave input clock,  $C_{LOAD}$  = 3.3 pF, and  $R_{LOAD}$  = 100  $\Omega$ , unless otherwise noted. Minimum and maximum values are across the full temperature range:  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C, AVDD = 1.9 V, AVDD\_BUF = 3.3 V, and DRVDD = 1.7 V to 2 V.

|                                                | PARAMETER                                         | DESCRIPTION                                                                                                                    | MIN  | TYP  | MAX  | UNIT               |

|------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

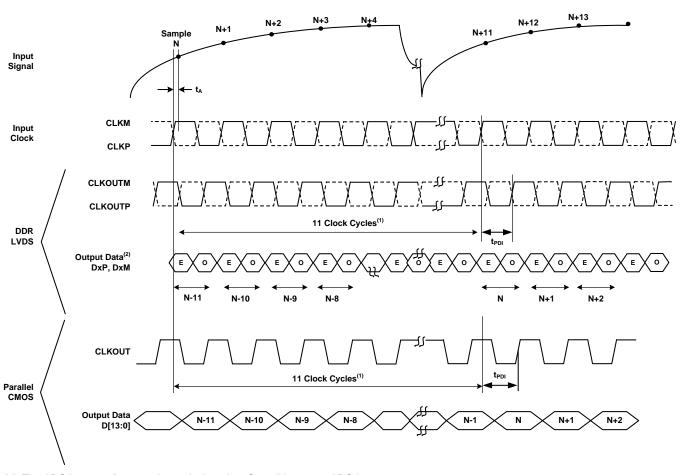

| t <sub>A</sub>                                 | Aperture delay                                    |                                                                                                                                | 0.5  | 0.8  | 1.1  | ns                 |

|                                                | Aperture delay matching                           | Between two channels of the same device                                                                                        |      | ±70  |      | ps                 |

|                                                | Variation of aperture delay                       | Between two devices at the same temperature and DRVDD supply                                                                   |      | ±150 |      | ps                 |

| t <sub>J</sub>                                 | Aperture jitter                                   |                                                                                                                                |      | 120  |      | f <sub>S</sub> rms |

|                                                | Malaun tina                                       | Time to valid data after coming out of STANDBY mode                                                                            |      | 50   |      | μs                 |

|                                                | Wakeup time                                       | Time to valid data after coming out of GLOBAL power-down mode                                                                  |      | 100  |      | μs                 |

|                                                | ADC latency <sup>(1)</sup>                        | Default latency after reset                                                                                                    |      | 11   |      | Clock cycles       |

|                                                | ,                                                 | Digital functions enabled (EN DIGITAL = 1)                                                                                     |      | 19   |      | Clock<br>cycles    |

| DDR LVI                                        | OS MODE <sup>(2)(3)</sup>                         |                                                                                                                                |      |      |      |                    |

| t <sub>SU_RISE</sub>                           | Data setup time on rising edge of CLKOUTP         | Data valid to zero-crossing of differential output clock (CLKOUTP – CLKOUTM) (4)                                               | 0.32 | 0.68 |      | ns                 |

| t <sub>HO_RISE</sub>                           | Data hold time on rising edge of CLKOUTP          | Zero-crossing of differential output clock (CLKOUTP – CLKOUTM) to data becoming invalid (4)                                    | 0.5  | 0.82 |      | ns                 |

| t <sub>SU_FALL</sub>                           | Data setup time on falling edge of CLKOUTP        | Data valid to zero-crossing of differential output clock (CLKOUTP – CLKOUTM) <sup>(4)</sup>                                    | 0.63 | 1.04 |      | ns                 |

| t <sub>HO_FALL</sub>                           | Data hold time on falling edge of CLKOUTP         | Zero-crossing of differential output clock (CLKOUTP – CLKOUTM) to data becoming invalid (4)                                    | 0.18 | 0.58 |      | ns                 |

| t <sub>PDI</sub>                               | Clock propagation delay                           | Input clock rising edge cross-over to output clock (CLKOUTP – CLKOUTM) rising edge cross-over                                  | 7.6  | 8.9  | 10.2 | ns                 |

|                                                | LVDS bit clock duty cycle                         | Duty cycle of differential clock (CLKOUTP – CLKOUTM)                                                                           |      | 57   |      | %                  |

| t <sub>FALL</sub> ,<br>t <sub>RISE</sub>       | Data fall time,<br>Data rise time                 | Rise time measured from −100 mV to +100 mV<br>1 MSPS ≤ Sampling frequency ≤ 250 MSPS                                           |      | 0.13 |      | ns                 |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | Rise time measured from −100 mV to +100 mV<br>1 MSPS ≤ Sampling frequency ≤ 250 MSPS                                           |      | 0.13 |      | ns                 |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub>       | Data rise time,<br>Data fall time                 | Rise time measured from 20% to 80% of DRVDD 1 MSPS ≤ Sampling frequency ≤ 250 MSPS                                             |      | 0.13 |      | ns                 |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | Rise time measured from 20% to 80% of DRVDD 1 MSPS ≤ Sampling frequency ≤ 250 MSPS                                             |      | 0.13 |      | ns                 |

| PARALL                                         | EL CMOS MODE                                      |                                                                                                                                |      |      |      |                    |

| t <sub>PDI</sub>                               | Clock propagation delay                           | Input clock rising edge cross-over to output clock rising edge cross-over                                                      | 5.9  | 8.3  | 10.6 | ns                 |

|                                                | Output clock duty cycle                           | Duty cycle of output clock, CLKOUT  1 MSPS ≤ Sampling frequency ≤ 200 MSPS                                                     |      | 50   |      | %                  |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub>       | Data rise time,<br>Data fall time                 | Rise time measured from 20% to 80% of DRVDD Fall time measured from 80% to 20% of DRVDD 1 MSPS ≤ Sampling frequency ≤ 200 MSPS |      | 0.7  |      | ns                 |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time<br>Output clock fall time  | Rise time measured from 20% to 80% of DRVDD Fall time measured from 80% to 20% of DRVDD 1 MSPS ≤ Sampling frequency ≤ 200 MSPS |      | 0.7  |      | ns                 |

<sup>(1)</sup> Overall latency = ADC latency + t<sub>PDI</sub>. At 250 MSPS, t<sub>PDI</sub> is greater than two clock periods. Therefore, overall latency at 250 MSPS = ADC latency + 2 clock cycles.

<sup>(2)</sup> Measurements are done with a transmission line of a 100-Ω characteristic impedance between the device and load. Setup and hold time specifications take into account the effect of jitter on the output data and clock.

<sup>(3)</sup> Setup and hold values in DDR LVDS mode are taken with a delayed output clock by writing register 42h, value 30h.

<sup>(4)</sup> Data valid refers to a logic high of +100 mV and a logic low of -100 mV.

## Table 2. LVDS Timings at Lower Sampling Frequencies (1)

|                       | SETUP TIME (ns)      |      |     |                      | HOLD TIME (ns) |                      |      |                      |     |      | CLOCK<br>PROPAGATION<br>DELAY (ns) |     |      |      |      |

|-----------------------|----------------------|------|-----|----------------------|----------------|----------------------|------|----------------------|-----|------|------------------------------------|-----|------|------|------|

| SAMPLING<br>FREQUENCY | t <sub>SU_RISE</sub> |      |     | t <sub>SU_FALL</sub> |                | t <sub>HO RISE</sub> |      | t <sub>HO FALL</sub> |     |      | t <sub>PDI</sub>                   |     |      |      |      |

| (MSPS)                | MIN                  | TYP  | MAX | MIN                  | TYP            | MAX                  | MIN  | TYP                  | MAX | MIN  | TYP                                | MAX | MIN  | TYP  | MAX  |

| 100                   | 0.36                 | 0.72 |     | 0.67                 | 1.10           |                      | 3.37 | 3.80                 |     | 3.02 | 3.48                               |     | 10.4 | 11.8 | 13.1 |

| 125                   | 0.35                 | 0.72 |     | 0.66                 | 1.08           |                      | 2.43 | 2.82                 |     | 2.09 | 2.51                               |     | 9.4  | 10.8 | 12.1 |

| 150                   | 0.35                 | 0.70 |     | 0.66                 | 1.07           |                      | 1.77 | 2.15                 |     | 1.47 | 1.86                               |     | 8.8  | 10.1 | 11.5 |

| 175                   | 0.35                 | 0.70 |     | 0.63                 | 1.07           |                      | 1.32 | 1.67                 |     | 1.00 | 1.40                               |     | 8.3  | 9.7  | 11.0 |

| 200                   | 0.38                 | 0.70 |     | 0.68                 | 1.08           |                      | 0.93 | 1.29                 |     | 0.66 | 1.04                               |     | 8.0  | 9.4  | 10.8 |

| 230                   | 0.33                 | 0.69 |     | 0.67                 | 1.06           |                      | 0.63 | 0.97                 |     | 0.35 | 0.74                               |     | 7.7  | 9.1  | 10.5 |

<sup>(1)</sup> Setup and hold values in DDR LVDS mode belong to delayed output clock by writing register 42h, value 30h.

## **Table 3. CMOS Timings at Lower Sampling Frequencies**

| SAMPLING<br>FREQUENCY |      | UP TIME <sup>(1)</sup><br>t <sub>SU</sub> , ns) |     |      | LD TIME <sup>(1)</sup><br>t <sub>HO</sub> , ns) |     | CLOCK PROPAGATION DELAY (t <sub>PDI</sub> , ns) |      |      |

|-----------------------|------|-------------------------------------------------|-----|------|-------------------------------------------------|-----|-------------------------------------------------|------|------|

| (MSPS)                | MIN  | TYP                                             | MAX | MIN  | TYP                                             | MAX | MIN                                             | TYP  | MAX  |

| 100                   | 3.91 | 4.40                                            |     | 3.68 | 4.18                                            |     | 9.5                                             | 11.5 | 13.3 |

| 125                   | 2.81 | 3.40                                            |     | 2.73 | 3.14                                            |     | 8.5                                             | 10.5 | 12.3 |

| 150                   | 2.00 | 2.64                                            |     | 2.09 | 2.52                                            |     | 7.9                                             | 9.9  | 11.7 |

| 175                   | 1.43 | 2.14                                            |     | 1.67 | 2.06                                            |     | 7.6                                             | 9.4  | 11.4 |

| 200                   | 1.01 | 1.76                                            |     | 1.25 | 1.68                                            |     | 6.4                                             | 8.9  | 11.1 |

<sup>(1)</sup> In CMOS mode, setup time is measured from the beginning of data valid to the mid-point of the CLKOUT rising edge, whereas hold time is measured from the mid-point of the CLKOUT rising edge to data becoming invalid.

Product Folder Links: ADS42B49

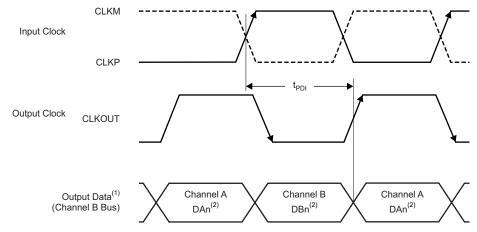

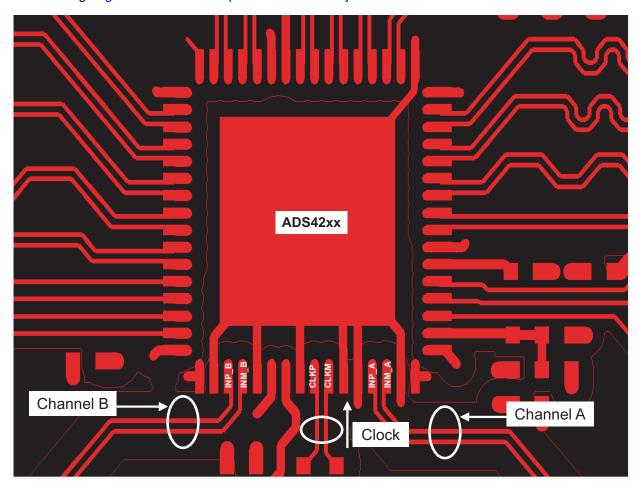

### PARAMETER MEASUREMENT INFORMATION

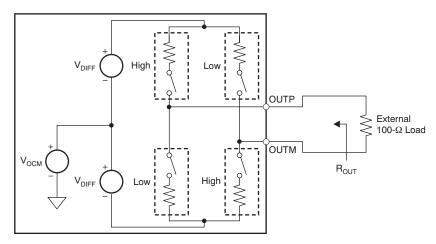

(1) With an external  $100-\Omega$  termination.

Figure 1. LVDS Output Voltage Levels

- (1) The ADC latency after reset is 11 clock cycles. Overall latency = ADC latency +  $t_{PDI}$ .

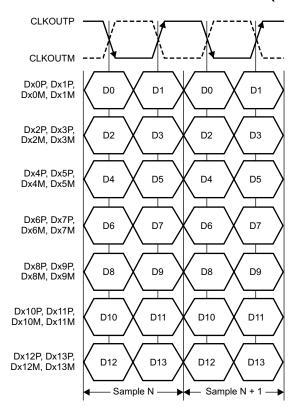

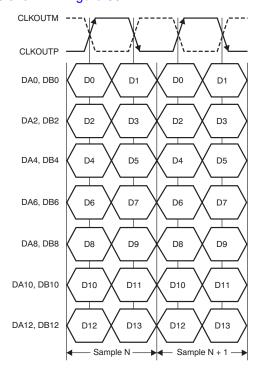

- (2) E = even bits (D0, D2, D4, and so forth); O = odd bits (D1, D3, D5, and so forth).

Figure 2. Latency Timing Diagram

## PARAMETER MEASUREMENT INFORMATION (continued)

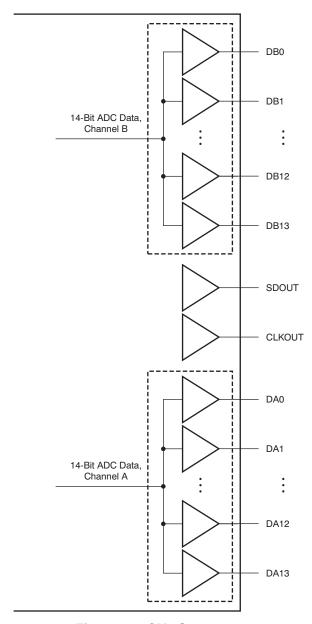

(1) Dn = bits D0, D1, D2, and so forth of channels A and B.

Figure 3. CMOS Interface Timing Diagram

(1) Dn = D0, D2, D4, and so forth. Dn+1 = D1, D3, D5, and so forth.

Figure 4. LVDS Interface Timing Diagram

## PARAMETER MEASUREMENT INFORMATION (continued)

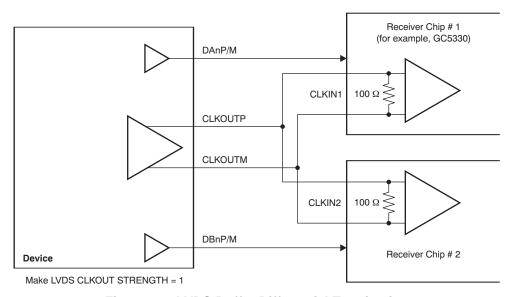

Figure 5. LVDS Bit Order

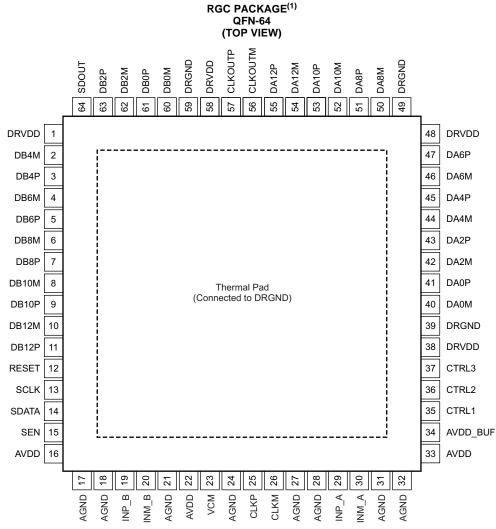

## PIN CONFIGURATION: LVDS MODE

(1) The PowerPAD is connected to DRGND.

Figure 6. LVDS Mode

#### **PIN DESCRIPTIONS: LVDS Mode**

| PIN NAME | PIN NUMBER                        | # OF PINS | FUNCTION | DESCRIPTION                                                                            |  |  |  |  |

|----------|-----------------------------------|-----------|----------|----------------------------------------------------------------------------------------|--|--|--|--|

| AGND     | 17, 18, 21, 24, 27, 28,<br>31, 32 | 8         | Input    | Analog ground                                                                          |  |  |  |  |

| AVDD     | 16, 22, 33                        | 3         | Input    | Analog power supply                                                                    |  |  |  |  |

| AVDD_BUF | 34                                | 1         | Input    | Analog buffer supply                                                                   |  |  |  |  |

| CLKM     | 26                                | 1         | Input    | Differential clock negative input                                                      |  |  |  |  |

| CLKP     | 25                                | 1         | Input    | Differential clock positive input                                                      |  |  |  |  |

| CLKOUTM  | 56                                | 1         | Output   | Differential output clock, complement                                                  |  |  |  |  |

| CLKOUTP  | 57                                | 1         | Output   | Differential output clock, true                                                        |  |  |  |  |

| CTRL1    | 35                                | 1         | Input    | Digital control input pins. Together, these pins control the various power-down modes. |  |  |  |  |

| CTRL2    | 36                                | 1         | Input    | Digital control input pins. Together, these pins control the various power-down modes. |  |  |  |  |

| CTRL3    | 37                                | 1         | Input    | Digital control input pins. Together, these pins control the various power-down modes. |  |  |  |  |

|          |                                   |           |          |                                                                                        |  |  |  |  |

Copyright © 2012–2013, Texas Instruments Incorporated

## PIN DESCRIPTIONS: LVDS Mode (continued)

| The besonit flows. Evbs mode (continued) |                   |           |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------------------------------|-------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN NAME                                 | PIN NUMBER        | # OF PINS | FUNCTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| DA0P, DA0M                               | Refer to Figure 6 | 2         | Output   | Channel A differential output data pair, D0 and D1 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| DA2P, DA2M                               | Refer to Figure 6 | 2         | Output   | Channel A differential output data D2 and D3 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DA4P, DA4M                               | Refer to Figure 6 | 2         | Output   | Channel A differential output data D4 and D5 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DA6P, DA6M                               | Refer to Figure 6 | 2         | Output   | Channel A differential output data D6 and D7 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DA8P, DA8M                               | Refer to Figure 6 | 2         | Output   | Channel A differential output data D8 and D9 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DA10P,<br>DA10M                          | Refer to Figure 6 | 2         | Output   | Channel A differential output data D10 and D11 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DA12P,<br>DA12M                          | Refer to Figure 6 | 2         | Output   | Channel A differential output data D12 and D13 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DB0P, DB0M                               | Refer to Figure 6 | 2         | Output   | Channel B differential output data pair, D0 and D1 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| DB2P, DB2M                               | Refer to Figure 6 | 2         | Output   | Channel B differential output data D2 and D3 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DB4P, DB4M                               | Refer to Figure 6 | 2         | Output   | Channel B differential output data D4 and D5 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DB6P, DB6M                               | Refer to Figure 6 | 2         | Output   | Channel B differential output data D6 and D7 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DB8P, DB8M                               | Refer to Figure 6 | 2         | Output   | Channel B differential output data D8 and D9 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DB10P,<br>DB10M                          | Refer to Figure 6 | 2         | Output   | Channel B differential output data D10 and D11 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DB12P,<br>DB12M                          | Refer to Figure 6 | 2         | Output   | Channel B differential output data D12 and D13 multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| DRGND                                    | 39, 49, 59, PAD   | 4         | Input    | Output buffer ground, should be shorted on-board to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DRVDD                                    | 1, 38, 48, 58     | 4         | Input    | Output buffer supply                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| INM_A                                    | 30                | 1         | Input    | Differential analog negative input, channel A                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| INP_A                                    | 29                | 1         | Input    | Differential analog positive input, channel A                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| INM_B                                    | 20                | 1         | Input    | Differential analog negative input, channel B                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| INP_B                                    | 19                | 1         | Input    | Differential analog positive input, channel B                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

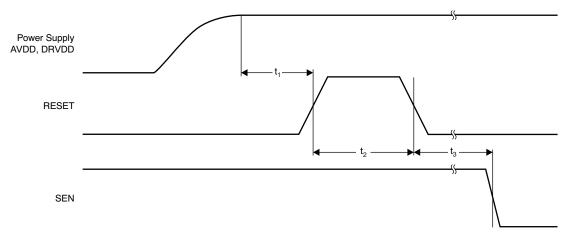

| RESET                                    | 12                | 1         | Input    | Serial interface RESET input. When using the serial interface mode, the internal registers must be initialized through a hardware RESET by applying a high pulse on this pin or by using the software reset option; refer to the <i>Serial Interface Configuration</i> section. In parallel interface mode, the RESET pin must be permanently tied high. SCLK and SEN are used as parallel control pins in this mode. This pin has an internal 150-k $\Omega$ pull-down resistor. |  |  |  |  |

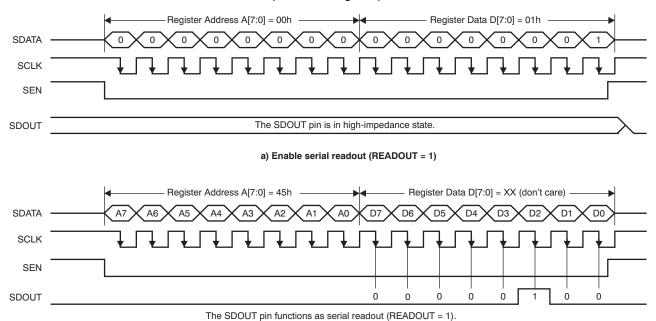

| SCLK                                     | 13                | 1         | Input    | This pin functions as a serial interface clock input when RESET is low. SCLK controls the low-speed mode selection when RESET is tied high; see Table 5 for detailed information. This pin has an internal 150-k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                     |  |  |  |  |

| SDATA                                    | 14                | 1         | Input    | Serial interface data input; this pin has an internal 150-kΩ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SDOUT                                    | 64                | 1         | Output   | This pin functions as a serial interface register readout when the READOUT bit is enabled. When READOUT = 0, this pin is in high-impedance state.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SEN                                      | 15                | 1         | Input    | This pin functions as a serial interface enable input when RESET is low. SEN controls the output interface and data format selection when RESET is tied high; see Table 6 for detailed information. This pin has an internal 150-k $\Omega$ pull-up resistor to AVDD.                                                                                                                                                                                                             |  |  |  |  |

| VCM                                      | 23                | 1         | Output   | This pin outputs the common-mode voltage (1.9 V) that can be used externally to bias the analog input pins                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

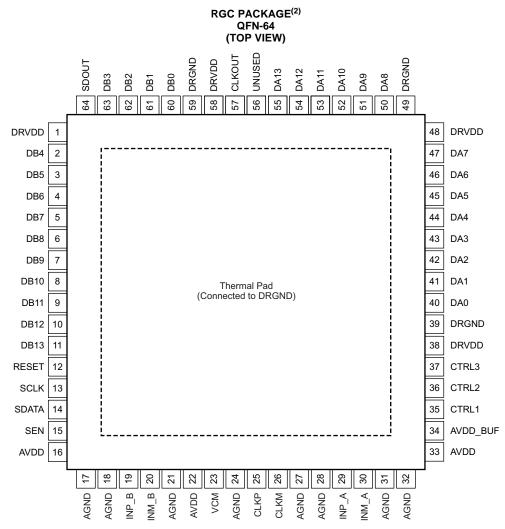

### **PIN CONFIGURATION: CMOS MODE**

(2) The PowerPAD is connected to DRGND.

Figure 7. CMOS Mode

## PIN DESCRIPTIONS: CMOS Mode

| PIN NAME    | PIN NUMBER                        | # OF<br>PINS | FUNCTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----------------------------------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND        | 17, 18, 21, 24, 27,<br>28, 31, 32 | 8            | Input    | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AVDD        | 16, 22, 33                        | 3            | Input    | Analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AVDD_BUF    | 34                                | 1            | Input    | Analog buffer supply                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLKM        | 26                                | 1            | Input    | Differential clock negative input                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLKP        | 25                                | 1            | Input    | Differential clock positive input                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLKOUT      | 57                                | 1            | Output   | CMOS output clock                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

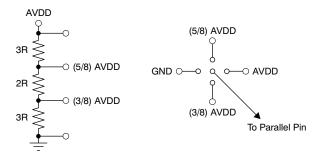

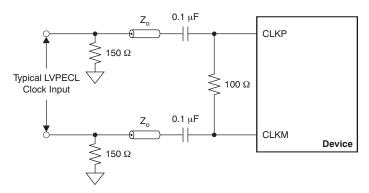

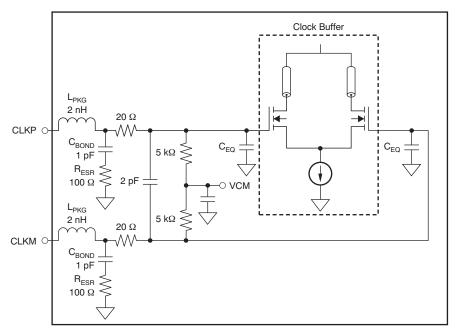

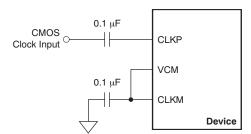

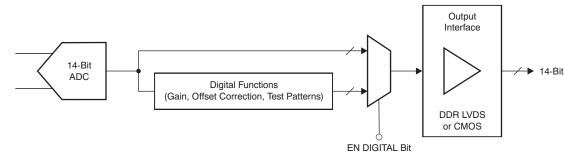

| CTRL1       | 35                                | 1            | Input    | Digital control input pins. Together, these pins control various power-down modes.                                                                                                                                                                                                                                                                                                                                                                                     |