www.ti.com

SBOS442C -JUNE 2008-REVISED OCTOBER 2011

# FULLY-INTEGRATED, 8-CHANNEL ANALOG FRONT-END FOR ULTRASOUND 0.89nV/\(\sqrt{Hz}\), 12-Bit, 40MSPS, 101mW/Channel

Check for Samples: AFE5804

#### **FEATURES**

- 8-Channel Complete Analog Front-End:

- LNA, VCA, PGA, LPF, and ADC

- Mode Control for Power/Noise Optimization:

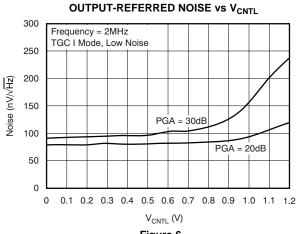

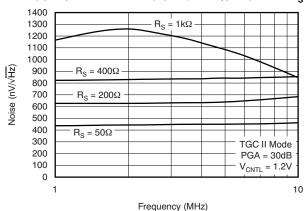

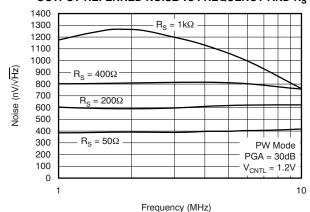

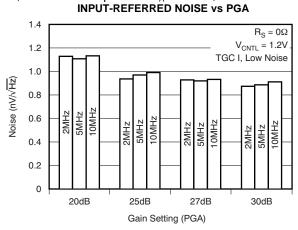

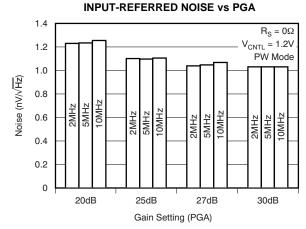

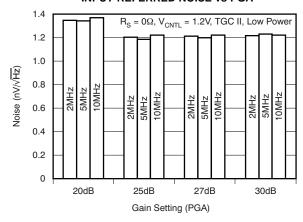

- Low Noise (Full-Channel): 0.89nV/√Hz (TGC Mode I) 1.23nV/√Hz (TGC Mode II) 1.03nV/√Hz (PW Mode)

- Ultra-Low Power:

101mW/Channel (TGC Mode II)

65mW/Channel (CW Mode)

- Low-Noise Pre-Amp (LNA):

- 0.75nV/√Hz

- 20dB Fixed Gain

- 280mV<sub>PP</sub> Linear Input Range

- Variable-Gain Amplifier:

- Gain Control Range: 46dB

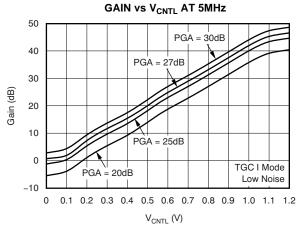

- PGA Gain Settings: 20dB, 25dB, 27dB, 30dB

- Low-Pass Filter:

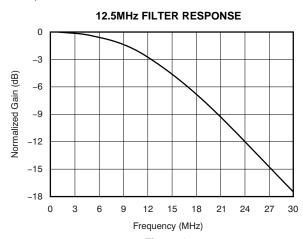

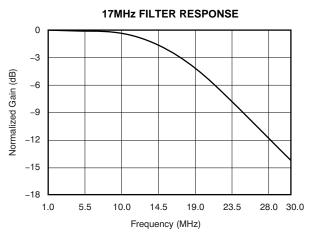

- Selectable BW: 12.5MHz, 17MHz

- 2nd-Order, Bessel

- Gain Error: ±0.5dB

- Channel Matching: ±0.25dB

- Clamping

- Fast Overload Recovery: Two Clock Cycles

- 12-Bit Analog-to-Digital Converter:

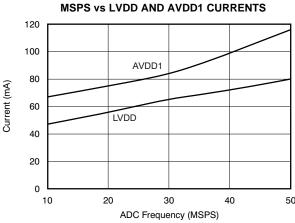

- 10MSPS to 50MSPS

- 69dB SNR at 10MHz

- Serial LVDS Interface

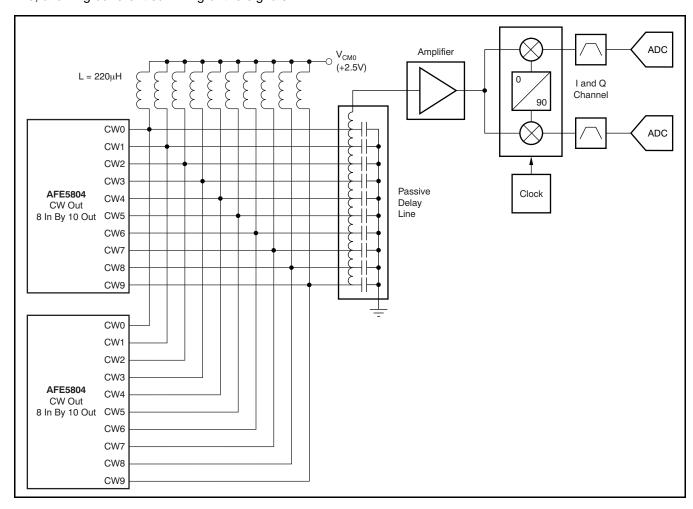

- Integrated CW Switch Matrix

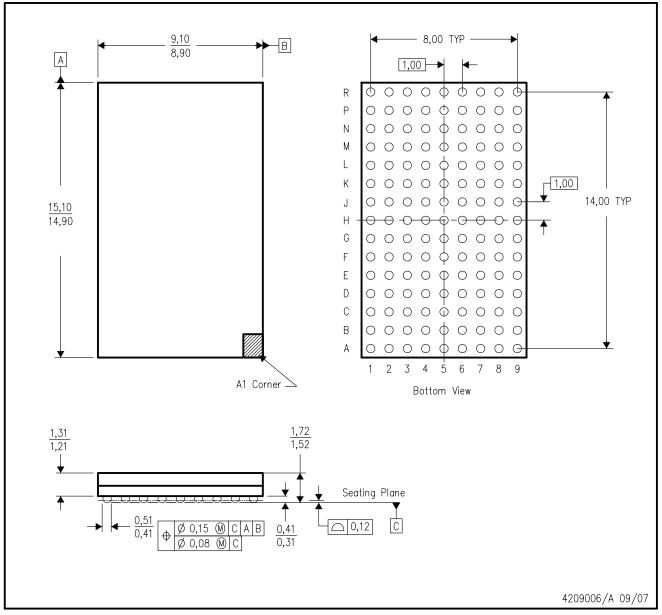

- 15mm × 9mm, 135-BGA Package:

- Pb-Free (RoHS-Compliant) and Green

#### **APPLICATIONS**

- Medical Imaging, Ultrasound

- Portable Systems

- Battery-Powered Systems

#### DESCRIPTION

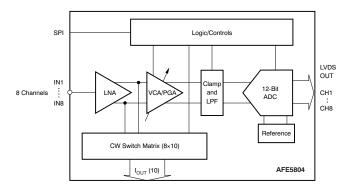

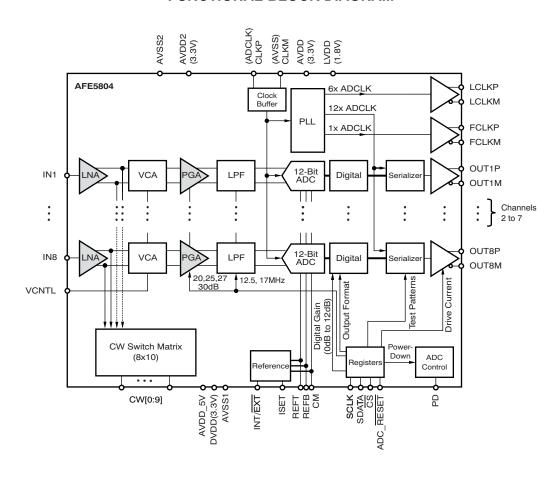

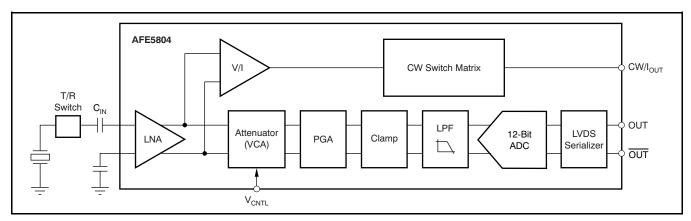

The AFE5804 is a complete analog front-end device specifically designed for ultrasound systems that require low power and small size.

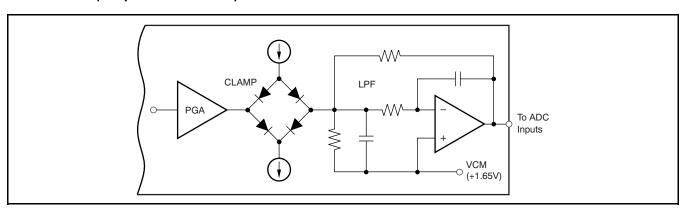

The AFE5804 consists of eight channels, including a low-noise amplifier (LNA), voltage-controlled attenuator (VCA), programmable gain amplifier (PGA), low-pass filter (LPF), and a 12-bit analog-to-digital converter (ADC) with low voltage differential signaling (LVDS) data outputs.

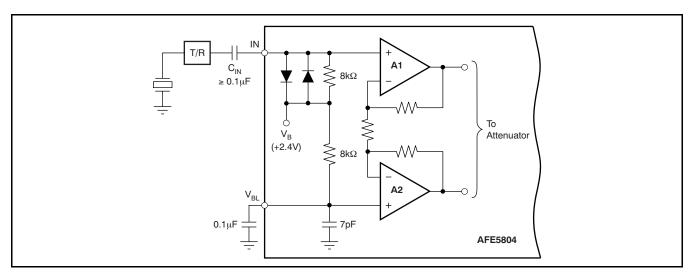

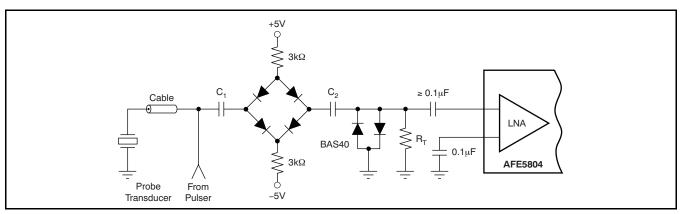

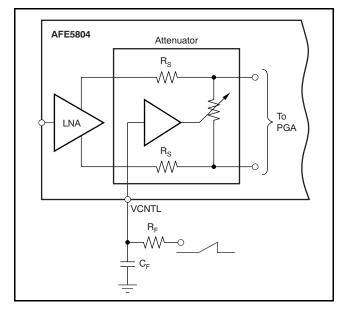

The LNA gain is set for 20dB gain and has excellent noise and signal handling capabilities, including fast overload recovery. VCA gain can vary over a 46dB range with a 0V to 1.2V control voltage common to all channels of the AFE5804.

The PGA can be programmed for gains of 20dB, 25dB, 27dB, and 30dB. The internal low-pass filter can also be programmed to 12.5MHz or 17MHz.

The LVDS outputs of the ADC reduce the number of interface lines to an ASIC or FPGA, thereby enabling the high system integration densities desired for portable systems. The ADC can either be operated with internal or external references. The ADC also features a signal-to-noise ratio (SNR) enhancement mode that can be useful at high gains.

The AFE5804 is available in a 15mm × 9mm, 135-ball BGA package that is Pb-free (RoHS-compliant) and green. It is specified for operation from 0°C to +85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Infineon is a registered trademark of Infineon Technologies. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# PACKAGING/ORDERING INFORMATION(1) (2)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | OPERATING<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY | ECO STATUS     |

|---------|--------------|-----------------------|-----------------------------------|--------------------|------------------------------|----------------|

|         |              |                       |                                   | AFE5804ZCFR        | Tape and Reel, 1000          |                |

| AFE5804 | μFBGA-135    | ZCF                   | 0°C to +85°C                      | AFE5804ZCFT        | Tape and Reel, 250           | Pb-Free, Green |

|         |              |                       |                                   | AFE5804ZCF         | Tray, 160                    |                |

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- These packages conform to Lead (Pb)-free and green manufacturing specifications. Additional details including specific material content can be accessed at www.ti.com/leadfree.

GREEN: TI defines Green to mean Lead (Pb)-Free and in addition, uses less package materials that do not contain halogens, including bromine (Br), or annimony (Sb) above 0.1% of total product weight. N/A: Not yet available Lead (Pb)-Free; for estimated conversion details are to represent the conversion details.

bromine (Br), or antimony (Sb) above 0.1%of total product weight. N/A: Not yet available Lead (Pb)-Free; for estimated conversion dates, go to <a href="https://www.ti.com/leadfree">www.ti.com/leadfree</a>. Pb-FREE: TI defines Lead (Pb)-Free to mean RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and, if designed to be soldered, suitable for use in specified lead-free soldering processes.

# **ABSOLUTE MAXIMUM RATINGS(1)**

Over operating free-air temperature range, unless otherwise noted.

|                                      |                       | AFE5804                              | UNIT |

|--------------------------------------|-----------------------|--------------------------------------|------|

| Supply voltage range, AV             | DD1                   | -0.3 to +3.9                         | V    |

| Supply voltage range, AV             | DD2                   | -0.3 to +3.9                         | V    |

| Supply voltage range, AVDD_5V        |                       | -0.3 to +6                           | V    |

| Supply voltage range, DV             | DD                    | -0.3 to +3.9                         | V    |

| Supply voltage range, LVI            | DD                    | -0.3 to +2.2                         | V    |

| Voltage between AVSS1                | and LVSS              | -0.3 to +0.3                         | V    |

| Voltage at analog inputs             |                       | -0.3 to minimum [3.6, (AVDD2 + 0.3)] | V    |

| External voltage applied to REFT-pin |                       | -0.3 to +3                           | V    |

| External voltage applied to          | o REFB-pin            | -0.3 to +2                           | V    |

| Voltage at digital inputs            |                       | -0.3 to minimum [3.9, (AVDD2 + 0.3)] | V    |

| Peak solder temperature (            | 2)                    | +260                                 | °C   |

| Maximum junction temper              | ature, T <sub>J</sub> | +125                                 | °C   |

| Storage temperature rang             | е                     | -55 to +150                          | °C   |

| Operating temperature rai            | nge                   | 0 to +85                             | °C   |

|                                      | НВМ                   | 2000                                 | V    |

| ESD ratings                          | CDM                   | 750                                  | V    |

|                                      | MM                    | 150                                  | V    |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

(2) Device complies with JSTD-020D.

#### **ELECTRICAL CHARACTERISTICS**

At AVDD\_5V = 5.0V, AVDD1 = AVDD2 = DVDD = 3.3V, LVDD = 1.8V, TGC mode I, single-ended input into LNA, ac-coupled  $(1.0\mu F)$ ,  $V_{CNTL}$  = 1.0V,  $f_{IN}$  = 5MHz, Clock = 40MSPS, 50% duty cycle, LPF = 12.5MHz, internal reference mode, ISET = 56k $\Omega$ , LVDS buffer setting = 3.5mA, and ambient temperature  $T_A$  = +25°C, unless otherwise noted.

|                                     |                      |                                                                |      | AFE5804        |      |                    |

|-------------------------------------|----------------------|----------------------------------------------------------------|------|----------------|------|--------------------|

| PARAMETER                           |                      | TEST CONDITIONS                                                | MIN  | TYP            | MAX  | UNIT               |

| PREAMPLIFIER (LNA)                  |                      |                                                                |      |                |      |                    |

| Gain                                | Α                    | SE-input to differential output                                |      | 20             |      | dB                 |

| Input voltage (TGC, PW modes)       | V <sub>IN</sub>      | Linear operation (HD2 ≤ 40dB)                                  |      | 280            |      | $mV_{PP}$          |

| (CW mode)                           |                      | Linear operation                                               |      | 220            |      | $mV_{PP}$          |

| Maximum input voltage               |                      | Limited by internal diodes                                     |      | 600            |      | $mV_{PP}$          |

| Input voltage noise (TGC)           | e <sub>n</sub> (RTI) | $R_S = 0\Omega$ , $f = 2MHz$                                   |      | 0.75           |      | nV/√ <del>Hz</del> |

|                                     | 1 (DTI)              | TGC mode I                                                     |      | 3              |      | pA/√Hz             |

| Input current noise                 | I <sub>n</sub> (RTI) | TGC mode II                                                    |      | 1.7            |      | pA/√ <del>Hz</del> |

| Common-mode voltage, input          | V <sub>CMI</sub>     | Internally generated                                           |      | 2.4            |      | V                  |

| Bandwidth                           | BW                   | Small-signal, –3dB                                             |      | 55             |      | MHz                |

| Input resistance                    | R <sub>IN</sub>      | At 2.5MHz                                                      |      | 8              |      | kΩ                 |

| Input capacitance                   | C <sub>IN</sub>      | Includes internal ESD and clamping diodes                      |      | 16             |      | pF                 |

| FULL-SIGNAL CHANNEL (LNA + V        | /CA + LPF            | + ADC)                                                         |      |                |      |                    |

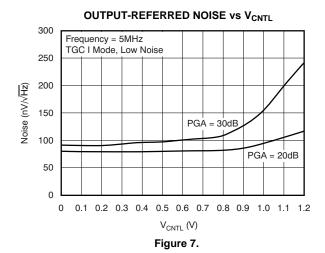

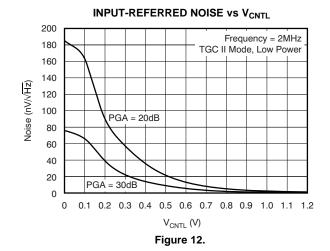

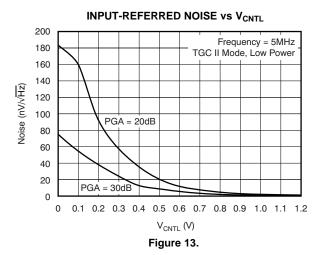

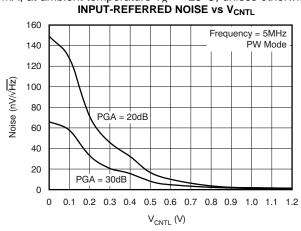

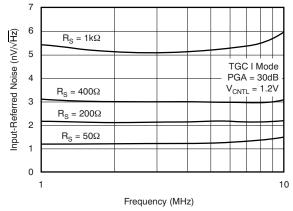

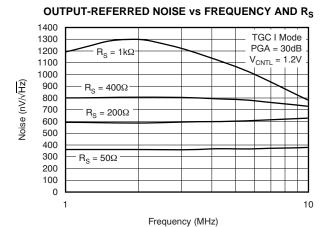

| Input voltage noise (TGC mode I)    | e <sub>n</sub>       | $R_S = 0\Omega$ , $f = 2MHz$ , $PGA = 30dB$                    |      | 0.89           |      | nV/√Hz             |

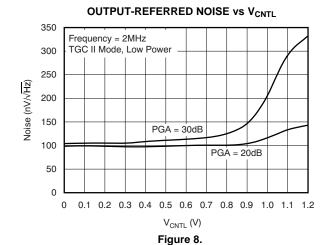

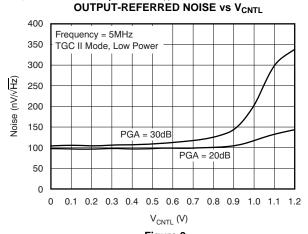

| Input voltage noise (TGC mode II)   |                      | $R_S = 0\Omega$ , $f = 2MHz$ , $PGA = 30dB$                    |      | 1.23           |      | nV/√ <del>Hz</del> |

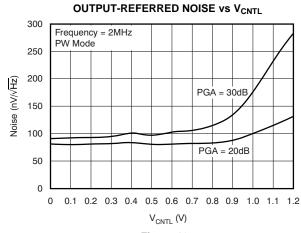

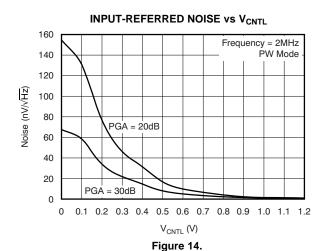

| Input voltage noise (PW mode)       |                      | $R_S = 0\Omega$ , $f = 2MHz$ , $PGA = 30dB$                    |      | 1.03           |      | nV/√ <del>Hz</del> |

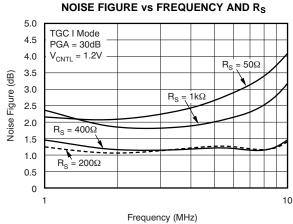

| Noise figure                        | NF                   | $R_S = 200\Omega$ , $f = 2MHz$                                 |      | 1.1            |      | dB                 |

| Low-pass filter bandwidth           | LPF                  | At –3dB, selectable through SPI                                |      | 12.5, 17       |      | MHz                |

| Bandwidth tolerance                 |                      |                                                                |      | ±10            |      | %                  |

| High-pass filter                    | HPF                  | (First-order, due to internal ac-coupling)                     |      | 200            |      | kHz                |

| Group delay variation               |                      | 1MHz to 10MHz                                                  |      | ±3             |      | ns                 |

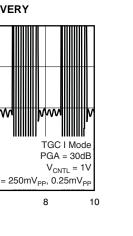

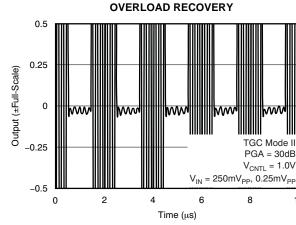

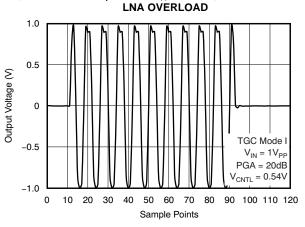

| Overload recovery                   |                      | ≤ 6dB overload to within 3%,<br>V <sub>CNTL</sub> = 0V to 1.2V |      | 2              |      | Clock Cycles       |

| ACCURACY                            |                      |                                                                |      |                |      |                    |

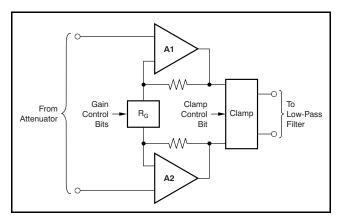

| Gain (PGA)                          |                      | Selectable through SPI                                         |      | 20, 25, 27, 30 |      | dB                 |

| Total gain, max <sup>(1)</sup>      |                      | LNA + PGA gain, V <sub>CNTL</sub> = 1.2V                       | 47.5 | 49             | 50.5 | dB                 |

| Coin rongo                          |                      | $V_{CNTL} = 0V \text{ to } 1.2V$                               |      | 46             |      | dB                 |

| Gain range                          |                      | V <sub>CNTL</sub> = 0.1V to 1.0V                               |      | 40             |      | dB                 |

|                                     |                      | 0V < V <sub>CNTL</sub> < 0.1V                                  |      | ±0.5           |      | dB                 |

| Gain error, absolute <sup>(2)</sup> |                      | 0.1V < V <sub>CNTL</sub> < 1.0V                                | -1.5 | ±0.5           | +1.5 | dB                 |

|                                     |                      | 1.0V < V <sub>CNTL</sub> < 1.2V                                |      | ±0.5           |      | dB                 |

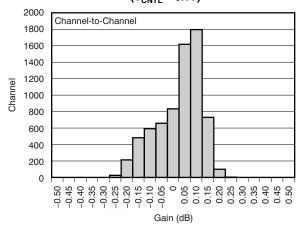

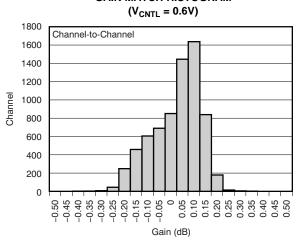

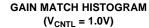

| Gain matching                       |                      | Channel-to-channel                                             | -0.5 | ±0.25          | +0.5 | dB                 |

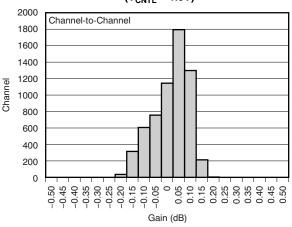

| Offset error                        |                      | V <sub>CNTL</sub> = 1.2V, PGA = 30dB                           | -39  |                | +39  | LSB                |

| Offset error drift (tempco)         |                      |                                                                |      | ±5             |      | ppm/°C             |

| Clamp level                         |                      | Level internally fixed before LPF                              |      | 2.3            |      | $V_{PP}$           |

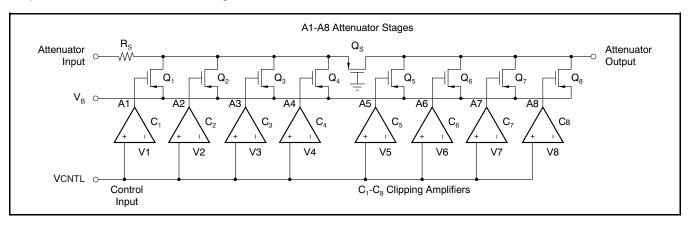

| GAIN CONTROL (VCA)                  |                      |                                                                |      |                |      |                    |

| Input voltage range                 | $V_{CNTL}$           | Gain range = 46dB                                              |      | 0 to 1.2       |      | V                  |

| Gain slope                          |                      | V <sub>CNTL</sub> = 0.1V to 1.0V                               |      | 44.4           |      | dB/V               |

| Input resistance                    |                      |                                                                |      | 25             |      | kΩ                 |

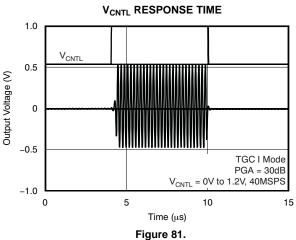

| Response time                       |                      | V <sub>CNTL</sub> = 0V to 1.2V step; to 90% signal             |      | 0.5            |      | μs                 |

<sup>(1)</sup> Excludes digital gain within ADC.(2) Excludes error of internal reference.

At AVDD\_5V = 5.0V, AVDD1 = AVDD2 = DVDD = 3.3V, LVDD = 1.8V, TGC mode I, single-ended input into LNA, ac-coupled (1.0 $\mu$ F), V<sub>CNTL</sub> = 1.0V, f<sub>IN</sub> = 5MHz, Clock = 40MSPS, 50% duty cycle, LPF = 12.5MHz, internal reference mode, ISET = 56k $\Omega$ , LVDS buffer setting = 3.5mA, and ambient temperature T<sub>A</sub> = +25°C, unless otherwise noted.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                                                  |       | AFE5804 |       |                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------|-------|---------|-------|--------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | TEST CONDITIONS                                                  | MIN   | TYP     | MAX   | UNIT               |

| DYNAMIC PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |                                                                  |       |         |       |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | $f_{IN} = 2MHz; -1dBFS$<br>( $V_{CNTL} = 1.0V, PGA = 30dB$ )     |       | 59.7    |       | dBFS               |

| Signal-to-noise ratio  Second-harmonic distortion  Third-harmonic distortion  Intermodulation distortion  Crosstalk  EW—SIGNAL CHANNELS  Input voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SNR                               | f <sub>IN</sub> = 5MHz; -1dBFS                                   |       | 59.5    |       | dBFS               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | f <sub>IN</sub> = 10MHz; -1dBFS                                  |       | 59.1    |       | dBFS               |

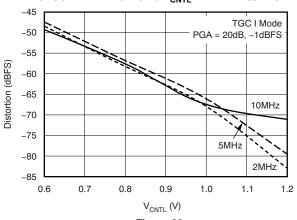

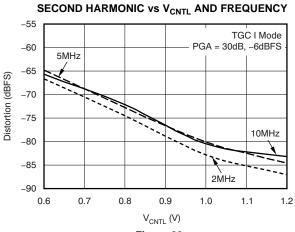

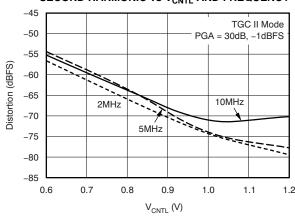

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | $f_{IN} = 5MHz; -1dBFS$<br>( $V_{CNTL} = 0.35V, PGA = 30dB$ )    |       | -45     |       | dBFS               |

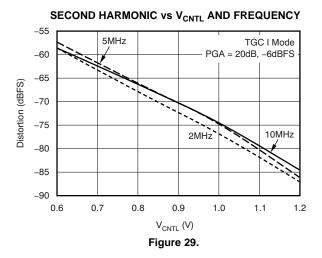

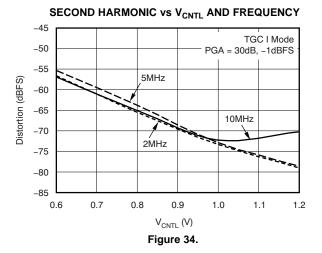

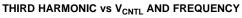

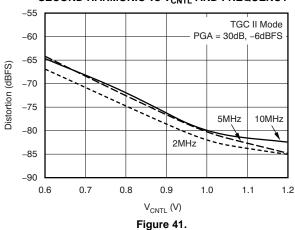

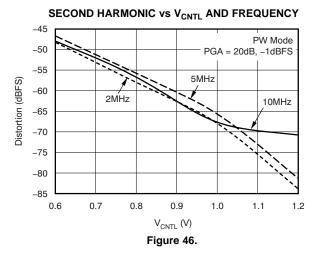

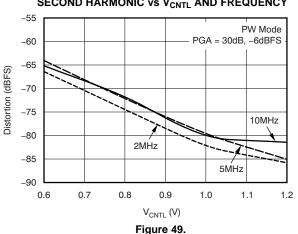

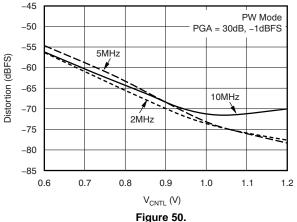

| Second-harmonic distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HD2                               | $f_{IN} = 5MHz; -1dBFS$<br>( $V_{CNTL} = 1V, PGA = 30dB$ )       | -50   | -70     |       | dBFS               |

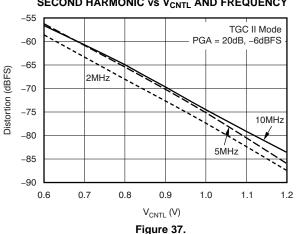

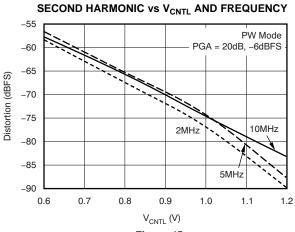

| nal-to-noise ratio  cond-harmonic distortion  cond-harmonic distortion |                                   | $f_{IN} = 5MHz; -6dBFS$<br>( $V_{CNTL} = 1V, PGA = 20dB$ )       | -61   | -70     |       | dBFS               |

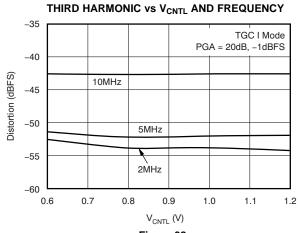

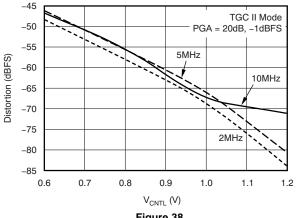

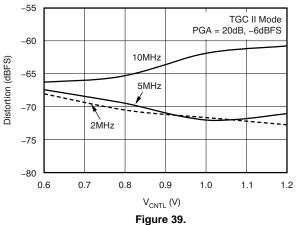

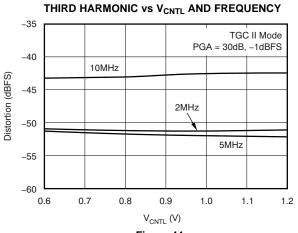

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | $f_{IN} = 5MHz; -1dBFS$<br>( $V_{CNTL} = 0.35V, PGA = 30dB$ )    |       | -43     |       | dBFS               |

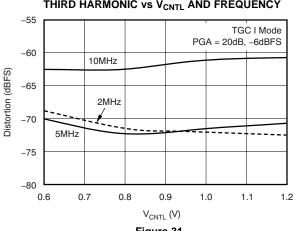

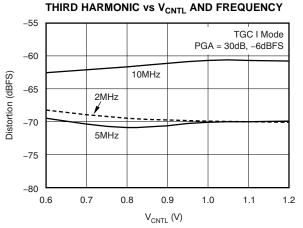

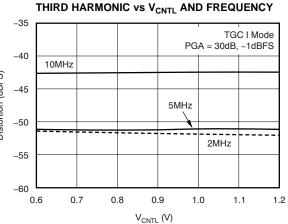

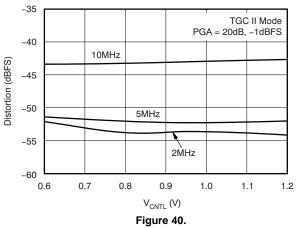

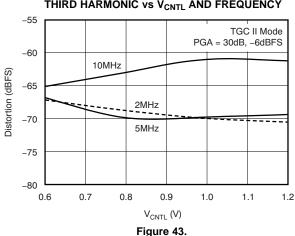

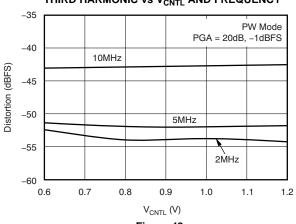

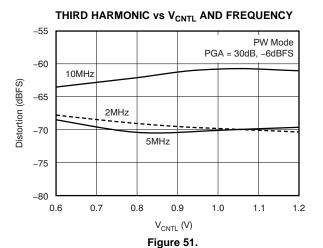

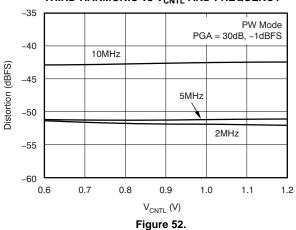

| ntermodulation distortion<br>crosstalk<br>cw—SIGNAL CHANNELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | HD3                               | $f_{IN} = 5MHz$ ; -1dBFS<br>( $V_{CNTL} = 1V$ , PGA = 30dB)      | -43   | -50     |       | dBFS               |

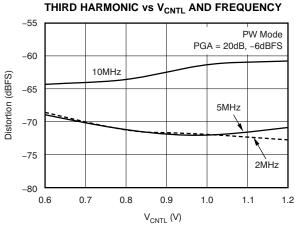

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | $f_{IN} = 5MHz$ ; $-6dBFS$<br>( $V_{CNTL} = 1V$ , $PGA = 20dB$ ) | -61   | -70     |       | dBFS               |

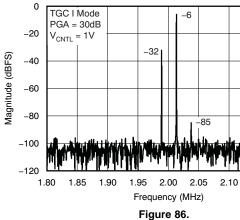

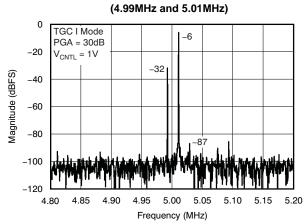

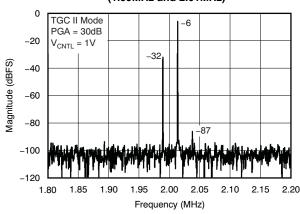

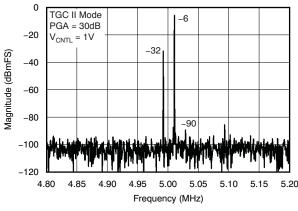

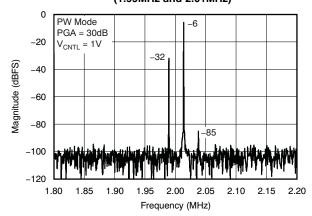

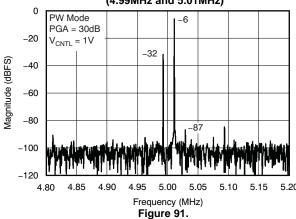

| Intermodulation distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IMD3                              | $f_1 = 4.99MHz$ at -6dBFS,<br>$f_2 = 5.01MHz$ at -32dBFS         |       | 58      |       | dBc                |

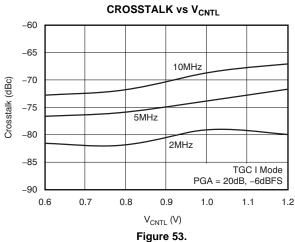

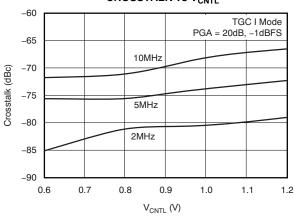

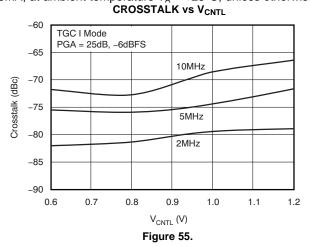

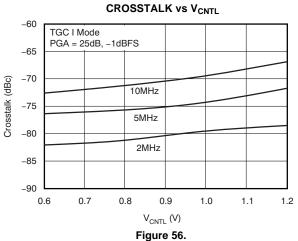

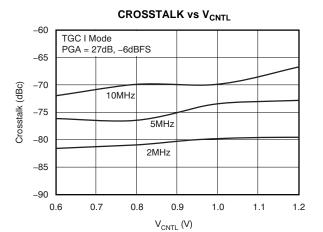

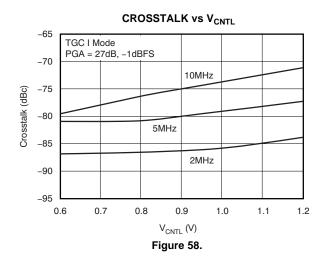

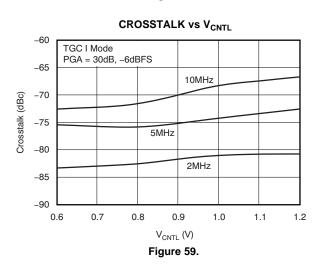

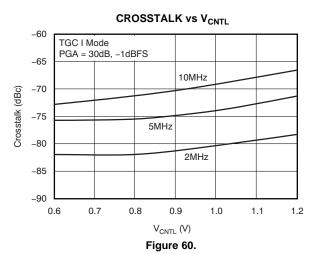

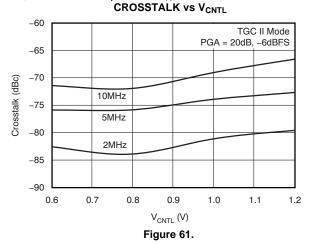

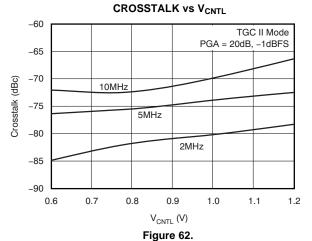

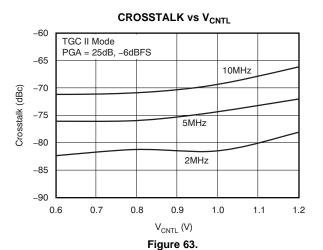

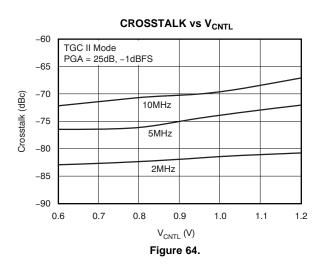

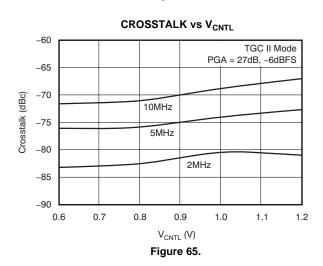

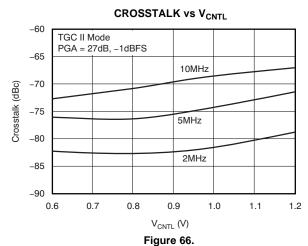

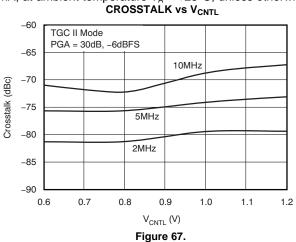

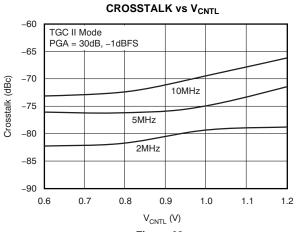

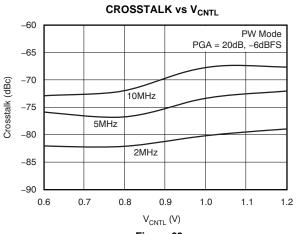

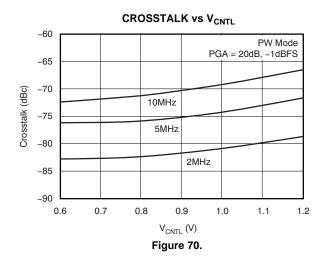

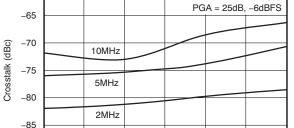

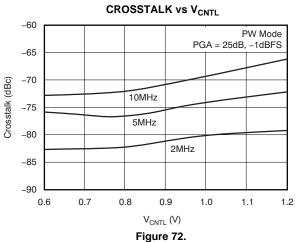

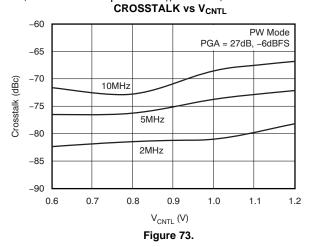

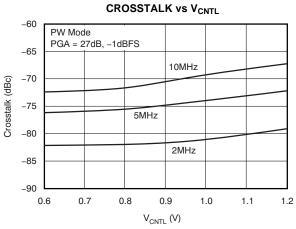

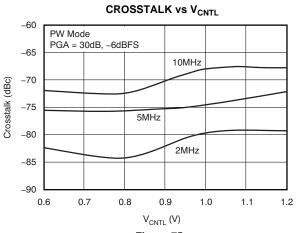

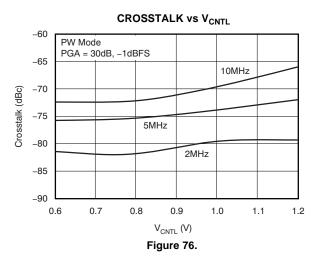

| Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | $f_{IN} \le 5MHz$ , $V_{CNTL} = 0.6V$ , $-6dBFS$                 |       | -67     |       | dBc                |

| CW—SIGNAL CHANNELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                                                                  |       |         |       |                    |

| Input voltage noise (CW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $e_n$                             | $R_S = 0\Omega$ , $f = 2MHz$                                     |       | 1.1     |       | nV/√ <del>Hz</del> |

| Output noise correlation factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | Summing of eight channels                                        |       | 0.6     |       | %                  |

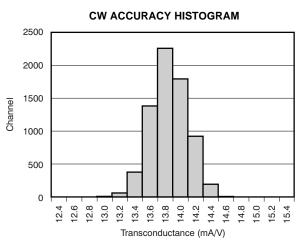

| Output transconductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <sub>OUT</sub> /V <sub>IN</sub> | At $V_{IN} = 100 \text{mV}_{PP}$                                 |       | 13.8    |       | mA/V               |

| Output transconductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OUT/ VIN                          | At $V_{IN} = 270 \text{mV}_{PP}$                                 |       | 12.2    |       | mA/V               |

| Dynamic CW output current, max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>OUTAC</sub>                |                                                                  |       | 2.9     |       | $mA_{PP}$          |

| Static CW output current (sink)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>OUTDC</sub>                |                                                                  |       | 0.9     |       | mA                 |

| Output common-mode voltage (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VCM                               |                                                                  |       | 2.5     |       | V                  |

| Output impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |                                                                  |       | 50      |       | kΩ                 |

| Output capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                                                                  |       | 10      |       | pF                 |

| INTERNAL REFERENCE VOLTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ES (ADC)                          |                                                                  |       |         |       |                    |

| Reference top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VREFT                             |                                                                  |       | 0.5     |       | V                  |

| Reference bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VREFB                             |                                                                  |       | 2.5     |       | V                  |

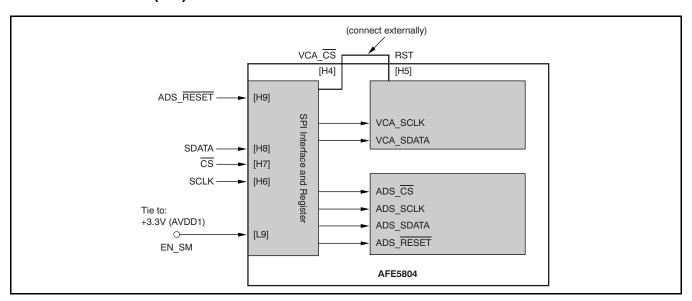

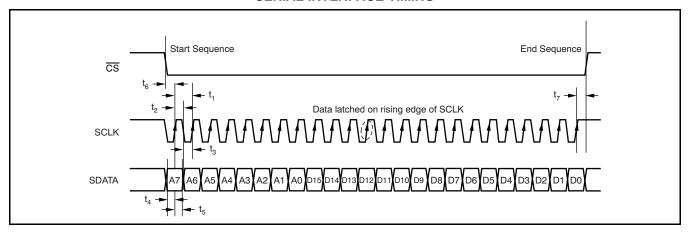

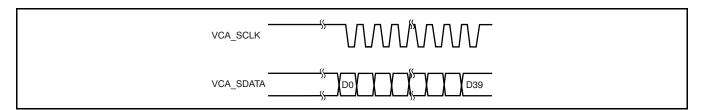

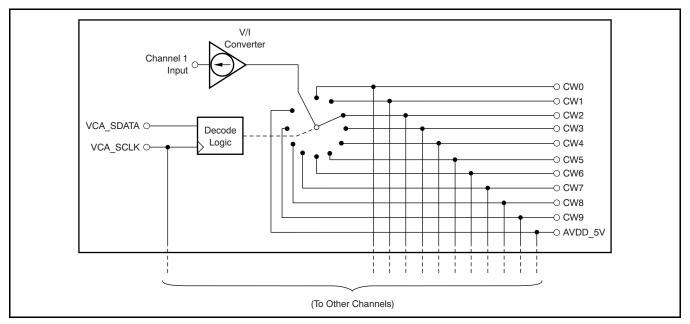

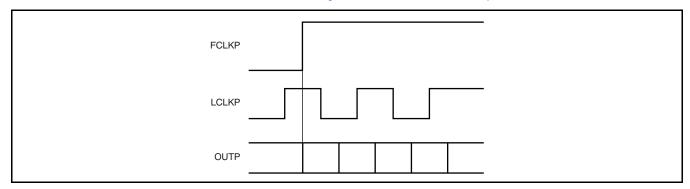

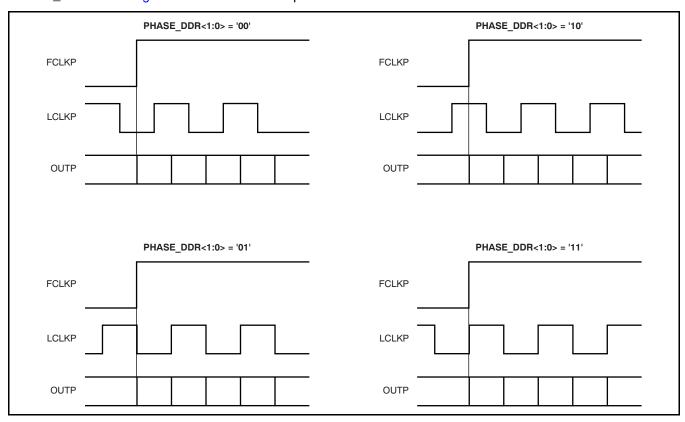

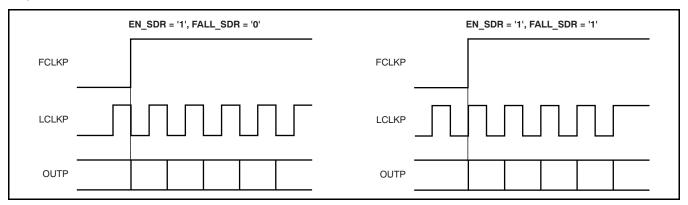

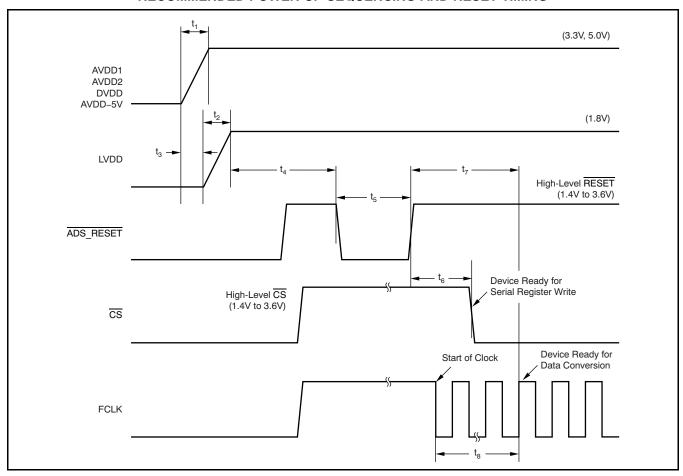

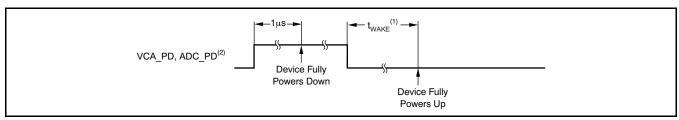

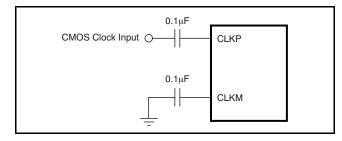

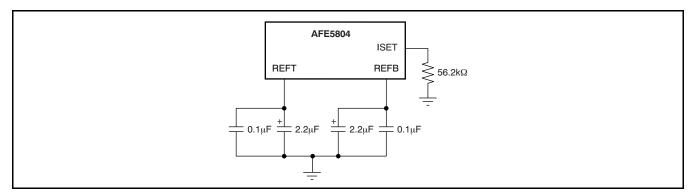

| VREFT – VREFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |                                                                  | 1.95  | 2       | 2.05  | V                  |