# Cool-GG™ PROGRAMMABLE BATTERY MANAGEMENT IC

#### **FEATURES**

- Powerful Low-Power 8-Bit RISC CPU Core Operating at up to 4 MHz Clock Frequency

- Flexible Memory Architecture

- 16k × 22 Program Flash EPROM

- 4k × 22 Program Mask ROM

- 512 × 8 Data Flash EPROM

- 512 × 8 Data RAM

- Three Reduced Power Modes

- Low Power: <240 μA

- Sleep: < 8 μA

- Hibernate: <0.5 μA

- High-Accuracy Analog Front End With Two Independent ADCs

- High-Resolution Integrator for Coulomb Counting—Better Than 3nVh Resolution

- Coulomb Counter Self-Calibration

Reduces Offset to Less Than 1 μV

- 15-Bit Delta-Sigma ADC With a 12-Channel Multiplexer for Voltage, Current, and Temperature Measurements

- Accurate On-Chip 32.768-kHz Oscillator

- Internal Clock Synthesizer Generates

Frequencies up to 4 MHz

- Integrated Flash Memory Eliminates Need for External EEPROM

- 24 Memory-Mapped I/O Pins

- Supports Two Serial Communication Protocols

- Two-Wire SMBus v1.1 Interface

- Single-Wire HDQ Interface

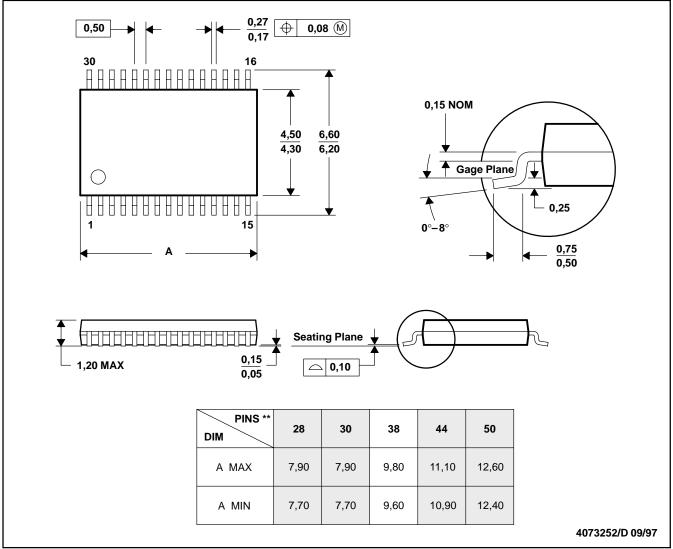

- Package: 38-Pin TSSOP (DBT)

- Complete Integrated Development Environment

## **APPLICATIONS**

- Battery Management

- Gas Gauges

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

❤ Texas Instruments

www.ti.com

Cool-GG is a trademark of Texas Instruments.

#### DESCRIPTION

The Texas Instruments bq8015 Cool-GG™ programmable battery management IC is the next in a series of advanced, high-performance, reducedinstruction-set-CPU (RISC) integrated circuits for battery management and gas-gauge applications. In a single CMOS IC, the bq8015 combines high-accuracy analog measurement capabilities with a low-power high-speed RISC processor, integrated flash memory, and an array of peripheral and communication ports. The program flash EPROM allows fast development of custom implementations, and the low-power analog peripherals improve accuracy beyond discrete implementations. In its 38-pin TSSOP package, the bq8015 can implement a variety of functions in a small PCB area.

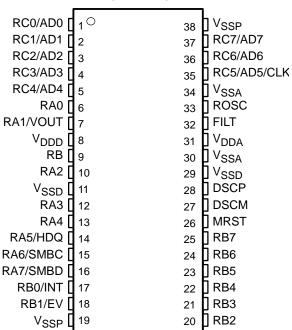

# TSSOP PACKAGE (TOP VIEW)

# **Terminal Functions**

| TERMINAL         |        |      |                                                                                                                                                                                             |

|------------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.    | 1/0  | DESCRIPTION                                                                                                                                                                                 |

| DSCM             | 27     | IA   | Analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between DSCP and DSCM. DSCM can also be selected as an input to the over-sampled ADC. |

| DSCP             | 28     | IA   | Analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between DSCP and DSCM. DSCP can also be selected as an input to the over-sampled ADC. |

| FILT             | 32     | IA   | Analog pin connected to the external PLL loop filter components                                                                                                                             |

| MRST             | 26     | ļ    | Master reset input pin that forces the device into reset when held high. Must be held low for normal operation.                                                                             |

| RA0              | 6      | I/OD | Port A.0 digital open-drain I/O pin                                                                                                                                                         |

| RA1/VOUT         | 7      | I/O  | Port A.1 digital push-pull I/O pin with pullup capable of driving power for an external device                                                                                              |

| RA2              | 10     | I/OD | Port A.2 digital open-drain I/O pin                                                                                                                                                         |

| RA3              | 12     | I/OD | Port A.3 digital open-drain I/O pin                                                                                                                                                         |

| RA4              | 13     | I/OD | Port A.4 digital open-drain I/O pin                                                                                                                                                         |

| RA5/HDQ          | 14     | I/OD | Port A.5 digital open-drain I/O pin or one-wire DQ/HDQ serial communication pin                                                                                                             |

| RA6/SMBC         | 15     | I/OD | Port A.6 digital open-drain I/O pin or SMBus clock pin                                                                                                                                      |

| RA7/SMBD         | 16     | I/OD | Port A.7 digital open-drain I/O pin or SMBus data pin                                                                                                                                       |

| RB               | 9      | Р    | RAM backup pin to provide backup potential to the internal DATA RAM if $V_{CC}$ is momentarily shorted, by using a capacitor attached between RB and $V_{SS}$                               |

| RB0/INT          | 17     | I/OD | Port B.0 digital open-drain I/O pin or selectable as a configurable external processor interrupt                                                                                            |

| RB1/EV           | 18     | I/OD | Port B.1 digital open-drain I/O pin or selectable as a configurable external event input to wake the controller from a halt state                                                           |

| RB2              | 20     | I/OD | Port B.2 digital open-drain I/O pin                                                                                                                                                         |

| RB3              | 21     | I/OD | Port B.3 digital open-drain I/O pin                                                                                                                                                         |

| RB4              | 22     | I/OD | Port B.4 digital open-drain I/O pin                                                                                                                                                         |

| RB5              | 23     | I/OD | Port B.5 digital open-drain I/O pin                                                                                                                                                         |

| RB6              | 24     | I/OD | Port B.6 digital open-drain I/O pin                                                                                                                                                         |

| RB7              | 25     | I/OD | Port B.7 digital open-drain I/O pin                                                                                                                                                         |

| RC0/AD0          | 1      | I/O  | Port C.0 digital push-pull I/O pin or selectable as an input, AD0, to the over-sampled ADC                                                                                                  |

| RC1/AD1          | 2      | I/O  | Port C.1 digital push-pull I/O pin or selectable as an input, AD1, to the over-sampled ADC                                                                                                  |

| RC2/AD2          | 3      | I/O  | Port C.2 digital push-pull I/O pin or selectable as an input, AD2, to the over-sampled ADC                                                                                                  |

| RC3/AD3          | 4      | I/O  | Port C.3 digital push-pull I/O pin or selectable as an input, AD3, to the over-sampled ADC                                                                                                  |

| RC4/AD4          | 5      | I/O  | Port C.4 digital push-pull I/O pin or selectable as an input, AD4, to the over-sampled ADC                                                                                                  |

| RC5/AD5/CLK      | 35     | I/O  | Port C.5 digital push-pull I/O pin or selectable as an input, AD5, to the over-sampled ADC or a 32-kHz square-wave output                                                                   |

| RC6/AD6          | 36     | I/O  | Port C.6 digital push-pull I/O pin or selectable as an input, AD6, to the over-sampled ADC                                                                                                  |

| RC7/AD7          | 37     | I/O  | Port C.7 digital push-pull I/O pin or selectable as an input, AD7, to the over-sampled ADC                                                                                                  |

| ROSC             | 33     | IA   | Internal oscillator bias resistor input pin                                                                                                                                                 |

| $V_{\text{DDA}}$ | 31     | Р    | Positive supply for analog circuitry. V <sub>DDA</sub> and V <sub>DDD</sub> must be driven to the same potential.                                                                           |

| $V_{\text{DDD}}$ | 8      | Р    | Positive supply for digital circuitry and I/O pins. V <sub>DDD</sub> and V <sub>DDA</sub> must be driven to the same potential.                                                             |

| VSSA             | 30, 34 | Р    | Negative supply for analog circuitry. VSSA, VSSD, and VSSP must be driven to the same potential.                                                                                            |

| VSSD             | 11, 29 | Р    | Negative supply for digital circuitry. VSSA, VSSD, and VSSP must be driven to the same potential.                                                                                           |

| VSSP             | 19, 38 | Р    | Negative supply for output circuitry. VSSA, VSSD, and VSSP must be driven to the same potential.                                                                                            |

NOTE: I = Input, IA = Analog input, I/O = Input/output, I/OD = Input/Open-drain output, O = Output, OA = Analog output, P = power

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>DD</sub> relative to V <sub>SS</sub> (see Note 1)                 | 0.3 V to 6 V  |

|------------------------------------------------------------------------------------------------|---------------|

| Open-drain I/O pins, V <sub>(IOD)</sub> relative to V <sub>SS</sub> (see Note 1)               |               |

| Input voltage range to all other pins, V <sub>I</sub> relative to V <sub>SS</sub> (see Note 1) |               |

| Operating free-air temperature range, T <sub>A</sub>                                           | 20°C to 85°C  |

| Storage temperature range, T <sub>stq</sub>                                                    | 65°C to 150°C |

| ESD Rating (see Note 2) HBM                                                                    |               |

| CDM                                                                                            | 1.5 kV        |

| MM                                                                                             | 50 V          |

NOTES: 1. VSS refers to the common node of V(SSA), V(SSD), and VSS.

2. Design considerations should be made with respect to excessive ESD.

# electrical characteristics, $T_A = -20^{\circ}C$ to 85°C, 3 V to 3.6 V (unless otherwise noted)

#### power supply

|                      | PARAMETER                    | TEST CONDITIONS            | MIN | TYP  | MAX  | UNIT |

|----------------------|------------------------------|----------------------------|-----|------|------|------|

| V(DDD)               | Digital supply voltage range |                            | 3   | 3.3  | 3.6  | .,   |

| V(DDA)               | Analog supply voltage range  |                            | 3   | 3.3  | 3.6  | V    |

|                      |                              | Normal (see Note 3)        |     | 1.7  | 2    | mA   |

| l.                   | Divital county county        | Low power (see Note 4)     |     | 13   | 30   |      |

| I(DDD)               | Digital supply current       | Sleep (see Note 5)         |     | 0.3  | 1    |      |

|                      |                              | Hibernate (see Notes 6, 7) |     | 0.05 | 0.2  |      |

|                      |                              | Normal (see Note 3)        |     | 315  | 400  |      |

| l.                   |                              | Low power (see Note 4)     |     | 240  | 310  | μΑ   |

| I(DDA)               | Analog supply current        | Sleep (see Note 5)         |     | 8    | 13.5 |      |

|                      |                              | Hibernate (see Notes 6, 7) |     | 0.4  | 8.0  |      |

| I <sub>(DDPOR)</sub> | Power on reset current       | V(DD) < V(POR)             |     | 0.01 | 0.5  |      |

NOTES: 3. CPU executing. No flash programming or erase operation .ADC and CC operating. VOUTEN = 0.

- 4. Oscillator, PLL and POR circuits active (PLL\_OFF=0, LP\_CLK=1, OSC\_EN=1) CC operating. CPU halted.

- 5. Oscillator and POR circuits active, PLL is off (PLL\_OFF=1, LP\_CLK=1, OSC\_EN=1) CPU halted.

- 6. POR circuit active. Oscillator and PLL are off. (PLL\_OFF=1, LP\_CLK=1, OSC\_EN=0). CPU halted.

- 7.  $I(DDD) + I(DDA) \le 1 \mu A$

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# electrical characteristics, $T_A = -20^{\circ}C$ to 85°C, 3 V to 3.6 V (unless otherwise noted) (continued)

# power-on reset (see Figure 1)

|                   | PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------|-----------------|-----|-----|-----|------|

| V <sub>IT</sub> . | Negative-going voltage input |                 | 2.1 | 2.3 | 2.5 | V    |

| $V_{hy}$          | Ys Hysteresis voltage        |                 | 50  | 125 | 200 | mV   |

#### **POR BEHAVIOR** FREE-AIR TEMPERATURE V<sub>IT</sub> - Negative-Going Input Threshold Voltage - V 2.50 150 145 2.45 Vhys - Hysteresis Voltage - mV 2.40 140 V<sub>IT</sub>\_ $v_{\text{hys}}$ 135 2.35 2.30 130 2.25 125 2.20 120 2.15 115 , –20 10 25 40 70 $T_A$ – Free-Air Temperature – ${}^{\circ}C$

Figure 1

# general purpose digital inputs and outputs

|                         | PARAMETER                        | TEST CONDITIONS                                        | MIN                  | TYP | MAX | UNIT |

|-------------------------|----------------------------------|--------------------------------------------------------|----------------------|-----|-----|------|

| VIH                     | High-level input voltage         |                                                        | 2                    |     |     | V    |

| V <sub>IL</sub>         | Low-level input voltage low      |                                                        |                      |     | 8.0 | V    |

| Voн                     | Output voltage <sup>†</sup> high | I <sub>L</sub> =-0.5 mA                                | V <sub>DD</sub> -0.5 |     |     | V    |

| VOL                     | Low-level output voltage         | I <sub>L</sub> = 0.5 mA                                |                      |     | 0.4 | V    |

| Cl                      | Input capacitance                |                                                        |                      | 5   |     | pF   |

| loL                     | Low-level output current         | Open drain outputs, V <sub>OL</sub> = 0.4 V            |                      |     | 10  | mA   |

| I(VOUT)                 | VOUT source current              | VOUT active, V <sub>OUT</sub> = V <sub>DD</sub> -0.6 V | <b>-</b> 5           |     |     | mA   |

| I <sub>lkg</sub> (VOUT) | VOUT leakage current             | VOUT inactive                                          | -0.2                 |     | 0.2 | μΑ   |

| l <sub>lkg</sub>        | Input leakage current            |                                                        |                      |     | 1   | μΑ   |

<sup>†</sup> RC[0:7] bus

4

# electrical characteristics, $T_A = -20^{\circ}C$ to $85^{\circ}C$ , 3 V to 3.6 V (unless otherwise noted) (continued)

# ADC (Unless otherwise specified, the specification limits are valid at both slow and fast modes as well as internal and external reference.)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                      | MIN  | TYP    | MAX                  | UNIT              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|--------|----------------------|-------------------|

| Leaved well- are many                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Internal V <sub>ref</sub>                            | -0.3 |        | 1                    | .,                |

| Input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External V <sub>ref</sub>                            | -0.3 |        | 0.8×V <sub>DDA</sub> | V                 |

| On the state of th | FAST = 0                                             |      | 31.5   |                      |                   |

| Conversion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FAST = 1                                             |      | 2.0    |                      | ms                |

| Resolution (no missing codes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FAST = 0                                             | 16   |        |                      | bits              |

| <b></b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FAST = 0                                             | 14   | 15     |                      |                   |

| Effective resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FAST = 1                                             | 9    | 10     |                      | bits              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FAST = 0                                             |      | 20     |                      | .,                |

| Input referred noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FAST = 1                                             |      | 375    |                      | $\mu V_{rms}$     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FAST = 0, $-0.1 \text{ V to } 0.8 \text{ x V}_{ref}$ |      | ±0.003 | ±0.009               |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FAST = 0, -0.3 V to -0.1 V                           |      | ±0.043 |                      |                   |

| Integral nonlinearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FAST = 1, $-0.1 \text{ V to } 0.8 \text{ x V}_{ref}$ |      | ±0.008 | ±0.016               | %FSR <sup>†</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FAST = 1, -0.3 V to -0.1 V                           |      | ±0.043 |                      |                   |

| Offset error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FAST = 0                                             |      | 100    | 250                  | μV                |

| Offset error drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FAST = 0; typical 25-70°C                            |      | 475    | 4000                 | nV/°C             |

| Full-scale error‡                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | =    | ±0.25% |                      |                   |

| Full-scale error drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FAST = 0                                             |      | 150    |                      | PPM/°C            |

| Effective input resistance§                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | 8    |        |                      | ΜΩ                |

<sup>†</sup> Full-scale reference

#### coulomb counter

| PARAMETER                         | TEST CONDITIONS                  | MIN TY | P MAX    | UNIT   |

|-----------------------------------|----------------------------------|--------|----------|--------|

| Input voltage range               |                                  | -0.3   | 1.0      | V      |

| Conversion time                   | Single conversion                | 25     | 0        | ms     |

| Effective resolution (see Note 8) | Single conversion                | 15     |          | bits   |

| Noise                             | Single conversion                | 2      | 0        | μVrms  |

| late and a caline wite.           | -0.1 V to 0.8 x V <sub>ref</sub> | ±0.00  | 3 ±0.009 | %FSR   |

| Integral nonlinearity             | -0.3 V to -0.1 V                 | ±0.04  | 3        |        |

| Offset error (see Note 8)         |                                  |        | 1        | μV     |

| Offset error drift                |                                  | 0.     | 4 3      | μV/°C  |

| Full-scale error                  |                                  | ±0.259 | 6        |        |

| Full-scale error drift            | 25°C-70°C typical                | 15     | 0        | PPM/°C |

| Effective input resistance        |                                  | 10     |          | МΩ     |

NOTE 8: Post-calibration performance

<sup>&</sup>lt;sup>‡</sup> Uncalibrated performance. This gain error can be eliminated with external calibration.

<sup>§</sup> The A/D input is a switched-capacitor input. Since the input is switched, the effective input resistance is a measure of the average resistance.

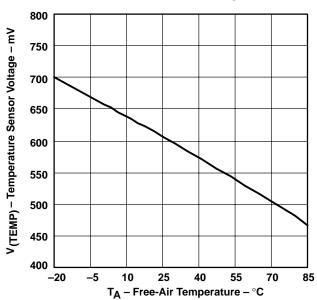

# electrical characteristics, $T_A = -20^{\circ}C$ to 85°C, 3 V to 3.6 V (unless otherwise noted) (continued) temperature sensor (see Figure 2)

| PARAMETER                                                   | TEST CONDITIONS | MIN | TYP  | MAX | UNIT  |

|-------------------------------------------------------------|-----------------|-----|------|-----|-------|

| V <sub>(TEMP)</sub> Temperature sensor voltage (see Note 9) |                 |     | -2.2 |     | mV/°C |

NOTE 9: -58.6 LSB/°C

# TEMPERATURE SENSOR VOLTAGE

# FREE-AIR TEMPERATURE

Figure 2

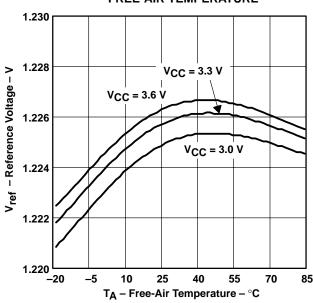

# electrical characteristics, $T_A = -20^{\circ}C$ to 85°C, 3 V to 3.6 V (unless otherwise noted) (continued) voltage reference (see Figure 3)

| PARAMETER            | TEST CONDITIONS | MIN    | TYP   | MAX    | UNIT   |

|----------------------|-----------------|--------|-------|--------|--------|

| Output voltage       |                 | 1.2128 | 1.225 | 1.2373 | V      |

| Output voltage drift | Over 50°C       |        | 40    |        | PPM/°C |

# REFERENCE VOLTAGE

# vs FREE-AIR TEMPERATURE

Figure 3

# PLL switching characteristics, $T_A = -20^{\circ}C$ to 85°C, 3 V to 3.6 V (unless otherwise noted)

|       | PARAMETER                   | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|-------|-----------------------------|-----------------------|-----|-----|-----|------|

| t(sp) | Start-up time (see Note 10) | ±0.5% frequency error |     | 2.0 | 5.0 | ms   |

NOTE 10: The frequency error is measured from 32768 Hz.

# electrical characteristics, $T_A = -20^{\circ}C$ to $85^{\circ}C$ , 3 V to 3.6 V (unless otherwise noted) (continued)

# internal oscillator (see Figure 4)

|        | PARAMETER                     | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|--------|-------------------------------|-----------------|-----|------|-----|------|

| f(exo) | Frequency error (see Note 11) |                 | -2% | 0.5% | 2%  |      |

| t(sxo) | Start-up time (see Note 12)   |                 |     |      | 250 | μs   |

NOTES: 11. The frequency error is measured from 32768 Hz.

12. The startup time is defined as the time it takes for the oscillator output frequency to be  $\pm 2\%$ .

# **OSCILLATOR ERROR** FREE-AIR TEMPERATURE 1.6 1.4 1.2 Oscillator Error – % 1.0 0.8 0.6 0.4 0.2 $V_{DD} = 3.3 V$ 0.0 -20 -10 0 10 20 30 40 50 $T_A$ – Free-Air Temperature – $^{\circ}C$

Figure 4

# data flash memory switching characteristics over recommended operating temperature and supply voltage (unless otherwise noted)

|                       | PARAMETER                      | TEST CONDITIONS | MIN | TYP             | MAX | UNIT   |

|-----------------------|--------------------------------|-----------------|-----|-----------------|-----|--------|

|                       | Data retention                 | See Note 13     | 10  |                 |     | Years  |

|                       | Flash programming write-cycles | See Note 13     |     | 10 <sup>5</sup> |     | Cycles |

| t(ROWPROG)            | Row programming time           | See Note 13     |     |                 | 2   | ms     |

| t(MASSERASE)          | Mass-erase time                | See Note 13     |     |                 | 4   | ms     |

| I <sub>(DDPROG)</sub> | Flash-write supply current     | See Note 13     |     | 14              | 16  | mA     |

| I(DDERASE)            | Flash-erase supply current     | See Note 13     |     | 14              | 16  | mA     |

NOTE 13: Assured by design. Not production tested.

# register backup

|                   | PARAMETER                                     | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| I(RB)             | RB data-retention input current (see Note 14) | $V_{RB} > 3.0 \text{ V}, V_{DD} < V_{IT}$ |     | 10  | 100 | nA   |

| V <sub>(RB)</sub> | RB data-retention voltage                     |                                           | 1.3 |     |     | V    |

NOTE 14: Assured by design. Not production tested.

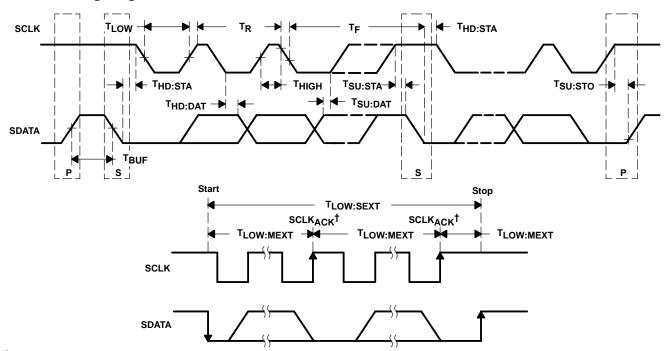

# SMBus timing characteristics, $T_A = -20^{\circ}C$ to 85°C, 3.0 V < $V_{CC}$ < 3.6 V (unless otherwise noted)

|                       | PARAMETER                                              | TEST CONDITIONS                        | MIN | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------------------------------|----------------------------------------|-----|------|------|------|

| F <sub>SMB</sub>      | SMBus operating frequency                              | Slave mode, SMBC 50% duty cycle        | 10  |      | 100  | kHz  |

| FMAS                  | SMBus master clock frequency                           | Master mode, no clock low slave extend |     | 51.2 |      | kHz  |

| T <sub>BUF</sub>      | Bus free time between start and stop (see Figure 5)    |                                        | 4.7 |      |      | μs   |

| T <sub>HD:STA</sub>   | Hold time after (repeated) start (see Figure 5)        |                                        | 4.0 |      |      | μs   |

| T <sub>SU:STA</sub>   | Repeated start setup time (see Figure 5)               |                                        | 4.7 |      |      | μs   |

| T <sub>SU:STO</sub>   | Stop setup time (see Figure 5)                         |                                        | 4.0 |      |      | μs   |

| T                     | Data hald time (and Figure 5)                          | Receive mode                           | 0   |      |      |      |

| T <sub>HD:DAT</sub>   | Data hold time (see Figure 5)                          | Transmit mode                          | 300 |      |      | μs   |

| T <sub>SU:DAT</sub>   | Data setup time (see Figure 5)                         |                                        | 250 |      |      | μs   |

| TTIMEOUT              | Error signal/detect (see Figure 5)                     | See Note 15                            | 25  |      | 35   | ms   |

| $T_{LOW}$             | Clock low period (see Figure 5)                        |                                        | 4.7 |      |      | μs   |

| THIGH                 | Clock high period (see Figure 5)                       | See Note 16                            | 4.0 |      | 50   | μs   |

| T <sub>LOW:SEXT</sub> | Cumulative clock low slave extend time                 | See Note 17                            |     |      | 25   | ms   |

| T <sub>LOW:MEXT</sub> | Cumulative clock low master extend time (see Figure 5) | See Note 18                            |     |      | 10   | ms   |

| T <sub>F</sub>        | Clock/data fall time                                   | See Note 19                            |     |      | 300  | ns   |

| T <sub>R</sub>        | Clock/data rise time                                   | See Note 20                            |     |      | 1000 | ns   |

NOTES: 15. The bq8015 times out when any clock low exceeds  $T_{\mbox{TIMEOUT}}$

- 16. T<sub>HIGH, Max</sub>, is the minimum bus idle time. SMBC = SMBD = 1 for t > 50 μs causes reset of any transaction involving bq8015 that is in progress.

- 17. TLOW: SEXT is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

- 18. TLOW:MEXT is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

- 19. Rise time  $T_R = V_{ILMAX} 0.15$ ) to  $(V_{IHMIN} + 0.15)$

- 20. Fall time  $T_F = 0.9V_{DD}$  to  $(V_{ILMAX} 0.15)$

# HDQ timing characteristics, $T_A = -20^{\circ}C$ to $85^{\circ}C$ , $3.0~V < V_{CC} < 3.6~V$ (unless otherwise noted)

|                        | PARAMETER                               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

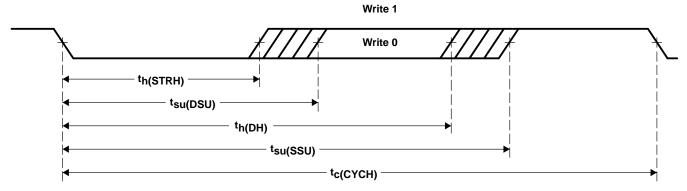

| t <sub>C</sub> (CYCH)  | Cycle time, host to bq8015 (write)      | See Figure 7    | 190 |     |     | μs   |

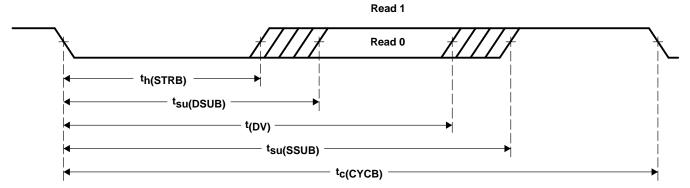

| t <sub>C</sub> (CYCB)  | Cycle time, bq8015 to host (read)       | See Figure 8    | 190 | 205 | 250 | μs   |

| th(STRH)               | Start hold time, host to bq8015 (write) | See Figure 7    | 5   |     |     | ns   |

| th(STRB)               | Start hold time, host to bq8015 (read)  | See Figure 8    | 32  |     |     | μs   |

| t <sub>su(DSU)</sub>   | Data setup time                         | See Figure 7    |     |     | 50  | μs   |

| t <sub>su</sub> (DSUB) | Data setup time                         | See Figure 8    |     |     | 50  | μs   |

| <sup>t</sup> h(DH)     | Data hold time                          | See Figure 7    | 100 |     |     | μs   |

| t(DV)                  | Data valid time                         | See Figure 8    | 80  |     |     | μs   |

| t <sub>su(SSU)</sub>   | Stop setup time                         | See Figure 7    |     |     | 145 | μs   |

| t <sub>su</sub> (SSUB) | Stop setup time                         | See Figure 8    |     |     | 145 | μs   |

| t(RSPS)                | Response time, bq8015 to host           |                 | 190 |     | 320 | μs   |

| t(B)                   | Break time                              | See Figure 6    | 190 |     |     | μs   |

| t(BR)                  | Break recovery time                     | See Figure 6    | 40  |     |     | μs   |

Figures 5–8 are timing diagrams for the bq8015.

# **SMBus timing diagrams**

$\ensuremath{^\dagger} \ensuremath{\mathsf{SCLK}}_{ACK}$  is the acknowledge-related clock pulse generated by the master.

Figure 5. SMBus Timing Diagram

# HDQ timing diagrams

- t(B)

Figure 6. HDQ Break Timing

Figure 7. HDQ Host to bq8015

Figure 8. HDQ bq8015 to Host

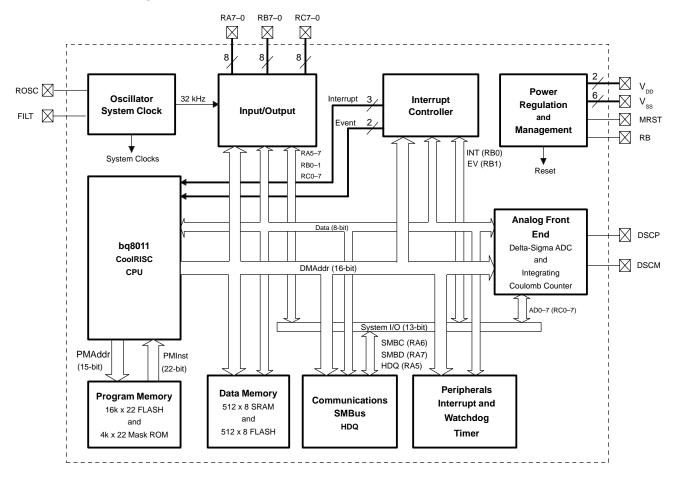

# functional block diagram

# general operational overview

The bq8015 functional block diagram outlines the major components within the IC. Together with the flash-based firmware, the bq8015 performs the necessary calculations and control for a fully functional battery management system. Each of the major component blocks in the bq8015 is outlined below.

# **RISC** processor

The bq8015's flexible architecture allows easy development of numerous battery-management solutions. Based on a RISC processor featuring a Harvard architecture, the bq8015 operates at frequencies up to 4 MHz. The clock frequency is synthesized from an internal 32 kHz oscillator and is programmable under firmware control. Using a three-stage instruction pipeline, the RISC processor can execute one instruction every clock cycle. With a 22-bit instruction width, the bq8015 can manipulate complex data with a single line of code. Further details about the bq8015 core architecture and CPU instruction set are in the bq80xx Core Manual.

# general operational overview (continued)

# data and program memory

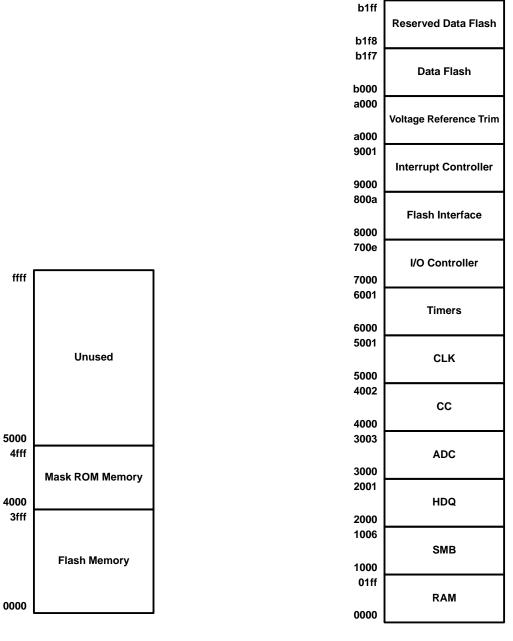

To improve performance and reduce operating power, the bq8015 uses separate data and program memory address busses, providing ample program and data-storage capability. This feature also allows for future memory expansion of the bq8015 family without affecting existing programs.

The bq8015 provides 512 bytes of data RAM on two 256-byte pages and another 512 bytes of flash EPROM on another two 256-byte pages. The flash EPROM is available to store user specific static data, such as serial numbers and system operational data, without modifying the program memory. The bq8015 provides flexible instruction memory for implementing a wide-variety of battery management functions. For better flash EPROM utilization, the bq8015 instruction memory is separated into two blocks. The first block is a 16k x 22 flash EPROM for custom user programs and the second block is a 4k x 22 mask ROM containing common programs such as the math and battery-management libraries, communication, and power-on reset routines. Refer to the bq8015 Mask ROM description for further details.

In addition, the 512 bytes of general-purpose SRAM can be powered by the RB pin of the bq8015 if power is lost. Typically, a capacitor provides the necessary voltage to the cells during inadvertent power loss. The RB pin can also be connected to a battery cell to provide power to the DATA RAM for longer periods. The RB pin operating current is less than 50 nA.

Figures 6 and 7 outline the bq8015 memory maps and show the address location of the internal registers. Further details about the bq8015 registers are in the register description section and Table 1, bq8015 Register and Peripheral Map.

# analog front end

The bq8015 features a precision analog front end ideal for battery monitoring and capacity measurement applications. Two analog-to-digital converters (ADCs) and a 12-channel multiplexer are available, allowing program flexibility. The first ADC is an integrating converter designed specifically for coulomb counting. The converter resolution is a function of how many samples are integrated: 16 samples for 10  $\mu$ V resolution. For example, 37.4  $\mu$ V can be resolved in 250 ms. Therefore, a 10  $\mu$ V signal is resolved in approximately 4 seconds. The second converter is a 15-bit delta sigma ADC for general-purpose measurements. This converter can be connected to one of eight multiple-purpose I/O pins, an internal temperature sensor, the current sense inputs, or the negative power supply. The 15-bit mode has a conversion time of 32 ms and the 10-bit mode has a conversion time of 2 ms. In either mode, a full 16 bits are returned from the converter for better averaging capability.

# I/O and specialized functions

The bq8015 provides a total of 24 memory-mapped I/O lines in three ports (A, B, C). These ports are used for data conversion, communication, external device power interface, external interrupt or wake, and general-purpose control functions.

The bq8015 provides two hardware communications ports. The first is the two-wire SMBus interface (SMBC and SMBD, dual function with RA6 and RA7). Together with the proper firmware, this communication port is compatible with the SMBus v1.1 protocol supporting packet error check (PEC) if enabled. The second communication is the single-wire HDQ serial interface (dual function with RA5). This pin can be made to support HDQ8 (8-bit) or HDQ16 (16-bit) protocols found on other bq gas gauge and battery management devices.

VOUT (Dual function with RA1) is a switch power supply of up to 5mA to an external device under bq8015 firmware control. This power supply reduces the system implementation requirements for powering devices external to the bq8015 and eliminates wasting the additional power when the external device is not needed.

## I/O and specialized functions (continued)

Clock out (32-kHz output) is dual-functioned with RC5. The 32-kHz output can be used to provide an accurate time base to external devices such as a lithium-ion protector IC without the cost of generating a new clock. The 32 kHz clock within the bq8015 simplifies the implementation.

The interrupt pin (dual function with RB0) provides a hardware means of interrupting the bq8015 during operation. The event pin (dual function with RB1) provides a hardware means of waking the bq8015 during sleep or hibernate modes. The inputs, if enabled, signal the CPU to resume from a HALT state.

Further information about the specialized port functions is given in the bq8015 device pin-out and pin descriptions. Using the special functions is detailed in the register map and register details section.

An internal temperature sensor is available on the bq8015 to reduce the cost, power, and size of the external components necessary to measure temperature. Scaled to –58.6 LSB/°C in the ADHI and ADLO registers, the internal temperature sensor is ideal for determining pack temperature during storage and the IC temperature during operations.

#### power consumption

The bq8015 core running from the mask ROM is capable of 1,700 MIPS/Watt in a 3 V system. Combined with other very low power analog peripherals, the bq8015 is ideal for embedded battery management applications. The bq8015 also provides three reduced-power modes for additional power savings. In the low-power mode, the CPU is halted but the PLL and clock oscillator are still operating. In the sleep mode, the CPU is halted, the PLL is off, and the clock oscillator is running. In this mode, the current is less than 8  $\mu$ A. In the hibernate-mode, the CPU is halted, and both the PLL and clock oscillator are turned off, reducing the current to less than 1  $\mu$ A.

#### mask ROM functions

The bq8015 default-state is with the flash EPROM programmed to all 1s. Upon powering up the bq8015 for the first time, the initialization routine is executed from the mask ROM. After initialization, the bq8015 defaults as an SMBus slave (address 16h). From this point, the flash instruction memory may be programmed. Once the flash programming is complete and the proper commands initiated, the bq8015 executes its program from the flash memory. During normal operation, the library commands in the mask ROM are still available for use.

Figure 9. Program Memory Register Map

Figure 10. Data Memory Map

# Table 1. bq8015 Register and Peripheral Map

|         | Ì        |                                     | Pood/ | Read/ Bit fields |        |         |         |         |          |           |          |

|---------|----------|-------------------------------------|-------|------------------|--------|---------|---------|---------|----------|-----------|----------|

| Address | Symbol   | Name                                | Write | 7 (MSB)          | 6      | 5       | 4       | 3       | 2        | 1         | 0 (LSB)  |

| 1000h   | SMBMA    | SMBus master<br>mode                | Write | SMBMA7           | SMBMA6 | SMBMA5  | SMBMA4  | SMBMA3  | SMBMA2   | SMBMA1    | R/W_B    |