# CA3020, CA3020A

8MHz Power Amps For Military, Industrial and Commercial Equipment

#### Features

November 2000

- High Power Output Class B Amplifier

- CA3020 ...... 0.5W (Typ) at V<sub>CC</sub> = 9V

- Wide Frequency Range . . Up to 8MHz with Resistive Loads

- Single Power Supply For Class B Operation With Transformer

- Built-In Temperature-Tracking Voltage Regulator Provides Stable Operation Over -55°C to 125°C Temperature Range

# **Applications**

- AF Power Amplifiers For Portable and Fixed Sound and Communications Systems

- · Servo-Control Amplifiers

- · Wide-Band Linear Mixers

- Video Power Amplifiers

- Transmission-Line Driver Amplifiers (Balanced and Unbalanced)

- Fan-In and Fan-Out Amplifiers For Computer Logic Circuits

- Lamp-Control Amplifiers

- Motor-Control Amplifiers

- · Power Multivibrators

- Power Switches

### Ordering Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE          | PKG.<br>NO. |

|-------------|---------------------|------------------|-------------|

| CA3020      | -55 to 125          | 12 Pin Metal Can | T12.B       |

| CA3020A     | -55 to 125          | 12 Pin Metal Can | T12.B       |

#### Description

The CA3020 and CA3020A are integrated-circuit, multistage, multipurpose, wide-band power amplifiers on a single monolithic silicon chip. They employ a highly versatile and stable direct coupled circuit configuration featuring wide frequency range, high voltage and power gain, and high power output. These features plus inherent stability over a wide temperature range make the CA3020 and CA3020A extremely useful for a wide variety of applications in military, industrial, and commercial equipment.

The CA3020 and CA3020A are particularly suited for service as class B power amplifiers. The CA3020A can provide a maximum power output of 1W from a 12V<sub>DC</sub> supply with a typical power gain of 75dB. The CA3020 provides 0.5W power output from a 9V supply with the same power gain.

Refer to AN5766 for application information.

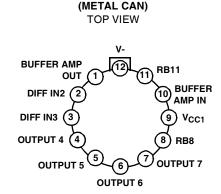

#### **Pinout**

CA3020

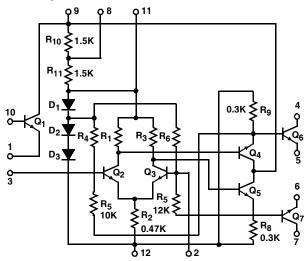

# Schematic Diagram

The resistance values included on the schematic diagram have been supplied as a convenience to assist Equipment Manufacturers in optimizing the selection of "outboard" components of equipment designs. The values shown may vary as much as  $\pm 30\%$ .

Intersil reserves the right to make any changes in the Resistance Values provided such changes do not adversely affect the published performance characteristics of the device.

#### CA3020, CA3020A

#### **Absolute Maximum Ratings**

####

#### **Operating Conditions**

Temperature Range . . . . . . -55°C to 125°C

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ ( $^{o}C/W$ )          |

|-----------------------------------------|----------------------|--------------------------------------|

| Metal Can Package                       | 165                  | 80                                   |

| Maximum Junction Temperature (Metal Car |                      |                                      |

| Maximum Storage Temperature Range .     | 65                   | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1   | 0s)                  | 300°C                                |

|                                         |                      |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. The voltage ratings for Pin 9, Pin 4 and Pin 7 are referenced to the V- (Pin 12). A normal bias configuration for Pin 8 and Pin 11 is shown in Figure 1B. Refer to Application Note AN5766 for other options.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications** $T_A = 25$ °C

|                                                                    |                                                | TEST CON              |                  |                  |     |        |      |         |      |      |       |

|--------------------------------------------------------------------|------------------------------------------------|-----------------------|------------------|------------------|-----|--------|------|---------|------|------|-------|

|                                                                    |                                                | CIRCUIT AND PROCEDURE | DC SU<br>VOL     | TAGE             |     | CA3020 | )    | CA3020A |      |      |       |

| PARAMETER                                                          | SYMBOL                                         | FIGURE                | V <sub>CC1</sub> | V <sub>CC2</sub> | MIN | TYP    | MAX  | MIN     | TYP  | MAX  | UNITS |

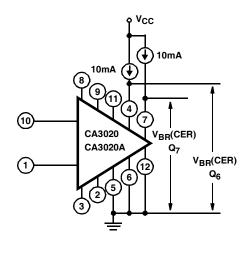

| Collector-to-Emitter Breakdown Voltage, $Q_6$ and $Q_7$ at 10mA    | V <sub>(BR)CER</sub>                           | 1A                    | -                | -                | 18  | -      | -    | 25      | -    | -    | V     |

| Collector-to-Emitter Breakdown<br>Voltage, Q <sub>1</sub> at 0.1mA | V <sub>(BR)CEO</sub>                           | -                     | -                | -                | 10  | -      | -    | 10      | -    | -    | V     |

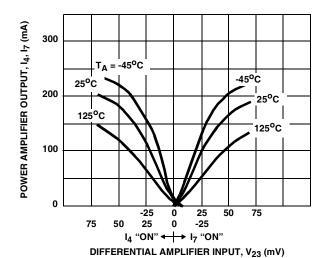

| Idle Currents, Q <sub>6</sub> and Q <sub>7</sub>                   | I <sub>4</sub> IDLE<br>I <sub>7</sub> IDLE     | 7                     | 9.0              | 2.0              | -   | 5.5    | -    | -       | 5.5  | -    | mA    |

| Peak Output Currents, Q <sub>6</sub> and Q <sub>7</sub>            | I <sub>4</sub> PK<br>I <sub>7</sub> PK         | 7                     | 9.0              | 2.0              | 140 | -      | -    | 180     | -    | -    | mA    |

| Cutoff Currents, Q <sub>6</sub> and Q <sub>7</sub>                 | I <sub>4</sub> CUTOFF<br>I <sub>7</sub> CUTOFF | 7                     | 9.0              | 2.0              | -   | -      | 1.0  | -       | -    | 1.0  | mA    |

| Differential Amplifier Current Drain                               | I <sub>CC1</sub>                               | 7                     | 9.0              | 9.0              | 6.3 | 9.4    | 12.5 | 6.3     | 9.4  | 12.5 | mA    |

| Total Current Drain                                                | I <sub>CC1</sub> + I <sub>CC2</sub>            | 7                     | 9.0              | 9.0              | 8.0 | 21.5   | 35.0 | 14.0    | 21.5 | 30.0 | mA    |

| Differential Amplifier Input<br>Terminal Voltages                  | V <sub>2</sub><br>V <sub>3</sub>               | 7                     | 9.0              | 2.0              | -   | 1.11   | -    | -       | 1.11 | -    | V     |

| Regulator Terminal Voltage                                         | V <sub>11</sub>                                | 7                     | 9.0              | 2.0              | -   | 2.35   | -    | -       | 2.35 | -    | V     |

| Q <sub>1</sub> Cutoff (Leakage) Currents:<br>Collector-to-Emitter  | I <sub>CEO</sub>                               |                       | 10.0             | -                | -   | -      | 100  | -       | -    | 100  | μΑ    |

| Emitter-to-Base                                                    | I <sub>EBO</sub>                               | 1 -                   | 3.0              | -                | -   | -      | 0.1  | -       | -    | 0.1  | μΑ    |

| Collector-to-Base                                                  | I <sub>CBO</sub>                               | 1                     | 3.0              | -                | -   | -      | 0.1  | -       | -    | 0.1  | μΑ    |

| Forward Current Transfer Ratio,<br>Q <sub>1</sub> at 3mA           | h <sub>FE1</sub>                               | -                     | 6.0              | -                | 30  | 75     | -    | 30      | 75   | -    |       |

| Bandwidth at -3dB Point                                            | BW                                             | 8                     | 6.0              | 6.0              | -   | 8      | -    | -       | 8    | -    | MHz   |

| Maximum Power Output for                                           | P <sub>O(MAX)</sub>                            | 9                     | 6.0              | 6.0              | 200 | 300    | -    | 200     | 300  | -    | mW    |

| $R_{CC} = 130\Omega$                                               |                                                | 9                     | 9.0              | 9.0              | 400 | 550    | -    | 400     | 550  | -    | mW    |

| Maximum Power Output for $R_{CC} = 200\Omega$                      |                                                | 9                     | 9.0              | 12.0             | -   | -      | -    | 800     | 1000 | -    | mW    |

| Sensitivity for $P_{OUT} = 400$ mW, $R_{CC} = 130\Omega$           | e <sub>IN</sub>                                | 9                     | 9.0              | 9.0              | -   | 35     | 55   | -       | -    | -    | mV    |

| Sensitivity for $P_{OUT} = 800 \text{mW}$ , $R_{CC} = 200 \Omega$  | eIN                                            | 9                     | 9.0              | 12.0             | -   | -      | -    | -       | 50   | 100  | mV    |

| Input Resistance -<br>Terminal 3 to Ground                         | R <sub>IN3</sub>                               | 10                    | 6.0              | 6.0              | -   | 1000   | -    | -       | 1000 | -    | Ω     |

**Typical Performance Data** (Note 3) A heat sink is recommended for high ambient temperature operation.

| PARAM                                             | METER                  | SYMBOL           | CA3020 | CA3020A | UNITS |

|---------------------------------------------------|------------------------|------------------|--------|---------|-------|

| Power Supply Voltage                              |                        | V <sub>CC1</sub> | 9.0    | 9.0     | V     |

|                                                   |                        | V <sub>CC2</sub> | 9.0    | 12.0    | V     |

| Zero Signal Current                               | Differential Amplifier | I <sub>CC1</sub> | 15     | 15      | mA    |

|                                                   | Output Amplifier       | I <sub>CC2</sub> | 24     | 24      | mA    |

| Maximum Signal Current                            | Differential Amplifier | I <sub>CC1</sub> | 16     | 16.6    | mA    |

|                                                   | Output Amplifier       | I <sub>CC2</sub> | 125    | 140     | mA    |

| Maximum Power Output at THD = 10%                 |                        | PO               | 550    | 1000    | mW    |

| Sensitivity                                       |                        | e <sub>IN</sub>  | 35     | 45      | mV    |

| Power Gain                                        |                        | G <sub>P</sub>   | 75     | 75      | dB    |

| Input Resistance                                  |                        | R <sub>IN</sub>  | 55     | 55      | kΩ    |

| Efficiency                                        |                        | η                | 45     | 55      | %     |

| Signal-to-Noise Ratio                             |                        | S/N              | 70     | 66      | dB    |

| THD at 150mW Level                                |                        |                  | 3.1    | 3.3     | %     |

| Test Signal Frequency from 600Ω Generator         |                        |                  | 1000   | 1000    | Hz    |

| Equivalent Collector-to-Collector Load Resistance |                        | R <sub>CC</sub>  | 130    | 200     | Ω     |

#### NOTE:

3. Refer to Figures 7 through 11 for measurement and symbol information.

# Test Circuits and Waveforms

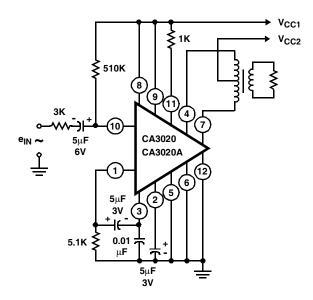

FIGURE 1B. TYPICAL AUDIO AMPLIFIER CIRCUIT UTILIZING

THE CA3020 OR CA3020A AS AN AUDIO

PREAMPLIFIER AND CLASS B POWER AMPLIFIER

FIGURE 1.

# Test Circuits and Waveforms (Continued)

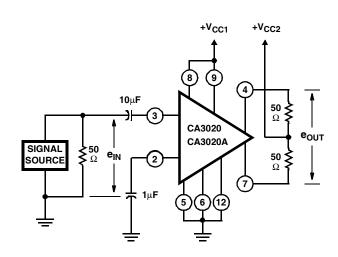

FIGURE 2A. TEST SETUP

FIGURE 2B. CHARACTERISTICS WITH R<sub>10</sub> SHORTED OUT

FIGURE 2. TYPICAL TRANSFER CHARACTERISTICS

FIGURE 3A. TEST SETUP

FIGURE 3B. CHARACTERISTIC WITH R<sub>10</sub> IN CIRCUIT

FIGURE 3. TYPICAL TRANSFER CHARACTERISTICS

FIGURE 4A. TEST SETUP

FIGURE 4B. CHARACTERISTIC

FIGURE 4. "MINIMUM DRIVE" TYPICAL CURRENT-VOLTAGE SATURATION CURVE

# Test Circuits and Waveforms (Continued)

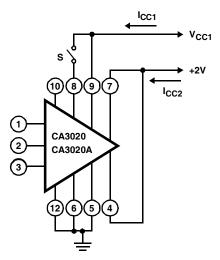

FIGURE 5A. TEST SETUP

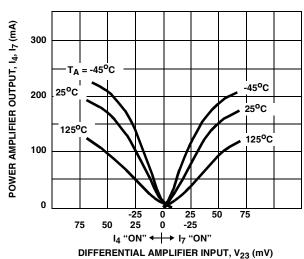

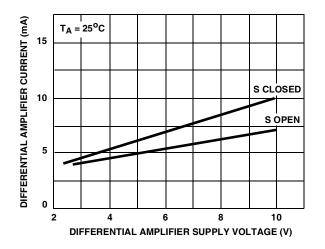

FIGURE 5B. DIFFERENTIAL AMPLIFIER CHARACTERISTICS

OF I<sub>CC1</sub> CURRENT vs V<sub>CC1</sub> VOLTAGE

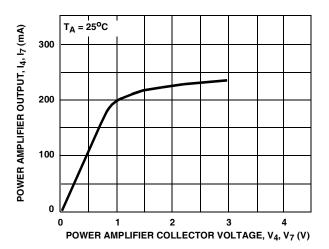

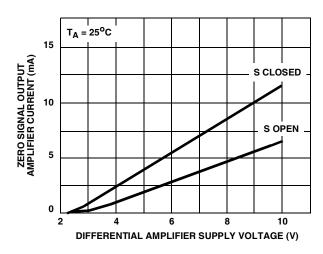

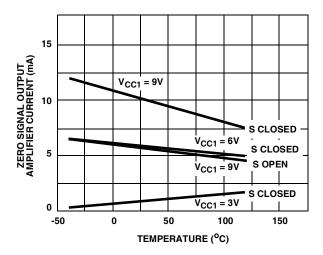

FIGURE 5C. OUTPUT AMPLIFIER CHARACTERISTICS OF  $I_{CC2}$  CURRENT vs  $V_{CC1}$  VOLTAGE FIGURE 5. ZERO SIGNAL AMPLIFIER CURRENT vs DIFFERENTIAL AMPLIFIER SUPPLY VOLTAGE

FIGURE 6A. TEST SETUP

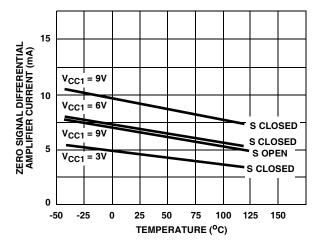

FIGURE 6B. DIFFERENTIAL AMPLIFIER CHARACTERISTICS

OF I<sub>CC1</sub> CURRENT vs AMBIENT TEMPERATURE

FIGURE 6. ZERO SIGNAL AMPLIFIER CURRENT VS AMBIENT TEMPERATURE

# Test Circuits and Waveforms (Continued)

FIGURE 6C. OUTPUT AMPLIFIER CHARACTERISTICS OF  $I_{CC2}$  CURRENT vs AMBIENT TEMPERATURE FIGURE 6. ZERO SIGNAL AMPLIFIER CURRENT vs AMBIENT TEMPERATURE

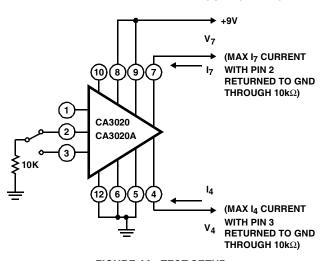

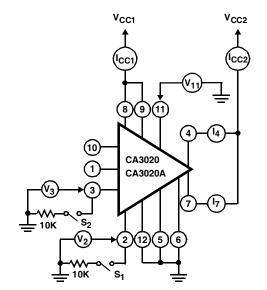

| CURRENTS OR<br>VOLTAGES | S <sub>1</sub> | s <sub>2</sub> |

|-------------------------|----------------|----------------|

| I <sub>4</sub> -IDLE    | OPEN           | OPEN           |

| I <sub>7</sub> -IDLE    | OPEN           | OPEN           |

| I <sub>4</sub> -PEAK    | OPEN           | CLOSE          |

| I <sub>7</sub> -PEAK    | CLOSE          | OPEN           |

| I <sub>4</sub> -CUTOFF  | CLOSE          | OPEN           |

| I <sub>7</sub> -CUTOFF  | OPEN           | CLOSE          |

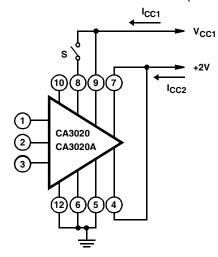

| CURRENTS OR<br>VOLTAGES | S <sub>1</sub> | S <sub>2</sub> |

|-------------------------|----------------|----------------|

| I <sub>CC1</sub>        | OPEN           | OPEN           |

| I <sub>CC2</sub>        | OPEN           | OPEN           |

| V <sub>2</sub>          | OPEN           | OPEN           |

| V <sub>3</sub>          | OPEN           | OPEN           |

| V <sub>11</sub>         | OPEN           | OPEN           |

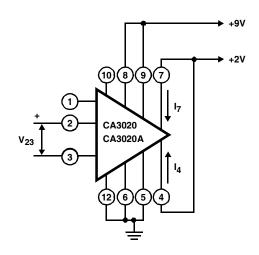

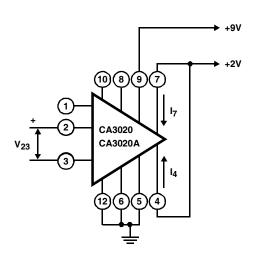

FIGURE 7. STATIC CURRENT AND VOLTAGE TEST CIRCUIT

#### PROCEDURES:

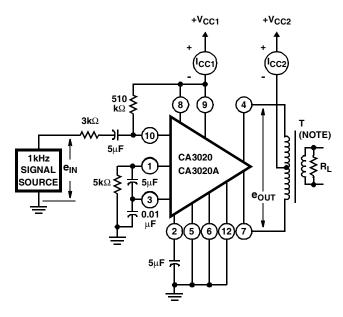

- 1. Apply desired value of V<sub>CC1</sub> and V<sub>CC2</sub>.

- 2. Apply 1kHz input signal and adjust for  $e_{IN} = 5mV_{RMS}$ .

- 3. Record the resulting value of eOUT in dB (reference

- 4. Vary input-signal frequency, keeping e<sub>IN</sub> constant at 5mV, and record frequencies above and below 1kHz at which eOUT decreases 3dB below reference value.

- 5. Record bandwidth as frequency range between -3dB

FIGURE 8. MEASUREMENT OF BANDWIDTH AT -3dB POINTS

NOTE: Push-pull output transformer; load resistance (R<sub>I</sub>) should be selected to provide indicated collector-to-collector load impedance  $(R_{CC}).$

#### **PROCEDURES:**

- 1. Apply desired value of  $V_{CC1}$  and  $V_{CC2}$  and reduce  $e_{\mbox{\scriptsize IN}}$  to

- 2. Record resulting values of  $I_{CC1}$  and  $I_{CC2}$  in mA as Zero-Signal DC Current Drain.

- 3. Apply desired value of  $V_{CC1}$  and  $V_{CC2}$  and adjust  $e_{IN}$  to the value at which the Total Harmonic Distortion in the output of the amplifier = 10%.

- 4. Record resulting value of I<sub>CC1</sub> and I<sub>CC2</sub> in mA as Maximum Signal DC Current Drain.

- 5. Determine resulting amplifier power output in watts and record as Maximum Power Output (POLIT).

- 6. Calculate Circuit Efficiency (η) in % as follows:

$$\eta = 100 \frac{P_{OUT}}{V_{CC1}^{I}CC1} + V_{CC2}^{I}CC2}$$

where  $P_{OUT}$  is in watts,  $V_{CC1}$  and  $V_{CC2}$  are in volts, and I<sub>CC1</sub> and I<sub>CC2</sub> are in amperes.

- 7. Record value of e<sub>IN</sub> in mV<sub>RMS</sub> required in Step 3 as Sensitivity (e<sub>IN</sub>).

- 8. Calculate Transducer Power Gain ( $G_p$ ) in dB as follows:  $G_p = 10log_{10} \frac{{}^POUT}{{}^PIN}$

$$G_p = 10log_{10} \frac{P_{OUT}}{P_{IN}}$$

where

$$P_{IN}(\text{in mW}) = \frac{e_{IN}2}{3000 + R_{IN(10)(Note 4)}}$$

NOTE:

4. See Figure 10 for definition of  $R_{IN(10)}$ .

FIGURE 9. MEASUREMENTS OF ZERO-SIGNAL DC CURRENT DRAIN, MAXIMUM-SIGNAL DC CURRENT DRAIN, MAXIMUM POWER OUTPUT, CIRCUIT EFFICIENCY, SENSITIVITY, AND TRANSDUCER POWER GAIN

# +V<sub>CC1</sub> +V<sub>CC2</sub> +V<sub>CC1</sub> +V<sub>CC2</sub> 510kΩ 8 9 4 7 CA3020 CA3020A SOURCE 0.01μF 5kΩ 2 5 6 (2)

#### PROCEDURES:

Input Resistance Terminal 10 to Ground (R<sub>IN10</sub>).

- 1. Apply desired value of  $V_{CC1}$  and  $V_{CC2}$  and set S in Position 1.

- 2. Adjust 1kHz input for desired signal level of measurement

- 3. Adjust R for  $e_2 = e_1/2$ .

- 4. Record resulting value of R as R<sub>IN10</sub>.

Input Resistance Terminal 3 to Ground (R<sub>IN3</sub>).

- 1. Apply desired value of  $V_{CC1}$  and  $V_{CC2}$  and set S in Position 2.

- 2. Adjust 1kHz input for desired signal level of measurement

- 3. Adjust R for  $e_2 = e_1/2$ .

- Record resulting value of R as R<sub>IN3</sub>.

FIGURE 10. MEASUREMENT OF INPUT RESISTANCE

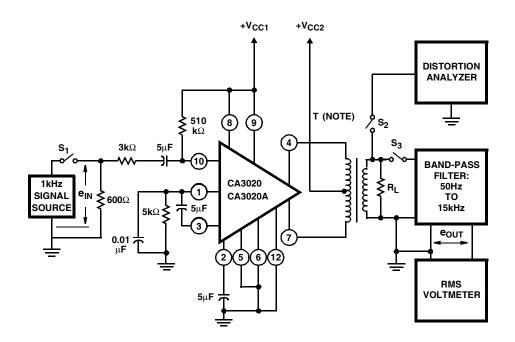

NOTE: Push-pull output transformer; load resistance ( $R_L$ ) should be selected to provide indicated collector-to-collector load impedance ( $R_{CC}$ ).

#### **PROCEDURES:**

Signal-to-Noise Ratio

- 1. Close S<sub>1</sub> and S<sub>3</sub>; open S<sub>2</sub>.

- 2. Apply desired values of  $V_{CC1}$  and  $V_{CC2}$ .

- 3. Adjust  $e_{IN}$  for an amplifier output of 150mW and record resulting value of  $E_{OUT}$  in dB as  $e_{OUT1}$  (reference value).

- 4. Open  ${\rm S_1}$  and record resulting value of  ${\rm e_{OUT}}$  in dB as  ${\rm e_{OUT2}}$

- 5. Signal-to-Noise Ratio  $(S/N) = 20log_{10} \frac{e_{OUT1}}{e_{OUT2}}$

Total Harmonic Distortion

- 1. Close S<sub>1</sub> and S<sub>2</sub>; open S<sub>3</sub>.

- 2. Apply desired values of  $V_{CC1}$  and  $V_{CC2}$ .

- 3. Adjust e<sub>IN</sub> for desired level amplifier output power.

- 4. Record Total Harmonic Distortion (THD) in %.

FIGURE 11. MEASUREMENT OF SIGNAL-TO-NOISE RATIO AND TOTAL HARMONIC DISTORTION

# CA3020, CA3020A

| All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice                                                                                                                                        |

| Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and rel                                                                                                                                           |

| able. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may recent from its use. No license is granted by implication or otherwise under any patent or patent girls of laterall or its subsidiaries. |

| result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.                                                                                                                                                                         |

| For information regarding Intersil Corporation and its products, see web site http://www.intersil.com                                                                                                                                                                                                             |