OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

NO RECOMMENDED 1-800-442-7747

Call Central Applications 1-800-442-000

Centapp@harris.com

# CD22354A, CD22357A

CMOS Single-Chip, Full-Feature PCM CODEC

February 1999

#### Features

- Meets or Exceeds All AT&T D3/D4 Specifications and CCITT Recommendations

- Complete CODEC and Filtering Systems: No External Components for Sample-and-Hold and Auto-Zero Functions. Receive Output Filter with (SIN X)/X Correction and Additional 8kHz Suppression

- Variable Data Clocks From 64kHz . . . . . . . . . . . . 2.1MHz

- Receiver Includes Power-Up Click Filter

- TTL or CMOS-Compatible Logic

- ESD Protection on All Inputs and Outputs

### **Applications**

- PABX

- Central Office Switching Systems

- · Accurate A/D and D/A Conversions

- Digital Telephones

- · Cellular Telephone Switching Systems

- Voice Scramblers Descramblers

- T1 Conference Bridges

- · Voice Storage and Retrieval Systems

- · Sound Based Security Systems

- Computerized Voice Analysis

- Mobile Radio Telephone Systems

- Microwave Telephone Networks

- Fiber-Optic Telephone Networks

### Description

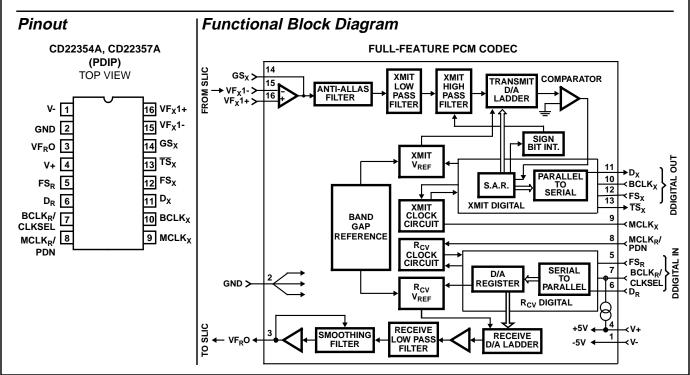

The CD22354A and CD22357A are monolithic silicongate, double-poly CMOS integrated circuits containing the band-limiting filters and the companding A/D and D/A conversion circuits that conform to the AT&T D3/D4 specifications and CCITT recommendations. The CD22354A provides the AT&T  $\mu\text{-law}$  and the CD22357A provides the CCITT A-law companding characteristic.

The primary applications for the CD22354A and CD22357A are in telephone systems. These circuits perform the analog and digital conversions between the subscriber loop and the PCM highway in a digital switching system. The functional block diagram is shown below.

With flexible features, including synchronous and asynchronous operations and variable data rates, the CD22354A and CD22357A are ideally suited for PABX, central office switching system, digital telephones as well as other applications that require accurate A/D and D/A conversions and minimal conversion time.

### Ordering Information

| PART<br>NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG. NO. |

|----------------|---------------------|------------|----------|

| CD22354AE      | -40 to 80           | 16 Ld PDIP | E16.3    |

| CD22357AE      | -40 to 80           | 16 Ld PDIP | E16.3    |

### **Absolute Maximum Ratings**

###

#### **Thermal Information**

| Maximum Junction Temperature                                 | 175°C |

|--------------------------------------------------------------|-------|

| Maximum Junction Temperature (Plastic Package)               |       |

| Maximum Storage Temperature Range (T <sub>STG</sub> )65°C to | 150°C |

| Maximum Lead Temperature (Soldering 10s)                     |       |

### **Operating Conditions**

| Operating-Temperature | Range (T <sub>A</sub> ) | 40°C to 80°C |

|-----------------------|-------------------------|--------------|

|                       |                         |              |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### **Electrical Specifications** At T<sub>A</sub> = 25°C

| PARAMETER                     | SYMBOL            | TEST CONDITIONS | MIN   | TYP | MAX   | UNITS |

|-------------------------------|-------------------|-----------------|-------|-----|-------|-------|

| STATIC SPECIFICATIONS         | -                 | -               |       |     |       |       |

| Positive Power Supply         | V+                |                 | 4.75  | 5   | 5.25  | V     |

| Negative Power Supply         | V-                |                 | -4.75 | -5  | -5.25 | V     |

| Power Dissipation (Operating) | P <sub>OPR</sub>  | V+ = 5V         | -     | 75  | 90    | mW    |

| Power Dissipation (Standby)   | P <sub>STBY</sub> | V- = -5V        | -     | 9   | 15    | mW    |

### **Electrical Specifications** At $T_A = 0^{\circ}C$ to $70^{\circ}C$ ; $V + = 5V \pm 5\%$ , $V - = -5V \pm 5\%$

| PARAMETER                      | SYMBOL           | TEST CONDITIONS                       | MIN  | TYP | MAX | UNITS |

|--------------------------------|------------------|---------------------------------------|------|-----|-----|-------|

| STATIC SPECIFICATIONS          |                  |                                       | •    |     |     |       |

| Analog Input Resistance        | R <sub>INA</sub> |                                       | 10   | -   | -   | ΜΩ    |

| Input Capacitance              | C <sub>IN</sub>  | All Logic and Analog Inputs           | -    | 5   | -   | pF    |

| Input Leakage Current, Digital | l <sub>l</sub>   | V <sub>I</sub> = 0V or V+             | -10  | -   | 10  | μΑ    |

| Low Level Input Voltage        | V <sub>IL</sub>  | $I_{IL} = \pm 10\mu A \text{ (Max)}$  | -    | -   | 0.8 | V     |

| High Level Input Voltage       | V <sub>IH</sub>  | $I_{IH} = \pm 10 \mu A \text{ (Max)}$ | 2    | -   | -   | V     |

| Low Level Output Voltage       | V <sub>OL</sub>  | I <sub>OL</sub> = 3.2mA               | -    | -   | 0.4 | V     |

| High Level Output Voltage      | V <sub>OH</sub>  | I <sub>OH</sub> = 1.0mA               | 2.4  | -   | -   | V     |

| Open State Output Current      | I <sub>OZ</sub>  | GND < D <sub>X</sub> < V+             | -10  | -   | 10  | μΑ    |

| Input Leakage Current, Analog  | l <sub>l</sub>   | -2.5V ≤ VF <sub>X</sub> < 2.5V        | -200 | -   | 200 | nA    |

**Electrical Specifications**  $V+ = 5V \pm 5\%$ ,  $V- = -5V \pm 5\%$ , BCLK<sub>R</sub> = BCLK<sub>X</sub> = MCLK<sub>X</sub> = 1.544MHz,  $V_{IN} = 0$ dBm0,  $T_A = 0$ °C to 70°C

| PARAMETER                                                         | SYMBOL          | TEST CONDITIONS                          | MIN   | TYP | MAX  | UNITS |

|-------------------------------------------------------------------|-----------------|------------------------------------------|-------|-----|------|-------|

| TRANSMIT AND RECEIVE FILTER T                                     | RANSFER CH      | HARACTERISTICS                           |       |     |      |       |

| Transmit Gain<br>(Relative to Gain at 1020Hz)                     | G <sub>RX</sub> | f = 16Hz                                 | -     | -   | -40  | dB    |

| Input Amplifier Set to Unity Gain                                 |                 | f = 50Hz                                 | -     | -   | -30  | dB    |

|                                                                   |                 | f = 60Hz                                 | -     | -   | -26  | dB    |

|                                                                   |                 | f = 200Hz                                | -1.8  | -   | -0.1 | dB    |

|                                                                   |                 | f = 300Hz to 3000Hz                      | -0.15 | -   | 0.15 | dB    |

|                                                                   |                 | f = 3300Hz                               | -0.35 | -   | 0.05 | dB    |

|                                                                   |                 | f = 3400Hz                               | -0.7  | -   | 0    | dB    |

|                                                                   |                 | f = 4000Hz                               | -     | -   | -14  | dB    |

|                                                                   |                 | f ≥ 4600Hz,<br>Measure 0 - 4kHz Response | -     | -   | -32  | dB    |

| Receive Gain                                                      | G <sub>RR</sub> | f = 0Hz to 3000Hz                        | -0.15 | -   | 0.15 | dB    |

| (Relative to Gain at 1020Hz)<br>(Includes (SIN X)/X Compensation) |                 | f = 3300Hz                               | -0.35 | -   | 0.05 | dB    |

|                                                                   |                 | f = 3400Hz                               | -0.9  | -   | 0    | dB    |

|                                                                   |                 | f = 4000Hz                               | -     | -   | -14  | dB    |

### **AC Specifications**

Unless otherwise specified, the following conditions apply:

$V+ = 5V \pm 5\%, V- = -5V \pm 5\%$

$\mathsf{GND}_\mathsf{A}$ ,  $\mathsf{GND}_\mathsf{D}$  = 0V,  $\mathsf{F}_\mathsf{FX}$  = 1020Hz at 0dBm0

Transmit input amplifier operating in a unity gain configuration

Temperature .......0°C to 70°C

Receive output is measured single-ended. All output levels are (SIN X)/X corrected.

### Definition

AMPLITUDE RESPONSE

Absolute Levels Definition:

$V_{REF} = -2.5V$

Nominal 0dBm0 level. . . . . . . . . . . . . . . . 4dBm into  $600\Omega$

1.2276V<sub>RMS</sub>

Maximum Overload Level:

Voltage reference (V<sub>REF</sub>) of -2.5V . . . . . . . . . . . . . 2.5V µ-Law 2.49V A-Law

### AC Specifications Encoding Format at $D_{\chi}$ Output

|                                                     |   | <b>CD22354A</b><br>μ <b>-LAW</b> |   |   |   | (INC | LUDES | CD22<br>A-L<br>S EVEN |   | NVERS | SION) |   |   |   |   |   |

|-----------------------------------------------------|---|----------------------------------|---|---|---|------|-------|-----------------------|---|-------|-------|---|---|---|---|---|

| $V_{IN}$ (at $GS_X$ ) = +Full-Scale                 | 1 | 0                                | 0 | 0 | 0 | 0    | 0     | 0                     | 1 | 0     | 1     | 0 | 1 | 0 | 1 | 0 |

| $V_{IN}$ (at $GS_X$ ) = 0V                          | 1 | 1                                | 1 | 1 | 1 | 1    | 1     | 1                     | 1 | 1     | 0     | 1 | 0 | 1 | 0 | 1 |

|                                                     | 0 | 1                                | 1 | 1 | 1 | 1    | 1     | 1                     | 0 | 1     | 0     | 1 | 0 | 1 | 0 | 1 |

| V <sub>IN</sub> (at GS <sub>X</sub> ) = -Full-Scale | 0 | 0                                | 0 | 0 | 0 | 0    | 0     | 0                     | 0 | 0     | 1     | 0 | 1 | 0 | 1 | 0 |

# **Electrical Specifications**

| PARAMETER                                              | SYMBOL                              | TEST CONDITIONS                                                  | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|-------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| AC DISTORTION                                          | •                                   |                                                                  |     |     |     |       |

| Signal to Total Distortion                             | STD <sub>X</sub> , STD <sub>R</sub> | Level = +3dBm0                                                   | 33  | -   | -   | dBc   |

| Xmit or R <sub>CV</sub>                                |                                     | Level = 0 to -30dBm0                                             | 36  | -   | -   | dBc   |

|                                                        |                                     | Level = -40dBm0                                                  | 30  | -   | -   | dBc   |

|                                                        |                                     | Level = -55dBm0, XMT                                             | 14  | -   | -   | dBc   |

|                                                        |                                     | Level = -55dBm0, R <sub>CV</sub>                                 | 15  | -   | -   | dBc   |

| Single Frequency Distortion<br>Xmit or R <sub>CV</sub> | SFD <sub>X</sub> , SFD <sub>R</sub> |                                                                  | -   | -   | -46 | dBc   |

| Intermodulation<br>(End-to-End Measurement)<br>2-Tone  | IMD                                 | V <sub>FX</sub> = -4dBm0 to -21dBm0<br>f1, f2 from 300 to 3400Hz | -   | -   | -41 | dB    |

| Transmit Delay, Absolute                               | t <sub>DAX</sub>                    | f = 1600Hz                                                       | -   | 280 | 315 | μs    |

| Transmit Envelope Delay                                | t <sub>DEX</sub>                    | f = 500-600Hz                                                    | -   | 170 | 220 | μs    |

| Relative to t <sub>DAX</sub>                           |                                     | f = 600-1000Hz                                                   | -   | 70  | 145 | μs    |

|                                                        |                                     | f = 1000-2600Hz                                                  | -   | 40  | 75  | μs    |

|                                                        |                                     | f = 2600-2800Hz                                                  | -   | 90  | 105 | μs    |

| Receive Delay, Absolute                                | t <sub>DAR</sub>                    | f = 1600Hz                                                       | -   | 180 | 200 | μs    |

| Receive Envelope Delay                                 | t <sub>DER</sub>                    | f = 500-600Hz                                                    | -40 | -25 | -   | μs    |

| Relative to t <sub>DAR</sub>                           |                                     | f = 600-1000Hz                                                   | -40 | -25 | -   | μs    |

|                                                        |                                     | f = 1000-2600Hz                                                  | -   | 60  | 90  | μs    |

|                                                        |                                     | f = 2600-2800Hz                                                  | -   | 110 | 125 | μs    |

# **Electrical Specifications**

| PARAMETER                                   | SYMBOL          | TEST CONDITIONS              | MIN | TYP | MAX  | UNITS |

|---------------------------------------------|-----------------|------------------------------|-----|-----|------|-------|

| AC GAIN TRACKING                            |                 |                              |     |     |      |       |

| Transmit Gain Tracking Error                | GTX             | +3 to -40dBm0                | -   | -   | ±0.2 | dB    |

|                                             |                 | -40 to -50dBm0               | -   | -   | ±0.4 | dB    |

|                                             |                 | -50 to -55dBm0               | -   | -   | ±1.2 | dB    |

| Receive Gain Tracking Error                 | GTR             | +3 to -40dBm0                | -   | -   | ±0.2 | dB    |

|                                             |                 | -40 to -50dBm0               | -   | -   | ±0.4 | dB    |

|                                             |                 | -50 to -55dBm0               | -   | -   | ±1.2 | dB    |

| Transmit Input Amplifier Gain,<br>Open Loop | A <sub>OL</sub> | $R_L \ge 1M\Omega$ at $GS_X$ | 68  | -   | -    | dB    |

# **Electrical Specifications** (Continued)

| PARAMETER                               | SYMBOL          | TEST CONDITIONS                                                                    | MIN   | TYP | MAX  | UNITS |

|-----------------------------------------|-----------------|------------------------------------------------------------------------------------|-------|-----|------|-------|

| Transmit Input Amplifier Gain,<br>Unity | A <sub>CL</sub> | Unity Gain Configuration Inverting or Non-Inverting $R_L \ge 10K$ , $C_L \le 50pF$ | -0.01 | -   | 0.01 | dB    |

| Transmit Gain, Absolute                 | G <sub>XA</sub> | $R_L \ge 10K$ , $C_L \le 50pF$                                                     | -0.15 | -   | 0.15 | dB    |

| Receive Gain, Absolute                  | G <sub>RA</sub> | $R_L \ge 600\Omega, C_L \le 500pF$                                                 | -0.15 | -   | 0.15 | dB    |

## **Electrical Specifications**

| PARAMETER                             | SYMBOL           | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNITS  |

|---------------------------------------|------------------|---------------------------------------------------------------------------------|-----|-----|-----|--------|

| AC NOISE                              |                  |                                                                                 | ·   |     |     |        |

| Transmit Noise                        | N <sub>X</sub>   | VF <sub>X</sub> I- = GND                                                        | -   | 12  | 15  | dBrnc0 |

|                                       |                  | VF <sub>X</sub> I+ = GND                                                        | -   | -74 | -67 | dBrn0p |

| Receive Noise                         | N <sub>R</sub>   | PCM Code Equivalent to 0V                                                       | -   | 7   | 11  | dBrnc0 |

|                                       |                  |                                                                                 | -   | -83 | -79 | dBrn0p |

| V+ Power Supply Rejection<br>Transmit | PSRR             | $VF_XI+ = 0V$ $V+ = 5V + (100mV_{RMS})$ $f = 0kHz \text{ to } 50kHz$            | 40  | -   | -   | dBc    |

| V- Power Supply Rejection<br>Transmit | PSRR             | $VF_XI$ - = 0V<br>V- = -5V + (100mV <sub>RMS</sub> )<br>f = 0kHz to 50kHz       | 40  | -   | -   | dBc    |

| V+ Power Supply Rejection<br>Receive  | PSRR             | PCM Code = All 1 Code<br>V+ = 5V + (100mV <sub>RMS</sub> )<br>f = 0kHz to 4kHz  | 40  | -   | -   | dBc    |

|                                       |                  | f = 4kHz to 25kHz                                                               | 37  | -   | -   | dB     |

|                                       |                  | f = 25kHz to 50kHz                                                              | 36  | -   | -   | dB     |

| V- Power Supply Rejection<br>Receive  | PSRR             | PCM Code = All 1 Code<br>V- = -5V + (100mV <sub>RMS</sub> )<br>f = 0kHz to 4kHz | 40  | -   | -   | dBc    |

|                                       |                  | f = 4kHz to 25kHz                                                               | 40  | -   | -   | dB     |

|                                       |                  | f = 25kHz to 50kHz                                                              | 36  | -   | -   | dB     |

| Cross Talk Transmit to Receive        | CT <sub>XR</sub> | VF <sub>X</sub> I- = 0dBm0 at 1020Hz                                            | -   | -80 | -70 | dB     |

| Cross Talk Receive to Transmit        | CT <sub>RX</sub> | $D_R = 0$ dBm0 at 1020Hz,<br>VF <sub>X</sub> I- = 0V                            | -   | -76 | -70 | dB     |

# **Electrical Specifications**

| PARAMETER                                                                                                                     | SYMBOL            | TEST CONDITIONS                                                       | MIN | TYP   | MAX    | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------|-----|-------|--------|-------|

| AC TIMING                                                                                                                     |                   | •                                                                     |     | •     |        |       |

| Frequency of Master Clocks                                                                                                    | 1/t <sub>PM</sub> | Depends on the Device Used                                            | -   | 1.536 | -      | MHz   |

|                                                                                                                               |                   | and the BCLK <sub>R</sub> /CLKSEL Pin                                 | -   | 1.544 | -      | MHz   |

|                                                                                                                               |                   | MCLK <sub>X</sub> and MCLK <sub>R</sub>                               | -   | 2.048 | -      | MHz   |

| Width of Master Clock High                                                                                                    | t <sub>WMH</sub>  | MCLK <sub>X</sub> and MCLK <sub>R</sub>                               | 160 | -     | -      | ns    |

| Width of Master Clock Low                                                                                                     | t <sub>WML</sub>  | MCLK <sub>X</sub> and MCLK <sub>R</sub>                               | 160 | -     | -      | ns    |

| Rise Time of Master Clock                                                                                                     | t <sub>RM</sub>   | MCLK <sub>X</sub> and MCLK <sub>R</sub>                               | -   | -     | 50     | ns    |

| Fall Time of Master Clock                                                                                                     | t <sub>FM</sub>   | MCLK <sub>X</sub> and MCLK <sub>R</sub>                               | -   | -     | 50     | ns    |

| Set-up Time from BCLK <sub>X</sub> High<br>(and FS <sub>X</sub> in Long Frame Sync<br>Mode) to MCLK <sub>X</sub> Falling Edge | t <sub>SBFM</sub> | First Bit Clock after the Leading Edge of FS <sub>X</sub>             | 100 | -     | -      | ns    |

| Period of Bit Clock                                                                                                           | t <sub>PB</sub>   |                                                                       | 485 | 488   | 15,725 | ns    |

| Width of Bit Clock High                                                                                                       | t <sub>WBH</sub>  | V <sub>IH</sub> = 2.2V                                                | 160 | -     | -      | ns    |

| Width of Bit Clock Low                                                                                                        | t <sub>WBL</sub>  | V <sub>IL</sub> = 0.6V                                                | 160 | -     | -      | ns    |

| Rise Time of Bit Clock                                                                                                        | t <sub>RB</sub>   | t <sub>PB</sub> = 488ns                                               | -   | -     | 50     | ns    |

| Fall Time of Bit Clock                                                                                                        | t <sub>FB</sub>   | t <sub>PB</sub> = 488ns                                               | -   | -     | 50     | ns    |

| Hold Time from Bit Clock Low to Frame Sync                                                                                    | t <sub>HBF</sub>  | Long Frame Only                                                       | 0   | -     | -      | ns    |

| Hold Time from Bit Clock High to Frame Sync                                                                                   | <sup>t</sup> HOLD | Short Frame Only                                                      | 0   | -     | -      | ns    |

| Set-up Time from Frame Sync to<br>Bit Clock Low                                                                               | t <sub>SFB</sub>  | Long Frame Only                                                       | 80  | -     | -      | ns    |

| Delay Time from BCLK <sub>X</sub> High to Data Valid                                                                          | t <sub>DBD</sub>  | Load = 150pF plus 2 LSTTL<br>Loads                                    | 0   | -     | 180    | ns    |

| Delay Time to $\overline{TS_X}$ Low                                                                                           | t <sub>XDP</sub>  | Load = 150pF plus 2 LSTTL<br>Loads                                    | -   | -     | 140    | ns    |

| Delay Time from BCLK <sub>X</sub> Low or FS <sub>X</sub> Low to Data Output Disabled                                          | t <sub>DZC</sub>  |                                                                       | 50  | -     | 165    | ns    |

| Delay Time to Valid Data from FS <sub>X</sub> or BCLK <sub>X</sub> , Whichever Comes Later                                    | t <sub>DZF</sub>  | C <sub>L</sub> = 0pF to 150pF                                         | 20  | -     | 165    | ns    |

| Set-up Time from $D_R$ Valid to $BCLK_{R/X}$ Low                                                                              | t <sub>SDB</sub>  |                                                                       | 50  | -     | -      | ns    |

| Hold Time from $\mathrm{BCLK}_{R/X}$ Low to $\mathrm{D}_R$ Invalid                                                            | t <sub>HBD</sub>  |                                                                       | 50  | -     | -      | ns    |

| Set-up Time from $FS_{X/R}$ to $BCLK_{X/R}$ Low                                                                               | t <sub>SF</sub>   | Short Frame Sync Pulse<br>(1 or 2 Bit Clock Periods Long)<br>(Note 1) | 50  | -     | -      | ns    |

| Hold Time from BCLK $_{X/R}$ Low to FS $_{X/R}$ Low                                                                           | t <sub>HF</sub>   | Short Frame Sync Pulse<br>(1 or 2 Bit Clock Periods Long)<br>(Note 1) | 100 | -     | -      | ns    |

# **Electrical Specifications** (Continued)

| PARAMETER                                                                                            | SYMBOL            | TEST CONDITIONS                                               | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------|-----|-----|-----|-------|

| Hold Time from 3rd Period of Bit<br>Clock Low to Frame Sync<br>(FS <sub>X</sub> or FS <sub>R</sub> ) | t <sub>HBFI</sub> | Long Frame Sync Pulse<br>(from 3 to 8-Bit Clock Periods Long) | 100 | -   | -   | ns    |

| Minimum Width of the Frame<br>Sync Pulse (Low Level)                                                 | t <sub>WFL</sub>  | 64K Bit/s Operating Mode                                      | 160 | -   | -   | ns    |

### NOTE:

# Pin Descriptions

| PIN NO. | SYMBOL                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                          |  |  |

|---------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | V-                             | Negative power supply, V- = -5V $\pm$ 5%.                                                                                                                                                                                                                                                                                            |  |  |

| 2       | GND                            | Analog and digital ground. All signals referenced to this pin.                                                                                                                                                                                                                                                                       |  |  |

| 3       | VF <sub>R</sub> O              | Analog output of RECEIVE FILTER.                                                                                                                                                                                                                                                                                                     |  |  |

| 4       | V+                             | Positive power supply, V+ = 5V ±5%.                                                                                                                                                                                                                                                                                                  |  |  |

| 5       | FS <sub>R</sub>                | Receive Frame Sync Pulse which enables $\mathrm{BCLK}_R$ to shift PCM data into $\mathrm{D}_R$ . FS $_R$ is an 8kHz PULSE TRAIN.                                                                                                                                                                                                     |  |  |

| 6       | D <sub>R</sub>                 | Receive Data Input. PCM data is shifted into $D_R$ following the $FS_R$ leading edge.                                                                                                                                                                                                                                                |  |  |

| 7       | BCLK <sub>R</sub> /CLK-<br>SEL | The Receive Bit Clock, which shifts data into $D_R$ after the frame sync leading edge, may vary from 64kHz to 2.048MHz. Alternatively, the leading edge may be a logic input which selects either 1.536MHz/1.544MHz or 2.048MHz for Master Clock in synchronous mode and BCLK $_X$ is used for both transmit and receive directions. |  |  |

| 8       | MCLK <sub>R</sub> /PDN         | Receive Master Clock. Must be 1.536MHz, 1.544MHz or 2.048MHz. May be asynchronous with MCLI but best performance is realized from synchronous operation. When this pin is continuously connect low, MCLK $_{\rm X}$ is selected for all internal timing. When this pin is continuously connected high, the device powered down.      |  |  |

| 9       | MCLK <sub>X</sub>              | Transmit Master Clock. Must be 1.536MHz, 1.544MHz or 2.048MHz. May be asynchronous with MCLK <sub>R</sub> , but best performance is realized from synchronous operation.                                                                                                                                                             |  |  |

| 10      | BCLK <sub>X</sub>              | The Bit Clock which shifts out the PCM Data on $D_X$ . May vary from 64kHz to 2.048MHz, but must be synchronous with MCLK $_X$ .                                                                                                                                                                                                     |  |  |

| 11      | D <sub>X</sub>                 | The THREE-STATE PCM Data Output which is enabled by FS <sub>X</sub> .                                                                                                                                                                                                                                                                |  |  |

| 12      | FS <sub>X</sub>                | Transmit Frame Sync Pulse input which enables $\mathrm{BCLK}_X$ to shift out the data on $\mathrm{D}_X$ . $\mathrm{FS}_X$ is an 8kHz PULSE TRAIN.                                                                                                                                                                                    |  |  |

| 13      | TS <sub>X</sub>                | Open drain output which pulses low during the encoder time slot.                                                                                                                                                                                                                                                                     |  |  |

| 14      | GS <sub>X</sub>                | Transmit gain adjust.                                                                                                                                                                                                                                                                                                                |  |  |

| 15      | VF <sub>X</sub> I-             | Inverting input of the transmit input amplifier.                                                                                                                                                                                                                                                                                     |  |  |

| 16      | VF <sub>X</sub> I+             | Non-inverting input of the transmit input amplifier.                                                                                                                                                                                                                                                                                 |  |  |

<sup>1.</sup> For short frame sync timing,  $FS_X$  and  $FS_R$  must go high while their respective bit clocks are high.

### **Functional Description**

### **Power Supply Sequencing**

Do not apply input signal or load on output before powering up  $V_{CC}$  supply. Care must be taken to ensure that  $D_X$  pin goes on common back plane (with other  $D_X$  pins from other chips).  $D_X$  pin cannot drive >50mA before Power-Up. This will cause the part to latch up.

#### Power-Up

When power is first applied, the Power-On reset circuitry initializes the CODEC and places it in a Power-Down mode. When the CODEC returns to an active state from the Power-Down mode, the receive output is muted briefly to minimize turn-on "click".

To power up the device, there are two methods available.

- A logical zero at MCLK<sub>R</sub>/PDN will power up the device, provided FS<sub>X</sub> or FS<sub>R</sub> pulses are present.

- 2. Alternatively, a clock (MCLK $_{\rm R}$ ) must be applied to MCLK $_{\rm R}$ / PDN and FS $_{\rm X}$  or FS $_{\rm R}$  pulses must be present.

#### Power-Down

Two power-down modes are available.

- A logical 1 at MCLK<sub>R</sub>/PDN, after approximately 0.5ms, will power down the device.

- 2. Alternatively, hold both  $FS_X$  and  $FS_R$  continuously low, the device will power down approximately 0.5ms after the last  $FS_X$  or  $FS_R$  pulse.

#### Synchronous Operation (Transmit and Receive Sections use the Same Master Clock)

The same master clock and bit-clock should be used for the receive and transmit sections.  $\mathrm{MCLK}_X$  (pin 9) is used to provide the master clock for the transmit section; the receive section will use the same master clock if the  $\mathrm{MCLK}_R/\mathrm{PDN}$  (pin 8) is grounded (synchronous operation), or at V+ (power-down mode).  $\mathrm{MCLK}_R/\mathrm{PDN}$  may be clocked only if a clock is provided at  $\mathrm{BCLK}_R/\mathrm{CLKSEL}$  (pin 7) as in asynchronous operation.

The BCLK $_{\rm X}$  (pin 10) is used to provide the bit clock to the transmit section. In synchronous operation, this bit clock is also used for the receive section if MCLK $_{\rm R}$ /PDN (pin 8) is grounded. BCLK $_{\rm R}$ /CLKSEL (pin 7) is then used to select the proper internal frequency division for 1.544MHz, 1.536MHz or 2.048MHz operation (see Table below). For 1.544MHz operation, the device automatically compensates for the 193rd clock pulse each frame.

Each FS $_X$  pulse begins the encoding cycle and the PCM data from the previous encode cycle is shifted out of the enabled D $_X$  output on the leading edge of BCLK $_X$ . After 8 bitclock periods, the tristate D $_X$  output is returned to a high impedance state. With an FS $_R$  pulse, PCM data is latched via the D $_R$  input on the negative edge of the BCLK $_X$ . FS $_X$  and FS $_R$  must be synchronous with MCLK $_X$ .

#### **CLOCKING OPTIONS**

|                             | BCLK <sub>R</sub> /CLKSEL | MASTER CLOCK<br>FREQUENCY SELECTED |                         |  |

|-----------------------------|---------------------------|------------------------------------|-------------------------|--|

| MODE                        | (PIN 7)                   | <b>CD22354A (</b> μ <b>)</b>       | CD22357A (A)            |  |

| Asynchronous or Synchronous | Clocked                   | 1.536MHz or<br>1.544MHz            | 2.048MHz                |  |

| Synchronous                 | 0                         | 2.048MHz                           | 1.536MHz or<br>1.544MHz |  |

| Synchronous                 | 1(or open circuit)        | 1.536MHz or<br>1.544MHz            | 2.048MHz                |  |

#### Asynchronous Operation (Transmit and Receive Sections use Separate Master Clocks)

For the CD22357A, the MCLK $_{\rm X}$  and MCLK $_{\rm R}$  must be 2.048MHz and for the CD22354A must be 1.536MHz or 1.544MHz. These clocks need not be synchronous. However, for best transmission performance, it is recommended that MCLK $_{\rm X}$  and MCLK $_{\rm R}$  be synchronous.

For 1.544MHz operation the device automatically compensates for the 193rd clock pulse each frame. FS $_{\rm X}$  starts the encoding operation and must be synchronous with MCLK $_{\rm X}$  and BCLK $_{\rm X}$ . FS $_{\rm R}$  starts the decoding operation and must be synchronous with BCLK $_{\rm R}$ . BCLK $_{\rm R}$  must be clocked in asynchronous operation. BCLK $_{\rm X}$  and BCLK $_{\rm R}$  may be between 64kHz - 2.04MHz.

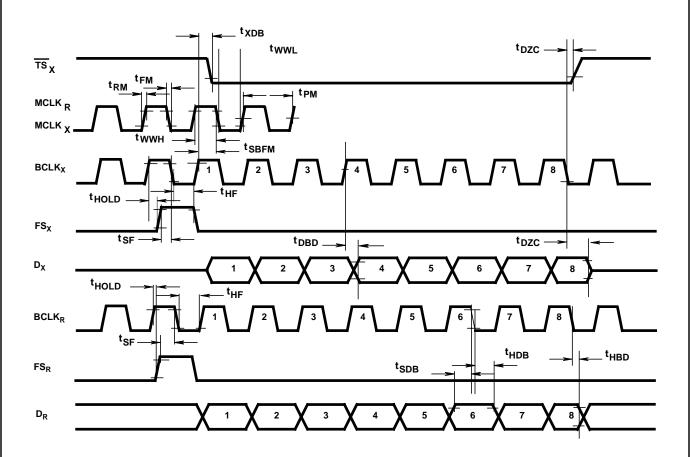

#### **Short-Frame Sync Mode**

When the power is first applied, the power initialization circuitry places the CODEC in a short-frame sync mode. In this mode both frame sync pulses must be 1 bit-clock period long, with the timing relationship shown in Figure 1.

With  $FS_X$  high during the falling edge of the  $BCLK_X$ , the next rising edge of  $BCLK_X$  enables the  $D_X$  tristate output buffer, which will output the sign bit. The following rising seven edges clock out the remaining seven bits upon which the next falling edge will disable the  $D_X$  output.

With  $FS_R$  high during the falling edge of the  $BCLK_R$  ( $BCLK_X$  in synchronous mode), the next falling edge of  $BCLK_R$  latches in the sign bit. The following seven edges latch in the seven remaining bits.

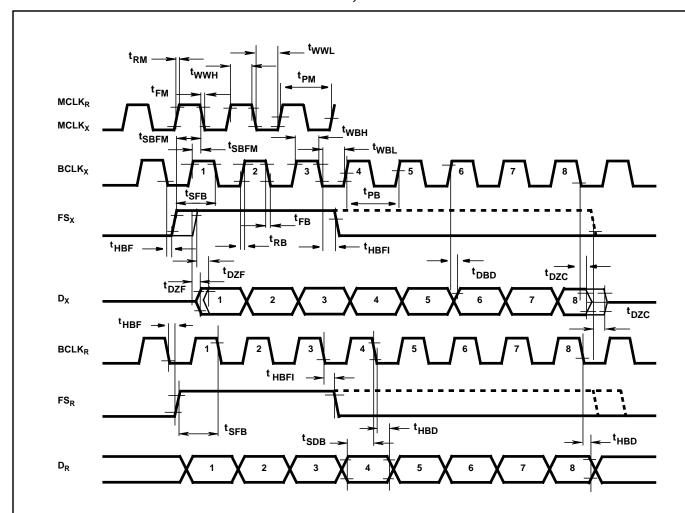

#### Long-Frame Sync Mode

In this mode of operation, both of the frame sync pulses must be three or more bit-clock periods long with the timing relationship shown in Figure 2.

Based on the transmit frame sync  $FS_X$ , the CODEC will sense whether short or long-frame sync pulses are being used.

For 64kHz operation the frame sync pulse must be kept low for a minimum of 160ns.

The  $D_X$  tristate output buffer is enabled with the rising edge of  $FS_X$  or the rising edge of the  $BCLK_X$ , whichever comes later and the first bit clocked out is the sign bit. The following seven rising edges of the  $BCLK_X$  clock out the remaining seven bits. The  $D_X$  output is disabled by the next falling edge of the  $BCLK_X$  following the 8th rising edge or by  $FS_X$  going low whichever comes later.

A rising edge on the receive frame sync,  $FS_R$ , will cause the PCM data at  $D_R$  to be latched in on the next falling edge of the BCLK $_R$ . The remaining seven bits are latched on the successive seven falling edges of the bit-clock (BCLK $_X$  in synchronous mode).

#### **Transmit Section**

The transmit section consists of a gain-adjustable input opamp, an anti-aliasing filter, a low-pass filter, a high-pass filter and a compressing A/D converter. The input op-amp drives a RC active anti-aliasing filter. This filter eliminates the need for any off-chip filtering as it provides 30dB attenuation (Min) at the sampling frequency. From this filter the signal enters a 5th order low-pass filter clocked at 128kHz, followed by a 3rd order high-pass filter clock at 32kHz. The output of the high-pass filter directly drives the encoder capacitor ladder at an 8kHz sampling rate. A precision voltage reference is trimmed in manufacturing to provide an input overload of nominally 2.5V<sub>PEAK</sub>. Transmit frame sync

pulse  $FS_X$  controls the process. The 8-bit PCM data is clocked out at  $D_X$  by the BCLK $_X$ . BCLK $_X$  can be varied from 64kHz to 2.048MHz.

#### **Receive Section**

The receive section consists of an expanding D/A converter and a low-pass filter which fulfills both the AT&T D3/D4 specifications and CCITT recommendations. PCM data enters the receive section at  $D_R$  upon the occurrence of  $FS_R$ , Receive Frame sync pulse. BCLK $_R$ , Receive Data Clock, which can range from 64kHz to 2.048MHz, clocks the 8-bit PCM data into the receive data register. A D/A conversion is performed on the 8-bit PCM data and the corresponding analog signal is held on the D/A capacitor ladder. This signal is transferred to a switched capacitor low-pass filter clocked at 128kHz to smooth the sample-and-hold signal as well as to compensate for the (SIN X)/X distortion.

The filter is then followed by a second order Sallen and Key active filter capable of driving a  $600\Omega$  load to a level of 7.2dBm.

FIGURE 1. SHORT FRAME-SYNC TIMING

FIGURE 2. LONG FRAME-SYNC TIMING