# **CXD1198AQ**

# **CD-ROM Subcode Decoder**

## **Description**

The CXD1198AQ is a CD-ROM subcode decoder LSI.

#### **Features**

- Real time error correction of subcodes

- Connection possible with DRAM up to 1 MB as buffer memory

- · Automatic generation of sync patterns

- Error pointer buffering function (separated mode, mixed mode)

- 4 MB/s maximum rate for transferring data with SCSI control LSI

## **Applications**

**CD-ROM** drives

#### **Structure**

Silicon gate CMOS IC

## **Absolute Maximum Ratings** (Ta=25 °C)

| <ul> <li>Supply voltage</li> </ul>      | Vcc  | -0.5 to $+7.0$               | V  |

|-----------------------------------------|------|------------------------------|----|

| <ul> <li>Input voltage</li> </ul>       | Vı   | -0.5 to V <sub>DD</sub> +0.5 | V  |

| <ul> <li>Output voltage</li> </ul>      | Vo   | -0.5 to V <sub>DD</sub> +0.5 | V  |

| • Operating temperature                 | Topr | -20 to +75                   | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg | -55 to +150                  | °C |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>        | VDD  | $5.0 \pm 0.5$ | V  |

|-------------------------------------------|------|---------------|----|

| <ul> <li>Operating temperature</li> </ul> | Topr | -20 to +75    | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

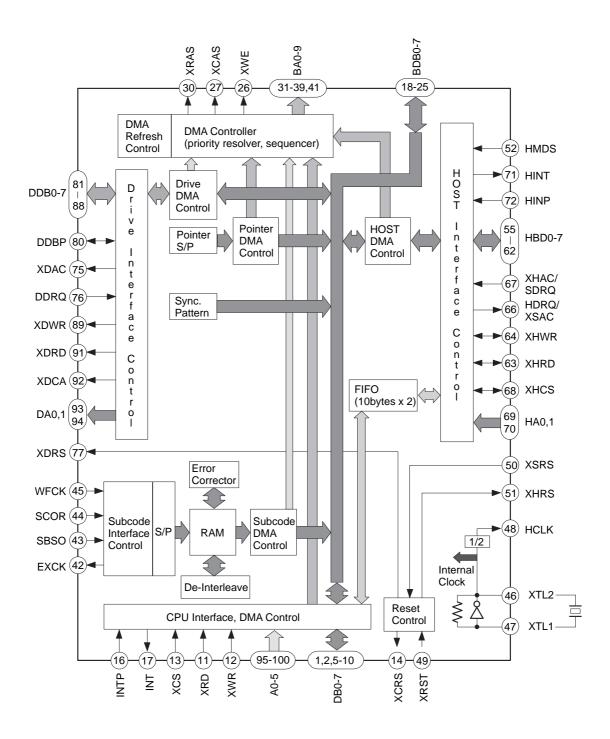

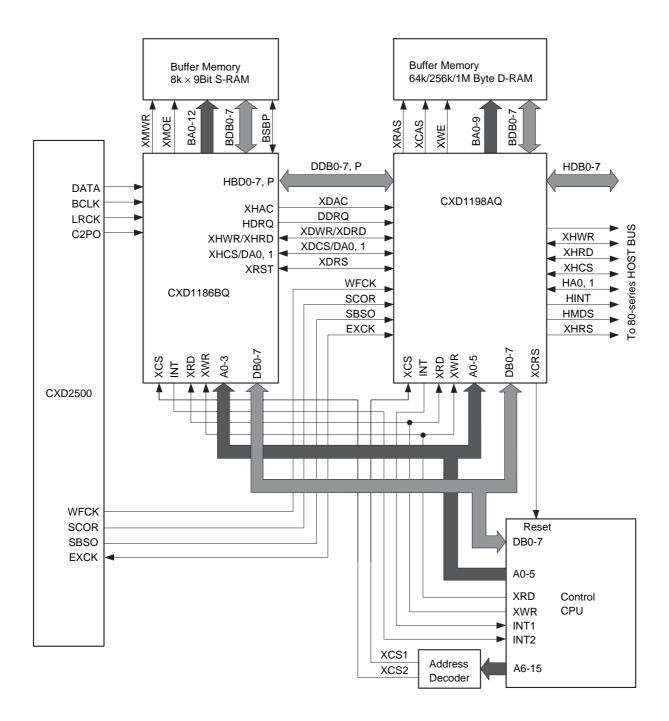

#### **Block Diagram**

# **Pin Description**

| Pin No. | Symbol | I/O | Description                                                      |

|---------|--------|-----|------------------------------------------------------------------|

| 1       | DB0    | I/O | CPU data bus                                                     |

| 2       | DB1    | I/O | CPU data bus                                                     |

| 3       | Vdd    |     | Power supply (+5 V)                                              |

| 4       | Vss    |     | GND                                                              |

| 5       | DB2    | I/O | CPU data bus                                                     |

| 6       | DB3    | I/O | CPU data bus                                                     |

| 7       | DB4    | I/O | CPU data bus                                                     |

| 8       | DB5    | I/O | CPU data bus                                                     |

| 9       | DB6    | I/O | CPU data bus                                                     |

| 10      | DB7    | I/O | CPU data bus                                                     |

| 11      | XRD    | I   | Register read strobe negative logic signal in this IC            |

| 12      | XWR    | I   | Register write strobe negative logic signal in this IC           |

| 13      | XCS    | I   | Chip select signal to this IC                                    |

| 14      | XCRS   | 0   | Reset negative logic signal to CPU                               |

| 15      | Vss    |     | GND                                                              |

| 16      | INTP   | I   | INT signal polarity control input signal                         |

| 17      | INT    | 0   | Interrupt request signal to CPU                                  |

| 18      | BDB0   | I/O | Buffer memory data bus                                           |

| 19      | BDB1   | I/O | Buffer memory data bus                                           |

| 20      | BDB2   | I/O | Buffer memory data bus                                           |

| 21      | BDB3   | I/O | Buffer memory data bus                                           |

| 22      | BDB4   | I/O | Buffer memory data bus                                           |

| 23      | BDB5   | I/O | Buffer memory data bus                                           |

| 24      | BDB6   | I/O | Buffer memory data bus                                           |

| 25      | BDB7   | I/O | Buffer memory data bus                                           |

| 26      | XWE    | 0   | Strobe negative logic signal for writing in buffer memory        |

| 27      | XCAS   | 0   | Strobe negative logic signal for column address in buffer memory |

| 28      | Vdd    |     | Power supply (+5 V)                                              |

| 29      | Vss    |     | GND                                                              |

| 30      | XRAS   | 0   | Strobe negative logic signal for row address in buffer memory    |

| 31      | BA0    | 0   | Buffer memory address                                            |

| 32      | BA1    | 0   | Buffer memory address                                            |

| 33      | BA2    | 0   | Buffer memory address                                            |

| 34      | BA3    | 0   | Buffer memory address                                            |

| Pin No.           | Symbol | I/O | Description                                                            |

|-------------------|--------|-----|------------------------------------------------------------------------|

| 35                | BA4    | 0   | Buffer memory address                                                  |

| 36                | BA5    | 0   | Buffer memory address                                                  |

| 37                | BA6    | 0   | Buffer memory address                                                  |

| 38                | BA7    | 0   | Buffer memory address                                                  |

| 39                | BA8    | 0   | Buffer memory address                                                  |

| 40                | Vss    |     | GND                                                                    |

| 41                | BA9    | 0   | Buffer memory address                                                  |

| 42                | EXCK   | 0   | Subcode data readout clock output signal to the CXD2500                |

| 43                | SBSI   | I   | Subcode data input signal from the CXD2500                             |

| 44                | SBSY   | I   | Subcode frame sync input signal from the CXD2500                       |

| 45                | WFCK   | I   | Write frame clock input signal from the CXD2500                        |

| 46                | XTL2   | 0   | Crystal oscillator circuit output                                      |

| 47                | XTL1   | I   | Crystal oscillator circuit input                                       |

| 48                | HCLK   | 0   | Crystal 1/2 frequency-divided clock output                             |

| 49                | XRST   | I   | Reset negative logic input signal                                      |

| 50                | XSRS   | I   | SCSI bus reset negative logic input signal                             |

| 51                | XHRS   | 0   | Reset negative logic output signal to host                             |

| 52                | HMDS   | 1   | Host mode select input signal                                          |

| 53                | Vdd    |     | Power supply (+5 V)                                                    |

| 54                | Vss    |     | GND                                                                    |

| 55                | HDB7   | I/O | Host data bus                                                          |

| 56                | HDB6   | I/O | Host data bus                                                          |

| 57                | HDB5   | I/O | Host data bus                                                          |

| 58                | HDB4   | I/O | Host data bus                                                          |

| 59                | HDB3   | I/O | Host data bus                                                          |

| 60                | HDB2   | I/O | Host data bus                                                          |

| 61                | HDB1   | I/O | Host data bus                                                          |

| 62                | HDB0   | I/O | Host data bus                                                          |

| 63                | XHRD   | I/O | Data read strobe signal from host or to SCSI control IC                |

| 64                | XHWR   | I/O | Data write strobe signal from host or to SCSI control IC               |

| 65                | Vss    |     | GND                                                                    |

| 66 HDRQ O /XSAC O |        | 0   | Data request positive logic signal to host or DMA acknowledge negative |

|                   |        |     | logic signal to SCSI control IC                                        |

| 67                | XHAC   | 1   | DMA acknowledge negative logic signal from host or data request        |

|                   | /SDRQ  | 1   | positive logic signal from SCSI control IC                             |

| Pin No. | Symbol | I/O | Description                                                           |

|---------|--------|-----|-----------------------------------------------------------------------|

| 68      | XHCS   | 1   | Chip select input signal from host                                    |

| 69      | HA0    | 1   | Host address signal                                                   |

| 70      | HA1    | I   | Host address signal                                                   |

| 71      | HINT   | 0   | Interrupt request signal to host                                      |

| 72      | HINP   | 1   | HINT signal polarity control input signal                             |

| 73      | NC1    | 0   | No connection; leave open.                                            |

| 74      | NC2    | 0   | No connection; leave open.                                            |

| 75      | XDAC   | 0   | DMA acknowledge negative logic signal to the CXD1186BQ                |

| 76      | DDRQ   | I   | Data request positive logic signal from the CXD1186BQ                 |

| 77      | XDRS   | 0   | Reset negative logic signal to the CXD1186BQ                          |

| 78      | Vdd    |     | Power supply (+5 V)                                                   |

| 79      | Vss    |     | GND                                                                   |

| 80      | DDBP   | I/O | Error pointer bus connected with the CXD1186BQ                        |

| 81      | DDB7   | I/O | Data bus connected with the CXD1186BQ                                 |

| 82      | DDB6   | I/O | Data bus connected with the CXD1186BQ                                 |

| 83      | DDB5   | I/O | Data bus connected with the CXD1186BQ                                 |

| 84      | DDB4   | I/O | Data bus connected with the CXD1186BQ                                 |

| 85      | DDB3   | I/O | Data bus connected with the CXD1186BQ                                 |

| 86      | DDB2   | I/O | Data bus connected with the CXD1186BQ                                 |

| 87      | DDB1   | I/O | Data bus connected with the CXD1186BQ                                 |

| 88      | DDB0   | I/O | Data bus connected with the CXD1186BQ                                 |

| 89      | XDWR   | 0   | Host register write strobe negative logic signal to the CXD1186BQ     |

| 90      | Vss    |     | GND                                                                   |

| 91      | XDRD   | 0   | Host register read strobe negative logic signal to the CXD1186BQ      |

| 92      | XDCS   | 0   | Chip select negative logic signal for host register read/write to the |

| 92      | ADGS   | O   | CXD1186BQ                                                             |

| 93      | DA1    | 0   | Address signal to the CXD1186BQ                                       |

| 94      | DA0    | 0   | Address signal to the CXD1186BQ                                       |

| 95      | A5     | I   | CPU address signal                                                    |

| 96      | A4     | I   | CPU address signal                                                    |

| 97      | А3     | I   | CPU address signal                                                    |

| 98      | A2     | I   | CPU address signal                                                    |

| 99      | A1     | I   | CPU address signal                                                    |

| 100     | A0     | I   | CPU address signal                                                    |

#### **Electrical Characteristics**

#### **DC** characteristics

(VDD=5.0±0.5 V, Vss=0 V, Topr=-20 to +75 °C)

| Item              |             | Symbol        | Conditions | Min.           | Тур.               | Max.               | Unit               |    |

|-------------------|-------------|---------------|------------|----------------|--------------------|--------------------|--------------------|----|

| TTL input voltage |             | High level    | VIH1       |                | 2.2                |                    |                    | V  |

|                   |             | Low level     | VIL1       |                |                    |                    | 0.8                | V  |

| CMOS input vol    | tage        | High level    | VIH2       |                | 0.7Vdd             |                    |                    | V  |

|                   |             | Low level     | VIL2       |                |                    |                    | 0.3Vdd             | V  |

| Input current of  | pull-up inp | out           | lıL        | VIL=0 V        | -40                | -100               | -240               | μA |

| Input current of  | pull-down   | input         | lін        | VIH=VDD        | 40                 | 100                | 240                | μA |

| CMOS Schmitt      |             | High level    | Vt+        |                | 0.8VDD             |                    |                    | V  |

| input voltage     |             | Low level     | Vt-        |                |                    |                    | 0.2Vdd             | V  |

|                   | Hysteres    | sis           | Vt+-Vt-    |                |                    | 0.6                |                    | V  |

| Output voltage    |             | High level    | Voн1       | Iон1=-2 mA     | VDD-0.8            |                    |                    | V  |

|                   |             | Low level     | Vol1       | IoL1=4 mA      |                    |                    | 0.4                | V  |

| Charge pump       |             | High level    | Voh2       | Iон2=-6 mA     | VDD-0.8            |                    |                    | V  |

| output voltage    |             | Low level     | VOL2       | IoL2=4 mA      |                    |                    | 0.4                | V  |

| Oscillation cell  | Input       | High level    | VIH3       |                | 0.7Vdd             |                    |                    | V  |

|                   | voltage     | Low level     | VIL3       |                |                    |                    | 0.3Vdd             | V  |

|                   | Logic the   | reshold       | LVth       |                |                    | V <sub>DD</sub> /2 |                    | V  |

| Feedbac           |             | ck resistance | RfB        | VIN=Vss or VDD | 250 k              | 1 M                | 2.5 M              | Ω  |

|                   | Output      | High level    | Vонз       | Iонз=-3 mA     | V <sub>DD</sub> /2 |                    |                    | V  |

|                   | voltage     | Low level     | Vol3       | Іоцз=3 mA      |                    |                    | V <sub>DD</sub> /2 | V  |

CMOS input pins : DDRQ, SBSY, SBSI, A5 to 0, XWR, XRD, XCS, INTP

CMOS Schmitt input pins : WFCK, XRST

Pull-up input pins : XHCS, HA1, HA0

PUII-down input pin : HMDS

Charge pump output pins : HINT, BA9 to 0

Oscillation cell input pin : XTL1

Oscillation cell output pin : XTL2

The characteristics for all other pins follow the TTL input and output voltage items. All bidirectional data buses are pulled up by standard 25 k $\Omega$  resistance.

## Input/output capacitance

VDD=Vi=0 V, f=1 MHz

| Item       | Symbol | Min. | Тур. | Max. | Unit |

|------------|--------|------|------|------|------|

| Input pin  | CIN    |      |      | 9    | pF   |

| Output pin | COUT   |      |      | 11   | pF   |

| I/O pin    | CI/O   |      |      | 11   | pF   |

## **AC** characteristics

(Ta=-20 to +75 °C, VDD=5 V±10 %, output load=75 pF, f≤24 MHz)

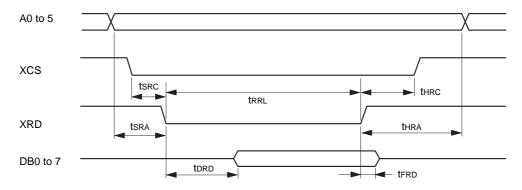

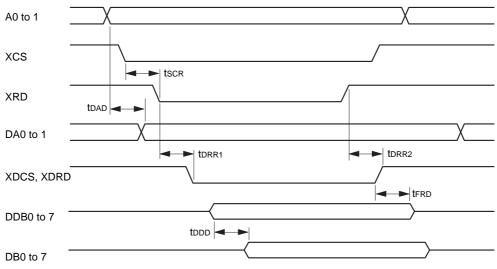

# 1. CPU interface

# (1) Read

| Item                              | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|------|------|------|------|

| Address setup time (vs. XRD↓)     | tsra   | 20   |      |      | ns   |

| Chip select setup time (vs. XRD↓) | tsrc   | 0    |      |      | ns   |

| Data delay time (vs. XRD↓)        | tdrd   |      |      | 80   | ns   |

| Data float time (vs. XRD↑)        | tfrd   | 3    |      | 10   | ns   |

| Chip select hold time (vs. XRD↑)  | thrc   | 0    |      |      | ns   |

| Address hold time (vs. XRD↑)      | thra   | 0    |      |      | ns   |

| Low-level XRD pulse width         | trrl   | 100  |      |      | ns   |

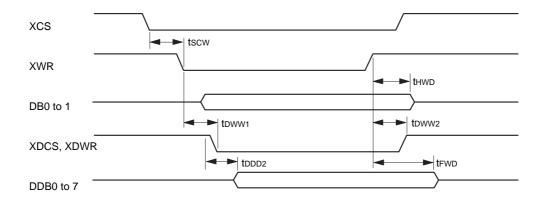

| Item                              | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|------|------|------|------|

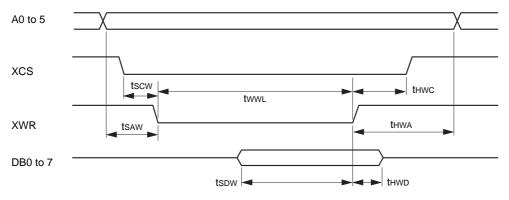

| Address setup time (vs. XWR↓)     | tsaw   | 20   |      |      | ns   |

| Chip select setup time (vs. XWR↓) | tscw   | 0    |      |      | ns   |

| Data setup time (vs. XWR↓)        | tsdw   | 40   |      |      | ns   |

| Data hold time (vs. XWR↑)         | thwp   | 10   |      |      | ns   |

| Chip select hold time (vs. XWR↑)  | thwc   | 0    |      |      | ns   |

| Address hold time (vs. XWR↑)      | thwa   | 0    |      |      | ns   |

| Low-level XWR pulse width         | twwL   | 50   |      |      | ns   |

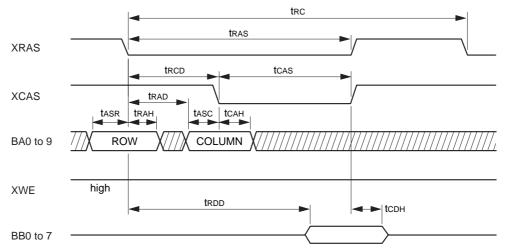

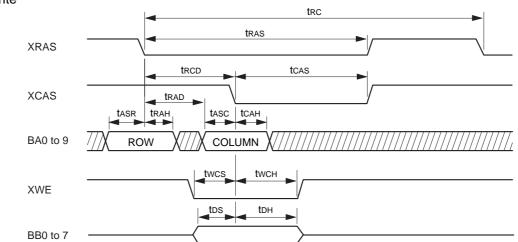

## 2. DRAM interface

# (1) Read

# (2) Write

| Item                          | Symbol | Min.   | Тур. | Max.    | Unit |

|-------------------------------|--------|--------|------|---------|------|

| Random read/write cycle time  | trc    |        | 4Tw  |         | ns   |

| RAS pulse width               | tras   | 2Tw+5  |      | 2Tw+19  | ns   |

| RAS/CAS delay time            | trcd   |        | Tw   |         | ns   |

| CAS pulse width               | tcas   | Tw+5   |      | Tw+19   | ns   |

| RAS/column address delay time | trad   | Tw/2+5 |      | Tw/2+17 | ns   |

| Row address setup time        | tasr   | 10     |      |         | ns   |

| Row address hold time         | trah   | Tw/2   |      |         | ns   |

| Column address setup time     | tasc   | 0      |      |         | ns   |

| Column address hold time      | tcah   | Tw/2   |      |         | ns   |

| Delay time from RAS           | trdd   |        |      | 2TW     | ns   |

| Hold time from CAS            | tcdh   | 0      |      |         | ns   |

| Write command setup time      | twcs   | 10     |      |         | ns   |

| Write command hold time       | twch   | 20     |      |         | ns   |

| Data output setup time        | tos    | 10     |      |         | ns   |

| Data output hold time         | tон    | 20     |      |         | ns   |

Tw is 1/f here.

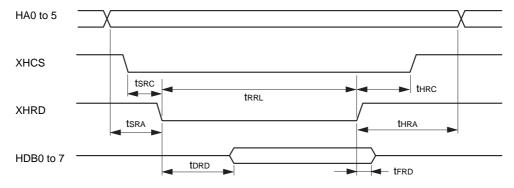

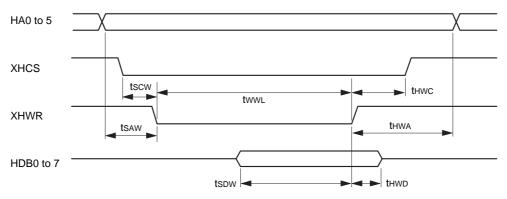

# 3. Host interface

# (1) Read

| Item                               | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XHRD↓)     | tsra   | 20   |      |      | ns   |

| Chip select setup time (vs. XHRD↓) | tsrc   | 0    |      |      | ns   |

| Data delay time (vs. XHRD↓)        | tord   |      |      | 70   | ns   |

| Data float time (vs. XHRD↑)        | tfRD   | 2    |      |      | ns   |

| Chip select hold time (vs. XHRD↑)  | tHRC   | 0    |      |      | ns   |

| Address hold time (vs. XHRD↑)      | thra   | 0    |      |      | ns   |

| Low-level XHRD pulse width         | trrl   | 100  |      |      | ns   |

| Item                               | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XHWR↓)     | tsaw   | 20   |      |      | ns   |

| Chip select setup time (vs. XHWR↓) | tscw   | 0    |      |      | ns   |

| Data setup time (vs. XHWR↓)        | tsow   | 40   |      |      | ns   |

| Data hold time (vs. XHWR↑)         | thwd   | 10   |      |      | ns   |

| Chip select hold time (vs. XHWR↑)  | thwc   | 0    |      |      | ns   |

| Address hold time (vs. XHWR↑)      | thwa   | 0    |      |      | ns   |

| Low-level XHWR pulse width         | twwL   | 50   |      |      | ns   |

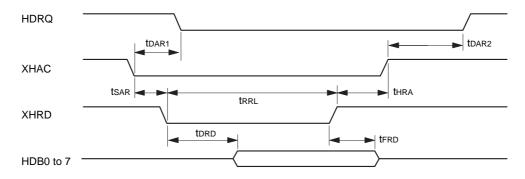

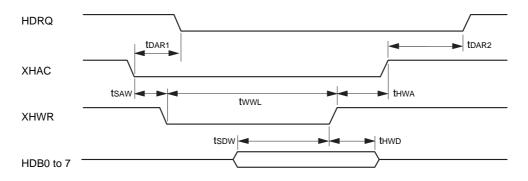

# 4. Host DMA cycle (80-series bus)

# (1) Read

| Item                        | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------|------|------|------|

| HDRQ fall time (vs. XHAC↓)  | tDAR1  |      |      | 35   | ns   |

| HDRQ rise time (vs. XHAC↑)  | tDAR2  |      |      | 55   | ns   |

| XHAC setup time (vs. XHRD↓) | tsar   | 0    |      |      | ns   |

| XHAC hold time (vs. XHRD↑)  | thra   | 0    |      |      | ns   |

| Low-level XHRD pulse width  | trrl   | 100  |      |      | ns   |

| Data delay time (vs. XHRD↓) | tord   |      |      | 70   | ns   |

| Data float time (vs. XHRD↑) | tfrd   | 0    |      |      | ns   |

| Item                        | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------|------|------|------|

| HDRQ fall time (vs. XHAC↓)  | tDAR1  |      |      | 35   | ns   |

| HDRQ rise time (vs. XHAC↑)  | tDAR2  |      |      | 55   | ns   |

| XHAC setup time (vs. XHWR↓) | tsaw   | 0    |      |      | ns   |

| XHAC hold time (vs. XHWR↑)  | thwa   | 0    |      |      | ns   |

| Low-level XHWR pulse width  | twwL   | 50   |      |      | ns   |

| Data setup time (vs. XHWR↓) | tsdw   | 40   |      |      | ns   |

| Data float time (vs. XHWR↑) | thwd   | 10   |      |      | ns   |

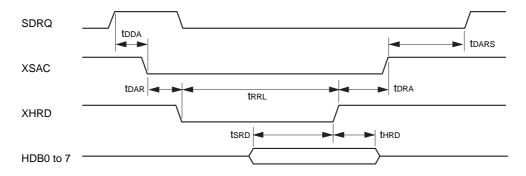

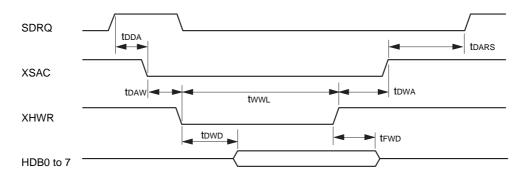

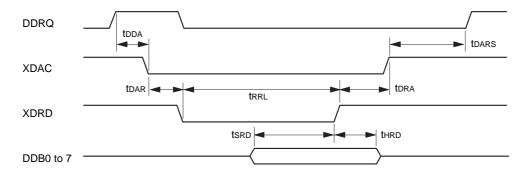

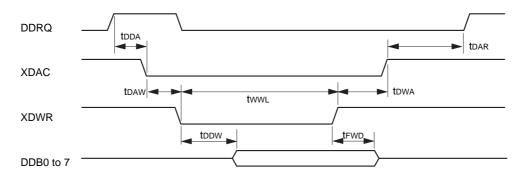

# 5. Host DMA cycle (SCSI bus)

# (1) Read

| Item                        | Symbol | Min. | Тур. | Max.  | Unit |

|-----------------------------|--------|------|------|-------|------|

| XSAC fall time (vs. SDRQ↓)  | tdda   |      |      | Tw+31 | ns   |

| HDRQ cycle time (vs. XSAC↑) | tdars  |      |      | Tw    | ns   |

| XHRD delay time (vs. XSAC↑) | tdar   |      | 0    |       | ns   |

| XSAC delay time (vs. XHRD↑) | tdra   |      | 23   |       | ns   |

| Low-level XHRD pulse width  | trrl   |      | 2Tw  |       | ns   |

| Data setup time (vs. XHRD↑) | tsrd   | 15   |      |       | ns   |

| Data hold time (vs. XHRD↑)  | thrd   | 5    |      |       | ns   |

Twis 1/f here.

| Item                                    | Symbol | Min. | Тур. | Max.  | Unit |

|-----------------------------------------|--------|------|------|-------|------|

| XSAC fall time (vs. SDRQ↓)              | tdda   |      |      | Tw+31 | ns   |

| SDRQ rise time (vs. XSAC <sup>↑</sup> ) | tdars  |      |      | Tw    | ns   |

| XHWR delay time (vs. XSAC↓)             | tdaw   |      |      | 0     | ns   |

| XSAC delay time (vs. XHWR↑)             | towa   |      | 24   |       | ns   |

| Low-level XHWR pulse width              | twwL   |      | 2Tw  |       | ns   |

| Data delay time (vs. XHWR↓)             | towo   |      |      | 38    | ns   |

| Data float time (vs. XHWR↑)             | trwd   | 10   |      |       | ns   |

Twis 1/f here.

# 6. Drive interface

(1) Read

(2) Write

| Item                                     | Symbol       | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------------|------|------|------|------|

| Drive address delay time (vs. A1 to 0)   | <b>t</b> DAD |      |      | 45   | ns   |

| Chip select setup time (vs. XRD↓)        | tscr         | 0    |      |      | ns   |

| Drive read signal delay time (vs. XRD↓)  | tDRR1        |      |      | 35   | ns   |

| CPU data delay time (vs. DDB0 to 7)      | todo         |      |      | 70   | ns   |

| Drive read signal delay time (vs. XRD↑)  | tDDR2        |      | 27   |      | ns   |

| Data float time (vs. XDRD↑)              | tfrd         | 0    |      |      | ns   |

| Chip select setup time (vs. XWR↓)        | tscw         | 0    |      |      | ns   |

| Drive write signal delay time (vs. XWR↓) | tDWW1        |      |      | 30   | ns   |

| Data delay time (vs. DB0 to 7)           | tDDD2        |      |      | 70   | ns   |

| Data hold time (vs. XWR↑)                | thwp         | 10   |      |      | ns   |

| Drive write signal delay time (vs. XWR↑) | tDWW2        |      | 24   |      | ns   |

| Data float time (vs. XWR↑)               | trwd         | Tw   |      |      | ns   |

Tw is 1/f here.

# 7. Drive DMA cycle

# (1) Read

| Item                        | Symbol       | Min. | Тур.   | Max.  | Unit |

|-----------------------------|--------------|------|--------|-------|------|

| XDAC fall time (vs. DDRQ↑)  | <b>t</b> dda |      |        | Tw+32 | ns   |

| DDRQ cycle time (vs. XDAC↑) | tdars        |      |        | TW    | ns   |

| XDRD delay time (vs. XDAC↓) | tdar         |      |        | 8     | ns   |

| XDAC delay time (vs. XDRD↑) | <b>t</b> dra | 0    |        | Tw-5  | ns   |

| Low-level XDRD pulse width  | trrl         |      | 2Tw+10 |       | ns   |

| Data setup time (vs. XDRD↓) | tsrd         | 25   |        |       | ns   |

| Data hold time (vs. XDRD↓)  | thrd         | 0    |        |       | ns   |

Twis 1/f here.

| Item                        | Symbol | Min.  | Тур. | Max.   | Unit |

|-----------------------------|--------|-------|------|--------|------|

| XDAC fall time (vs. DDRQ↑)  | tdda   |       |      | Tw+32  | ns   |

| DDRQ rise time (vs. XDAC↑)  | tdars  |       |      | Tw     | ns   |

| XDWR delay time (vs. XDAC↓) | tdaw   |       |      | 5      | ns   |

| XDAC delay time (vs. XDWR↑) | towa   |       |      | Tw     | ns   |

| Low-level XDWR pulse width  | twwL   | 2Tw+5 |      | 2Tw+18 | ns   |

| Data delay time (vs. XDWR↓) | todw   |       |      | 60     | ns   |

| Data float time (vs. XDWR↑) | trwd   | 10    |      |        | ns   |

Twis 1/f here.

## **Description of Functions**

## 1. Pin description

1-1. Drive interface (16 pins)

(1) DDB0 to 7 (Drive Data Bus: bidirectional)

Data bus input/output signals connected with the CXD1186BQ; connected to the HDB0 to 7 pins of the CXD1186BQ.

(2) DDBP (Drive Data Pointer : bidirectional)

Error pointer input/output signal connected with the CXD1186BQ; connected to the HDBE pin of the CXD1186BQ.

(3) XDCS (Drive Chip Select : negative logic output)

Chip select negative logic output signal for reading/writing host interface registers of the CXD1186BQ; connected to the XHCS pin of the CXD1186BQ. The host interface registers of the CXD1186BQ are mapped in 20H to 23H within register address space (00H to 3FH) of this IC.

(4) XDWR (Drive Write Strobe : negative logic output)

Strobe negative logic output signal for writing data into host interface registers of the CXD1186BQ; connected to the XHWR pin of the CXD1186BQ.

(5) XDRD (Drive Read Strobe : negative logic output)

Strobe negative logic output signal for reading data into host interface registers of the CXD1186BQ; connected to the XHRD pin of the CXD1186BQ.

(6) DA0, 1 (Drive Address : output)

Address output signals to the CXD1186BQ; connected to the HA0 and 1 pins of the CXD1186BQ.

(7) DDRQ (Drive DMA Request : positive logic input)

DMA request input signal from the CXD1186BQ; connected to the HDRQ pin of the CXD1186BQ.

(8) XDAC (Drive Acknowledge : negative logic output)

DMA acknowledge negative logic output signal to the CXD1186BQ in response to DDRQ; connected to the XHAC pin of the CXD1186BQ.

1-2. Host interface (18pins)

(1) HDB0 to 7 (Host Data Bus: bidirectional)

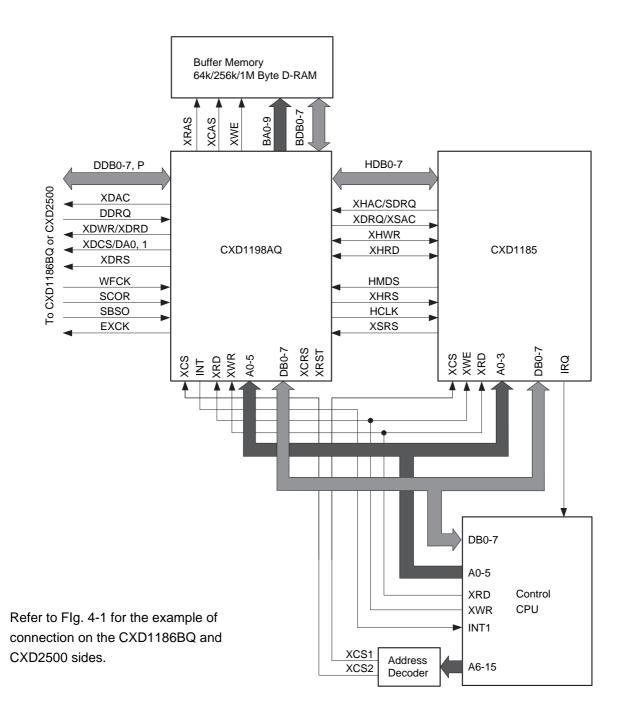

Data bus input/output signals connected with host or SCSI control LSI (CXD1185); connected to the D0 to 7 pins for the SCSI control LSI (CXD1185).

(2) HMDS (Host Mode Select : input)

Input signal for selecting host mode. When connected with Intel 80-series CPU bus, set to low or open; when connected with the SCSI control LSI (CXD1185), set to high.

SONY CXD1198AQ

(3) HDRQ/XSAC (Host DMA Request/SCSI DMA Acknowledge : output)

HMDS = low: DMA request positive logic signal to host

HMDS = high: DMA acknowledge negative logic signal to SCSI control LSI (CXD1185)

(4) XHAC/SDRQ (Host DMA Acknowledge/SCSI DMA Request : input)

HMDS = low: DMA acknowledge negative logic signal from host

HMDS = high: DMA request positive logic signal from SCSI control LSI (CXD1185)

(5) XHWR (Host Write Strobe : negative logic input/output)

HMDS = low: Data write strobe negative logic input signal from host

HMDS = high: Data write strobe negative logic output signal to SCSI control LSI (CXD1185);

connected to the /WED pin of SCSI control LSI (CXD1185)

(6) XHRD (Host Read Strobe : negative logic input/output)

HMDS = low: Data read strobe negative logic input signal from host

HMDS = high: Data read strobe negative logic output signal to SCSI control LSI (CXD1185);

connected to the /RED pin of SCSI control LSI (CXD1185)

(7) XHCS (Host Chip Select : negative logic input)

Pulled up by standard 50 k $\Omega$  resistance in the IC.

HMDS = low: Chip select negative logic input signal of host

HMDS = high: Not used; set to high or open

(8) HA0, 1 (Host Address : inputs)

Pulled up by standard 50 k $\Omega$  resistance in the IC. HMDS = low: Address input signal from host HMDS = high: Not used; set to high or open

(9) HINT (Host Interrupt : output)

Open drain output.

HMDS = low: Interrupt request signal to host

HMDS = high: Not used

(10) HINP (Host Interrupt Polarity: input)

Selects the polarity of the HINT signal; set to low when the HINT signal turns to Low active and high when it turns to High active.

1-3. Buffer Memory Interface (21 pins)

(1) BDB0 to 7 (Buffer Data Bus: input/output)

Buffer memory data bus signals

(2) BA0 to 9 (Buffer Address : output)

Buffer memory address signals; the addresses are output to different pins depending on the setting value of Bits 2 and 3 (Buffer Memory Size) of the Configuration Register: to BA0 to 7 at 64 kB, to BA0 to 8 at 256 kB and to BA0 to 9 at 1 MB.

SONY

CXD1198AQ

(3) XRAS (Row Address Strobe : negative logic output)

Strobe negative logic output signal for row address in dynamic RAM.

(4) XCAS (Column Address Strobe : negative logic output)

Strobe negative logic output signal for column address in dynamic RAM.

(5) XWE (Write Enable : negative logic output)

Strobe negative logic output signal for writing in dynamic RAM.

(Note) Use a DRAM with an access time of 80 ns or less in this IC.

#### 1-4. Subcode Interface (4 pins)

(1) WFCK (Write Frame Clock: input) Write frame clock input signal from the CXD2500; connected to the WFCK pin of the CXD2500.

(2) <u>SBSY</u> (Subcode Sync : positive logic input)

Subcode frame sync input signal from the CXD2500; connected to the SCOR pin of the CXD2500.

(3) <u>SBSI</u> (Subcode Serial Input: input) Channel P-W subcode data input signal from the CXD2500; connected to the SBSO pin of the CXD2500.

(4) <u>EXCK</u> (External Clock : output) Readout clock signal to the CXD2500 for reading channel P-W subcode data input to SBSI; connected to the EXCK pin of the CXD2500.

## 1-5. CPU Interface (19 pins)

(1) <u>DB0 to 7</u> (CPU Data Bus : input/output) 8-bit CPU data bus signals

(2) A0 to 5 (CPU Address: input)

Address input signals for selecting this IC internal register and the host interface registers of the CXD1186BQ from the CPU

(3) XWR (CPU Write : negative logic input)

Strobe negative logic input signal for the CPU to write data into this IC internal register and the host interface registers of the CXD1186BQ.

(4) XRD (CPU Read : negative logic input)

Strobe negative logic input signal for the CPU to read data from this IC internal register and the host interface registers of the CXD1186BQ.

(5) XCS (Chip Select : negative logic input)

Chip select negative logic input signal for the CPU to read/write data with the register in this IC and the host interface registers of the CXD1186BQ.

(6) <u>INT</u> (CPU Interrupt : output) Interrupt request signal to CPU

(7) INTP (CPU Interrupt Polarity: input)

Selects the polarity of the INT signal; set to low when the INT signal turns to Low active and high when it turns to High active.

- 1-6. Clock Signals (3 pins)

- (1) XTL1 (X'tal1: input)

- (2) XTL2 (X'tal2 : output)

Inserts a crystal oscillator with a 24 MHZ oscillation frequency between the XTL1 and XTL2 pins. Alternatively, inputs a 24 MHZ clock signal to the XTL1 pin.

(3) HCLK (Half Clock : output)

Half frequency divided clock of XTL2.

- 1-7. Reset Signals (5 pins)

- (1) XRST (Reset : negative logic input)

Power on reset negative logic input signal

(2) XSRS (SCSI Bus Reset : negative logic input)

SCSI bus reset negative logic input signal

(3) XCRS (CPU Reset : negative logic output)

Reset negative logic output signal to the CPU; it is low in either of the cases below.

- 1) XRST = Low

- 2) XSRS = low

- (4) XHRS (SCSI Reset : negative logic output)

Reset negative logic output signal to the SCSI LSI (CXD1185); it is low in any of the cases below.

- 1) XRST = Low

- 2) XSRS = low

- 3) SCSI reset bit (Bit 2) of reset control register = high

- (5) XDRS (Drive Reset : negative logic output)

Reset negative logic output signal to drive block; it is low either of the cases below.

- 1) XRST = low

- 2) Drive reset bit (Bit 1) of reset control register = high

## 2. Description of Register Functions

#### 2-1. Write Registers

## (1) Reset Control Register (00H)

Bit 0: BMM Reset

When this bit is "1", all the circuits in this IC except for this register and the HCLK frequency divider circuit are initialized. This bit is automatically set to "0" after the IC has been initialized.

Bit 1: Drive Reset

When this bit is "1", the XDRS pin is set to low (activated).

Bit 2: SCSI Reset

When this bit is "1", the XSRS pin is set to low (activated).

Bit 3: Reserved

Bit 4: Reserved

Bit 5: Reserved

Bit 6: Reserved

Bit 7: Reserved

#### (2) DMA Control Register-1 (01H)

Bit 0: Drive DMA Enable

DMA with the CXD1186BQ is enabled when "1" is written in this bit.

Bit 1: Drive DMA Source

Selects the transfer direction of DMA with the CXD1186BQ: when "0", data is transferred from the buffer memory to the CXD1186BQ and when "1", from the CXD1186BQ to the buffer memory. This bit is valid only when Bits 0 is "1".

Bit 2: Error Pointer Transfer Enable

When this bit is "1", the error pointers are written into the buffer memory together with the main channel data. This bit is valid only when Bits 0 and 1 are both "1".

Bit 3: Error Pointer Transfer Mode

Selects the format for writing the error pointers into the buffer memory. When "0", all the error pointers starting from the address selected by the Pointer DMA Address Counter are written separately from the main channel data (separated mode). When "1", 1 byte of the error pointer is written immediately after 8-byte of the main channel data (mixed mode). (The value of Pointer DMA Address Counter is ignored in this case.) This bit is valid only when Bits 0, 1 and 2 are all "1".

Bit 4: Sync Pattern Enable

When this bit is "1" a 12-byte dummy sync pattern is written starting with the address selected by the Drive DMA Address Counter before the data is written from the CXD1186BQ into the buffer memory. (It is assumed in this case that the error pointer of the sync byte is "0".) This bit is valid only when Bits 0 and 1 are both "1".

Bit 5: Reserved Bit 6: Reserved Bit 7: Reserved

## (3) DMA Control Register-2 (02H)

Bit 0: Host DMA Enable

DMA with the host is enabled when "1" is written in this bit.

Bit 1: Host DMA Source

Selects the transfer direction of DMA with the host: when "0", from the buffer memory to the host; and when "1", from the host to the buffer memory. This bit is valid only when Bit 0 is "1".

Bit 2: CPU DMA Enable

DMA with the CPU is enabled via the CPU DMA Data Register when "1" is written in this bit.

Bit 3: CPU DMA Source

Selects the transfer direction of DMA with the CPU: when "0", data is transferred from the buffer memory to the CPU DMA Data Register; and when "1", from the CPU DMA Data Register to the buffer memory. This bit is valid only when Bit 2 is "1".

Bit 4: Subcode P-W Decode Enable

Decoding of the channel P-W subcode from the CXD2500 is enabled when this bit is "1". Subcodes are decoded inside this IC.

Bit 5: Subcode P-W DMA Enable

The channel P-W subcodes decoded inside this IC can be written into the buffer memory when "1". However, even when this bit is "1", DMA will commence 3 sectors after Bit 4 has been set to "1".

Bit 6: Subcode P-W ECC Enable

When this bit is "1", errors in the channel R-W subcodes are corrected. This bit is a valid only when Bit 4 is "1".

Bit 7: Subcode P-W ECC Strategy

When this bit is "1", double correction is provided while the channel R-W subcodes are corrected. This bit is valid only when Bit 4 is "1".

#### (4) CPU DMA Data Register (03H)

Data is written into this register when it is written from the CPU into the buffer memory.

## (5) Interrupt Mask Register (04H)

When "1" is written in all the bits of this register and one or more of the interrupt causes corresponding to these bits (with "1" written) arise, the INT pin is activated. The values of Bits 0 to 5 of this register do not affect the values of the interrupt status register. Use Bit 6 (Sub Q Interrupt) as the enable register rather than mask register. When Bit 6 (Sub Q Interrupt) is "1" and a Sub Q interrupt arrives, the values of Interrupt Status Register are set to "1".

Bit 0: Drive DMA Complete

Blt 1: Subcode P-W DMA Complete

Bit 2: Host DMA Complete

Bit 3: Host Chip Reset Issued

Blt 4: Host Command

Blt 5: Error Pointer DMA Complete

Bit 6: Sub Q Interrupt

Bit 7: Reserved

## (6) Clear Interrupt Status Register (05H)

When any of respective bits of this register is set to "1", the corresponding interrupt status is cleared. The bit is automatically turns to "0" after the interrupt status have been cleared.

Bit 0: Drive DMA Complete

Bit 1: Subcode P-W DMA Complete

Bit 2: Host DMA Complete

Bit 3: Host Chip Reset Issued

Bit 4: Host Command

Bit 5: Error Pointer DMA Complete

Bit 6: Sub Q Interrupt

Bit 7: Reserved

## (7) Host Result Register (06H)

This register is utilized to transfer the command execution result to the host when the HMDS pin is low. It consists of a 10-byte FIFO.

#### (8) Host Interface Control Register (07H)

Controls the host interface hardware when the HMDS pin is low. It has the same specifications as the host interface control register of the CXD1186BQ.

Bit 0: Host Interrupt #1

This bit value becomes the value of HINTSTS#1 (bit 0) of the Status register on the host side.

Bit 1: Host Interrupt #2

This bit value becomes the value of HINTSTS#2 (bit 1) of the Status register on the host side.

Bit 2: Host Interrupt #3

This bit value becomes the value of HINTSTS#3 (bit 2) of the Status register on the host side.

(Note) Once "1" has been written into Bits 0 to 2, the bits will keep at "1" until they are cleared from the host or the chip is reset. This register cannot be accessed from the CPU to set Bits 0 to 2 from "1" to "0". Accordingly, to set any of these bits, it is not necessary to take into consideration the value of the other bits. Writing "1" into these bits is prohibited when the corresponding Host Interrupt Status #1 to #3 bits of the Host Interface Status Register are "1". Therefore, before writing "1" into these bits, the CPU must read the Host Interface Status Register and confirm that the corresponding Host Interrupt Status #1 to #3 bits are "0".

Bit 3: Reserved

Bit 4: Reserved

Bit 5: Reserved

Bit 6: Clear Result

The host result register is cleared when "1" is written

The host result register is cleared when "1" is written into this bit. This bit is automatically turns to "0" when the clearing of the host result register has been completed. There is therefore no need for the CPU to write "0" again.

Bit 7: Clear Busy

The busy status bit of the host interrupt status register is cleared when "1" is written into this bit. This bit is automatically turns to "0" when the clearing of the busy status bit has been completed. There is therefore no need for the CPU to write "0" again.

- (9) Drive DMA Address Counter Lower (08H)

- (10) Drive DMA Address Counter Middle (09H)

#### (11) Drive DMA Address Counter Upper (0AH)

These are 20-bit registers for setting the address from which to start the DMA transfer with the CXD1186BQ. Their values are incremented each time 1 byte has been transferred by DMA.

- (12) Drive DMA Transfer Counter Lower (0BH)

- (13) Drive DMA Transfer Counter Upper (0CH)

These are 12-bit registers for setting the number of bytes to be transferred by DMA with the CXD1186BQ. Their values are decremented each time 1 byte has been transferred by DMA.

- (14) Error Pointer DMA Address Counter Lower (0DH)

- (15) Error Pointer DMA Address Counter Middle (0EH)

- (16) Error Pointer DMA Address Counter Upper (0FH)

These are 20-bit registers for setting the address from which to start writing error pointers from the CXD1186BQ when Bit 3 (pointer transfer mode) of the DMA Control Register is "0". Their values are incremented each time 8 bits (1 byte) have been transferred by DMA.

- (17) Subcode P-W DMA Address Counter Lower (10H)

- (18) Subcode P-W DMA Address Counter Middle (11H)

- (19) Subcode P-W DMA Address Counter Upper (12H)

These are 20-bit registers for setting the address from which to start writing the channel P-W subcodes from the CXD2500. Their values are incremented each time 1 byte (1 symbol) has been transferred by DMA.

- (20) Host DMA Address Counter Lower (13H)

- (21) Host DMA Address Counter Middle (14H)

- (22) Host DMA Address Counter Upper (15H)

These are 20-bit registers for setting the address from which to start the data transfer by DMA with the host. Their values are incremented each time 1 byte has been transferred by DMA.

- (23) Host DMA Transfer Counter Lower (16H)

- (24) Host DMA Transfer Counter Upper (17H)

These are 16-bit registers for setting the number of bytes transferred by DMA with the host. Their values are decremented each time 1 byte has been transferred by DMA.

SONY

CXD1198AQ

## (25) CPU DMA Address Counter Lower (18H)

#### (26) CPU DMA Address Counter Middle (19H)

## (27) CPU DMA Address Counter Upper (1AH)

These are 20-bit registers for setting the address from which to start the data transfer by DMA with the CPU. Their values are incremented each time 1 byte has been transferred by DMA.

#### (28) Configuration Register (1BH)

Bit 0: CDL 3 × Series

This bit is set to "1" when connected to the CDL30 or 35 series LSI.

Bit 1: Packet Mode

When this bit is "0", transfers the decoded data in 4 packs to the DRAM for each subcode sync; when it is "1", transfers the decoded data in 4 packs starting from the pack prior to the fifth pack to the DRAM for each subcode sync.

Bit 2: Buffer Memory Size 1

Bit 3: Buffer Memory Size 2

Select the buffer memory size : 64 kB with (Bit 3, Bit 2) = (0, 0), 256 kB with (0, 1) and 1 MB with (1, x).

Bit 4: Error Pointer Write Data

Sets the error pointer (DDBP) value when data is transferred by DMA from the buffer memory to the CXD1186BQ.

Bit 5: HCLK Disable Mode

The HCLK output remains low when this bit is "1". When "0", a clock signal with half the frequency of XTL2 is output from the HCLK output.

Bit 6: Reserved Bit 7: Reserved

# (29) Drive Command Register (20H)

The command register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

## (30) Drive Parameter Register (21H)

The parameter register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

## (31) Drive Write Data Register (22H)

The write data register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

## (32) Drive Control Register (23H)

The control register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

#### 2-2. Read Registers

#### (1) BMM Status Register (00H)

Bit 0: Reset Condition

This bit is set to "1" when XSRS is low and "0" when XRST is low or when "1" is written into Bit 0 (BMM Reset) of the Reset Control Register. It is used for determining whether the CPU which was reset externally was the SCSI bus or power-on.

Bit 1: CPU Buffer Read Ready

This bit is set to "1" when the 1-byte data read from the buffer memory is provided in the CPU DMA Data Register. It returns to "0" when the data in the CPU DMA Data Register is read.

Bit 2: CPU Buffer Write Ready

This bit is set to "0" when1-byte data is written into the CPU MDA Data Register. It is set to "1" when the data in the CPU DMA data register is written into the buffer memory.

Bit 3: Pointer Status Flag

This bit is set to "1" when one or more error pointers were set in 1 block of data transferred from the CXD1186BQ. It is cleared to "0" by setting a value in the Drive DMA Transfer Counter.

Bit 4: Subcode ECC Status #0

Indicates the results of the error correction in channel R-W subcode pack #0. It is set to "1" when uncorrectable data errors occur.

Bit 5: Subcode ECC Status #1

Indicates the results of the error correction in channel R-W subcode pack #1. It is set to "1" when uncorrectable data errors occur.

Bit 6: Subcode ECC Status #2

Indicates the results of the error correction in channel R-W subcode pack #2. It is set to "1" when uncorrectable data errors occur.

Bit 7: Subcode ECC Status #3

Indicates the results of the error correction in channel R-W subcode pack #3. It is set to "1" when uncorrectable data errors occur.

#### (2) DMA Status Register-1 (01H)

The setting values of DMA Control Register-1 can be read from this register.

Bit 0: Drive DMA Enable

Bit 1: Drive DMA Source

Bit 2: Pointer Transfer Enable

Bit 3: Pointer Transfer Mode

Bit 4: Sync Pattern Enable

Bit 5: Reserved

Bit 6: Reserved

Bit 7: Reserved

SONY

## (3) DMA Status Register-2 (02H)

The setting values of DMA Control Register-2 can be read from this register.

Bit 0: Host DMA Enable

Bit 1: Host DMA Source

Bit 2: CPU DMA Enable

Bit 3: CPU DMA Source

Bit 4: Reserved

Bit 5: Subcode P-W DMA Enable Bit 6: Subcode P-W ECC Enable Bit 7: Subcode P-W ECC Strategy

#### (4) CPU DMA Data Register (03H)

The data read from the buffer memory by DMA with the CPU is written into this register.

## (5) Interrupt Status Register (04H)

The values of this register's bits indicate the corresponding interrupt statuses respectively.

Bit 0: Drive DMA Complete

This is set to "1" when data transfer by DMA with the CXD1186BQ is completed.

Bit 1: Subcode P-W DMA Complete

This is set to "1" when the channel P-W subcodes have been written into the buffer memory.

Bit 2: Host DMA Complete

This is set to "1" when data transfer by DMA with the host is completed.

Bit 3: Host Chip Reset Issued

This is set to "1" when the host writes "1" into Bit 7 (Chip Reset Bit) of the Host Control Register and this IC is reset.

Bit 4: Host Command

This is set to "1" when the host writes a 1 byte command into the Host Command Register.

Bit 5: Pointer DMA Complete

This is set to "1" when the DMA transfer of pointers is completed.

Bit 6: Sub Q Interrupt

This is set to "1" if the falling edge of the SBSY pin (connected to the SCOR pin of the CXD2500) is detected when "1" has been written into Bit 6 (Sub Q Interrupt) of the Interrupt Mask Register.

Bit 7: Reserved

#### (6) Host Command Register (05H)

This register is used to know the commands from the host when the HMDS pin is low.

#### (7) Host Parameter Register (06H)

This register is used to know the command parameters from the host when the HMDS pin is low. It consists of a 10-byte FIFO.

## (8) Host Interface Status Register (07H)

This register is used to know the status of the host interface hardware when the HMDS pin is low. It has the same specifications as the Host Interface Control Register of the CXD1186BQ.

Bit 0: Host Interrupt Status #1

This bit turns to "1" when the CPU writes "1" into host interrupt #1 (Host Interface Control Register Bit 0). It is set to "0" when the host writes "1" into CLRINT #1 (Control Register Bit 0). This bit is used to monitor the interrupt status to the host.

Bit 1: Host Interrupt Status #2

This bit turns to "1" when the CPU writes "1" into host interrupt #2 (Host Interface Control Register Bit 1). It is set to "0" when the host writes "1" into CLRINT #2 (Control Register Bit 1). This bit is used to monitor the interrupts status to the host.

Bit 2: Host Interrupt Status #3

This bit turns to "1" when the CPU writes "1" into host interrupt #3 (Host Interface Control Register Bit 2). It is set to "0" when the host writes "1" into CLRINT #3 (Control Register Bit 2). This bit is used to monitor the interrupts status to the host.

Bit 3: Parameter Read Ready

When this bit is "1", it indicates that the Parameter Register of the host is not empty and parameter data can be read from the CPU. When "0", the Parameter Register is empty.

Bit 4: Parameter Full

When this bit is "1", it indicates that the Parameter Register of the host is full.

Bit 5: Result Write Ready

When this bit is "1", it indicates that the Host Result Register is not full and result data can be written from the CPU. When "0", the Host Result Register is full and the CPU cannot write the result data into the register.

Bit 6: Result Empty

When this bit is "1", it indicates that the Host Result Register is empty.

Bit 7: Busy Status

This bit has the same value as Bit 7 of the Host Status Register. It is set to "1" when the host writes a command in the Command Register. It is set to "0" when the CPU writes "1" into the Clear Busy Bit of the Host Interface Control Register.

- (9) Drive DMA Address Counter Lower (08H)

- (10) Drive DMA Address Counter Middle (09H)

- (11) <u>Drive DMA Address Counter Upper</u> (0AH) Indicate the Drive DMA Address Counter values.

- (12) Drive DMA Transfer Counter Lower (0BH)

- (13) <u>Drive DMA Transfer Counter Upper</u> (0CH) <u>Indicate the Drive DMA Transfer Counter values.</u>

- (14) Error Pointer DMA Address Counter Lower (0DH)

- (15) Error Pointer DMA Address Counter Middle (0EH)

- (16) Error Pointer DMA Address Counter Upper (0FH)

Indicate the Error Pointer DMA Address Counter values.

- (17) Subcode P-W DMA Address Counter Lower (10H)

- (18) Subcode P-W DMA Address Counter Middle (11H)

- (19) Subcode P-W DMA Address Counter Upper (12H)

Indicate the Subcode P-W DMA Address Counter values.

- (20) Host DMA Address Counter Lower (13H)

- (21) Host DMA Address Counter Middle (14H)

- (22) Host DMA Address Counter Upper (15H)

Indicate the Host DMA Address Counter values.

- (23) Host DMA Transfer Counter Lower (16H)

- (24) Host DMA Transfer Counter Upper (17H)

Indicate the Host DMA Transfer Counter values.

- (25) CPU DMA Address Counter Lower (18H)

- (26) CPU DMA Address Counter Middle (19H)

- (27) CPU DMA Address Counter Upper (1AH)

Indicate the CPU DMA Address Counter values.

- (28) Drive Status Register (20H)

The Status Register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

(29) Drive Result Register (21H)

The Result Register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

(30) Drive Read Data Register (22H)

The Read Data Register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

(31) Drive FIFO Status Register (23H)

The FIFO Status Register for the host interface of the CXD1186BQ is mapped in the register address space of this IC.

# Write Register

| Reset Contro          | ol Register (0        | 0H)                  |                           |                              |                               |                            |                          |

|-----------------------|-----------------------|----------------------|---------------------------|------------------------------|-------------------------------|----------------------------|--------------------------|

| bit7                  | bit6                  | bit5                 | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

|                       |                       |                      |                           |                              | SCSI IC<br>Reset              | Drive<br>Reset             | BMM<br>Reset             |

| DMA Control           | Register - 1          | (01H)                |                           |                              |                               |                            |                          |

| bit7                  | bit6                  | bit5                 | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

|                       |                       |                      | Sync<br>Pattern<br>Enable | Pointer<br>Transfer<br>Mode  | Pointer<br>Transfer<br>Enable | Drive<br>DMA<br>Source     | Drive<br>DMA<br>Enable   |

|                       |                       |                      | Litable                   | Wiodo                        | Lilabic                       | Course                     | LIIGOIC                  |

| DMA Control<br>bit7   | Register - 2<br>bit6  | (02H)<br>bit5        | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

| Subcode               | Subcode               | Subcode              | Subcode                   | CPU                          | CPU                           | Host                       | Host                     |

| ECC                   | ECC                   | DMA                  | Decode                    | DMA                          | DMA                           | DMA                        | DMA                      |

| Strategy              | Enable                | Enable               | Enable                    | Source                       | Enable                        | Source                     | Enable                   |

| CPU DMA D             | ata Register          | (03H)                |                           |                              |                               |                            |                          |

| bit7                  | bit6                  | bit5                 | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

| D7                    | D6                    | D5                   | D4                        | D3                           | D2                            | D1                         | D0                       |

| Interrupt Mas         | sk Register ((        | )4H)                 |                           |                              | I                             |                            |                          |

| bit7                  | bit6                  | bit5                 | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

|                       | Sub Q<br>interrupt    | Pointer<br>DMA       | Host<br>Command           | Host Chip<br>Reset           | Host<br>DMA                   | Subcode<br>DMA             | Drive<br>DMA             |

|                       | пистири               | Complete             | Command                   | Issued                       | Complete                      | Complete                   | Complete                 |

| Clear Interru         | ot Register (0        | )5H)                 |                           |                              |                               |                            |                          |

| bit7                  | bit6                  | bit5                 | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

|                       | Sub Q<br>interrupt    | Pointer DMA Complete | Host<br>Command           | Host Chip<br>Reset<br>Issued | Host DMA Complete             | Subcode<br>DMA<br>Complete | Drive<br>DMA<br>Complete |

| Hoot Decult           | Dogiotor (OCL         | 1)                   |                           |                              |                               |                            |                          |

| Host Result F<br>bit7 | Register (06F<br>bit6 | 1)<br>bit5           | bit4                      | bit3                         | bit2                          | bit1                       | bit0                     |

| D7                    | D6                    | D5                   | D4                        | D3                           | D2                            | D1                         | D0                       |

|                       | ļ                     | ļ                    | <u> </u>                  | <u> </u>                     | ļ                             | <u> </u>                   |                          |

| Host Interface | e Control Re    | gister (07H)  |      |      |                         |                         |                         |

|----------------|-----------------|---------------|------|------|-------------------------|-------------------------|-------------------------|

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

| Clear<br>Busy  | Clear<br>Result |               |      |      | Host<br>Interrupt<br>#3 | Host<br>Interrupt<br>#2 | Host<br>Interrupt<br>#1 |

| Drive DMA A    | ddress Coun     | ter Lower (08 | BH)  |      |                         |                         |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

| A7             | A6              | A5            | A4   | А3   | A2                      | A1                      | A0                      |

| Drive DMA A    | ddress Coun     | ter Middle (0 | 9H)  |      |                         |                         |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

| A15            | A14             | A13           | A12  | A11  | A10                     | A9                      | A8                      |

| Drive DMA A    | ddress Coun     | ter Upper (0/ | AH)  |      |                         |                         |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

|                |                 |               |      | A19  | A18                     | A17                     | A16                     |

| Drive DMA T    | ransfer Coun    | ter Lower (0E | 3H)  |      |                         |                         |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

| A7             | A6              | A5            | A4   | A3   | A2                      | A1                      | A0                      |

| Drive DMA T    | ransfer Coun    | ter Upper (00 | CH)  |      |                         |                         |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

|                |                 |               |      | A11  | A10                     | A9                      | A8                      |

| Pointer DMA    | Address Co.     | unter Lower ( | ODH) | '    |                         | •                       |                         |

| bit7           | bit6            | bit5          | bit4 | bit3 | bit2                    | bit1                    | bit0                    |

| A7             | A6              | A5            | A4   | А3   | A2                      | A1                      | A0                      |

| Pointer DMA | Address Cou  | unter Middle  | (0EH)        |      |      |      |      |

|-------------|--------------|---------------|--------------|------|------|------|------|

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

| A15         | A14          | A13           | A12          | A11  | A10  | A9   | A8   |

| Pointer DMA | Address Cou  | unter Upper ( | 0FH)         |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

|             |              |               |              | A19  | A18  | A17  | A16  |

| Subcode P-V | V DMA Addre  | ess Counter L | ower (10H)   |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

| A7          | A6           | A5            | A4           | A3   | A2   | A1   | A0   |

| Subcode P-V | V DMA Addre  | ess Counter M | Middle (11H) |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

| A15         | A14          | A13           | A12          | A11  | A10  | A9   | A8   |

| Subcode P-V | V DMA Addre  | ess Counter l | Joper (12H)  |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

|             |              |               |              | A19  | A18  | A17  | A16  |

| Host DMA A  | ddress Count | er Lower (13  | H)           |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

| A7          | A6           | A5            | A4           | А3   | A2   | A1   | A0   |

| Host DMA A  | ddress Count | er Middle (14 | !H)          |      |      |      |      |

| bit7        | bit6         | bit5          | bit4         | bit3 | bit2 | bit1 | bit0 |

| A15         | A14          | A13           | A12          | A11  | A10  | A9   | A8   |

|             |              |               | <u> </u>     |      |      |      |      |

| Host DMA Ad                           | ddress Count | er Upper (15            | H)                             |                            |                            |                |                 |  |  |

|---------------------------------------|--------------|-------------------------|--------------------------------|----------------------------|----------------------------|----------------|-----------------|--|--|

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

|                                       |              |                         |                                | A19                        | A18                        | A17            | A16             |  |  |

| Host DMA Tr                           | ansfer Count | er Lower (16            | :H)                            |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

| A7                                    | A6           | A5                      | A4                             | A3                         | A2                         | A1             | A0              |  |  |

| Host DMA Transfer Counter Upper (17H) |              |                         |                                |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

| A15                                   | A14          | A13                     | A12                            | A11                        | A10                        | A9             | A8              |  |  |

| CPU DMA Ad                            | ddress Count | er Lower (18            | ·H)                            |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

| A7                                    | A6           | A5                      | A4                             | А3                         | A2                         | A1             | A0              |  |  |

| CPU DMA Ad                            | ddress Count | er Middle (19           | )H)                            |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

| A15                                   | A14          | A13                     | A12                            | A11                        | A10                        | A9             | A8              |  |  |

| CPU DMA Ad                            | ddress Count | er Unner (1A            | \H)                            |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

|                                       |              |                         |                                | A19                        | A18                        | A17            | A16             |  |  |

| Configuration                         | Register (1F | 3H)                     | -                              |                            |                            |                |                 |  |  |

| bit7                                  | bit6         | bit5                    | bit4                           | bit3                       | bit2                       | bit1           | bit0            |  |  |

|                                       |              | HCLK<br>Disable<br>Mode | Error<br>Pointer<br>Write Data | Buffer<br>Memory<br>Size 2 | Buffer<br>Memory<br>Size 1 | Packet<br>Mode | CDL3X<br>Series |  |  |

Drive Command Register (20H)

Drive Parameter Register (21H)

Drive Write Data Register (22H)

Drive Control Register (23H)

Internal RAM-1 Write (30H)

Internal RAM-2 Write (31H)

# Test Register (35H)

| bit7 | bit6 | bit5                    | bit4          | bit3 | bit2 | bit1                 | bit0                 |  |

|------|------|-------------------------|---------------|------|------|----------------------|----------------------|--|

|      |      | Reset<br>Signal<br>Sync | HCLK<br>Reset | TSTE | TSTD | REF<br>Block<br>Test | SUB<br>Block<br>Test |  |

# Read register

| BMM Status     | Register (00l | <b>⊣</b> ) |           |           |            |            |           |

|----------------|---------------|------------|-----------|-----------|------------|------------|-----------|

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

| Subcode        | Subcode       | Subcode    | Subcode   | Pointer   | CPU Buffer | CPU Buffer | Deset     |

| ECC            | ECC           | ECC        | ECC       | Status    | Write      | Read       | Reset     |

| Status #3      | Status #2     | Status #1  | Status #0 | Flag      | Ready      | Ready      | Condition |

|                |               |            |           |           |            |            | <u> </u>  |

| DMA Status I   | •             | •          |           |           |            |            |           |

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

|                |               |            | Sync      | Pointer   | Pointer    | Drive      | Drive     |

|                |               |            | Pattern   | Transfer  | Transfer   | DMA        | DMA       |

|                |               |            | Enable    | Mode      | Enable     | Source     | Enable    |

| DMA Ctatus     | Danistan 0./0 | 2011)      |           |           |            |            |           |

| DMA Status I   | •             | •          | L:44      | F:40      | h:40       | F:44       | F:40      |

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

| Subcode        | Subcode       | Subcode    |           | CPU       | CPU        | Host       | Host      |

| ECC            | ECC           | DMA        |           | DMA       | DMA        | DMA        | DMA       |

| Strategy       | Enable        | Enable     |           | Source    | Enable     | Source     | Enable    |

| CDLL DMA D     | ata Dagiatar  | (O2LI)     |           |           |            |            |           |

| CPU DMA Da     | bit6          |            | bi+4      | bit3      | b:+0       | bit1       | bit0      |

| Dit/           | DILO          | bit5       | bit4      | DILO      | bit2       | DILI       | DILU      |

| D7             | D6            | D5         | D4        | D3        | D2         | D1         | D0        |

|                | D0            | D3         | D4        | D3        | 02         |            | D0        |

|                |               |            |           |           |            |            |           |

| Interrupt Stat | us Register ( | 04H)       |           |           |            |            |           |

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

|                |               | Pointer    |           | Host Chip | Host       | Subcode    | Drive     |

|                | Sub Q         | DMA        | Host      | Reset     | DMA        | DMA        | DMA       |

|                | interrupt     | Complete   | Command   | Issued    | Complete   | Complete   | Complete  |

| V              |               |            |           |           |            |            | <u>'</u>  |

| Host Comma     | nd Register ( | (05H)      |           |           |            |            |           |

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

|                |               |            |           |           |            |            |           |

| D7             | D6            | D5         | D4        | D3        | D2         | D1         | D0        |

|                |               |            |           |           |            |            |           |

|                |               | /a.a»      |           |           | -          |            |           |

| Host Parame    | •             | •          |           | 1.1.0     | 1.1.0      |            | 1.440     |

| bit7           | bit6          | bit5       | bit4      | bit3      | bit2       | bit1       | bit0      |

|                |               |            |           |           | 50         | 5.         | 50        |

| D7             | D6            | D5         | D4        | D3        | D2         | D1         | D0        |

|                |               |            |           |           |            |            |           |

| Hot Interface  | Status Regis    | ster (07H)               |                   |                            |                         |                         |                         |

|----------------|-----------------|--------------------------|-------------------|----------------------------|-------------------------|-------------------------|-------------------------|

| bit7           | bit6            | bit5                     | bit4              | bit3                       | bit2                    | bit1                    | bit0                    |

| Busy<br>Status | Result<br>Empty | Result<br>Write<br>Ready | Parameter<br>Full | Parameter<br>Read<br>Ready | Host<br>Interrupt<br>#3 | Host<br>Interrupt<br>#2 | Host<br>Interrupt<br>#2 |

| Drive DMA A    | ddress Coun     | ter Lower (08            | 3H)               |                            |                         |                         |                         |

| bit7           | bit6            | bit5                     | bit4              | bit3                       | bit2                    | bit1                    | bit0                    |

| A7             | A6              | A5                       | A4                | А3                         | A2                      | A1                      | A0                      |

| Drive DMA A    | ddress Coun     | ter Middle (0            | 9H)               |                            |                         |                         |                         |

| bit7           | bit6            | bit5                     | bit4              | bit3                       | bit2                    | bit1                    | bit0                    |

| A15            | A14             | A13                      | A12               | A11                        | A10                     | A9                      | A8                      |

| Drive DMA A    | ddress Coun     | ter Upper (0/            | <b>Л</b> Н)       |                            |                         |                         |                         |

| bit7           | bit6            | bit5                     | bit4              | bit3                       | bit2                    | bit1                    | bit0                    |