# 1:18 Clock Distribution Buffer

#### **Features**

■ Operational range: Up to 200 MHz

■ LVCMOS/LVTTL clock input

■ LVCMOS-/LVTTL-compatible logic input

■ 18 clock outputs: Drive up to 36 clock lines

■ Output-to-output Skew: 110 ps (typical)

■ Output enable control

■ Supply voltage: 2.5 V or 3.3 V

■ Temperature range: Commercial and Industrial

■ 32-pin TQFP package

■ Pin compatible with MPC942C

## **Functional Description**

The CY29942 is a low voltage clock distribution buffer with an LVCMOS or LVTTL compatible clock input. The output enable control input is LVCMOS/LVTTL compatible. The eighteen outputs are 2.5 V or 3.3 V LVCMOS or LVTTL compatible, operate up to 200 MHz, and can drive 50  $\Omega$  series or parallel terminated transmission lines. For series terminated transmission lines, each output can drive one or two traces, giving the devices an effective fanout of 1:36. Low output-to-output skews make the CY29942 an ideal clock distribution buffer for nested clock trees in the most demanding of synchronous systems.

## **Logic Block Diagram**

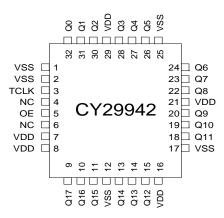

#### **Pinouts**

Figure 1. Pin Configuration

Table 1. Pin Description

| Pin                                                                   | Name    | I/O    | Description                                                                                                                         |

|-----------------------------------------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 3                                                                     | TCLK    | Input  | External reference/Test clock input. Weak internal pull-down resistor.                                                              |

| 5                                                                     | OE      | Input  | Output enable. When HIGH, all outputs are enabled. When set LOW, the outputs are at high impedance. Weak internal pull-up resistor. |

| 9, 10, 11, 13, 14, 15, 18, 19, 20, 22, 23, 24, 26, 27, 28, 30, 31, 32 | Q(17:0) | Output | Clock outputs                                                                                                                       |

| 7, 8, 16, 21, 29                                                      | VDD     |        | 2.5 V or 3.3 V power supply                                                                                                         |

| 1, 2, 12, 17, 25                                                      | VSS     |        | Ground                                                                                                                              |

| 4, 6                                                                  | NC      |        | No connection                                                                                                                       |

## **Absolute Maximum Ratings**

Exceeding the maximum ratings may impair the useful life of the device. User guidelines are not tested. [1]

| Maximum input voltage relative to $\rm V_{SS}{:}$ $\rm V_{SS}{\:-\:}0.3~V$ |

|----------------------------------------------------------------------------|

| Maximum input voltage relative to $V_{DD}$ : $V_{DD}$ + 0.3 $V$            |

| Storage temperature:65 °C to 150 °C                                        |

| Operating temperature:40 °C to 85 °C                                       |

| Maximum ESD protection                                                     |

| Maximum power supply:5.5 V                                                 |

| Maximum input current: ±20 mA                                              |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, I/O voltages should be constrained to the range:

$$V_{SS} < V_{I/O} < V_{DD}$$

Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>SS</sub> or V<sub>DD</sub>).

## **DC Electrical Specifications**

$V_{DD}$  = 3.3 V ±5% or 2.5 V ±5% over the specified temperature range.

| Parameter        | Description                        | Conditions                                        | Min             | Тур | Max      | Unit |

|------------------|------------------------------------|---------------------------------------------------|-----------------|-----|----------|------|

| V <sub>IL</sub>  | Input low voltage                  |                                                   | V <sub>SS</sub> | -   | 0.8      | V    |

| V <sub>IH</sub>  | Input high voltage                 |                                                   | 2.0             | _   | $V_{DD}$ | V    |

| I <sub>IL</sub>  | Input low current <sup>[2]</sup>   |                                                   | _               | _   | -200     | μΑ   |

| I <sub>IH</sub>  | Input high current <sup>[2]</sup>  |                                                   | _               | _   | 200      | μΑ   |

| V <sub>OL</sub>  | Output low voltage <sup>[3]</sup>  | I <sub>OL</sub> = 20 mA                           | _               | _   | 0.5      | V    |

| V <sub>OH</sub>  | Output high voltage <sup>[3]</sup> | $I_{OH} = -20 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.4             | _   | _        | V    |

|                  |                                    | $I_{OH} = -16 \text{ mA}, V_{DD} = 2.5 \text{ V}$ | 2.0             | _   | _        | V    |

| I <sub>DDQ</sub> | Quiescent supply current           | OE = V <sub>SS</sub>                              | _               | 5   | 7        | mA   |

| I <sub>DD</sub>  | Dynamic supply current             | $V_{DD}$ = 3.3 V, Outputs at 150 MHz, CL = 15 pF  | _               | 285 | _        | mA   |

|                  |                                    | $V_{DD}$ = 3.3 V, Outputs at 200 MHz, CL = 15 pF  | _               | 335 | _        | mA   |

|                  |                                    | $V_{DD}$ = 2.5 V, Outputs at 150 MHz, CL = 15 pF  | _               | 200 | -        | mA   |

|                  |                                    | $V_{DD}$ = 2.5 V, Outputs at 200 MHz, CL = 15 pF  | _               | 240 | -        | mA   |

| Z <sub>out</sub> | Output impedance                   | V <sub>DD</sub> = 3.3 V                           | 8               | 12  | 16       | Ω    |

|                  |                                    | V <sub>DD</sub> = 2.5 V                           | 10              | 15  | 20       | Ω    |

| C <sub>in</sub>  | Input capacitance                  |                                                   | _               | 4   | _        | pF   |

#### Notes

- The voltage on any input or I/O pin cannot exceed the power pin during power-up.

Inputs have pull-up/pull-down resistors that effect input current.

Driving series or parallel terminated 50Ω (or 50 Ω to V<sub>DD</sub>/2) transmission lines.

AC Electrical Specifications  $V_{DD} = 3.3 \text{ V } \pm 5\% \text{ or } 2.5 \text{ V } \pm 5\% \text{ over the specified temperature range}^{[4]}$

| Parameter | Description                                    | Conditions                                                                          | Min | Тур | Max | Unit |

|-----------|------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| Fmax      | Input frequency                                |                                                                                     | _   | _   | 200 | MHz  |

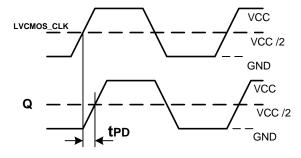

| tpd       | TTL_CLK to Q delay <sup>[5, 6]</sup>           | V <sub>DD</sub> = 3.3 V                                                             | 1.8 | 3.3 | 3.8 | ns   |

|           |                                                | V <sub>DD</sub> = 2.5 V                                                             | 2.3 | 3.8 | 4.4 | ns   |

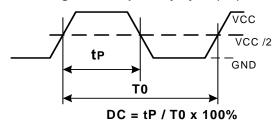

| DC        | Output duty cycle <sup>[5, 6, 7]</sup>         | Measured at V <sub>DD</sub> /2                                                      | 45  | _   | 55  | %    |

| tsk(0)    | Output-to-output skew <sup>[5, 6]</sup>        |                                                                                     | _   | 110 | 200 | ps   |

| tskew(pp) | Part-to-part skew <sup>[8]</sup>               | V <sub>DD</sub> = 3.3 V                                                             | _   | _   | 1.0 | ns   |

|           |                                                | V <sub>DD</sub> = 2.5 V                                                             | _   | _   | 1.3 | ns   |

| tskew(pp) | Part-to-part skew <sup>[9]</sup>               |                                                                                     | _   | _   | 600 | ps   |

| tr/tf     | Output clocks rise/fall time <sup>[5, 6]</sup> | 0.8 V to 2.0 V, V <sub>DD</sub> = 3.3 V;<br>0.5 V to 1.8 V, V <sub>DD</sub> = 2.5 V | 0.2 | -   | 1.1 | ns   |

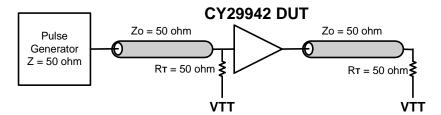

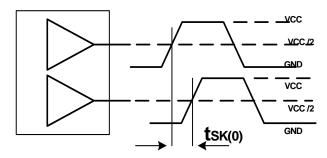

Figure 2. LVCMOS\_CLK CY29942 Test Reference for  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 2.5 V

Figure 3. LVCMOS Propagation Delay (tpd) Test Reference

#### Notes

- 4. Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with loaded outputs.

- 5. Outputs driving 50  $\Omega$  transmission lines.

- 6. See Figure 2.

- 50% input duty cycle.

- 8. Across temperature and voltage ranges, includes output skew.

- 9. For a specific temperature and voltage, includes output skew.

Figure 4. Output Duty Cycle (DC)

Figure 5. Output-to-Output Skew tsk(0)

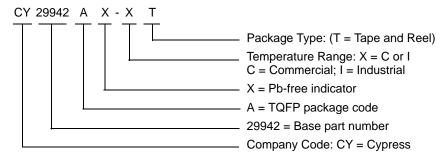

# **Ordering Information**

| Part Number | Package Type                | Production Flow             |

|-------------|-----------------------------|-----------------------------|

| CY29942AI   | 32-pin TQFP                 | Industrial,-40 °C to 85 °C  |

| CY29942AIT  | 32-pin TQFP – Tape and Reel | Industrial, -40 °C to 85 °C |

| Pb-free     | · ·                         |                             |

| CY29942AXI  | 32-pin TQFP                 | Industrial, -40 °C to 85 °C |

| CY29942AXIT | 32-pin TQFP – Tape and Reel | Industrial, -40 °C to 85 °C |

| CY29942AXC  | 32-pin TQFP                 | Commercial, 0 °C to 70 °C   |

| CY29942AXCT | 32-pin TQFP – Tape and Reel | Commercial, 0 °C to 70 °C   |

## **Ordering Code Definitions**

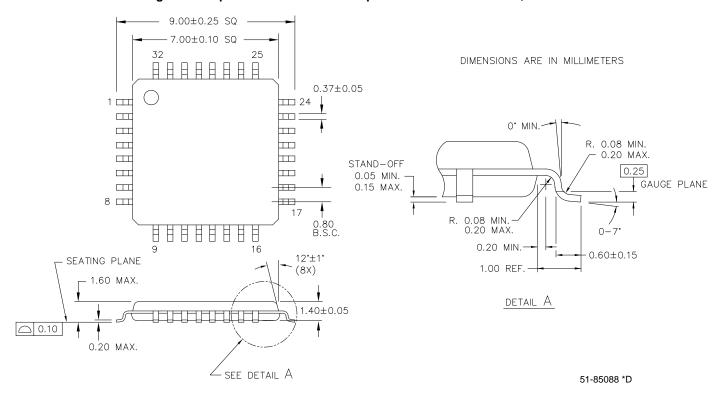

# **Package Drawing and Dimensions**

Figure 6. 32-pin Thin Plastic Quad Flatpack  $7 \times 7 \times 1.4$  mm A32.14, 51-85088

# Acronyms

| Acronym | Description                                         |  |  |

|---------|-----------------------------------------------------|--|--|

| TQFP    | thin quad flat package                              |  |  |

| LVCMOS  | low voltage complementary metal oxide semiconductor |  |  |

| LVTTL   | low voltage transistor transistor logic             |  |  |

| OE      | output enable                                       |  |  |

| PLL     | phase-locked loop                                   |  |  |

| TQFP    | thin quad flat pack                                 |  |  |

# **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure |  |  |  |

|--------|-----------------|--|--|--|

| °C     | degree Celsius  |  |  |  |

| Ω      | ohms            |  |  |  |

| MHz    | Mega Hertz      |  |  |  |

| μΑ     | micro Amperes   |  |  |  |

| mA     | milli Amperes   |  |  |  |

| ms     | milli seconds   |  |  |  |

| mW     | milli Watts     |  |  |  |

| ns     | nano seconds    |  |  |  |

| %      | percent         |  |  |  |

| pF     | pico Farads     |  |  |  |

| ps     | pico seconds    |  |  |  |

| V      | Volts           |  |  |  |

| kV     | kilo Volts      |  |  |  |

# **Document History Page**

| Document Title: CY29942 1:18 Clock Distribution Buffer Document Number: 38-07284 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                         | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| **                                                                               | 111095  | BRK                | 02/07/02           | New datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *A                                                                               | 116777  | HWT                | 08/14/02           | Added a Commercial Temp. Range in the Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *B                                                                               | 122876  | RBI                | 12/21/02           | Add power up requirements to maximum rating information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *C                                                                               | 334117  | RGL                | See ECN            | Added Lead-free devices Added typical value for output-output skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *D                                                                               | 2761988 | KVM                | 09/10/09           | Ordering Information table: fixed typo and removed obsolete CY29942ACT. Changed Lead-free to Pb-free.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *E                                                                               | 2899304 | BASH/CXQ           | 03/25/2010         | Removed CY29942AC part from Ordering Information. Updated package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *F                                                                               | 3034172 | CXQ                | 09/21/2010         | Changed spec title. Updated format of "Features", changed wording in "Functional Description". Removed note 1, added info into Table 1 directly. Removed reference to multiple supplies, power supply sequencing from Absolute Maximum Ratings. Removed reference to $V_{DDC}$ from AC/DC Electrical Specs tables. Added condition OE = $V_{SS}$ for $I_{DDQ}$ in DC Electrical Specs table. Fixed formatting in AC/DC Electrical specs tables. Changed $t_{SKEW}$ to $t_{SK(0)}$ to match Figure 6. Added Ordering Code Definitions. Added Acronyms and Units of Measure sections. Minor edits. |

| *G                                                                               | 3548252 | PURU               | 03/12/2012         | Changed LQFP to TQFP throughout document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive cypres

Clocks & Buffers cy

Interface cypre

Lighting & Power Control cypres

Memory

Optical & Image Sensing

PSoC

Touch Sensing

USB Controllers

Wireless/RF

cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc

cypress.com/go/memory cypress.com/go/image cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2002-2012. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.