# 8 × 4 Wideband Video Crosspoint Array

### **Features**

- Routes Any Input to Any Output

- Wide Bandwidth: 300 MHz

- Low Crosstalk: −85 dB @ 5 MHz

- Double Buffered TTL-Compatible Latches with Readback

- Low r<sub>DS(on)</sub>: 45 Ω

- Optional Negative Supply

### **Benefits**

- Reduced Board Space

- Improved System Bandwidth

- Improved Channel Off-Isolation

- Simplified Logic Interfacing

- Allows Bipolar Signal Swings

- Reduced Insertion Loss

- High Reliability

## **Applications**

- Wideband Signal Routing and Multiplexing

- High-End Video Systems

- NTSC, PAL, SECAM Switchers

- Digital Video Routing

- ATE Systems

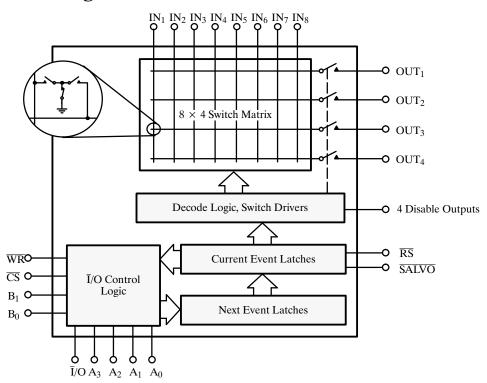

## **Description**

The DG884 contains a matrix of 32 T-switches configured in an  $8 \times 4$  crosspoint array. Any of the IN/OUT pins may be used as an input or output. Any of the IN pins may be switched to any or simultaneously to all OUT pins.

The DG884 is built on a proprietary D/CMOS process that combines low capacitance switching DMOS FETs with low power CMOS control logic and drivers. The ground lines between adjacent signal input pins help to reduce crosstalk. The low on-resistance and low on-capacitance of the DG884 make it ideal for video and wideband signal routing.

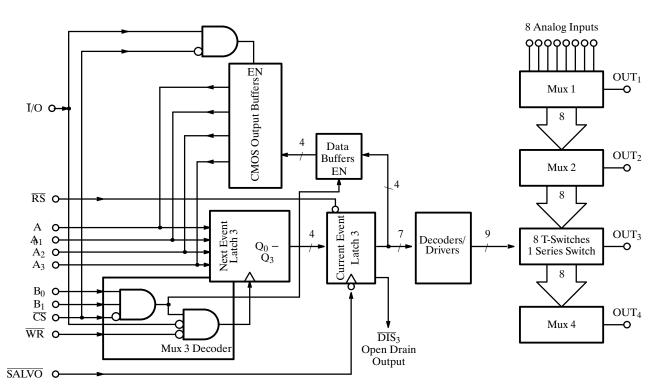

Control data is loaded individually into four Next Event latches. When all Next Event latches have been programmed, data is transferred into the Current Event latches via a SALVO command. Current Event latch data readback is available to poll array status.

Output disable capabilities make it possible to parallel multiple DG884s to form larger switch arrays. DIS outputs provide control signals used to place external buffers in a power saving mode.

For additional information please refer to AN504.

## **Functional Block Diagram**

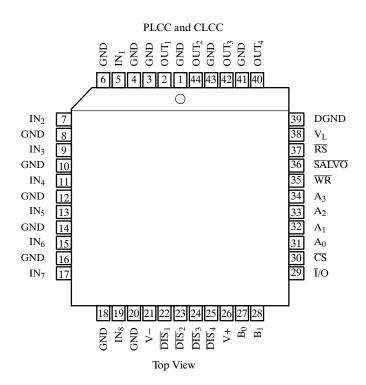

# **Pin Configuration**

#### **Ordering Information**

| Temp Range   | Package     | Part<br>Number |

|--------------|-------------|----------------|

| −40 to 85°C  | 44-Pin PLCC | DG884DN        |

| −55 to 125°C | 44-Pin CLCC | DG884AM/883    |

### **Truth Tables**

| RS | Ī/O | CS | WR       | SALVO | Actions                                                                                                                                                               |  |

|----|-----|----|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | 0   | 1  | Ĩ.       | 1     | No change to Next Event latches                                                                                                                                       |  |

| 1  | 0   | 0  | TL.      | 1     | Next Event latches loaded as defined in table below                                                                                                                   |  |

| 1  | 0   | 0  | 0        | 1     | Next Event latches are transparent.                                                                                                                                   |  |

| 1  | 0   | 0  | <u>.</u> | 1     | Next Event data latched-in                                                                                                                                            |  |

| 1  | 0   | X  | 1        | 7.    | Data in all Next Event latches is simultaneously loaded into the Current Event latches, i.e., all new crosspoint addresses change simultaneously when SALVO goes low. |  |

| 1  | 0   | 0  | X        | 0     | Current Event latches are transparent                                                                                                                                 |  |

| 1  | 0   | X  | 1        | -5    | Current Event data latched-in                                                                                                                                         |  |

| 1  | 0   | 0  | 0        | 0     | Both next and Current Event latches are transparent                                                                                                                   |  |

| 1  | 1   | 1  | 1        | 1     | $A_0, A_1, A_2, A_3$ – High impedance                                                                                                                                 |  |

| 1  | 1   | 0  | 1        | 1     | $A_0, A_1, A_2, A_3$ become outputs and reflect the contents of the Current Event latches. $B_0, B_1$ determine which Current Event latches are being read            |  |

| 0  | X   | X  | 1        | 1     | All crosspoints opened (but data in Next Event latches is preserved)                                                                                                  |  |

All other states are not recommended.

# **Truth Tables (Cont'd)**

| WR | B <sub>1</sub> | B <sub>0</sub> | A <sub>3</sub> | A <sub>2</sub>                       | A <sub>1</sub>                       | A <sub>0</sub>                       | Next Event Latches                                                                                                                                                                                                                                        |

|----|----------------|----------------|----------------|--------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 0              |                | 1              | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $IN_1$ to $OUT_1$ Loaded $IN_2$ to $OUT_1$ Loaded $IN_3$ to $OUT_1$ Loaded $IN_4$ to $OUT_1$ Loaded $IN_5$ to $OUT_1$ Loaded $IN_6$ to $OUT_1$ Loaded $IN_7$ to $OUT_1$ Loaded $IN_7$ to $OUT_1$ Loaded $IN_8$ to $OUT_1$ Loaded $IN_8$ to $OUT_1$ Loaded |

|    |                |                | 0              | X                                    | X                                    | X                                    | Turn Off OUT <sub>1</sub> Loaded                                                                                                                                                                                                                          |

|    | 0              | 1              | 1              | 0<br>0<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $IN_1$ to OUT $_2$ Loaded $IN_2$ to OUT $_2$ Loaded $IN_3$ to OUT $_2$ Loaded $IN_4$ to OUT $_2$ Loaded $IN_5$ to OUT $_2$ Loaded $IN_6$ to OUT $_2$ Loaded $IN_7$ to OUT $_2$ Loaded $IN_7$ to OUT $_2$ Loaded $IN_8$ to OUT $_2$ Loaded                 |

|    |                |                | 0              | X                                    | X                                    | X                                    | Turn Off OUT <sub>2</sub> Loaded                                                                                                                                                                                                                          |

| 0  | 1              | 0              | 1              | 0<br>0<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $IN_1$ to OUT $_3$ Loaded $IN_2$ to OUT $_3$ Loaded $IN_3$ to OUT $_3$ Loaded $IN_4$ to OUT $_3$ Loaded $IN_5$ to OUT $_3$ Loaded $IN_6$ to OUT $_3$ Loaded $IN_7$ to OUT $_3$ Loaded $IN_7$ to OUT $_3$ Loaded $IN_8$ to OUT $_3$ Loaded                 |

|    |                |                | 0              | X                                    | X                                    | X                                    | Turn Off OUT <sub>3</sub> Loaded                                                                                                                                                                                                                          |

|    | 1 1            |                | 1              | 0<br>0<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $IN_1$ to OUT $_4$ Loaded $IN_2$ to OUT $_4$ Loaded $IN_3$ to OUT $_4$ Loaded $IN_4$ to OUT $_4$ Loaded $IN_5$ to OUT $_4$ Loaded $IN_6$ to OUT $_4$ Loaded $IN_7$ to OUT $_4$ Loaded $IN_7$ to OUT $_4$ Loaded $IN_8$ to OUT $_4$ Loaded                 |

|    |                |                | 0              | X                                    | X                                    | X                                    | Turn Off OUT <sub>4</sub> Loaded                                                                                                                                                                                                                          |

Note: When  $\overline{WR} = 0$  Next Event latches are transparent. Each crosspoint is addressed individually, e.g., to connect  $IN_1$  to  $OUT_1$  thru  $OUT_4$  requires  $A_0$ ,  $A_1$ ,  $A_2 = 0$  to be latched with each combination of  $B_0$ ,  $B_1$ . When  $\overline{RS} = 0$ , all four  $\overline{DIS}$  outputs pull low simultaneously.

# **Absolute Maximum Ratings**

| V+ to GND0.3 V to 21 V                                                  |

|-------------------------------------------------------------------------|

| V+ to V0.3 V to 21 V                                                    |

| V- to GND10 V to 0.3 V                                                  |

| $V_L$ to GND                                                            |

| Digital Inputs $(V-) - 0.3 \text{ V to } (V_L) + 0.3 \text{ V}$         |

| or 20 mA, whichever occurs first                                        |

| $V_S, V_D$ (V-) - 0.3 V to (V-) + 14 V or 20 mA, whichever occurs first |

| CURRENT (any terminal) Continuous 20 mA                                 |

| CURRENT (S or D) Pulsed 1 ms 10% duty 40 mA                             |

|                                                                         |

| Storage Temperature   | (A Suffix)   | 65 to 150°C |

|-----------------------|--------------|-------------|

|                       | (D Suffix) – |             |

| Operating Temperature | (A Suffix)   | 55 to 125°C |

|                       | (D Suffix)   | −40 to 85°C |

Power Dissipation (Package)<sup>a</sup>

#### Notes:

- a. All leads soldered or welded to PC board.

- b. Derate 6 mW/°C above 75°C.

- c. Derate 16 mW/°C above 75°C.

# $Specifications ^{a} \\$

|                                              |                                                     | Test Conditions<br>Unless Otherwise Specified                                                                                                                                                                      |                   |                  |                  | uffix<br>125°C   |                                                                  | uffix<br>o 85°C  |      |

|----------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|------------------|------------------------------------------------------------------|------------------|------|

| Parameter                                    | Symbol                                              | $V+ = 15 \text{ V}, V- = -3 \text{ V} $ $V_{L} = 5 \text{ V}, \overline{\text{RS}} = 2.0 \text{ V} $ $\overline{\text{SALVO}}, \overline{\text{CS}}, \overline{\text{WR}}, \overline{\text{I/O}} = 0.8 \text{ V} $ | Temp <sup>b</sup> | Тур <sup>с</sup> | Min <sup>d</sup> | Max <sup>d</sup> | Min <sup>d</sup>                                                 | Max <sup>d</sup> | Unit |

| Analog Switch                                |                                                     |                                                                                                                                                                                                                    |                   |                  |                  |                  |                                                                  |                  |      |

| Analog Signal Range <sup>e</sup>             | V <sub>ANALOG</sub>                                 | V - = -5 V                                                                                                                                                                                                         | Full              |                  | -5               | 8                | -5                                                               | 8                | V    |

| Drain-Source On-Resistance                   | r <sub>DS(on)</sub>                                 | $I_S = -10 \text{ mA}, V_D = 0 \text{ V}$<br>$V_{AIH} = 2.0 \text{ V}, V_{AIL} = 0.8 \text{ V}$                                                                                                                    | Room<br>Full      | 45               |                  | 90<br>120        |                                                                  | 90<br>120        | Ω    |

| Resistance Match<br>Between Channels         | $\Delta r_{DS(on)}$                                 | Sequence Each Switch On                                                                                                                                                                                            | Room              | 3                |                  | 9                |                                                                  | 9                | 52   |

| Source Off Leakage Current                   | I <sub>S(off)</sub>                                 | $V_S = 8 \text{ V}, V_D = 0 \text{ V}, \overline{RS} = 0.8 \text{ V}$                                                                                                                                              | Room<br>Full      |                  | -20<br>-200      | 20<br>200        | -20<br>-200                                                      | 20<br>200        |      |

| Drain Off Leakage Current                    | $I_{D(off)}$                                        | $V_S = \underbrace{0}_{RS} V, V_D = 8 V,$ $\overline{RS} = 0.8 V$                                                                                                                                                  | Room<br>Full      |                  | -20<br>-200      | 20<br>200        | $     \begin{array}{r}       -20 \\       -200     \end{array} $ | 20<br>200        | nA   |

| Total Switch On<br>Leakage Current           | I <sub>D(on)</sub>                                  | $V_S = V_D = 8 V$                                                                                                                                                                                                  | Room<br>Full      |                  | -20<br>-200<br>0 | 20<br>2000       | -20<br>-200                                                      | 20<br>200        |      |

| Digital Input/Output                         |                                                     |                                                                                                                                                                                                                    |                   |                  |                  |                  |                                                                  |                  |      |

| Input Voltage High                           | $V_{ m AIH}$                                        |                                                                                                                                                                                                                    | Full              |                  | 2                |                  | 2                                                                |                  | ***  |

| Input Voltage Low                            | V <sub>AIL</sub>                                    |                                                                                                                                                                                                                    | Full              |                  |                  | 0.8              |                                                                  | 0.8              | V    |

| Address Input Current                        | $I_{AI}$                                            | $V_{AI} = 0 \text{ V or } 2 \text{ V or } 5 \text{ V}$                                                                                                                                                             | Room<br>Full      | 0.1              | -1<br>-10        | 1<br>10          | -1<br>-10                                                        | 1<br>10          |      |

| Address Output Current                       | $I_{AO}$                                            | $V_{AO} = 2.7 \text{ V}$ , See Truth Table                                                                                                                                                                         | Room              | -600             |                  | -200             |                                                                  | -200             | μΑ   |

| _                                            |                                                     | $V_{AO} = 0.4 \text{ V}$ , See Truth Table                                                                                                                                                                         | Room              | 1500             | 500              |                  | 500                                                              |                  |      |

| DIS Pin Sink Current                         | $I_{DIS}$                                           |                                                                                                                                                                                                                    | Room              | 1.5              |                  |                  |                                                                  |                  | mA   |

| <b>Dynamic Characteristics</b>               |                                                     |                                                                                                                                                                                                                    | _                 |                  |                  | _                | _                                                                | _                | _    |

| On State Input Capacitance <sup>e</sup>      | on State Input Capacitance <sup>e</sup> $C_{S(on)}$ |                                                                                                                                                                                                                    | Room              | 30               |                  |                  |                                                                  | 40               |      |

|                                              | CS(on)                                              | 1 In to 4 Out, See Figure 11                                                                                                                                                                                       | Room              | 120              |                  |                  |                                                                  | 160              | ] _  |

| Off State Input Capacitance <sup>e</sup>     | $C_{S(off)}$                                        |                                                                                                                                                                                                                    | Room              | 8                |                  | 20               |                                                                  | 20               | pF   |

| Off State Output<br>Capacitance <sup>e</sup> | $C_{D(off)}$                                        | See Figure 11                                                                                                                                                                                                      | Room              | 10               |                  | 20               |                                                                  | 20               |      |

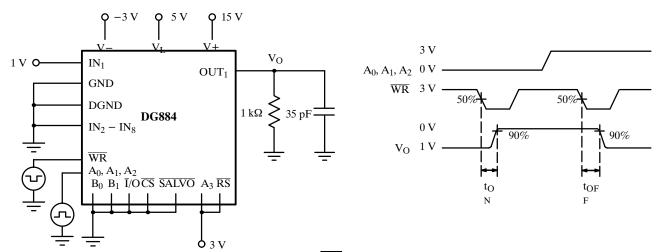

| Transition Time                              | t <sub>TRANS</sub>                                  | See Figure 5                                                                                                                                                                                                       | Room              |                  |                  |                  |                                                                  | 300              |      |

| Break-Before-Make Interval                   | t <sub>OPEN</sub>                                   | See Figure 3                                                                                                                                                                                                       | Full              |                  |                  | 10               |                                                                  | 10               |      |

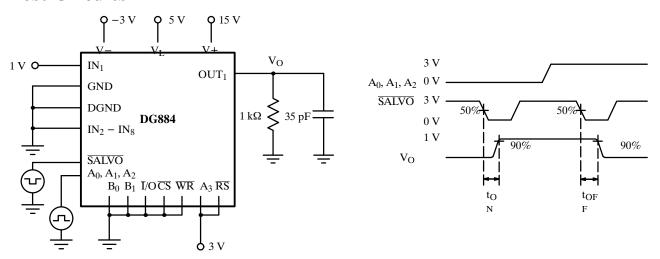

| SALVO, WR Turn On Time                       | t <sub>ON</sub>                                     | $R_L$ = 1 k $\Omega$ , $C_L$ = 35 pF 50% Control to 90% Output                                                                                                                                                     | Room<br>Full      |                  |                  | 300<br>500       |                                                                  | 300              | ns   |

| SALVO, WR Turn Off Time                      | t <sub>OFF</sub>                                    | See Figure 3                                                                                                                                                                                                       | Room<br>Full      |                  |                  | 175<br>300       |                                                                  | 175              |      |

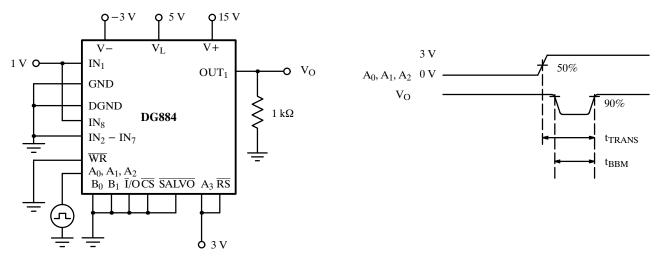

| Charge Injection                             | Q                                                   | See Figure 6                                                                                                                                                                                                       | Room              | -100             |                  |                  |                                                                  |                  | рC   |

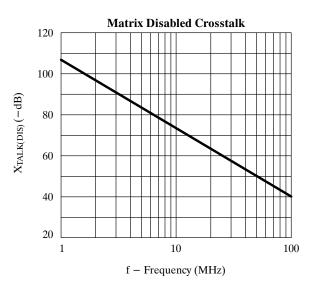

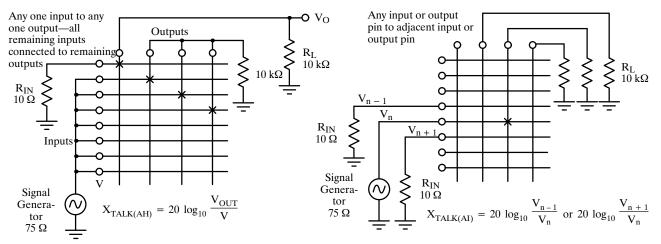

| Matrix Disabled Crosstalk                    | X <sub>TALK(DIS)</sub>                              | $R_{IN} = R_L = 75 \Omega$<br>f = 5 MHz, See Figure 10                                                                                                                                                             | Room              | -82              |                  |                  |                                                                  |                  |      |

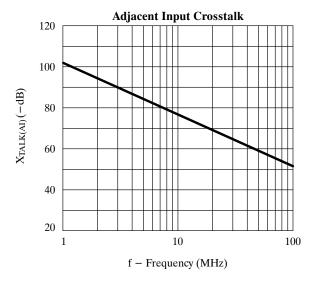

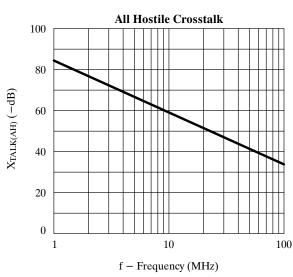

| Adjacent Input Crosstalk                     | X <sub>TALK</sub> (AI)                              | $R_{IN} = 10 \Omega, R_L = 10 k\Omega$<br>f = 5 MHz, See Figure 9                                                                                                                                                  | Room              | -85              |                  |                  |                                                                  |                  | dB   |

| All Hostile Crosstalk                        | X <sub>TALK(AH)</sub>                               | $R_{IN} = 10 \Omega$ , $R_L = 10 k\Omega$<br>f = 5 MHz, See Figure 8                                                                                                                                               | Room              | -66              |                  |                  |                                                                  |                  |      |

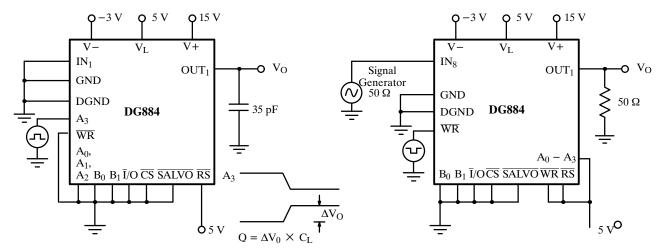

| Bandwidth                                    | BW                                                  | $R_L = 50 \Omega$ , See Figure 7                                                                                                                                                                                   | Room              | 300              |                  |                  |                                                                  |                  | MHz  |

# **Specifications**<sup>a</sup>

|                                                           |                   | Test Conditions<br>Unless Otherwise Specified                                                                                                                                                                      |                   |                  |                  | uffix<br>125°C   |                  | uffix<br>o 85°C  |         |

|-----------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|------------------|------------------|------------------|---------|

| Parameter                                                 | Symbol            | $V+ = 15 \text{ V}, V- = -3 \text{ V} $ $V_{L} = 5 \text{ V}, \overline{\text{RS}} = 2.0 \text{ V} $ $\overline{\text{SALVO}}, \overline{\text{CS}}, \overline{\text{WR}}, \overline{\text{I/O}} = 0.8 \text{ V} $ | Temp <sup>b</sup> | Тур <sup>с</sup> | Min <sup>d</sup> | Max <sup>d</sup> | Min <sup>d</sup> | Max <sup>d</sup> | Unit    |

| Power Supplies                                            |                   |                                                                                                                                                                                                                    |                   |                  |                  |                  |                  |                  |         |

| Positive Supply Current                                   | I+                |                                                                                                                                                                                                                    | Room<br>Full      | 1.5              |                  | 3<br>6           |                  | 3<br>6           | mA      |

| Negative Supply Current                                   | I-                | All Inputs At GND or 2 V $\overline{RS} = 2 \text{ V}$                                                                                                                                                             | Room<br>Full      | -1.5             | -3<br>-5         |                  | -3<br>-5         |                  | l III/A |

| Digital GND Supply Current                                | $I_{\mathrm{DG}}$ |                                                                                                                                                                                                                    | Full              | -275             | -750             |                  | -750             |                  | 4       |

| Logic Supply Current                                      | $I_{L}$           |                                                                                                                                                                                                                    | Full              | 200              |                  | 500              |                  | 500              | μΑ      |

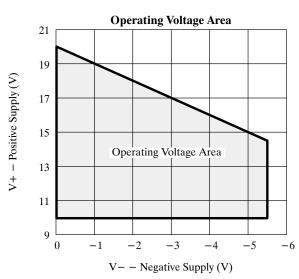

| T 10 15 5                                                 | V+ to V-          | See Operating Voltage Range                                                                                                                                                                                        | Full              |                  | 13               | 20               | 13               | 20               |         |

| Functional Operating Supply<br>Voltage Range <sup>e</sup> | V- to GND         | (Typical Characteristics)                                                                                                                                                                                          | Full              |                  | -5.5             | 0                | -5.5             | 0                | V       |

| 5 0                                                       | V+ to GND         | page 6                                                                                                                                                                                                             | Full              |                  | 10               | 20               | 10               | 20               |         |

| Minimum Input Timing Re                                   | quirements        | _                                                                                                                                                                                                                  |                   |                  |                  |                  |                  |                  |         |

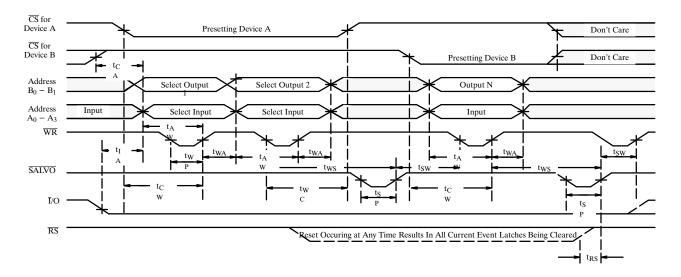

| Address Write Time                                        | $t_{AW}$          |                                                                                                                                                                                                                    | Full              | 20               | 50               |                  | 50               |                  |         |

| Minimum WR Pulse Width                                    | t <sub>WP</sub>   |                                                                                                                                                                                                                    | Full              | 50               | 100              |                  | 100              |                  | 1       |

| Write Address Time                                        | t <sub>WA</sub>   |                                                                                                                                                                                                                    | Full              | -10              | 10               |                  | 10               |                  | 1       |

| Chip Select Write Time                                    | $t_{CW}$          |                                                                                                                                                                                                                    | Full              | 50               | 100              |                  | 100              |                  | 1       |

| Write Chip Select Time                                    | t <sub>WC</sub>   |                                                                                                                                                                                                                    | Full              | 25               | 75               |                  | 75               |                  | 1       |

| Minimum SALVO Pulse<br>Width                              | t <sub>SP</sub>   |                                                                                                                                                                                                                    | Full              | 50               | 100              |                  | 100              |                  | 1       |

| SALVO Write Time                                          | $t_{SW}$          | See Figure 1                                                                                                                                                                                                       | Full              | -10              | 10               |                  | 10               |                  | ns      |

| Write SALVO Time                                          | t <sub>WS</sub>   |                                                                                                                                                                                                                    | Room              | 20               |                  |                  | 50               |                  | 1       |

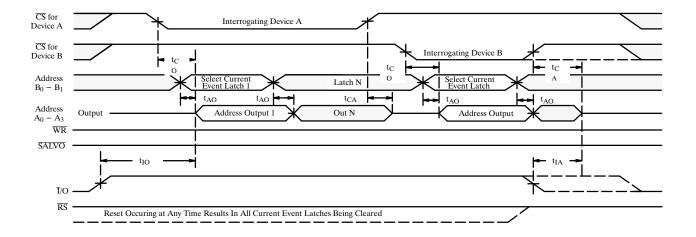

| Input Output Time                                         | $t_{ m IO}$       |                                                                                                                                                                                                                    | Room              | 150              | 200              |                  | 200              |                  | 1       |

| Address Output Time                                       | $t_{AO}$          |                                                                                                                                                                                                                    | Room              | 150              | 200              |                  | 200              |                  | ]       |

| Chip Select Output Time                                   | t <sub>CO</sub>   |                                                                                                                                                                                                                    | Room              | 150              | 200              |                  | 200              |                  | 1       |

| Chip Select Address Time                                  | $t_{CA}$          |                                                                                                                                                                                                                    | Room              | 60               |                  |                  | 100              |                  | ]       |

| Reset to SALVO                                            | $t_{RS}$          |                                                                                                                                                                                                                    | Full              |                  | 50               |                  | 50               |                  | 1       |

| Ī/O Address Input Time                                    | $t_{\mathrm{IA}}$ |                                                                                                                                                                                                                    | Room              | 50               |                  |                  |                  |                  | 1       |

- Notes: a. Refer to PROCESS OPTION FLOWCHART (Section 5 of the 1994 Data Book or FaxBack number 7103).

- b. Room = 25°C, Full = as determined by the operating temperature suffix.

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

Guaranteed by design, not subject to production test.

# **Typical Characteristics**

# **Timing Diagrams and Parameter Definitions**

| Symbol            | Parameter         | Description                                                             |

|-------------------|-------------------|-------------------------------------------------------------------------|

| $T_{AW}$          | Address to Write  | Minimum time address must be valid before WR goes high                  |

| T <sub>WA</sub>   | Write to Address  | Minimum time address must remain valid after WR pulse goes high         |

| $T_{\mathrm{WP}}$ | WR Pulse          | Minimum time of WR pulse width to write address into Next Event latches |

| $T_{CW}$          | Chip Select to WR | Minimum time chip select must be valid before a WR pulse                |

| $T_{ m WC}$       | WR to Chip Select | Minimum time chip select must remain valid after WR pulse               |

| $T_{SP}$          | SALVO Pulse       | Minimum time of SALVO pulse width                                       |

| T <sub>WS</sub>   | WR to SALVO       | Minimum time from WR pulse to SALVO to load new address                 |

| $T_{SW}$          | SALVO to WR       | Minimum time from SALVO pulse to WR to load current address             |

| $T_{IA}$          | Ī/O to Address In | Minimum time I/O must be valid before address applied                   |

# Timing Diagrams and Parameter Definitions (Cont'd)

| Symbol          | Parameter         | Description                                                                                                        |

|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| $T_{RS}$        | RS to SALVO       | Minimum time $\overline{\text{RS}}$ must be valid before $\overline{\text{SALVO}}$ pulse                           |

| $T_{IO}$        | Ī/O to Output     | Minimum time $\overline{I}/O$ must be valid before address output valid                                            |

| T <sub>AO</sub> | Address to Output | Minimum time address $B_X$ must be valid until address $A_X$ output valid                                          |

| $T_{CO}$        | CS to Output      | Minimum time $\overline{\text{CS}}$ must be valid until $A_X$ output is valid                                      |

| T <sub>CA</sub> | CS to Address In  | Minimum time $\overline{\text{CS}}$ must be valid before address applied if $\overline{\text{I}}/\text{O}$ is high |

Figure 1. Input Timing Requirements

Figure 2. Output Timing Requirements

### **Test Circuits**

Figure 3. SALVO Turn On/Off Time

Figure 4. WR Turn On/Off Time

Figure 5. Transition Time and Break-Before-Make Interval

### **Test Circuits**

Figure 6. Charge Injection

**Figure 7.** −3 dB Bandwidth

Figure 8. All Hostile Crosstalk

Figure 9. Adjacent Input Crosstalk

Figure 10. Matrix Disabled Crosstalk

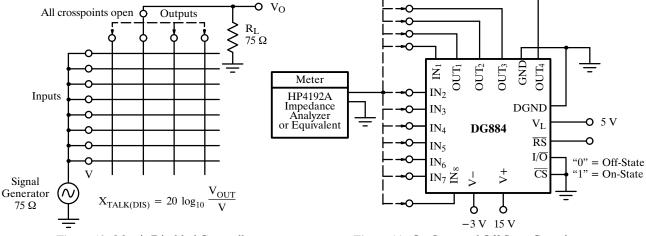

Figure 11. On-State and Off-State Capacitances

### **Pin Description**

| Pin                                              | Symbol                                                 | Description                                                                                                              |  |

|--------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 1, 3, 4, 6, 8, 10, 12, 14,<br>16, 18, 20, 41, 43 | GND                                                    | Analog Signal Ground                                                                                                     |  |

| 39                                               | DGND                                                   | Digital Ground                                                                                                           |  |

| 26                                               | V+                                                     | Positive Supply Voltage                                                                                                  |  |

| 21                                               | V-                                                     | Negative Supply Voltage                                                                                                  |  |

| 38                                               | $V_{\rm L}$                                            | Logic Supply Voltage—generally 5 V                                                                                       |  |

| 5, 7, 9, 11, 13, 15, 17, 19                      | IN <sub>1</sub> to IN <sub>8</sub>                     | 8 Analog Input Channels                                                                                                  |  |

| 2, 40, 42, 44                                    | OUT <sub>1</sub> to<br>OUT <sub>4</sub>                | 4 Analog Output Channels                                                                                                 |  |

| 29                                               | Ī/O                                                    | Determines whether data is being written into the Next Event latches or read from the Current Event latches              |  |

| 30                                               | CS                                                     | Chip Select—a logic input                                                                                                |  |

| 31, 32, 22, 24                                   | $A_0, A_1, A_2, A_3$                                   | IN Address—logic inputs or outputs as defined by $\overline{I}/O$ pin, select one of eight IN channels                   |  |

| 27, 28                                           | B <sub>0</sub> , B <sub>1</sub>                        | OUT Address—logic inputs, select one of four OUT channels                                                                |  |

| 35                                               | WR                                                     | Write command that latches A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> into the Next Event latches |  |

| 36                                               | SALVO                                                  | Master write command, that in one action, transfers all the data from Next Event latches into Current Event latches      |  |

| 37                                               | RS                                                     | Reset—a low will clear the Current Event latches                                                                         |  |

| 22, 23, 24, 25                                   | $\overline{\text{DIS}}_1$ to $\overline{\text{DIS}}_4$ | Open drain disable outputs—these outputs pull low when the corresponding OUT channel is off                              |  |

# **Device Description**

The DG884 is the world's first monolithic wideband crosspoint array that operates from dc to >100 MHz. The DG884 offers the ability to route any one of eight input signals to any one of four OUT pins. Any input can be routed to one, two, three or four OUTs simultaneously with no risk of shorting inputs together (guaranteed by design).

Each crosspoint is configured as a "T" switch in which DMOS FETs are used due to their excellent low resistance and low capacitance characteristics. Each OUT line has a series switch that minimizes capacitive loading when the OUT is off.

### **Interfacing**

The DG884 was designed to allow complex matrices to be developed while maintaining a simple control interface. The status of the  $\overline{I}/O$  pin determines whether the DG884 is being written to or read from (see Figures 1 and 2).

In order to WRITE to an individual latch,  $\overline{CS}$  and  $\overline{I}/O$  need to be low, while  $\overline{RS}$ ,  $\overline{WR}$  and  $\overline{SALVO}$  must be high. The IN to OUT path is selected by using address  $A_0$  through  $A_3$  to define the IN line and address  $B_0$  and  $B_1$  to define the OUT line. That is, The IN defined by

$A_0$  through  $A_3$  is electrically connected to the OUT defined by  $B_0$ ,  $B_1$ . This chosen path is loaded into the Next Event latches when  $\overline{WR}$  goes low and returns high again. This operation is repeated up to three more times if other crosspoint connections need to be changed.

Upon completing all crosspoint connections that are to be changed in a single device, other DG884s can be similarly preset by taking the  $\overline{\text{CS}}$  pin low on the appropriate device. When all DG884s are preset, the Current Event latches are simultaneously changed by a single  $\overline{\text{SALVO}}$  command applied to all devices. In this manner the crosspoint configuration of any number of devices can be simultaneously updated.

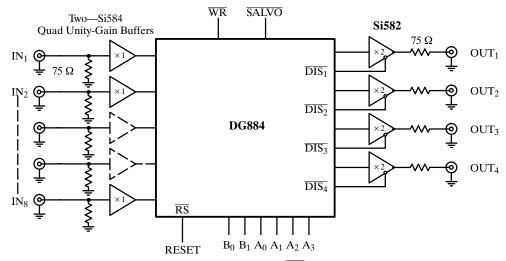

#### **DIS** Outputs

Four open drain disable OUTs are provided to control external line drivers or to provide visual or electrical signaling. For example, any or all of the  $\overline{DIS}$  OUTs can directly interface with a Siliconix Si582 Video Amplifier to place it into a high impedance, low-power standby mode when the corresponding OUT is not being used. (See Figure 15). The  $\overline{DIS}$  outputs are low and sink to V— when corresponding OUT is open or  $\overline{RS}$  is low.

# **Device Description (Cont'd)**

#### Reset

The reset function  $(\overline{RS})$  allows the resetting of all crosspoints to a known state (open). At power up, the reset facility may be used to guarantee that all switches are open. It should be noted that  $\overline{RS}$  clears the Current Event latches, but the Next Event latches remain unchanged. This useful facility allows the user to return the matrix to its previous state (prior to reset) by simply applying the  $\overline{SALVO}$  command. Alternatively, the user can reprogram the Next Event latches, and then apply the  $\overline{SALVO}$  command to reconfigure the matrix to a new state.

#### Readback

The  $\overline{I}/O$  facility enables the user to write data to the Next Event latches or to read the contents of the Current Event latches. This feature permits the central controller to periodically monitor the state of the matrix. If a power loss to the controller occurs, the readback feature helps the matrix to recover rapidly. It also offers a means to perform PC board diagnostics both in production and in system operation.

One of Four Blocks of Logic/Latches Shown

Figure 12. Control Circuitry

### **Applications**

Note:  $\overline{\text{DIS}}$  outputs are used to power down the Si582 amplifiers.

Figure 13. Fully Buffered  $8 \times 4$  Crosspoint

#### **Power Supplies and Decoupling**

A useful feature of the DG884 is its power supply flexibility. It can be operated from dual supplies, or a single positive supply (V – connected to 0 V) if required. Allowable operating voltage ranges are shown in Operating Voltage Range (Typical Characteristics) graph, page 6.

Note that the analog signal must not go below V- by more than 0.3 V (see absolute maximum ratings). However, the addition of a V- pin has a number of advantages:

- 1) It allows flexibility in analog signal handling, i.e. with V = -5 V and V + = 15 V, up to  $\pm 5 \text{ V}$  ac signals can be accepted.

- 2) The value of on-capacitance (C<sub>S(on)</sub>) may be reduced by increasing the value of V−. It is useful to note that optimum video differential phase and gain occur when V− is −3 V. Note that V+ has no effect on C<sub>S(on)</sub>.

- V- eliminates the need to bias an ac analog signal using potential dividers and large decoupling capacitors.

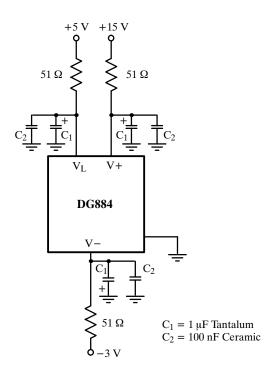

It is established RF design practice to incorporate sufficient bypass capacitors in the circuit to decouple the power supplies to all active devices in the circuit. The dynamic performance of the DG884 is adversely affected by poor decoupling of power supply pins. Also, since the substrate of the device is connected to the negative supply, proper decoupling of this pin is essential.

#### **Rules:**

- 1) Decoupling capacitors should be incorporated on all power supply pins  $(V+, V-, V_L)$ .

- 2) They should be mounted as close as possible to the device pins.

- 3) Capacitors should have good high frequency characteristics—tantalum bead and/or monolithic ceramic disc types are suitable.

Recommended decoupling capacitors are 1- to 10- $\mu F$  tantalum bead, in parallel with 100-nF monolithic ceramic.

4) Additional high frequency protection may be provided by  $51-\Omega$  carbon film resistors connected in series with the power supply pins (see Figure 14).

# **Applications (Cont'd)**

Figure 14. DG884 Power Supply Decoupling

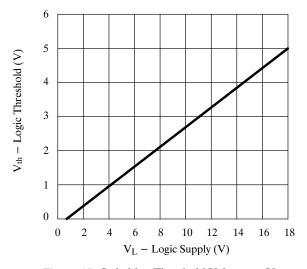

The  $V_L$  pin permits interface to various logic types. The device is primarily designed to be TTL or CMOS logic compatible with +5 V applied to  $V_L$ . The actual logic threshold can be raised simply by increasing  $V_L$ .

A typical switching threshold versus  $V_L$  is shown in Figure 15.

Figure 15. Switching Threshold Voltage vs.  $V_L$

These devices feature an address readback facility whereby the last address written to the device may be read by the system. This allows improved status monitoring and hand shaking without additional external components.

When the  $\overline{I}/O$  assigns the address output condition, the  $A_X$  address pins can sink or source current for logic low and high, respectively. Note that  $V_L$  is the logic high output condition. This point must be respected if  $V_L$  is varied for input logic threshold shifting.

Note: Even though these devices are designed to be latchup resistant,  $V_L$  must not exceed V+ by more than 0.3 V in operation or during power supply on/off sequencing.

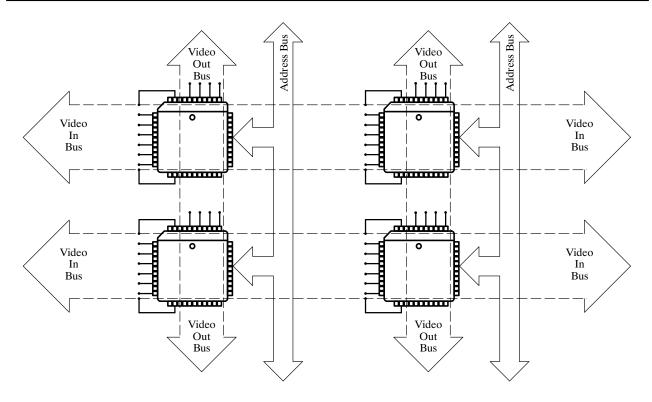

#### Layout

The PLCC package pinout is optimized so that large crosspoint arrays can be easily implemented with a minimum number of PCB layers (see Figure 16). Crosstalk is minimized and off-isolation is optimized by having ground pins located adjacent to each input and output signal pins. Optimum off-isolation and low crosstalk performance can only be achieved by the proper use of RF layout techniques: avoid sockets, use ground planes, avoid ground loops, bypass the power supplies with high frequency type capacitors (low ESR, low ESL), use striplines to maintain transmission line impedance matching.

For additional information please refer to Application Note AN504.

Figure 16. 16 × 8 Expandable Crosspoint Matrix Using DG884