# **Component Video Selector**

### **Features**

- Wide Bandwidth: 200 MHz

- Very Low Crosstalk: −70 dB at 5 MHz

- CMOS Compatible

- I<sup>2</sup>C Bus Compatible

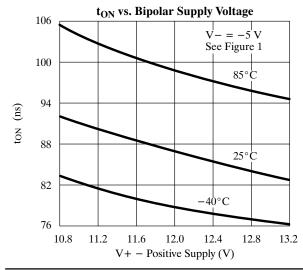

- Fast Switching—t<sub>ON</sub>: <200 ns

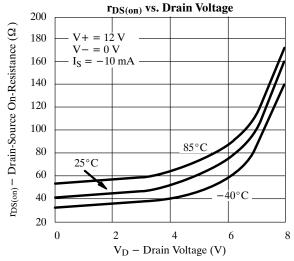

- Low r<sub>DS(on)</sub>: 44 Ω

- Single Supply Capability

## **Benefits**

- Low Insertion Loss

- Improved System Performance

- Reduced Power Consumption

- Easily Interfaced

- Future System Expansion via I<sup>2</sup>C Bus

## **Applications**

- Component Video Switching: RGB + SYNC, S-VHS, Y-C, etc.

- Audio/Video Routing

- Digital TV

- ATE

- I<sup>2</sup>C Bus Audio/Video Systems

- SCART Video Switching

## **Description**

The DG894 is a monolithic video selector designed for switching a variety of component video signals. The low on-resistance and low capacitance of the DG894 make it ideal for video/audio signal routing. Switch control can be through direct CMOS addressing or through the two-wire I<sup>2</sup>C bus.

The DG894 is built on the Siliconix proprietary D/CMOS process that combines n-channel DMOS switching FETs with low-power CMOS control logic and drivers. Low-capacitance DMOS FETs are used to achieve high levels of off isolation at low cost.

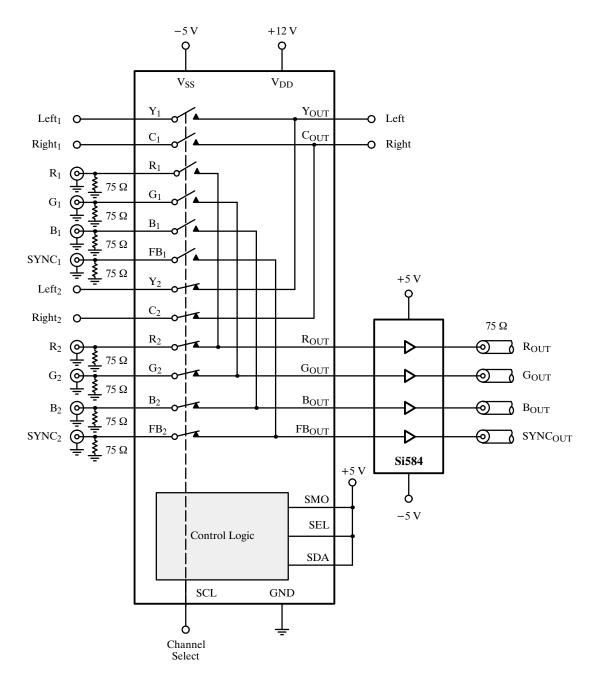

## **Functional Block Diagram and Pin Configuration**

#### **Truth Table**

| SMO | SEL | SDA                                       | SCL                                       | Function/Switch On                                                                                  |  |  |  |

|-----|-----|-------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| 0   | 0   | $I^2C$ Bus Operation, Address $A_0 = "1"$ |                                           |                                                                                                     |  |  |  |

| 0   | 1   | I <sup>2</sup> C Bu                       | $I^2C$ Bus Operation, Address $A_0 = "0"$ |                                                                                                     |  |  |  |

| 1   | 0   | 0                                         | 0                                         | All switches off                                                                                    |  |  |  |

| 1   | 0   | 0                                         | 1                                         | $Y_0, C_0$                                                                                          |  |  |  |

| 1   | 0   | 1                                         | 0                                         | $Y_1, C_1$                                                                                          |  |  |  |

| 1   | 0   | 1                                         | 1                                         | $Y_2, C_2$                                                                                          |  |  |  |

| 1   | 1   | 0                                         | 0                                         | $R_1, G_1, B_1, F_1$                                                                                |  |  |  |

| 1   | 1   | 0                                         | 1                                         | $R_2, G_2, B_2, F_2$                                                                                |  |  |  |

| 1   | 1   | 1                                         | 0                                         | $R_1, G_1, B_1, F_1, Y_1, C_1$                                                                      |  |  |  |

| 1   | 1   | 1                                         | 1                                         | R <sub>2</sub> , G <sub>2</sub> , B <sub>2</sub> , F <sub>2</sub> , Y <sub>2</sub> , C <sub>2</sub> |  |  |  |

#### **Ordering Information**

| Temp Range  | Package               | Part Number |  |  |

|-------------|-----------------------|-------------|--|--|

| −40 to 85°C | 28-Pin Plastic DIP    | DG894DJ     |  |  |

| -40 to 65 C | 28-Pin Wide Body SOIC | DG894DW     |  |  |

**TEMIC**

DG894 Siliconix

# **Absolute Maximum Ratings**

| V+ to GND0.3 V to 19 V | Continuous Current (Any Terminal)                                                                                                          |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| V+ to V0.3 V to 19 V   | Current (Any Terminal) Pulsed 1 ms, 10% Duty Cycle Max 40 mA                                                                               |

| V- to GND10 V to 0.3 V | Storage Temperature                                                                                                                        |

| Digital Inputs         | Power Dissipation (Package) <sup>a</sup> 625 mW           28-Pin Plastic DIP         625 mW           28-Pin Wide Body SOIC         450 mW |

| Signal Inputs          | Notes: a. All leads welded or soldered to PC board.                                                                                        |

# **Specifications**

|                                           |                       | Test Conditions<br>Unless Otherwise Specified                                                                          |                   | Limits<br>-40 to 85°C |                  |                  |       |  |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|------------------|------------------|-------|--|

| Parameter                                 | Symbol                | $V_{DD} = 12 \text{ V}, V_{SS} = -5 \text{ V}$<br>$V_{INH} = 3 \text{ V}, V_{INL} = 1.5 \text{ V}^{e}$                 | Temp <sup>a</sup> | Min <sup>c</sup>      | Typ <sup>b</sup> | Max <sup>c</sup> | Unit  |  |

| Analog Switch                             |                       |                                                                                                                        |                   |                       |                  |                  |       |  |

| Analog Signal Range <sup>d</sup>          | V                     | $V_{DD} = 12 \text{ V}, V_{SS} = \text{GND}$                                                                           | Full              | 0                     |                  | 4                | v     |  |

| Analog Signal Kange                       | V <sub>ANALOG</sub>   | $V_{DD} = 12 \text{ V}, V_{SS} = -5 \text{ V}$                                                                         | Full              | -2                    |                  | 2                | 1     |  |

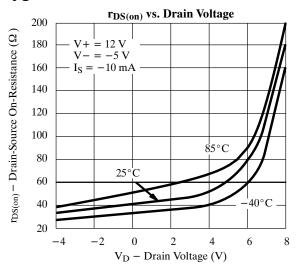

| Drain-Source On-Resistance                | r <sub>DS(on)</sub>   | I 10 A 37 O 37                                                                                                         | Room<br>Full      |                       | 44<br>51         | 100<br>150       |       |  |

| Resistance Match Between<br>Channels      | $\Delta r_{DS(on)}$   | $I_{S} = -10 \text{ mA}, V_{D} = 0 \text{ V}$                                                                          | Room              |                       | 10               |                  | Ω     |  |

| Source Off Leakage Current                | I <sub>S(off)</sub>   | $V_S = 4 \text{ V}, V_D = 0 \text{ V}$                                                                                 | Room<br>Full      | -10<br>-100           | -0.05            | 10<br>100        |       |  |

| Drain Off Leakage Current                 | I <sub>D(off)</sub>   | $V_D = 4 \text{ V}, V_S = 0 \text{ V}$                                                                                 | Room<br>Full      | -10<br>-100           | -0.05            | 10<br>100        | nA    |  |

| Total Switch On Leakage Current           | I <sub>D(on)</sub>    | $V_D = V_S = 4 V$                                                                                                      | Room<br>Full      | -10<br>-100           | -0.07            | 10<br>100        |       |  |

| Input                                     |                       |                                                                                                                        | •                 | •                     |                  | •                | •     |  |

| Input Voltage High                        | V <sub>INH</sub>      |                                                                                                                        | Full              | 3                     | 2.55             |                  |       |  |

| Input Voltage Low                         | V <sub>INL</sub>      |                                                                                                                        | Full              |                       | 2.55             | 1.5              | V     |  |

| Input Threshold                           | $V_{th}$              |                                                                                                                        | Room              |                       | 2.55             |                  | 1     |  |

| Temp Coefficient of Input<br>Threshold    | $TC_{th}$             |                                                                                                                        | Full              |                       | -200             |                  | μV/°C |  |

| Input Current                             | I <sub>IN</sub>       | $V_{IN} = GND \text{ or } V_{DD}$                                                                                      | Room<br>Full      | -1<br>-20             | 0.05             | 1<br>20          | μΑ    |  |

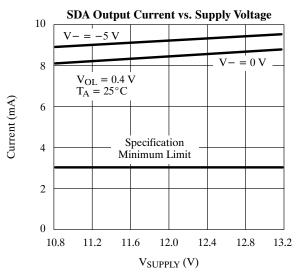

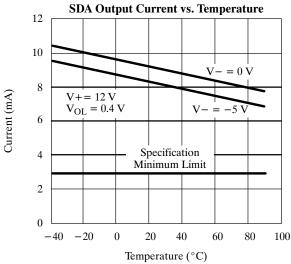

| Output Voltage Low                        | V <sub>OL</sub>       | Pin 21, During Acknowledge,<br>$I_{OL} = 3 \text{ mA}$                                                                 | Room              |                       |                  | 0.4              | V     |  |

| Dynamic                                   |                       |                                                                                                                        |                   | ·                     |                  |                  |       |  |

| Input Capacitanced                        | C <sub>in</sub>       | Pin 21, 22                                                                                                             | Room              |                       | 3                | 10               |       |  |

| On State Input Capacitance <sup>d</sup>   | C <sub>S(on)</sub>    | $V_S = V_D = 0 V$                                                                                                      | Room              |                       | 10               | 15               |       |  |

| Off State Input Capacitance <sup>d</sup>  | C <sub>S(off)</sub>   | $V_S = 0 V$                                                                                                            | Room              |                       | 4                | 8                | pF    |  |

| Off State Output Capacitance <sup>d</sup> | C <sub>D(off)</sub>   | $V_D = 0 V$                                                                                                            | Room              |                       | 4                | 8                | 1     |  |

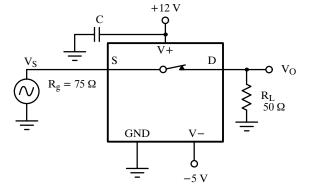

| Bandwidthd                                | BW                    | $R_L = 50 \Omega$ , See Figure 1                                                                                       | Room              | 200                   | 500              |                  | MHz   |  |

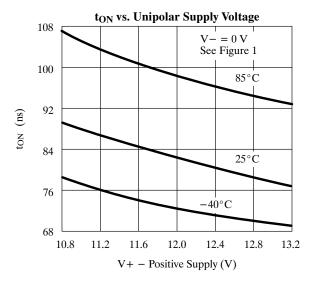

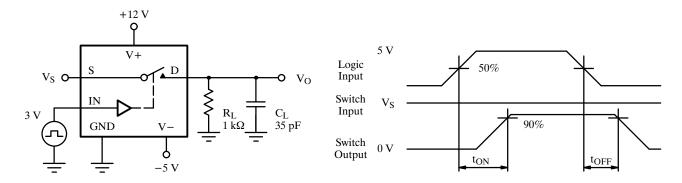

| Turn On Time                              | t <sub>ON</sub>       | $R_L = 1 \text{ k}\Omega$ , $C_L = 35 \text{ pF}$ , 50% to 90%<br>$V_{SS} = -5 \text{ V}$ , 0 V, $V_S = 3 \text{ V}$ , | Room              |                       |                  | 200              |       |  |

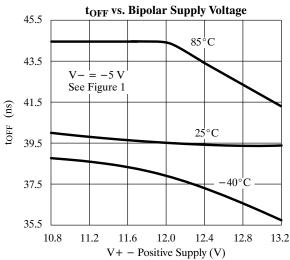

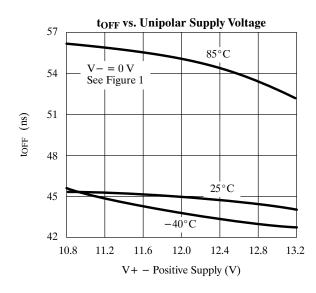

| Turn Off Time                             | t <sub>OFF</sub>      | $\mathbf{v}_{SS} = -3  \mathbf{v}, 0  \mathbf{v}, \mathbf{v}_{S} = 3  \mathbf{v},$<br>See Figure 1                     | Room              |                       |                  | 180              | ns    |  |

| SCL Max Clock Frequency                   | F <sub>SCL(MAX)</sub> |                                                                                                                        | Full              | 100                   |                  |                  | kHz   |  |

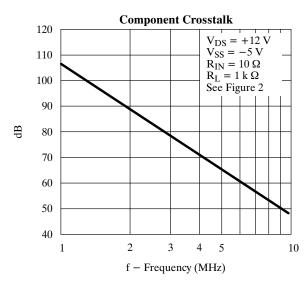

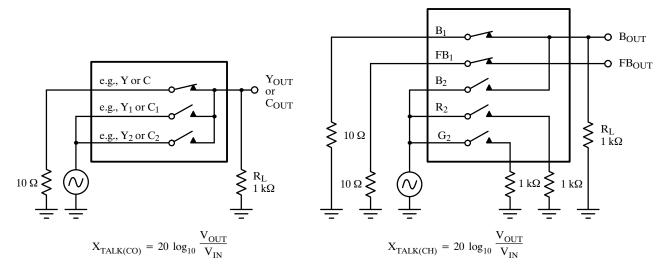

| Component Crosstalk                       | X <sub>TALK(CO)</sub> | $R_{IN} = 10 \Omega, R_{L} = 1 k\Omega$                                                                                | Room              |                       | -85              |                  | 155   |  |

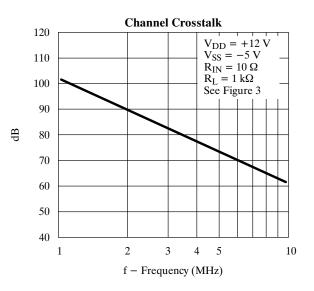

| Channel Crosstalk                         | X <sub>TALK(CH)</sub> | f = 5  MHz, See Figure 2 and 3                                                                                         | Room              |                       | -85              |                  | dB    |  |

# **Specifications**

|                         |        | Test Conditions<br>Unless Otherwise Specified                                                          |                   | Limits<br>-40 to 85°C |                  |                  |      |

|-------------------------|--------|--------------------------------------------------------------------------------------------------------|-------------------|-----------------------|------------------|------------------|------|

| Parameter               | Symbol | $V_{DD} = 12 \text{ V}, V_{SS} = -5 \text{ V}$<br>$V_{INH} = 3 \text{ V}, V_{INL} = 1.5 \text{ V}^{e}$ | Temp <sup>a</sup> | Min <sup>c</sup>      | Typ <sup>b</sup> | Max <sup>c</sup> | Unit |

| Supply Voltage          |        |                                                                                                        |                   |                       |                  |                  |      |

| Positive Supply Current | I+     | All Control Inputs 0 V, 5 V                                                                            | Room<br>Full      |                       | 3<br>4           | 8<br>10          | mA   |

| Negative Supply Current | I–     | All Collitor inputs 0 v, 3 v                                                                           | Room<br>Full      | -8<br>-10             | -2.5<br>-3.0     |                  | IIIA |

#### Notes

- a. Room =  $25^{\circ}$ C, Full = as determined by the operating temperature suffix.

- b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- d. Guaranteed by design, not subject to production test.

- e.  $V_{IN}$  = input voltage to perform proper function.

Purchase of Siliconix DG894 components conveys a license to use them in the I<sup>2</sup>C system as defined by Philips.

# **Typical Characteristics**

DG894 Siliconix

# Typical Characteristics (Cont'd)

## **Test Circuits**

C<sub>L</sub> (includes fixture and stray capacitance)

$$V_{O} = V_{S} - \frac{R_{L}}{R_{L} + r_{DS(on)}}$$

Figure 1. Switching Time

Figure 2. Component Crosstalk

Figure 3. Channel Crosstalk

Figure 4. Bandwidth

**DG894 Siliconix**

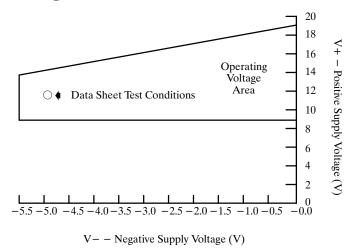

# **Operating Voltage Range**

Figure 5.

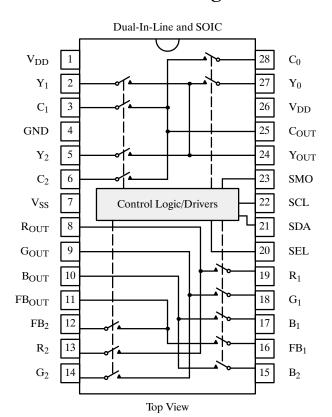

# **Pin Description**

| Symbol                                                                                                                                  | Description                                                                                    |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| $Y_0, Y_1, Y_2$                                                                                                                         | An analog channel input, typically luminance.                                                  |  |  |  |  |

| $C_0, C_1, C_2$                                                                                                                         | An analog channel input, typically chrominance.                                                |  |  |  |  |

| R <sub>1</sub> , R <sub>2</sub> , G <sub>1</sub> , G <sub>2</sub> , B <sub>1</sub> , B <sub>2</sub> , FB <sub>1</sub> , FB <sub>2</sub> | An analog channel input, typically "red", "green", "blue" or "fast blanking", as appropriate.  |  |  |  |  |

| GND                                                                                                                                     | Analog and digital ground.                                                                     |  |  |  |  |

| $V_{\mathrm{DD}}$                                                                                                                       | Positive supply voltage <sup>a</sup>                                                           |  |  |  |  |

| $V_{SS}$                                                                                                                                | Negative supply voltage                                                                        |  |  |  |  |

| $Y_{OUT}, C_{OUT}$                                                                                                                      | An analog channel output, typically luminance or chrominance, as appropriate                   |  |  |  |  |

| $R_{OUT}, G_{OUT}, B_{OUT}, FB_{OUT}$                                                                                                   | An analog channel output, typically "red", "green", "blue" or "fast blanking", as appropriate. |  |  |  |  |

| SMO                                                                                                                                     | A low selects serial mode (I <sup>2</sup> C) operation. A high selects CMOS operation.         |  |  |  |  |

| SDA                                                                                                                                     | Serial data line <sup>b</sup>                                                                  |  |  |  |  |

| SCL                                                                                                                                     | Serial clock line <sup>b</sup>                                                                 |  |  |  |  |

| SEL                                                                                                                                     | CMOS control line or I <sup>2</sup> C address <sup>c</sup> select line                         |  |  |  |  |

6

a. Both  $V_{\rm DD}$  pins (Pin 1 and Pin 26) must be connected for proper operation. b. SDA and SCL pins become CMOS control inputs when SMO = High.

c. The SEL pin, in I<sup>2</sup>C bus operation (i.e., with SMO low), is the least significant bit of the device address. This allows two devices to operate on the same I<sup>2</sup>C bus, yet retain independent control.

# **Applications**

# I<sup>2</sup>C Bus Operation—RGB Switching

Figure 6 shows an inexpensive RGB + stereo selector. The two audio channels are switched via the C, Y terminals. The Si584 quad video buffer drives four  $75-\Omega$  output lines.

Figure 6.

DG894 Siliconix

## **Applications (Cont'd)**

Figure 7.

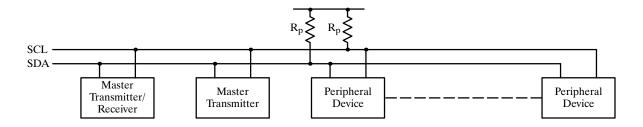

### Characteristics of the I<sup>2</sup>C Bus

The I<sup>2</sup>C Bus interface is ideally suited for communication between different ICs or modules. Its salient features are:

- Two wire bidirectional serial bus

- Serial data (SDA) and serial clock (SCL) lines

- Multi-master system (built-in arbitration for multi-master systems)

- Devices have independent clocks

- Master and slave devices can be receivers and/or transmitters.

- Each device has a unique address.

- Maximum bus clock rate of 100 kHz.

- Any number of interfaces may be connected to the bus

- Limited only by total capacitance of 400 pF

- Each pin on bus limited to 10-pF capacitance

- Input levels:

$V_{IL}$  max = 1.5 V (fixed supply operation)

$V_{IH} \min = 3 V$  (fixed supply operation)

$V_{IL} \max = 0.3 V_{DD}$  (wide range supply operation)

$V_{IH}$  min = 0.7  $V_{DD}$  (wide range supply operation)

#### **System Configuration**

R<sub>p</sub> value depends on:

- number of devices on bus

- total bus capacitance

- supply voltage (Figure 7).

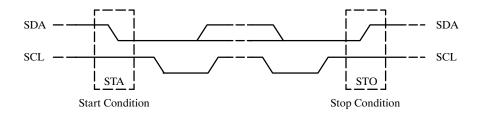

## **Data Transfer on the I<sup>2</sup>C Bus**

If the bus is not being used, both SDA and SCL lines must be left high.

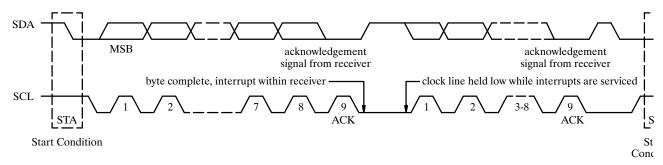

Every byte put onto the SDA line should be eight bits long (MSB first), followed by an acknowledge bit, which is generated by the receiving device.

Each data transfer is initiated with a start condition and ended with a stop condition. The first byte after a start condition is always the address byte. If this is the device's own address, the device will generate an acknowledge by pulling the SDA line low during the ninth clock pulse, then accept the data in subsequent bytes until another start or stop condition is detected.

The eight bit of the address byte is the read/write bit (high = read from addressed device, low = write to the addressed device) so, for the DG894, the address is only considered valid if the R/W bit is low.

Data bytes are always acknowledged during the ninth clock pulse by the addressed device. Note that during the acknowledge period the transmitting device must leave the SDA line high.

Premature termination of the data transfer is allowed by generating a stop condition at any time. When this happens, the DG894 will remain in the state defined by the last complete data byte transmitted.

## **Applications (Cont'd)**

Figure 8. START and STOP Conditions

**Figure 9.** Data Transfer on the I<sup>2</sup>C Bus

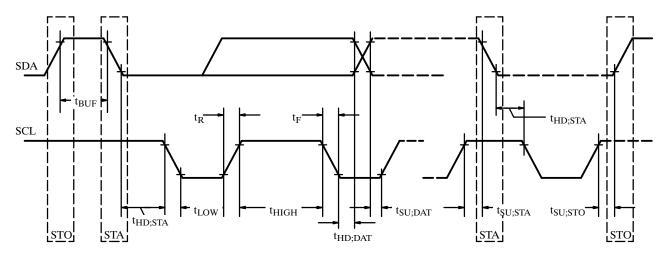

## Timing Specifications of the I<sup>2</sup>C Bus

I<sup>2</sup>C bus load conditions for timing specifications are as follows:

$4 \text{ k}\Omega$  pull-up resistors to +5 V; 200 pF capacitor to ground. All values are referred to  $V_{IH} = 3 \text{ V}$ ,  $V_{IL} = 1.5 \text{ V}$ .

| Parameter                   | Symbol              | Min  | Max | Unit |

|-----------------------------|---------------------|------|-----|------|

| SCL Clock Frequency         | $f_{scl}$           | _    | 100 | kHz  |

| Bus Free Before Start       | t <sub>BUF</sub>    | 4.7  | _   |      |

| Start Condition Set-up Time | t <sub>SU;STA</sub> | 4.7  | _   |      |

| Start Condition Hold Time   | t <sub>HD;STA</sub> | 4    | _   |      |

| SCL and SDA Low Period      | $t_{LOW}$           | 4.7  | _   |      |

| SCL and SDA High Period     | t <sub>HIGH</sub>   | 4    | _   | μs   |

| SCL and SDA Rise Time       | t <sub>r</sub>      | -    | 1.0 | ,    |

| SCL and SDA Fall Time       | $t_{\rm f}$         | -    | 0.3 |      |

| Data Set-Up Time<br>(WRITE) | t <sub>SU;DAT</sub> | 0.25 | _   |      |

| Data Hold Time (WRITE)      | t <sub>HD;DAT</sub> | 0*   | _   |      |

<sup>\*</sup> A transmitter must internally provide at lease a hold time to bridge the undefined region (max 300 ns) of the falling edge of the SCL.

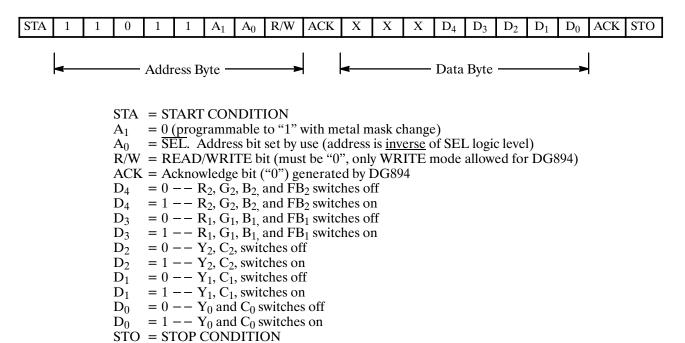

### I<sup>2</sup>C Bus Protocol

The DG894 is a slave receiver type of I<sup>2</sup>C interface and has four allocated addresses, two of which are user programmable through the SEL pin. Additional addresses may be obtained by a metal mask option for users requiring more than two DG894s on the same I<sup>2</sup>C bus. Contact Siliconix marketing for further information.

After the correct address has been sent, only one data byte is needed to define the switch configuration. Subsequent data put onto the bus will update the switches until a STOP condition (or another START condition) signals that the device is no longer being addressed. The switches will then remain in their last configuration as long as power is maintained to the chip.

#### **Power on Reset**

A power on reset function is provided on the DG894 to turn all switches off following power up if the  $I^2C$  mode is selected. In the CMOS control mode, the switches are selected according to the state of the control inputs.

DG894 Siliconix

# **Applications (Cont'd)**

Figure 10. I<sup>2</sup>C Bus Timing Diagram

## Minimum Bit Stream to Set Up DG894 Switches