# Freescale Semiconductor Product Brief

E600COREPB Rev. 0, 11/2004

# e600 Core Product Brief

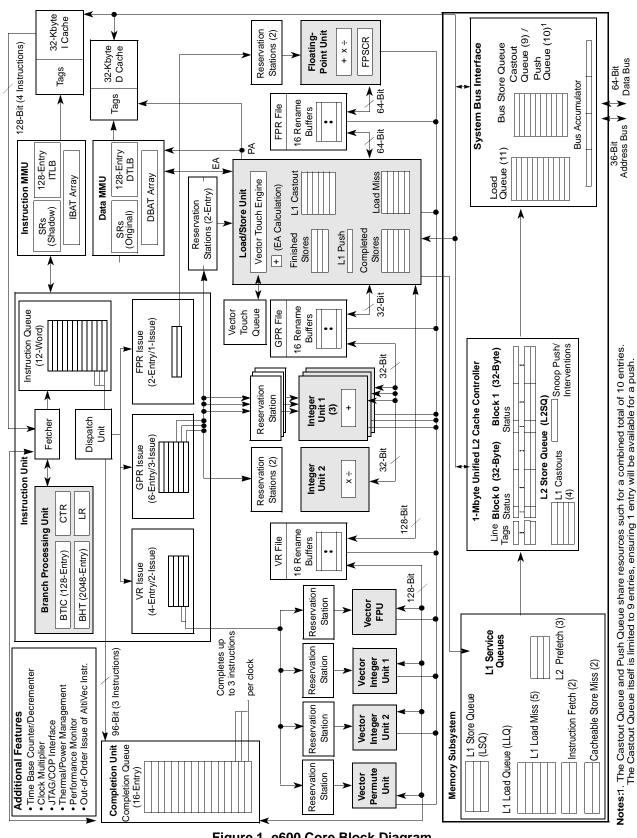

This product brief provides an overview of the e600 core features, including a block diagram showing the major functional components. The e600 is a PowerPC<sup>TM</sup> core.

This document also provides information about how the e600 implementation complies with the PowerPC and AltiVec<sup>TM</sup> architecture definitions.

## 1 e600 Core Overview

This section describes the features and general operation of the e600 core and provides a block diagram showing the major functional units. The e600 implements the PowerPC architecture and is a reduced instruction set computer (RISC) core. The e600 core consists of 32-Kbyte separate L1 instruction and data caches and a 1-Mbyte L2 cache. The core is a high-performance design supporting multiple execution units, including four independent units that execute AltiVec instructions.

The e600 core implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits. The core provides virtual memory support for up to 4 Petabytes (2<sup>52</sup>) of virtual memory and real memory support for up to 64 Gigabytes (2<sup>36</sup>) of physical memory.

The e600 core also implements the AltiVec instruction set architectural extension. The e600 core can dispatch and complete three instructions simultaneously. It incorporates the following execution units:

- 64-bit floating-point unit (FPU)

- Branch processing unit (BPU)

- Load/store unit (LSU)

#### e600 Core Overview

- Four integer units (IUs):

- Three shorter latency IUs (IU1a–IU1c)—execute all integer instructions except multiply, divide, and move to/from special-purpose register (SPR) instructions.

- Longer latency IU (IU2)—executes miscellaneous instructions including condition register (CR) logical operations, integer multiplication and division instructions, and move to/from SPR instructions.

- Four vector units that support AltiVec instructions:

- Vector permute unit (VPU)

- Vector integer unit 1 (VIU1)—performs shorter latency integer calculations

- Vector integer unit 2 (VIU2)—performs longer latency integer calculations

- Vector floating-point unit (VFPU)

The ability to execute several instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for e600-based systems. Most integer instructions (including VIU1 instructions) have a one-clock cycle execution latency.

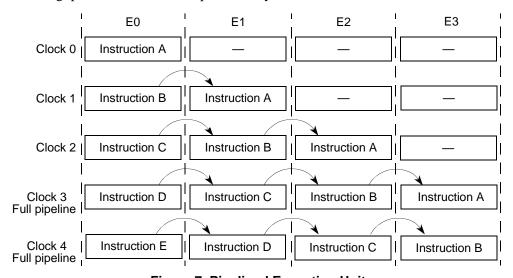

Several execution units feature multiple-stage pipelines; that is, the tasks they perform are broken into subtasks executed in successive stages. Typically, instructions follow one another through the stages, so a four-stage unit can work on four instructions when its pipeline is full. So, although an instruction may have to pass through several stages, the execution unit can achieve a throughput of one instruction per clock cycle.

AltiVec computational instructions are executed in four independent, pipelined AltiVec execution units. A maximum of two AltiVec instructions can be issued out-of-order to any combination of AltiVec execution units per clock cycle from the bottom two VIQ entries (VIQ1–VIQ0). This means an instruction in VIQ1 does not have to wait for an instruction in VIQ0 that is waiting for operand availability. Moreover, the VIU2, VFPU, and VPU are pipelined, so they can operate on multiple instructions. The VPU has a two-stage pipeline; the VIU2 and VFPU each have four-stage pipelines. As many as ten AltiVec instructions can be executing concurrently.

Note that for the e600 core, double- and single-precision versions of floating-point instructions have the same latency. For example, a floating-point multiply-add instruction takes 5 cycles to execute, regardless of whether it is single (**fmadds**) or double precision (**fmadd**).

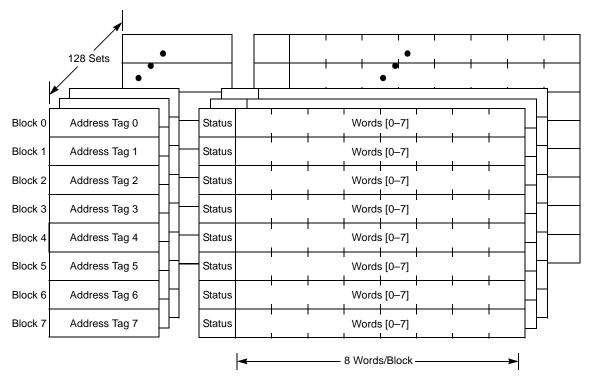

The e600 core has independent on-chip, 32-Kbyte, eight-way set-associative, physically addressed L1 (level one) caches for instructions and data, and independent instruction and data memory management units (MMUs). Each MMU has a 128-entry, two-way set-associative translation lookaside buffer (DTLB and ITLB) that saves recently used page address translations. Block address translation is implemented with the eight-entry instruction and data block address translation (IBAT and DBAT) arrays defined by the PowerPC architecture. During block translation, effective addresses are compared simultaneously with all BAT entries, as described in Chapter 5, "Memory Management," of the MPC7450 RISC Microprocessor Family User's Manual. For information about the L1 caches, see Chapter 3, "L1, L2, and L3 Cache Operation," of the MPC7450 RISC Microprocessor Family User's Manual.

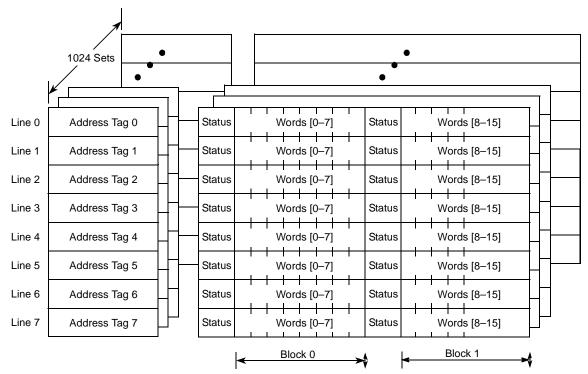

The L2 cache is implemented with an on-chip, 1-Mbyte, eight-way set-associative physically addressed memory available for storing data, instructions, or both. The L2 cache supports parity generation and checking for both tags and data. If ECC is disabled, it responds with an 11-cycle load latency for an L1 miss that hits in L2; if ECC is enabled, the L2 load access time is 12 cycles. The L2 cache is fully pipelined for two-cycle throughput. For information about the L2 cache implementation, see Chapter 3, "L1, L2, and L3 Cache Operation," of the MPC7450 RISC Microprocessor Family User's Manual.

The e600 core has three power-saving modes, nap, sleep, and deep sleep, which progressively reduce power dissipation. When functional units are idle, a dynamic power management mode causes those units to enter a low-power mode automatically without affecting operational performance, software execution, or external hardware. Section 2.9, "Power and Thermal Management," describes how power management can be used to reduce

3

power consumption when the processor, or portions of it, are idle. It also describes how the instruction cache throttling mechanism reduces the instruction dispatch rate. The information in these sections are described more fully in Chapter 10, "Power and Thermal Management," of the MPC7450 RISC Microprocessor Family User's Manual.

The performance monitor facility provides the ability to monitor and count predefined events such as processor clocks, misses in the instruction cache, data cache, or L2 cache, types of instructions dispatched, mispredicted branches, and other occurrences. The count of such events (which may be an approximation) can be used to trigger the performance monitor exception. Section 2.10, "Performance Monitor," describes the operation of the performance monitor diagnostic tool. This functionality is fully described in Chapter 11, "Performance Monitor," of the MPC7450 RISC Microprocessor Family User's Manual

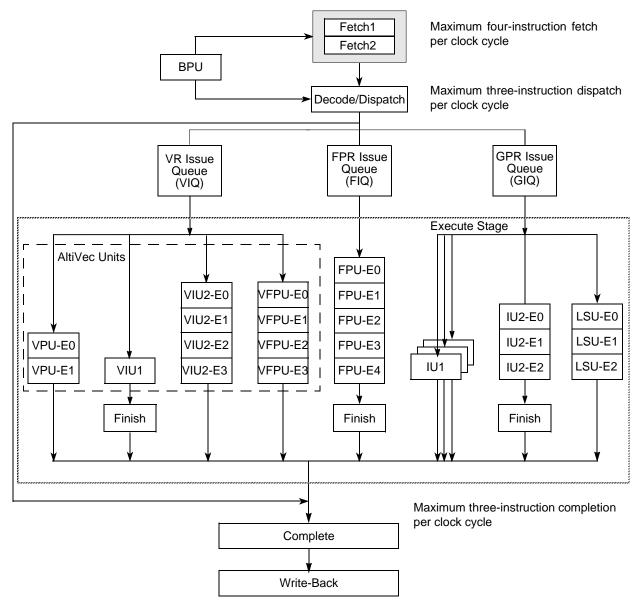

Figure 1 shows the parallel organization of the execution units (shaded in the diagram). Note that this is a conceptual model showing basic features, rather than an attempt at showing how features are implemented physically.

### e600 Core Overview

Figure 1. e600 Core Block Diagram

e600 Core Product Brief, Rev. 0

This section describes the features of the e600 core. The interrelationships of these features are shown in Figure 1.

#### 2.1 Features on the e600 Core

Major features of the e600 core are as follows:

- High-performance e600 core

- As many as 4 instructions can be fetched from the instruction cache at a time.

- As many as 3 instructions can be dispatched to the issue queues at a time.

- As many as 12 instructions can be in the instruction queue (IQ).

- As many as 16 instructions can be at some stage of execution simultaneously.

- Single-cycle execution for most instructions

- One-instruction throughput per clock cycle for most instructions

- Seven-stage pipeline control

- Eleven independent execution units and three register files

- Branch processing unit (BPU) features static and dynamic branch prediction

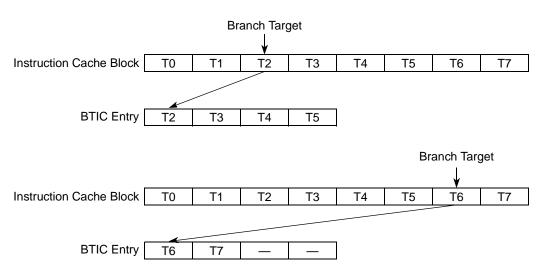

- 128-entry (32-set, four-way set-associative) branch target instruction cache (BTIC), a cache of branch instructions that have been encountered in branch/loop code sequences. If a target instruction is in the BTIC, it is fetched into the instruction queue a cycle sooner than it can be made available from the instruction cache. Typically, a fetch that hits the BTIC provides the first 4 instructions in the target stream.

- 2048-entry branch history table (BHT) with 2 bits per entry for four levels of prediction—not-taken, strongly not-taken, taken, strongly taken

- Up to three outstanding speculative branches

- Branch instructions that do not update the count register (CTR) or link register (LR) are often removed from the instruction stream.

- Eight-entry link register stack to predict the target address of Branch Conditional to Link Register (bclr) instructions

- Four integer units (IUs) that share 32 GPRs for integer operands

- Three identical IUs (IU1a, IU1b, and IU1) can execute all integer instructions except multiply, divide, and move to/from special-purpose register instructions.

- IU2 executes miscellaneous instructions including the CR logical operations, integer multiplication and division instructions, and move to/from special-purpose register instructions.

- 64-bit floating-point unit (FPU)

- Five-stage FPU

- Fully IEEE 754-1985 compliant FPU for both single- and double-precision operations

- Supports non-IEEE mode for time-critical operations

- Hardware support for denormalized numbers

- Thirty-two 64-bit FPRs for single- or double-precision operands

e600 Core Product Brief, Rev. 0 Freescale Semiconductor 5

- Four vector units and 32-entry vector register file (VRs)

- Vector permute unit (VPU)

- Vector integer unit 1 (VIU1) handles short-latency AltiVec integer instructions, such as vector add instructions (for example, vaddsbs, vaddshs, and vaddsws)

- Vector integer unit 2 (VIU2) handles longer-latency AltiVec integer instructions, such as vector multiply add instructions (for example, vmhaddshs, vmhraddshs, and vmladduhm).

- Vector floating-point unit (VFPU)

- Three-stage load/store unit (LSU)

- Supports integer, floating-point and vector instruction load/store traffic

- Four-entry vector touch queue (VTQ) supports all four architected AltiVec data stream operations

- Three-cycle GPR and AltiVec load latency (byte, half word, word, vector) with single-cycle throughput

- Four-cycle FPR load latency (single, double) with single-cycle throughput

- No additional delay for misaligned access within double-word boundary

- Dedicated adder calculates effective addresses (EAs)

- Supports store gathering

- Performs alignment, normalization, and precision conversion for floating-point data

- Executes cache control and TLB instructions

- Performs alignment, zero padding, and sign extension for integer data

- Supports hits under misses (multiple outstanding misses)

- Supports both big- and little-endian modes, including misaligned little-endian accesses

- Three issue queues, FIQ (floating point issue queue), VIQ (vector issue queue), and GIQ (general purpose issue queue), can accept as many as one, two, and three instructions, respectively, in a cycle. Instruction dispatch requires the following:

- Instructions can be dispatched only from the three lowest IQ entries—IQ0, IQ1, and IQ2.

- A maximum of three instructions can be dispatched to the issue queues per clock cycle.

- Space must be available in the completion queue (CQ) for an instruction to dispatch (this includes instructions that are assigned a space in the CQ but not in an issue queue).

- Rename buffers

- 16 GPR (general purpose register) rename buffers

- 16 FPR (floating point register) rename buffers

- 16 VR (vector register) rename buffers

- Dispatch unit—The decode/dispatch stage fully decodes each instruction.

- Completion unit

- The completion unit retires an instruction from the 16-entry CQ when all instructions ahead of it have been completed, the instruction has finished execution, and no exceptions are pending.

- Guarantees sequential programming model (precise exception model)

- Monitors all dispatched instructions and retires them in order

- Tracks unresolved branches and flushes instructions after a mispredicted branch

- Retires as many as three instructions per clock cycle

- L1 cache has the following characteristics:

- Two separate 32-Kbyte instruction and data caches (Harvard architecture)

- Instruction and data caches are eight-way set-associative

- Instruction and data caches have 32-byte cache blocks. A cache block is the block of memory that a

coherency state describes—it corresponds to a cache line for the L1 data cache.

- Cache directories are physically addressed. The physical (real) address tag is stored in the cache directory.

- The caches implement a pseudo least-recently-used (PLRU) replacement algorithm within each way.

- Cache write-back or write-through operation is programmable on a per-page or per-block basis.

- Instruction cache can provide four instructions per clock cycle; data cache can provide four words per clock cycle

- Two-cycle latency and single-cycle throughput for instruction or data cache accesses

- Caches can be disabled in software

- Caches can be locked in software

- Supports a four-state modified/exclusive/shared/invalid (MESI) coherency protocol

- A single coherency status bit for each instruction cache block allows encoding for the following two possible states:

```

Invalid (INV)

```

Valid (VAL)

- Two status bits (MESI[0-1]) for each data cache block allow encoding for coherency, as follows:

00 = invalid(I)

01 = shared(S)

10 = exclusive (E)

11 = modified (M)

- Separate copy of data cache tags for efficient snooping

- Both L1 caches support parity generation and checking (enabled through bits in the ICTRL register) as follows:

- Instruction cache—one parity bit per instruction

- Data cache—one parity bit per byte of data

- No snooping of instruction cache except for **icbi** instruction

- Caches implement a pseudo least-recently-used (PLRU) replacement algorithm within each way

- Data cache supports AltiVec LRU and transient instructions

- Critical double- and/or quad-word forwarding is performed as needed. Critical quad-word forwarding is used for AltiVec loads and instruction fetches. Other accesses use critical double-word forwarding.

- On-chip level 2 (L2) cache has the following features:

- Integrated 1-Mbyte, eight-way set-associative unified instruction and data cache

- Fully pipelined to provide 32 bytes every other clock cycle to the L1 caches

- Total latency of 11 processor cycles for L1 data cache miss that hits in the L2 with ECC disabled, 12 cycles when ECC is enabled

- Uses one of two random replacement algorithms (selectable through L2CR)

- Cache write-back or write-through operation programmable on a per-page or per-block basis

e600 Core Product Brief, Rev. 0

- Organized as 32 bytes/block and 2 blocks (sectors)/line (a cache block is the block of memory that a coherency state describes).

- Supports error correction and detection using a SECDED (single-error correction, double-error detection) protocol. Every 64 bits of data comes with 8 bits of error detection/correction, which can be programmed as ECC across the 64 bits of data, byte parity, or no error detection/correction.

- Supports parity generation and checking for both tags and data (enabled through L2CR). Tag parity is enabled separately in the L2ERRDIS register, and data parity can be enabled through L2CR only when ECC is disabled.

- Error injection modes provided for testing

- Separate memory management units (MMUs) for instructions and data

- 52-bit virtual address; 32- or 36-bit physical address

- Address translation for 4-Kbyte pages, variable-sized blocks, and 256-Mbyte segments

- Memory programmable as write-back/write-through, caching-inhibited/caching-allowed, and memory coherency enforced/memory coherency not enforced on a page or block basis

- Separate IBATs and DBATs (eight each) also defined as SPRs

- Separate instruction and data translation lookaside buffers (TLBs)

- Both TLBs are 128-entry, two-way set-associative, and use LRU replacement algorithm

- TLBs are hardware or software reloadable (that is, on a TLB miss a page table search is performed in hardware or by system software).

#### Efficient data flow

- Although the VR/LSU interface is 128 bits, the L1/L2 bus interface allows up to 256 bits.

- The L1 data cache is fully pipelined to provide 128 bits/cycle to or from the VRs.

- L2 cache is fully pipelined to provide 32 bytes every other processor clock cycle to the L1 cache

- As many as eight outstanding, out-of-order cache misses are allowed between the L1 data cache and L2 bus.

- As many as 16 out-of-order transactions can be present on the MPX bus.

- Store merging for multiple store misses to the same line. Only coherency action taken (address-only) for store misses merged to all 32 bytes of a cache block (no data tenure needed)

- Support for a second cacheable store miss

- Three-entry finished store queue and five-entry completed store queue between the LSU and the L1 data cache

- Separate additional queues for efficient buffering of outbound data (such as castouts and write-through stores) from the L1 data cache and L2 cache

- Multiprocessing support features include the following:

- Hardware-enforced, MESI cache coherency protocols for data cache

- Load/store with reservation instruction pair for atomic memory references, semaphores, and other multiprocessor operations

- Power and thermal management

- The following three power-saving modes are available to the system:

- Nap—Instruction fetching is halted. Only those clocks for the time base, decrementer, and JTAG logic remain running. The part goes into the doze state to snoop memory operations on the bus and then back to nap using a QREQ/QACK processor-system handshake protocol.

e600 Core Product Brief, Rev. 0

- Sleep—Power consumption is further reduced by disabling bus snooping, leaving only the PLL in a locked and running state. All internal functional units are disabled.

- Deep sleep—When the part is in deep sleep state, the system can disable the PLL. The system can

then disable the SYSCLK source for greater system power savings. Power-on reset procedures for

restarting and relocking the PLL must be followed upon exiting the deep sleep state.

- DFS (dynamic frequency switching) capability conserves power by lowering processor operating frequency. Divide-by-two and divide-by-four modes (DFS2 and DFS4) provided.

- Instruction cache throttling provides control of instruction fetching to limit device temperature.

- Performance monitor helps to debug system designs and improve software efficiency

- In-system testability and debugging features through JTAG boundary-scan capability

- Reliability and serviceability

- Parity checking on system bus

- Parity checking on L1 and L2 cache arrays

### 2.2 Instruction Flow

As shown in Figure 1, the e600 core instruction unit provides centralized control of instruction flow to the execution units. The instruction unit contains a sequential fetcher, 12-entry instruction queue (IQ), dispatch unit, and branch processing unit (BPU). It determines the address of the next instruction to be fetched based on information from the sequential fetcher and from the BPU.

See Chapter 6, "Instruction Timing," of the MPC7450 RISC Microprocessor Family User's Manual for a detailed discussion of instruction timing.

The sequential fetcher loads instructions from the instruction cache into the instruction queue. The BPU extracts branch instructions from the sequential fetcher. Branch instructions that cannot be resolved immediately are predicted using either e600-specific dynamic branch prediction or architecture-defined static branch prediction.

Branch instructions that do not affect the LR or CTR are often removed from the instruction stream. Chapter 6, "Instruction Timing," of the MPC7450 RISC Microprocessor Family User's Manual describes when a branch can be removed from the instruction stream.

Instructions dispatched beyond a predicted branch do not complete execution until the branch is resolved, preserving the programming model of sequential execution. If branch prediction is incorrect, the instruction unit flushes all predicted path instructions, and instructions are fetched from the correct path.

# 2.2.1 Instruction Queue and Dispatch Unit

The instruction queue (IQ), shown in Figure 1 holds as many as 12 instructions and loads as many as 4 instructions from the instruction cache during a single processor clock cycle.

The fetcher attempts to initiate a new fetch every cycle. The two fetch stages are pipelined, so as many as four instructions can arrive to the IQ every cycle. All instructions except branch (**b**x), Return from Exception (**rfi**), System Call (**sc**), Instruction Synchronize (**isync**), and no-op instructions are dispatched to their respective issue queues from the bottom three positions in the instruction queue (IQ0–IQ2) at a maximum rate of three instructions per clock cycle. Reservation stations are provided for the three IU1s, IU2, FPU, LSU, VPU, VIU2, VIU1, and VFPU. The dispatch unit checks for source and destination register dependencies, determines whether a position is available in the CQ, and inhibits subsequent instruction dispatching as required.

Branch instruction can be detected, decoded, and predicted from entries IQ0-IQ7.

e600 Core Product Brief, Rev. 0

## 2.2.2 Branch Processing Unit (BPU)

The BPU receives branch instructions from the IQ and executes them early in the pipeline, achieving the effect of a zero-cycle branch in some cases.

Branches with no outstanding dependencies (CR, LR, or CTR unresolved) can be processed and resolved immediately. For branches in which only the direction is unresolved due to a CR or CTR dependency, the branch path is predicted using either architecture-defined static branch prediction or e600-specific dynamic branch prediction. Dynamic branch prediction is enabled if HID0[BHT] is set. For **bclr** branches where the target address is unresolved due to a LR dependency, the branch target can be predicted using the hardware link stack. Link stack prediction is enabled if HID0[LRSTK] is set.

When a prediction is made, instruction fetching, dispatching, and execution continue from the predicted path, but instructions cannot complete and write back results to architected registers until the prediction is determined to be correct (resolved). When a prediction is incorrect, the instructions from the incorrect path are flushed from the processor and processing begins from the correct path.

Dynamic prediction is implemented using a 2048-entry branch history table (BHT), a cache that provides two bits per entry that together indicate four levels of prediction for a branch instruction—not-taken, strongly not-taken, taken, strongly taken. When dynamic branch prediction is disabled, the BPU uses a bit in the instruction encoding to predict the direction of the conditional branch. Therefore, when an unresolved conditional branch instruction is encountered, the e600 core executes instructions from the predicted target stream although the results are not committed to architected registers until the conditional branch is resolved. Unresolved branches are held in a three-entry branch queue. When the branch queue is full, no further conditional branches can be processed until one of the conditions in the branch queue is resolved.

When a branch is taken or predicted as taken, instructions from the untaken path must be flushed and the target instruction stream must be fetched into the IQ. The BTIC is a 128-entry, four-way set associative cache that contains the most recently used branch target instructions (up to four instructions per entry) for **b** and **bc** branches. When a taken branch instruction of this type hits in the BTIC, the instructions arrive in the IQ two clock cycles later, a clock cycle sooner than they would arrive from the instruction cache. Additional instructions arrive from the instruction cache in the next clock cycle. The BTIC reduces the number of missed opportunities to dispatch instructions and gives the processor a 1-cycle head start on processing the target stream.

The BPU contains an adder to compute branch target addresses and three user-accessible registers—the link register (LR), the count register (CTR), and the condition register (CR). The BPU calculates the return pointer for subroutine calls and saves it in the LR for certain types of branch instructions. The LR also contains the branch target address for Branch Conditional to Link Register (**bclr***x*) instructions. The CTR contains the branch target address for Branch Conditional to Count Register (**bcctr***x*) instructions. Because the LR and CTR are SPRs, their contents can be copied to or from any GPR. Also, because the BPU uses dedicated registers rather than GPRs or FPRs, execution of branch instructions is largely independent from execution of integer and floating-point instructions.

# 2.2.3 Completion Unit

The completion unit operates closely with the instruction unit. Instructions are fetched and dispatched in program order. At the point of dispatch, the program order is maintained by assigning each dispatched instruction a successive entry in the 16-entry CQ. The completion unit tracks instructions from dispatch through execution and retires them in program order from the three bottom CQ entries (CQ0–CQ2).

Instructions cannot be dispatched to an execution unit unless there is a CQ vacancy.

11

Branch instructions that do not update the CTR or LR are often removed from the instruction stream. Those that are removed do not take a CQ entry. Branches that are not removed from the instruction stream follow the same dispatch and completion procedures as non-branch instructions but are not dispatched to an issue queue.

Completing an instruction commits execution results to architected registers (GPRs, FPRs, VRs, LR, and CTR). In-order completion ensures the correct architectural state when the e600 core must recover from a mispredicted branch or any exception. An instruction is retired as it is removed from the CQ.

For a more detailed discussion of instruction completion, see Chapter 6, "Instruction Timing," of the MPC7450 RISC Microprocessor Family User's Manual.

### 2.2.4 Independent Execution Units

In addition to the BPU, the e600 core provides the ten execution units described in the following sections.

### 2.2.4.1 AltiVec Vector Permute Unit (VPU)

The VPU executes permutation instructions such as pack, unpack, merge, splat, and permute on vector operands.

### 2.2.4.2 AltiVec Vector Integer Unit 1 (VIU1)

The VIU1 executes simple vector integer computational instructions, such as addition, subtraction, maximum and minimum comparisons, averaging, rotation, shifting, comparisons, and Boolean operations.

### 2.2.4.3 AltiVec Vector Integer Unit 2 (VIU2)

The VIU2 executes longer-latency vector integer instructions, such as multiplication, multiplication/addition, and sum-across with saturation.

## 2.2.4.4 AltiVec Vector Floating-Point Unit (VFPU)

The VFPU executes all vector floating-point instructions.

A maximum of two AltiVec instructions can be issued out-of-order to any combination of AltiVec execution units per clock cycle from the bottom two VIQ entries (VIQ1-VIQ0). An instruction in VIQ1 does not have to wait for an instruction in VIQ0 that is waiting for operand availability. Moreover, the VIU2, VFPU, and VPU are pipelined, so they can operate on multiple instructions.

# 2.2.4.5 Integer Units (IUs)

The integer units (three IU1s and IU2) are shown in Figure 1. The IU1s execute shorter latency integer instructions, that is, all integer instructions except multiply, divide, and move to/from special-purpose register instructions. IU2 executes integer instructions with latencies of three cycles or more.

IU2 has a 32-bit integer multiplier/divider and a unit for executing CR logical operations and move to/from SPR instructions. The multiplier supports early exit for operations that do not require full  $32 \times 32$ -bit multiplication.

# 2.2.4.6 Floating-Point Unit (FPU)

The FPU, shown in Figure 1, is designed such that double-precision operations require only a single pass, with a latency of 5 cycles. As instructions are dispatched to the FPUs reservation station, source operand data can be

accessed from the FPRs or from the FPR rename buffers. Results in turn are written to the rename buffers and made available to subsequent instructions. Instructions start execution from the bottom reservation station only and execute in program order.

The FPU contains a single-precision multiply-add array and the floating-point status and control register (FPSCR). The multiply-add array allows the e600 core to implement multiply and multiply-add operations efficiently. The FPU is pipelined so that one single- or double-precision instruction can be issued per clock cycle.

Note that an execution bubble occurs after four consecutive, independent floating-point arithmetic instructions execute to allow for a normalization special case. Thirty-two 64-bit floating-point registers are provided to support floating-point operations. Stalls due to contention for FPRs are minimized by automatic allocation of the 16 floating-point rename registers. The e600 core writes the contents of the rename registers to the appropriate FPR when floating-point instructions are retired by the completion unit.

The e600 core supports all IEEE 754 floating-point data types (normalized, denormalized, NaN, zero, and infinity) in hardware, eliminating the latency incurred by software exception routines.

### 2.2.4.7 Load/Store Unit (LSU)

The LSU executes all load and store instructions as well as the AltiVec LRU and transient instructions and provides the data transfer interface between the GPRs, FPRs, VRs, and the cache/memory subsystem. The LSU also calculates effective addresses and aligns data.

Load and store instructions are issued and translated in program order; however, some memory accesses can occur out of order. Synchronizing instructions can be used to enforce strict ordering. When there are no data dependencies and the guarded bit for the page or block is cleared, a maximum of one out-of-order cacheable load operation can execute per clock cycle from the perspective of the LSU. Loads to FPRs require a 4-cycle total latency. Data returned from the cache is held in a rename register until the completion logic commits the value to a GPR, FPR, or VR. Stores cannot be executed out of order and are held in the store queue until the completion logic signals that the store operation is to be completed to memory. The e600 core executes store instructions with a maximum throughput of one per clock cycle and a 3-cycle total latency to the data cache. The time required to perform the load or store operation depends on the processor: bus clock ratio and whether the operation involves the on-chip caches, system memory, or an I/O device.

# 2.3 Memory Management Units (MMUs)

The e600 core MMUs support up to 4 Petabytes (2<sup>52</sup>) of virtual memory and 64 Gigabytes (2<sup>36</sup>) of physical memory for instructions and data. The MMUs control access privileges for these spaces on block and page granularities. Referenced and changed status is maintained by the processor for each page to support demand-paged virtual memory systems. The memory management units are contained within the load/store unit.

The LSU calculates effective addresses for data loads and stores; the instruction unit calculates effective addresses for instruction fetching. The MMU translates the effective address to determine the correct physical address for the memory access.

The e600 core supports the following types of memory translation:

• Real addressing mode—In this mode, translation is disabled by clearing bits in the machine state register (MSR): MSR[IR] for instruction fetching or MSR[DR] for data accesses. When address translation is disabled, the physical address is identical to the effective address. When extended addressing is disabled (HID0[XAEN] = 0) a 32-bit physical address is used, PA[4–35]. For more details see Chapter 5, "Memory Management Unit," of the MPC7450 RISC Microprocessor Family User's Manual.

e600 Core Product Brief, Rev. 0

- Page address translation—translates the page frame address for a 4-Kbyte page size

- Block address translation—translates the base address for blocks (4 Gbytes)

If translation is enabled, the appropriate MMU translates the higher-order bits of the effective address into physical address bits. Lower-order address bits are untranslated and are the same for both logical and physical addresses. These bits are directed to the on-chip caches where they form the index into the eight-way set-associative tag array. After translating the address, the MMU passes the higher-order physical address bits to the cache and the cache lookup completes. For caching-inhibited accesses or accesses that miss in the cache, the untranslated lower-order address bits are concatenated with the translated higher-order address bits; the resulting 32- or 36-bit physical address is used by the memory subsystem and the bus interface unit, which accesses external memory.

The TLBs store page address translations for recent memory accesses. For each access, an effective address is presented for page and block translation simultaneously. If a translation is found in both the TLB and the BAT array, the block address translation in the BAT array is used. Usually the translation is in a TLB and the physical address is readily available to the on-chip cache. When a page address translation is not in a TLB, hardware or system software searches for one in the page table following the model defined by the PowerPC architecture.

Instruction and data TLBs provide address translation in parallel with the on-chip cache access, incurring no additional time penalty in the event of a TLB hit. The e600 core instruction and data TLBs are 128-entry, two-way set-associative caches that contain address translations. The core can initiate a hardware or system software search of the page tables in memory on a TLB miss.

# 2.4 On-Chip L1 Instruction and Data Caches

The e600 core implements separate L1 instruction and data caches. Each cache is 32-Kbyte eight-way set-associative. As defined by the PowerPC architecture, they are physically indexed. Each cache block contains eight contiguous words from memory that are loaded from an eight-word boundary (that is, bits EA[27–31] are zeros); thus, a cache block never crosses a page boundary. An entire cache block can be updated by a four-beat burst load across a 64-bit system bus. Misaligned accesses across a page boundary can incur a performance penalty. The data cache is a non-blocking, write-back cache with hardware support for reloading on cache misses. The critical double word is transferred on the first beat and is forwarded to the requesting unit, minimizing stalls due to load delays. For vector loads, the critical quad word is handled similarly but is transferred on the second beat. The cache being loaded is not blocked to internal accesses while the load completes.

The e600 core L1 cache organization is shown in Figure 2.

Figure 2. L1 Cache Organization

The instruction cache provides up to four instructions per clock cycle to the instruction queue. The instruction cache can be invalidated entirely or on a cache-block basis. It is invalidated and disabled by setting HID0[ICFI] and then clearing HID0[ICE]. The instruction cache can be locked by setting HID0[ILOCK]. The instruction cache supports only the valid/invalid states.

The data cache provides four words per clock cycle to the LSU. Like the instruction cache, the data cache can be invalidated all at once or on a per-cache-block basis. The data cache can be invalidated and disabled by setting HID0[DCFI] and then clearing HID0[DCE]. The data cache can be locked by setting HID0[DLOCK]. The data cache tags are dual-ported, so a load or store can occur simultaneously with a snoop.

The e600 core also implements a 128-entry (32-set, four-way set-associative) branch target instruction cache (BTIC). The BTIC is a cache of branch instructions that have been encountered in branch/loop code sequences. If the target instruction is in the BTIC, it is fetched into the instruction queue a cycle sooner than it can be made available from the instruction cache. Typically, the BTIC contains the first four instructions in the target stream.

The BTIC can be disabled and invalidated through software. As with other aspects of e600 core instruction timing, BTIC operation is optimized for cache-line alignment. If the first target instruction is one of the first five instructions in the cache block, the BTIC entry holds four instructions. If the first target instruction is the last instruction before the cache block boundary, it is the only instruction in the corresponding BTIC entry. If the next-to-last instruction in a cache block is the target, the BTIC entry holds two valid target instructions, as shown in Figure 3.

Figure 3. Alignment of Target Instructions in the BTIC

BTIC ways are updated using a FIFO algorithm.

For more information and timing examples showing cache hit and cache miss latencies, see Chapter 6, "Instruction Timing," of the MPC7450 RISC Microprocessor Family User's Manual.

# 2.5 L2 Cache Implementation

The L2 cache is a unified cache that receives memory requests from both the L1 instruction and data caches independently. The integrated L2 cache on the e600 core is a unified (containing both instructions and data) 1-Mbyte on-chip cache. It is eight-way set-associative and organized with 32-byte blocks and two blocks/line.

Each line consists of 64 bytes of data organized as two blocks (also called sectors). Although all 16 words in a cache line share the same address tag, each block maintains the three separate status bits for the 8 words of the cache block, the unit of memory at which coherency is maintained. Thus, each cache line can contain 16 contiguous words from memory that are read or written as 8-word operations.

The integrated L2 cache organization of the e600 core is shown in Figure 4.

Figure 4. L2 Cache Organization

The L2 cache controller contains the L2 cache control register (L2CR), which does the following:

- Includes bits for enabling parity checking on the L2

- Provides for instruction-only and data-only modes

- Provides hardware flushing for the L2

- Selects between two available replacement algorithms for the L2 cache

The L2 implements the MESI cache coherency protocol using three status bits per sector.

Requests from the L1 cache generally result from instruction misses, data load or store misses, write-through operations, or cache management instructions. Requests from the L1 cache are compared against the L2 tags and serviced by the L2 cache if they hit; if they miss in the L2 cache, they go to main memory.

The L2 cache tags are fully pipelined and non-blocking for efficient operation. Thus the L2 cache can be accessed internally while a load for a miss is pending (allowing hits under misses). A reload for a cache miss is treated as a normal access and blocks other accesses for only 1 cycle.

For more information, see Chapter 3, "L1, L2, and L3 Cache Operation," of the MPC7450 RISC Microprocessor Family User's Manual.

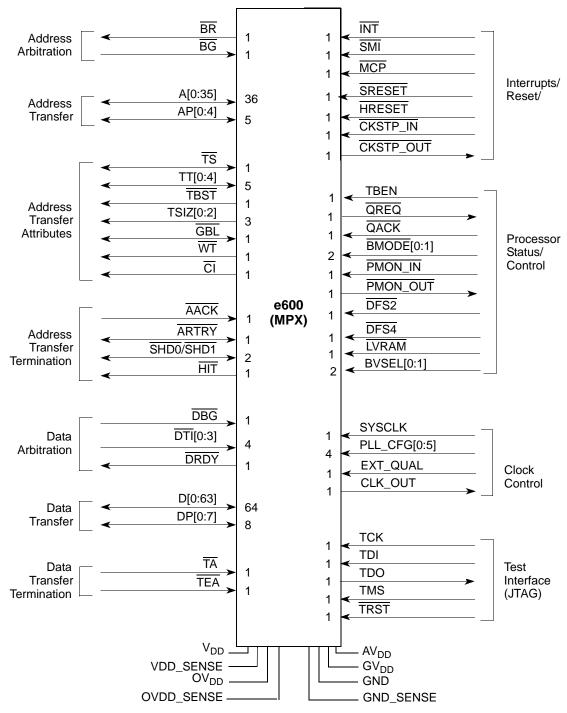

# 2.6 System Interface

The e600 core supports two interface protocols—the MPX bus protocol and a subset of the 60x bus protocol. Note that although this protocol is implemented by the MPC603e, MPC604e, MPC740, and MPC750 processors, it is referred to as the 60x bus interface. The MPX bus protocol is derived from the 60x bus protocol. The MPX bus interface includes several additional features that provide higher memory bandwidth than the 60x bus and more

efficient use of the system bus in a multiprocessing environment. Because the performance of the e600 core is optimized for the MPX bus, use of the MPX is recommended over use of the the 60x bus.

The e600 bus interface includes a 64-bit data bus with 8 bits of data parity, a 36-bit address bus with 5 bits of address parity, and additional control signals to allow for unique system level optimizations.

The bus interface protocol is configured using the  $\overline{BMODE0}$  configuration signal at reset. If  $\overline{BMODE0}$  is asserted at the negation of  $\overline{HRESET}$ , the e600 core uses the MPX bus protocol; if  $\overline{BMODE0}$  is negated during the negation of  $\overline{HRESET}$ , the e600 core uses a limited subset of the 60x bus protocol. Note that the inverse state of  $\overline{BMODE}[0:1]$  at the negation of  $\overline{HRESET}$  is saved in  $\overline{MSSCR0}[BMODE]$ .

# 2.7 e600 Core Bus Operation Features

The e600 core has a separate address and data bus, each with its own set of arbitration and control signals. This allows for decoupling the data tenure from the address tenure of a transaction and provides for a wide range of system-bus implementations including:

- Non-pipelined bus operation

- Pipelined bus operation

- Split transaction operation

The e600 core supports only the normal memory-mapped address segments defined in the PowerPC architecture. Access to direct store segments results in a DSI exception.

### 2.7.1 MPX Bus Features

The MPX bus has the following features:

- Extended 36-bit address bus plus 5 bits of odd parity (41 bits total)

- 64-bit data bus plus 8 bits of odd parity (72 bits total); a 32-bit data bus mode is not supported

- Support for a four-state (MESI) cache coherence protocol

- On-chip snooping to maintain L1 data cache and L2 cache coherency for multiprocessing applications and DMA environments

- Support for address-only transfers (useful for a variety of broadcast operations in multiprocessor applications)

- Address pipelining

- Support for up to 16 out-of-order transactions using 4 data transaction index (DTI[0:3]) signals

- Full data streaming

- Support for data intervention in multiprocessor systems

### 2.7.2 60x Bus Features

The following list summarizes the 60x bus interface features:

- Extended 36-bit address bus plus 5 bits of odd parity (41 bits total)

- 64-bit data bus plus 8 bits of odd parity (72 bits total); a 32-bit data bus mode is not supported

- Support for a four-state (MESI) cache coherence protocol

- On-chip snooping to maintain L1 data cache and L2 cache coherency for multiprocessing applications and DMA environments

e600 Core Product Brief, Rev. 0

- Support for address-only transfers (useful for a variety of broadcast operations in multiprocessor applications)

- · Address pipelining

- Support for up to 16 outstanding transactions. No reordering is supported.

# 2.8 Overview of System Interface Accesses

The system interface includes address register queues, prioritization logic, and a bus control unit. The system interface latches snoop addresses for snooping in the L1 data cache and the L2 cache, the memory hierarchy address register queues, and the reservation controlled by the Load Word and Reserve Indexed (**lwarx**) and Store Word Conditional Indexed (**stwcx**.) instructions. Accesses are prioritized with load operations preceding store operations.

Instructions are automatically fetched from the memory system into the instruction unit where they are issued to the execution units at a peak rate of three instructions per clock cycle. Conversely, load and store instructions explicitly specify the movement of operands to and from the integer, floating-point, and AltiVec register files and the memory system.

When the e600 core encounters an instruction or data access, it calculates the effective address and uses the lower-order address bits to check for a hit in the on-chip, 32-Kbyte L1 instruction and data caches. During L1 cache lookup, the instruction and data memory management units (MMUs) use the higher-order address bits to calculate the virtual address, from which they calculate the physical (real) address. The physical address bits are then compared with the corresponding cache tag bits to determine if a cache hit occurred in the L1 instruction or data cache. If the access misses in the corresponding cache, the transaction is sent to L1 load miss queue or the L1 store miss queue. L1 load miss queue transactions are sent to the internal 1-Mbyte L2 cache. Store miss queue transactions are queued up in the L2 cache controller. If no match is found in the L2 tags, the physical address is used to access system memory.

In addition to loads, stores, and instruction fetches, the e600 core performs hardware table search operations following TLB misses; L1 and L2 cache castout operations; and cache-line snoop push operations when a modified cache line detects a snoop hit from another bus master.

# 2.8.1 System Interface Operation

The primary activity of the e600 core system interface is transferring data and instructions between the processor and system memory. There are three types of transfer accesses:

- Single-beat transfers—These memory accesses allow transfer sizes of 1, 2, 3, 4, or 8 bytes in one bus clock cycle. Single-beat transactions are caused by uncacheable read and write operations that access memory directly (that is, when caching is disabled), cache-inhibited accesses, and stores in write-through mode.

- Two-beat burst (16-byte) data transfers—Generated to support caching-inhibited or write-through AltiVec loads and stores (only generated in MPX bus mode) and for caching-inhibited instruction fetches in MPX mode.

- Four-beat burst (32-byte) data transfers—Initiated when an entire cache block is transferred into or out of the internal caches. Because the first-level caches on the e600 core are write-back caches, burst-read memory operations are the most common memory accesses, followed by burst-write memory operations, and single-beat (caching-inhibited or write-through) memory read and write operations.

Memory accesses can occur in single-beat (1, 2, 3, 4, and 8 bytes), double-beat (16 bytes), and four-beat (32 bytes) burst data transfers. For memory accesses, the address and data buses are independent to support pipelining and split transactions. The bus interface can pipeline as many as 16 transactions and, in MPX bus mode, supports full

e600 Core Product Brief, Rev. 0

out-of-order split-bus transactions. The e600 core bursts out of reset in MPX bus mode, fetching eight instructions on the MPX bus at a time.

Access to the system interface is granted through an external arbitration mechanism that allows devices to compete for bus mastership. This arbitration mechanism is flexible, allowing the e600 core to be integrated into systems that implement various fairness and bus-parking procedures to avoid arbitration overhead.

Typically, memory accesses are weakly ordered to maximize the efficiency of the bus without sacrificing coherency of the data. The e600 core allows load operations to bypass store operations (except when a dependency exists). Because the processor can dynamically optimize run-time ordering of load/store traffic, overall performance is improved.

Note that the synchronize (**sync**) and enforce in-order execution of I/O (**eieio**) instructions can be used to enforce strong ordering.

The system interface is synchronous. All e600 core inputs are sampled and all outputs are driven on the rising edge of the bus clock cycle. The hardware specifications gives timing information. The system interface is specific for each microprocessor that implements the PowerPC architecture.

### 2.8.2 Signal Groupings

Signals are provided for implementing the bus protocol and clocking. Test and control signals provide diagnostics for selected internal circuits.

The e600 core MPX and 60x bus interface protocol signals are grouped as follows:

- Address arbitration—The e600 core uses these signals to arbitrate for address bus mastership.

- Address transfer start—These signals indicate that a bus master has begun a transaction on the address bus.

- Address transfer—These signals include the address bus and address parity signals. They are used to transfer the address and to ensure the integrity of the transfer.

- Transfer attribute—These signals provide information about the type of transfer, such as the transfer size and whether the transaction is bursted, write-through, or cache-inhibited.

- Address transfer termination—These signals are used to acknowledge the end of the address phase of the transaction. They also indicate whether a condition exists that requires the address phase to be repeated.

- Data arbitration—The e600 core uses these signals to arbitrate for data bus mastership.

- Data transfer—These signals, which consist of the data bus and data parity signals, are used to transfer the data and to ensure the integrity of the transfer.

- Data transfer termination—Data termination signals are required after each data beat in a data transfer. In a single-beat transaction, data termination signals also indicate the end of the tenure. In burst accesses, data termination signals apply to individual beats and indicate the end of the tenure only after the final data beat. Data termination signals also indicate whether a condition exists that requires the data phase to be repeated.

Many other e600 core signals control and affect other aspects of the device, aside from the bus protocol. They are as follows:

- Interrupts/resets—These signals include the external interrupt signal, checkstop signals, and both soft reset and hard reset signals. They are used to interrupt and, under various conditions, to reset the processor.

- Processor status and control—These signals enable the time-base facility and are used to select the bus mode and control sleep mode.

- Clock control—These signals determine the system clock frequency. They are also used to synchronize multiprocessor systems.

e600 Core Product Brief, Rev. 0

Freescale Semiconductor

- Test interface—The JTAG (IEEE 1149.1a-1993) interface and the common on-chip processor (COP) unit provide a serial interface to the system for performing board-level boundary-scan interconnect tests.

- Voltage selection—These signal control the electrical characteristics of the I/O circuitry of the device as appropriate to support various signaling levels.

#### **NOTE**

Active-low signals are shown with overbars. For example,  $\overline{ARTRY}$  (address retry) and  $\overline{TS}$  (transfer start). Active-low signals are referred to as asserted (active) when they are low and negated when they are high. Signals that are not active low, such as AP[0:4] (address bus parity signals) and TT[0:4] (transfer type signals) are referred to as asserted when they are high and negated when they are low.

### 2.8.3 MPX Bus Mode Functional Groupings

Figure 5 illustrates the signal configuration in MPX bus mode for the e600 core, showing how the signals are grouped. A pinout diagram and tables showing pin numbers are included in the hardware specifications. Note that the left side of the figure depicts the signals that implement the MPX bus protocol and the right side of the figure shows the remaining signals on the e600 core (not part of the bus protocol).

Figure 5. MPX Bus Signal Groups in the e600 Core

Signal functionality is described in detail in Chapter 8, "Signal Descriptions," and Chapter 9, "System Interface Operation," of the MPC7450 RISC Microprocessor Family User's Manual.

### **2.8.3.1 Clocking**

For functional operation, the e600 core uses a single clock input signal, SYSCLK, from which clocking is derived for the processor core and the MPX bus interface. Additionally, internal clock information is made available at the pins to support debug and development.

The e600 core clocking structure supports a wide range of processor-to-bus clock ratios. The internal processor core clock is synchronized to SYSCLK with the aid of a VCO-based PLL. The PLL\_CFG[0:5] signals are used to program the internal clock rate to a multiple of SYSCLK as defined in the hardware specifications. The bus clock is maintained at the same frequency as SYSCLK. SYSCLK does not need to be a 50% duty-cycle signal.

# 2.9 Power and Thermal Management

The e600 core is designed for low-power operation. It provides both automatic and program-controlled power reduction modes. If an e600 core functional unit is idle, it automatically goes into a low-power mode. This mode does not affect operational performance. Dynamic power management automatically supplies or withholds power to execution units individually, based upon the contents of the instruction stream. The operation of dynamic power management is transparent to software or any external hardware.

The following three programmable power modes are available to the system:

- Nap—Instruction fetching is halted. Only those clocks for time base, decrementer, and JTAG logic remain running. The e600 core goes into the doze state to snoop memory operations on the bus and then back to nap using a QREQ/QACK processor-system handshake protocol.

- Sleep—Power consumption is further reduced by disabling bus snooping, leaving only the PLL in a locked and running state. All internal functional units are disabled.

- Deep sleep—The system can disable the PLL. The system can then disable the SYSCLK source for greater system power savings. Power-on reset procedures for restarting and relocking the PLL must be followed upon exiting deep sleep.

The dynamic frequency switching (DFS) feature in the e600 core conserves power by lowering processor operating frequency. The e600 has the ability to divide the processor-to-system bus ratio by two or four during normal functional operation. Chapter 10, "Power and Thermal Management," of the MPC7450 RISC Microprocessor Family User's Manual provides information on power saving with DFS.

The e600 core also provides an instruction cache throttling mechanism to effectively reduce the instruction execution rate without the complexity and overhead of dynamic clock control. When used with the dynamic power management, instruction cache throttling provides the system designer with a flexible way to control device temperature while allowing the processor to continue operating. For thermal management, the e600 core provides a supervisor-level instruction cache throttling control register (ICTC). Chapter 10, "Power and Thermal Management," of the MPC7450 RISC Microprocessor Family User's Manual provides information about how to configure the ICTC register for the e600 core.

## 2.10 Performance Monitor

The e600 core incorporates a performance monitor facility that system designers can use to help bring up, debug, and optimize software performance. The performance monitor counts events during execution of instructions related to dispatch, execution, completion, and memory accesses.

The performance monitor incorporates several registers that can be read and written to by supervisor-level software. User-level versions of these registers provide read-only access for user-level applications. Performance monitor

control registers, MMCR0, MMCR1, and MMCR2 can be used to specify which events are to be counted and the conditions for which a performance monitoring exception is taken. Additionally, the sampled instruction address register, SIAR (USIAR), holds the address of the first instruction to complete after the counter overflowed.

Attempting to write to a user-level read-only performance monitor register causes a program exception, regardless of the MSR[PR] setting.

When a performance monitor exception occurs, program execution continues from vector offset 0x00F00.

Chapter 11, "Performance Monitor," of the MPC7450 RISC Microprocessor Family User's Manual describes the operation of the performance monitor diagnostic tool incorporated in the e600 core.

# 3 e600 Core Architectural Implementation

The PowerPC architecture consists of three layers. Adherence to the PowerPC architecture can be described in terms of which of the following levels of the architecture is implemented:

- PowerPC user instruction set architecture (UISA)—Defines the base user-level instruction set, user-level

registers, data types, floating-point exception model, memory models for a uniprocessor environment, and

programming model for a uniprocessor environment

- PowerPC virtual environment architecture (VEA)—Describes the memory model for a multiprocessor environment, defines cache control instructions, and describes other aspects of virtual environments.

Implementations that conform to the VEA also adhere to the UISA, but may not necessarily adhere to the OEA.

- PowerPC operating environment architecture (OEA)—Defines the memory management model, supervisor-level registers, synchronization requirements, and the exception model. Implementations that conform to the OEA also adhere to the UISA and the VEA.

The e600 core implementation supports the three levels of the architecture described above. For more information about the PowerPC architecture, see the *Programming Environments Manual for 32-Bit Implementations of the PowerPC Architecture.* Specific e600 core features are listed in Chapter 1, "Overview," of the *MPC7450 RISC Microprocessor Family User's Manual.*

This section describes the PowerPC architecture in general, and specific details about the implementation of the e600 core as a low-power, 32-bit device that implements this architecture. The structure of this section follows the user's manual organization. Each subsection provides an overview of that chapter.

- Registers and programming model—Describes the registers for the operating environment architecture

common among processors of this family and describes the programming model. It also describes the

registers that are unique to the e600 core.

- Instruction set and addressing modes—Describes the PowerPC instruction set and addressing modes for the PowerPC operating environment architecture, and defines and describes the PowerPC instructions implemented in the e600 core. The information in this section is described more fully in Chapter 2, "Programming Model," of the MPC7450 RISC Microprocessor Family User's Manual.

- Cache implementation—Describes the cache model that is defined generally by the virtual environment architecture. It also provides specific details about the e600 core cache implementation. The information in this section is described more fully in Chapter 3, "L1, L2, and L3 Cache Operation," of the MPC7450 RISC Microprocessor Family User's Manual.

- Exception model—Describes the exception model of the PowerPC operating environment architecture and the differences in the e600 core exception model. The information in this section is described more fully in Chapter 4, "Exceptions," of the MPC7450 RISC Microprocessor Family User's Manual.

e600 Core Product Brief, Rev. 0

- Memory management—Describes generally the conventions for memory management. This section also describes the e600 core implementation of the 32-bit PowerPC memory management specification. The information in this section is described more fully in Chapter 5, "Memory Management," of the MPC7450 RISC Microprocessor Family User's Manual.

- Instruction timing—Provides a general description of the instruction timing provided by the parallel execution supported by the PowerPC architecture and the e600 core. The information in this section is described more fully in Chapter 6, "Instruction Timing," of the MPC7450 RISC Microprocessor Family User's Manual.

- AltiVec implementation—Points out that the e600 core implements AltiVec registers, instructions, and

exceptions as described in the AltiVec Technology Programming Environments Manual. Chapter 7, "AltiVec

Technology Implementation," of the MPC7450 RISC Microprocessor Family User's Manual provides

complete details.

# 3.1 PowerPC Registers and Programming Model

The PowerPC architecture defines register-to-register operations for most computational instructions. Source operands for these instructions are accessed from the registers or are provided as immediate values embedded in the instruction opcode. The three-register instruction format allows specification of a target register distinct from the two source operands. Load and store instructions transfer data between registers and memory.

The PowerPC architecture also defines two levels of privilege—supervisor mode of operation (typically used by the operating system) and user mode of operation (used by the application software). The programming models incorporate 32 GPRs, 32 FPRs, SPRs, and several miscellaneous registers. The AltiVec extensions to the PowerPC architecture augment the programming model with 32 VRs, one status and control register, and one save and restore register. Each processor that implements the PowerPC architecture also has a unique set of implementation-specific registers to support functionality that may not be defined by the PowerPC architecture.

Having access to privileged instructions, registers, and other resources allows the operating system to control the application environment (providing virtual memory and protecting operating-system and critical machine resources). Instructions that control the state of the processor, the address translation mechanism, and supervisor registers can be executed only when the processor is operating in supervisor mode.

Figure 6 shows all the e600 core registers available at the user and supervisor level. The numbers to the right of the SPRs indicate the number that is used in the syntax of the instruction operands to access the register. For more information, see Chapter 2, "Programming Model," of the MPC7450 RISC Microprocessor Family User's Manual.

The OEA defines numerous SPRs that serve a variety of functions, such as providing controls, indicating status, configuring the processor, and performing special operations. During normal execution, a program can access the registers shown in Figure 6, depending on the program's access privilege (supervisor or user, determined by the privilege-level bit, MSR[PR]). GPRs, FPRs, and VRs are accessed through operands that are part of the instructions. Access to registers can be explicit (that is, through the use of specific instructions for that purpose such as Move to Special-Purpose Register (**mtspr**) and Move from Special-Purpose Register (**mfspr**) instructions) or implicit, as the part of the execution of an instruction.

|                                               |                                          | SUPERVIS                             | OR MODE                       | EL – OEA                  |                        |                                    |                    |

|-----------------------------------------------|------------------------------------------|--------------------------------------|-------------------------------|---------------------------|------------------------|------------------------------------|--------------------|

| USER MODEL – VEA                              | Hardware Config                          |                                      | guration Registers            |                           | Machine State Register |                                    |                    |

| Time Base Facility (For Read TBL TBR 268 TBU  | Implementation<br>Registers <sup>1</sup> |                                      | Processor Version<br>Register |                           | MSR                    | _                                  |                    |

| TBC TBK 200 TB0                               | HID0                                     | SPR 1008                             | PVR                           | SPR 287                   | Processor ID           | Register <sup>2</sup>              |                    |

| USER MODEL – UISA                             | HID1                                     | SPR 1009                             | 1 717                         | 01111207                  | PIR                    | SPR 1023                           |                    |

| Count Register Genera                         | al-Purpose                               | N                                    | lemory M                      | lanagement                | Register               | s                                  |                    |

| CTR SPR 9                                     | Registers                                | Instruction B                        | AT                            | Data BAT                  | •                      | Segment Regi                       | sters              |

| XER                                           | GPR0                                     | Registers                            | -                             | Registers                 | 1                      | SR0                                |                    |

| XER SPR 1                                     | GPR1                                     | IBAT0U                               | SPR 528                       | DBAT0U                    | SPR 536                | SR1                                |                    |

| Link Register                                 | :                                        | IBAT0L                               | SPR 529                       | DBAT0L                    | SPR 537                | :                                  |                    |

| LR SPR 8                                      | GPR31                                    | IBAT1U                               | SPR 530                       | DBAT1U                    | SPR 538                |                                    |                    |

|                                               |                                          | IBAT1L<br>IBAT2U                     | SPR 531<br>SPR 532            | DBAT1L<br>DBAT2U          | SPR 539<br>SPR 540     | SR15                               |                    |

| Performance Monitor Reg                       | gisters                                  | IBAT2L                               | SPR 533                       | DBAT2L                    | SPR 541                | PTE High/Low                       | 1                  |

| Floa                                          | ating-Point                              | IBAT3U                               | SPR 534                       | DBAT3U                    | SPR 542                | Registers <sup>1</sup>             |                    |

| Performance Counters <sup>1</sup>             | Registers                                | IBAT3L                               | SPR 535                       | DBAT3L                    | SPR 543                | PTEHI                              | SPR 981            |

| UPMC1 SPR 937                                 | FPR0                                     | IBAT4U <sup>1</sup>                  | SPR 560                       | DBAT4U <sup>1</sup>       | SPR 568                | PTELO                              | SPR 982            |

| UPMC2 SPR 938                                 | FPR1                                     | IBAT4L <sup>1</sup>                  | SPR 561                       | DBAT4L <sup>1</sup>       | SPR 569                | TLB Miss Reg                       | ister <sup>1</sup> |

| UPMC3 SPR 941                                 | :                                        | IBAT5U <sup>1</sup>                  | SPR 562                       | DBAT5U <sup>1</sup>       | SPR 570                | TLBMISS                            | SPR 980            |

| UPMC4 SPR 942                                 | FPR31                                    | IBAT5L <sup>1</sup>                  | SPR 563                       | DBAT5L <sup>1</sup>       | SPR 571                | SDR1                               |                    |

| UPMC5 SPR 929                                 |                                          | IBAT6U <sup>1</sup>                  | SPR 564                       | DBAT6U <sup>1</sup>       | SPR 572                | SDR1                               | SPR 25             |

| UPMC6 SPR 930                                 |                                          | IBAT6L <sup>1</sup>                  | SPR 565                       | DBAT6L <sup>1</sup>       | SPR 573                |                                    |                    |

| Sampled Instruction Conditio                  | n Register                               | IBAT7U <sup>1</sup>                  | SPR 566                       | DBAT7U <sup>1</sup>       | SPR 574                |                                    |                    |

| USIAR SPR 939                                 | CR                                       | IBAT7L <sup>1</sup>                  | SPR 567                       | DBAT7L <sup>1</sup>       | SPR 575                |                                    |                    |

|                                               |                                          | SPRGs                                | Exception                     | n Handling F              |                        |                                    |                    |

| Monitor Control <sup>1</sup> Floa             | ating-Point                              | SPRG0                                | SPR 272                       | Data Address<br>Register  | 5                      | Save and Rest<br>Registers         | ore                |

| 01                                            | Status and                               | SPRG0<br>SPRG1                       | SPR 272                       | DAR                       | SPR 19                 |                                    | SPR 26             |

| ONIMORT OF RESPO                              | ol Register                              | SPRG2                                | SPR 274                       |                           | 011013                 |                                    | SPR 27             |

| UMMCR2 SPR 928                                | FPSCR                                    | SPRG3                                | SPR 275                       | DSISR                     | 1                      | <u> </u>                           | · · · · · ·        |

| AltiVec Registers                             | SPRG4 <sup>1</sup>                       | SPR 276                              | DSISR                         | SPR 18                    |                        |                                    |                    |

| Vector Save/Restore Vector                    | SPRG5 <sup>1</sup>                       | SPR 277                              |                               |                           |                        |                                    |                    |

| Register <sup>3</sup>                         | VR0                                      | SPRG6 <sup>1</sup>                   | SPR 278                       |                           |                        |                                    |                    |

| VRSAVE SPR 256                                | VR1                                      | SPRG7 <sup>1</sup>                   | SPR 279                       | Cache/Men                 | -                      | system Regis                       |                    |

| Vector Status and                             | :                                        |                                      |                               | Instruction Con           | uonc,                  | L2 Error Contro<br>Capture Registe |                    |

| Control Register <sup>3</sup> VSCR            | VR31                                     | Load/Store                           |                               | Register <sup>1</sup>     | [                      | L2CAPTDATAH                        | II SPR 988         |

| \\\\_\V3CK                                    | <del></del>                              | Control Regis                        | ster <sup>1</sup>             | ICTRL                     | SPR 1011               | L2CAPTDATAL                        | SPR 989            |

|                                               |                                          | LDSTCR                               |                               | L2 Cache Cor              | ntrol                  | L2CAPTECC                          | SPR 990            |

|                                               |                                          | Memory Subs                          |                               | Register <sup>1</sup>     |                        | L2ERRDET                           | SPR 991            |

| Miscellaneous Registe                         |                                          | Status Contro                        |                               | L2CR                      | SPR 1017               | L2ERRDIS                           | SPR 992            |

| Time Base Data Addre (For Writing) Breakpoint | ess<br>• Register <sup>2</sup>           | Registers <sup>1</sup>               |                               | L2 Error Inject           | ion                    | L2ERRINTEN                         | SPR 993            |

| TBL SPR 284 DABR                              | SPR 1013                                 | MSSCR0                               | OI IX 1014                    | Registers                 | 7.000.00-              | L2ERRATTR                          | SPR 994            |

| TDU 000 005                                   |                                          | MSSSR0                               | SPR 1015                      | L2ERRINJHI                | SPR 985                | L2ERRADDR                          | SPR 995            |

| Pagistar2                                     | ccess                                    |                                      | -                             | L2ERRINJLO                |                        | L2ERREADDR                         |                    |

| Instruction Address Breakpoint Register  EAR  | SPR 282                                  |                                      |                               | L2ERRINJCTL               |                        | L2ERRCTL                           | SPR 997            |

| 1100 000 1010                                 |                                          |                                      |                               | nce Monitor               |                        |                                    |                    |

| IABR SPR 1010 Decremente                      | SPR 22                                   | Performance<br>Counters <sup>2</sup> |                               | Monitor Cont<br>Registers | roi                    | Breakpoint Ac<br>Mask Register     |                    |

|                                               |                                          | PMC1                                 | SPR 953                       | MMCR0 <sup>2</sup>        | SPR 952                | BAMR                               | SPR 951            |

| Thermal Management Reg                        | gister                                   | PMC2                                 | SPR 954                       | MMCR1 <sup>2</sup>        | SPR 956                |                                    |                    |

| Instruction Cache Throttling                  |                                          | PMC3                                 | SPR 957                       | MMCR2 <sup>1</sup>        | SPR 944                | Sampled Instr                      |                    |

| Control Register <sup>1</sup>                 |                                          | PMC4                                 | SPR 958                       |                           |                        | Address Regi                       |                    |

| ICTC SPR 1019                                 |                                          | PMC5                                 | SPR 945<br>SPR 946            |                           |                        | SIAR                               | SPR 955            |

|                                               |                                          | PMC6                                 | 3FR 940                       |                           |                        |                                    | /                  |

Figure 6. Programming Model—e600 Core Registers

e600-specific register may not be supported on other processors or cores that implement the PowerPC architecture.

Register defined as optional in the PowerPC architecture.

Register defined by the AltiVec technology.

Some registers can be accessed both explicitly and implicitly. In the e600 core, all SPRs are 32 bits wide. Table 1 describes registers implemented by the e600 core. For the full table, see Table 1-1 in Chapter 1, "Overview," of the MPC7450 RISC Microprocessor Family User's Manual.

Table 1. Register Summary for the e600 Core