# V.21 / V.23 FSK MODEM

- COMPLETE FSK MODEM JUST ADD LINE INTERFACE

- COMPATIBLE WITH BELL 103/113/108, BELL 202, CCITT V.21, CCITT V.23 SPECIFICA-TIONS

- NO EXTERNAL FILTERING REQUIRED

- ALL DIGITAL SIGNAL PROCESSING, DIGITAL FILTERS AND ADC/DAC INCLUDED ON-CHIP

- INCLUDES ESSENTIAL RS-232/CCITT V.24 HANDSHAKE SIGNALS

- AUTO-ANSWER CAPABILITY

- LOCAL COPY/TEST MODES

- 1200 BPS FULL DUPLEX ON 4-WIRE LINE

- PIN-PROGRAMMABLE MODE SECTION

## DESCRIPTION

The EF7910 is a single-chip asynchronous Frequency Shift Keying (FSK) voiceband modem. It is pin selectable for baud rates of 300, 600, or 1200 bits per second and is compatible with the applicable Bell and CCITT recommended standards for 103/113/108, 202, V.21 and V.23 type modems. Five mode control lines select a desired modem configuration.

Digital signal processing techniques are employed in the EF7910 to perform all major functions such as modulation, demodulation and filtering. The EF7910 contains on-chip analog-to-digital and digital-to-analog converter circuits to minimize the external components in a system. This device includes the essential RS-232/CCITT V.24 terminal control signals with TTL levels.

Clocking can be generated by attaching a crystal to drive the internal crystal oscillator or by applying an external clock signal.

A data access arrangement (DAA) or acoustic coupler must provide the phone line interface externally.

The EF7910 is fabricated using HMOS technology. All the digital input and output signals (except the external clock signal) are TTL compatible. Power supply requirements are  $\pm$  5 volts.

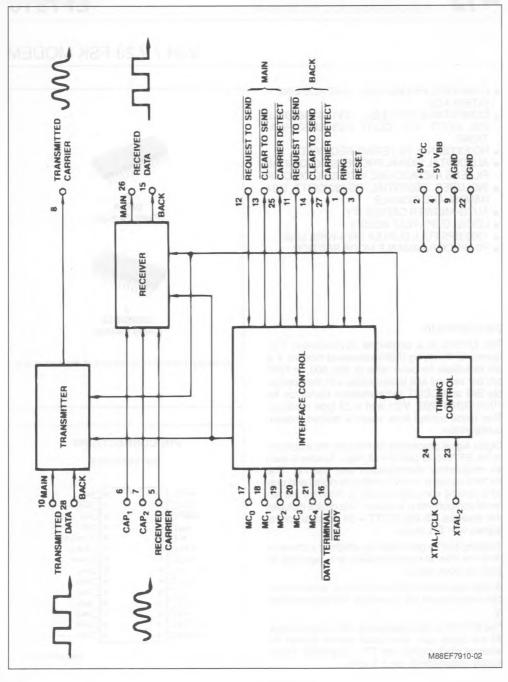

## **BLOCK DIAGRAM**

SGS-THOMSON

57

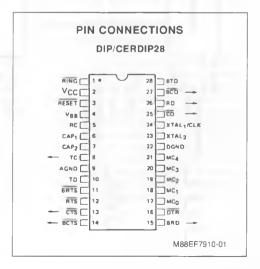

# INTERFACE SIGNAL DESCRIPTION

## MC<sub>0</sub> - MC<sub>4</sub> (control inputs)

These five inputs select one of thirty-two modem configurations according to the Bell or CCITT specifications listed in table 1. Only 19 of these 32 modes are actually available to the user.

Modes 0-8 are the normal operation modes. The 1200 Baud modes can be selected with or without a compromise equalizer.

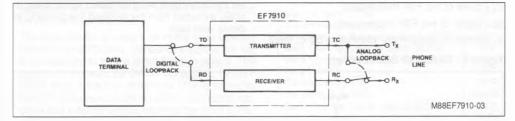

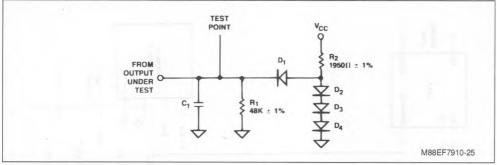

Modes 16-25 permit loop back of the EF7910 transmitter and receiver. No internal connection is made. The user must externally connect the TRANSMIT-TED CARRIER pin (figure 1) to the RECEIVED CARRIER pin if analog loopback is required. For digital loopback, external connection of RECEIVED DATA and TRANSMITTED DATA is required. Whenever a mode in this group is selected, the effect is to set all transmit and receive filters to the same channel frequency band so that loopback can be performed.

Modes 9-15 and 26-31 are reserved and should not be used.

# DATA TERMINAL READY (DTR)

A LOW level on this input indicates the data terminal desires to send and/or receive data via the modem. This signal is gated with all other TTL inputs and outputs so that a low level enables all these signals as well as the internal control logic to function. A HIGH level disables all TTL I/O pins and the internal logic.

# REQUEST TO SEND (RTS)

A LOW level on this input instructs the modem to enter transmit mode. This input must remain LOW for the duration of data transmission. The signal has no effect if DATA TERMINAL READY is HIGH (disabled). A HIGH level on this input turns off the transmitter.

# CLEAR TO SEND (CTS)

This output <u>goes LOW at the end</u> of a delay initiated when REQUEST TO SEND goes LOW. Actual data to be transmitted should not be presented to the TRANSMITTED DATA input until a LOW is indicated on the CLEAR TO SEND output. Normally the user should force the TD input HIGH whenever CTS is off (HIGH). This signal never goes LOW as long as DTR is HIGH (disabled). CLEAR TO SEND <u>goes HIGH at the</u> end of a delay initiated when RE-QUEST TO SEND goes HIGH.

# CARRIER DETECT (CD)

A LOW on this output indicates that a valid carrier signal is present at the receiver and has been present for at least a time,  $t_{CDON}$ , where  $t_{CDON}$  depends upon the selected modem configuration (Table 3b). A HIGH on this output signifies that no valid carrier is being received and has not been received for a time,  $t_{CDOFF}$ . CARRIER DETECT remains HIGH when DTR is HIGH. Values for  $t_{CDON}$  and  $t_{COFF}$  are configuration dependent and are listed in table 3b.

## TRANSMITTED DATA (TD)

Data bits to be transmitted are presented on this input serially; HIGH (mark) corresponds to logic 1 and LOW (space) corresponds to logic 0. This data determines which frequency appears at any instant at the TRANSMITTED CARRIER output pin (table 3a). No signal appears at the TRANSMITTED CARRIER output unless DTR is LOW and RTS is LOW.

## RECEIVED DATA (RD)

Data bits demodulated from the RECEIVED CAR-RIER input are available serially at this output. HIGH (mark) indicates logic 1 and LOW (space) indicates logic 0. Under the following conditions this output is forced to logic 1 because the data may be invalid :

- 1. When CARRIER DETECT is HIGH

- 2. During the internal squelch delay at half-duplex line turn around (202/V.23 modes only)

- During soft carrier turnoff at half-duplex line turn around (202 mode only)

- 4. When DTR is HIGH

- 5. When RTS ON and BRTS OFF in V.23/202 modes only

- 6. During auto-answer sequence

# BACK REQUEST TO SEND (BRTS)

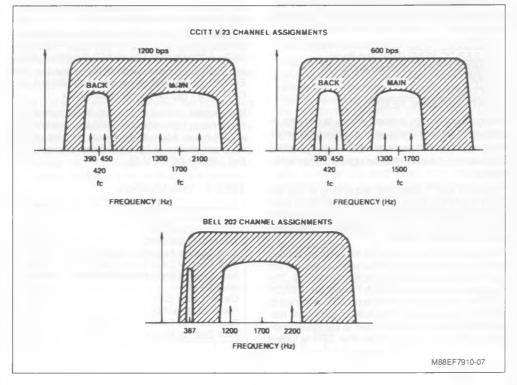

Since the 1200 bps modem configurations, Bell 202 and CCITT V.23, permit only half duplex operation over two-wire lines, a low baud rate "backward" channel is provided for transmission from the main channel receiver to the main channel transmitter. <u>This input</u> signal (BRTS) is equivalent to REQUEST TO SEND for the main channel, except it belongs to the backward channel. Note that since the EF7910 contains a single transmitter, RTS and BRTS should not be asserted simultaneously. BRTS is meaningful only when a 202 or V.23 mode is selected by MC<sub>0</sub>-MC<sub>4</sub>. In all other modes it is ignored.

For V.23 mode the frequency appearing at the transmitted carrier (TC) output pin is determined <u>bv</u> a MARK or SPACE at the back transmitted data (BTD) input (table 3a).

For 20<u>2 mode</u> a frequency of 387 Hz appears at TC when BRTS is LOW and BTD is <u>HIGH</u>. No energy (0.0 Volt) appears at TC when BRTS is LOW and BTD is <u>HIGH</u>. No energy (0.0 volt) appears at TC when BRTS is HIGH. BTD should be fixed HI<u>GH for</u> 202 back channel transmission. The signal, BRTS, then is equivalent to the signal, Secondary Request-to-Send, for 202 S/T modems, or Supervisory Transmitted Data for 202 C/D modems.

# BACK CLEAR TO SEND (BCTS)

This line is equivalent to CLEAR TO SEND for the main channel, except it belongs to the back channel. BCTS is meaningful only when a V.23 mode is selected by MC<sub>0</sub>-MC<sub>4</sub>. This signal is not used in Bell 202 back mode.

## BACK CARRIER DETECT (BCD)

This line is equivalent to CARRIER DETECT for the main channel. except it belongs to the backward channel. BCD is meaningful only when a 202 or V.23 mode is selected by MC<sub>0</sub>-MC<sub>4</sub>. For V.23 back channel mode, BCD turns on when either the MARK or SPACE frequency appears with sufficient level at the received carrier (RC) input.

For 202 back channel mode, BCD turns on in response to a 387 Hz tone of sufficient level at the RC input. In this case BCD is equivalent to the signal, Secondary Received Line Signal Detector, for 202 S/T modems, or Supervisory Received Data for 202 C/D modems.

## BACK TRANSMITTED DATA (BTD)

This line is equivalent to TRANSMITTED DATA for the main channel, except it belongs to the back channel. BTD is meaningful only when a 202 or V.23 mode is selected by  $MC_0$ - $MC_4$ . For 202 back transmission of on/off keying, BTD should be fixed at a HIGH level.

### BACK RECEIVED DATA (BRD)

This line is equivalent to RECEIVED DATA (except clamping) for the main channel, except it belongs to the back channel. BRD is meaningful only when a V.23 mode is selected by  $MC_0$ - $MC_4$ . Under the following conditions this output is forced HIGH :

- 1. BRD HIGH

- 2. DTR HIGH

- 3. V.21/103 mode

- 4. During auto-answer

5. When BRTS ON and RTS OFF in V.23 modes only

### TRANSMITTED CARRIER (TC)

This analog output is the modulated carrier to be conditioned and sent over the phone line.

### RECEIVED CARRIER (RC)

This input is the analog signal received from the phone line. The modem extracts the information contained in this modulated carrier and converts it into a serial data stream for presentation at the RE-CEIVED DATA (BACK RECEIVED DATA) output.

## RING

This input signal permits auto-answer capability by responding to a ringing signal from a data access arrangement. If a ringing signal is detected (RING LOW) and DTR is LOW, the modem begins a sequence to generate an answer tone at the TC output.

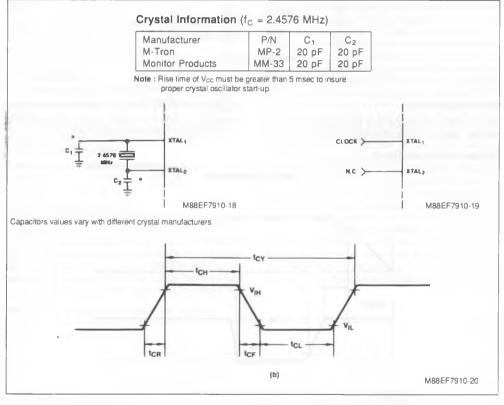

#### XTAL1, XTAL2

Master timing of the modern is provided by either a crystal connected to these two inputs or an external clock inserted into XTAL<sub>1</sub>. The value of the crystal or the external clock frequency must be  $2.4576 \text{ MHz} \pm 01 \%$ .

#### Vcc

+ 5 volt power supply  $(\pm 5 \%)$

VBB

-5 volt power supply ( $\pm 5$  %).

DGND

Digital signal ground pin.

### AGND

Analog signal ground pin (for TRANSMITTED CAR-RIER and RECEIVED CARRIER).

### CAP<sub>1</sub>, CAP<sub>2</sub>

Connection points of external capacitor/resistor required for proper operation of on-chip analog-to-digital converter.

Recommended values are :  $C = 2 nF \pm 10 \%$ ,

$R = 100 \Omega \pm 10 \%$ .

### RESET

This input signal is for a reset circuit which operates in either of two modes. It automatically resets when power is applied to the device, or it can be activated by application of an external active low TTL pulse.

Table 1.

| MC4 | MC <sub>3</sub> | MC <sub>2</sub> | MC1 | MC <sub>0</sub> |                                                       |

|-----|-----------------|-----------------|-----|-----------------|-------------------------------------------------------|

| 0   | 0               | 0               | 0   | 0               | Bell 103 Originate 300 bps Full Duplex                |

| 0   | 0               | 0               | 0   | 1               | Bell 103 Answer 300 bps Full Duplex                   |

| 0   | 0               | 0               | 1   | 0               | Bell 202 1200 bps Half Duplex                         |

| 0   | 0               | 0               | 1   | 1               | Bell 202 with Equalizer 1200 bps Half Duplex          |

| 0   | 0               | 1               | 0   | 0               | CCITT V.21 Orig 300 bps Full Duplex                   |

| 0   | 0               | 1               | 0   | 1               | CCITT V.21 Ans 300 bps Full Duplex                    |

| 0   | 0               | 1               | 1   | 0               | CCITT V.23 Mode 2 1200 bps Half Duplex                |

| 0   | 0               | 1               | 1   | 1               | CCITT V.23 Mode 2 with Equalizer 1200 bps Half Duplex |

| 0   | 1               | 0               | 0   | 0               | CCITT V.23 Mode 1600 bps Half Duplex                  |

| 0   | 1               | 0               | 0   | 1               |                                                       |

| 0   | 1               | 0               | 1   | 0               |                                                       |

| 0   | 1               | 0               | 1   | 1               |                                                       |

| 0   | 1               | 1               | 0   | 0               | Reserved                                              |

| 0   | 1               | 1               | 0   | 1               |                                                       |

| 0   | 1               | 1               | 1   | 0               |                                                       |

| 0   | 1               | 1               | 1   | 1               |                                                       |

| 1   | 0               | 0               | 0   | 0               | Bell 103 Orig Loopback                                |

| 1   | 0               | 0               | 0   | 1 1             | Bell 103 Ans Loopback                                 |

| 1   | 0               | 0               | 1   | 0               | Bell 202 Main Loopback                                |

| 1   | 0               | 0               | 1   | 1               | Bell 202 with Equalizer Loopback                      |

| 1   | 0               | . 1             | 0   | 0               | CCITT V.21 Orig Loopback                              |

| 1   | 0               | 1               | 0   | 1               | CCITT V.21 Ans Loopback                               |

| 1   | 0               | 1               | 1   | 0               | CCITT V.23 Mode 2 Main Loopback                       |

| 1   | 0               | 1               | 1   | 1               | CCITT V.23 Mode 2 with Equalizer Loopback             |

| 1   | 1               | 0               | 0   | 0               | CCITT V.23 Mode 1 Main Loopback                       |

| 1   | 1               | 0               | 0   | 1               | CCITT V.23 Back Loopback                              |

| 1   | 1               | 0               | 1   | 0               |                                                       |

| 1   | 1               | 0               | 1   | 1               |                                                       |

| 1   | 1               | 1               | 0   | 0               | Reserved                                              |

| 1   | 1               | 1               | 0   | 1               |                                                       |

| 1   | 1               | 1               | 1   | 0               |                                                       |

| 1   | 1               | 1               | 1   | 1               |                                                       |

Figure 1 : Loopback Configurations.

# THEORY OF OPERATION

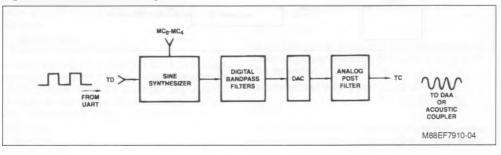

The EF7910 MODEM consists of three main sections, shown in the block diagram - Transmitter, Receiver, and Interface Control.

#### TRANSMITTER (modulator)

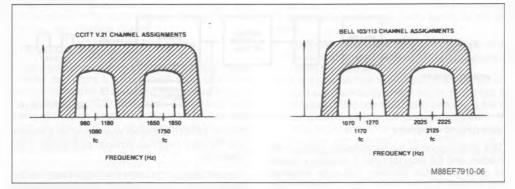

The transmitter, shown in figure 2 receives binary digital data from a source such as a UART and converts the data to an analog signal using frequency shift keying (FSK) modulation. This analog signal is applied to the phone line through a DAA or acoustic coupler. FSK is a modulation technique which encodes one bit per baud. A logic one applied to the TRANSMITTED DATA (TD) input causes a sine wave at a given frequency to appear at the analog TRANSMITTED CARRIER (TC) output. A logic zero applied to input TD causes a sine wave of a different frequency to appear at the TC output. As the data at the TD input switches between logical one and zero, the TC output switches between the two frequencies. In the EF7910 this switching between frequencies is phase continuous. The frequencies themselves are digitally synthesized sine functions.

The frequencies for each modem configuration available in the EF7910 are listed in table 3a.

The process of switching between two frequencies as in FSK generates energy at many more frequencies than the two used in the modulation. All the transmitted information can be recovered from a frequency band B Hz wide, where B is the bit rate or maximum rate of change of the digital data at the TD input. This band is centered about a frequency, fc,

where  $f_C = f_1 + (f_2 - f_1)/2$

(f1 = lower of two FSK frequencies)

(f2 = higher of two FSK frequencies)

In addition to this primary information band, there

Figure 2 : Transmitter Block Diagram.

exist side bands containing redundant information. It is desirable to attenuate these bands for two reasons :

- The phone companies have specifications on the amount of energy allowed in certain frequency bands on the line.

- 2. If two independent information channels are present simultaneously on the line (e.g. 300 bps full duplex or 1200 bps half duplex with back), the redundant transmitter components may fall in the frequency band of the local receiver channel and interfere with detection. In the EF7910 these redundant and undesirable components are attenuated by digital bandpass filters.

Following the digital bandpass filters, the filtered FSK signal is converted to an analog signal by an on-chip DAC operating at a high sample rate. This analog FSK signal is finally smoothed by a simple on-chip analog low pass filter.

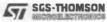

#### **RECEIVER** (demodulator)

A simplified block diagram of the EF7910 FSK receiver is shown in Figure 3. Data transmitted from a remote site modem over the phone line is an FSKmodulated analog carrier. This carrier is applied to the RECEIVED CARRIER (RC) pin via a DAA or acoustic coupler. The first stage of the demodulator is a simple on-chip analog low pass anti-alias filter. The output of this is converted into digital form and filtered by digital bandpass filters to improve the signal to noise ratio and reject other independent channel frequencies associated with the phone line in the case of full duplex configuration. The bandpass filtered output is digitally demodulated to recover the binary data. A carrier detect signal is also digitally extracted from the received line carrier to indicate valid data.

Figure 3 : Receiver Block Diagram.

#### INTERFACE CONTROL

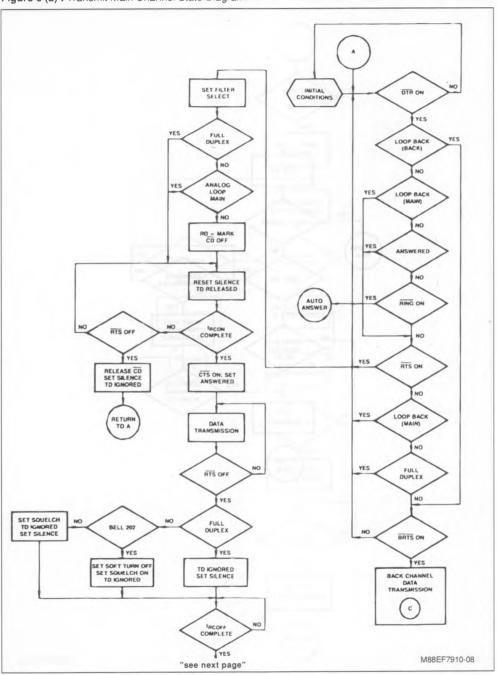

This section controls the handshaking between the modem and the local terminal. It consists primarily of delay generation counters, two state machines for controlling transmission and reception, and mode control decode logic for selecting proper transmit frequencies and transmit and receive filters according to the selected modem type. Inputs and outputs from this section are as follows :

REQUEST TO SEND (Main and Back) CLEAR TO SEND (Main and Back) CARRIER DETECT (Main and Back) RING MC0-MC4 DATA TERMINAL READY

Internal logic clamps protocol signals to different levels under certain conditions (e.g., initial conditions).

When Bell 103/113 and V.21 modem configurations are selected, the back channel signals are non-functional.

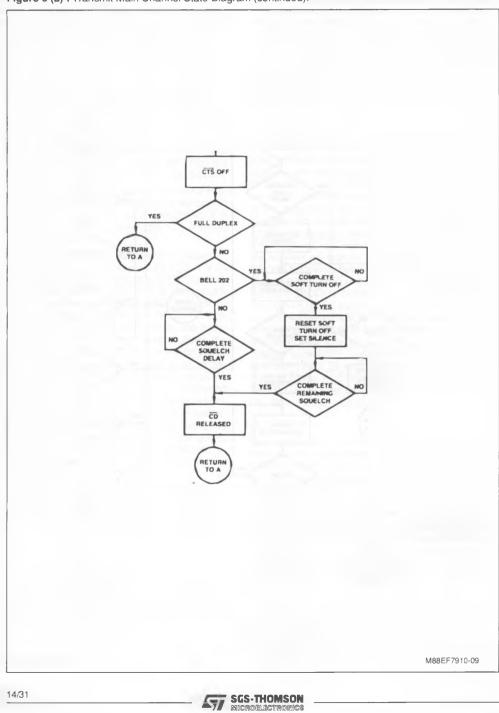

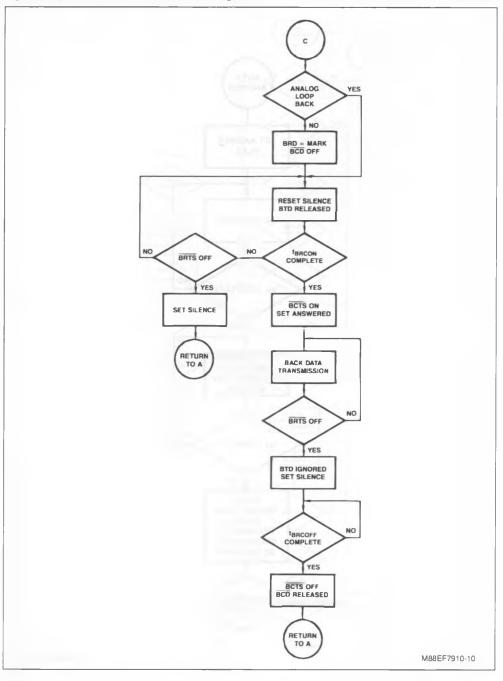

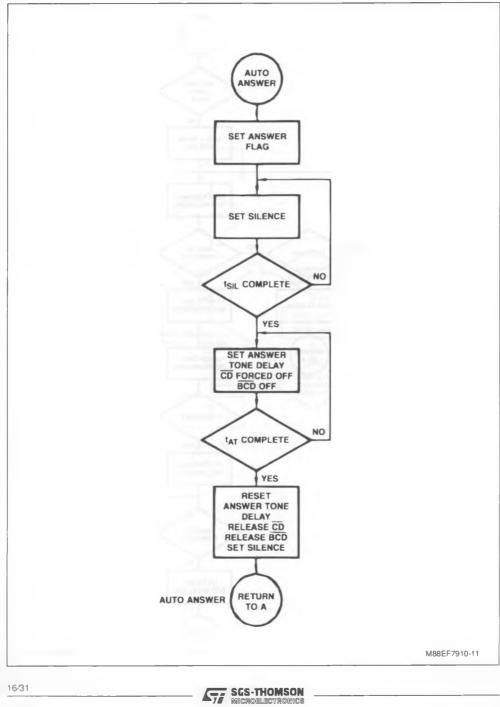

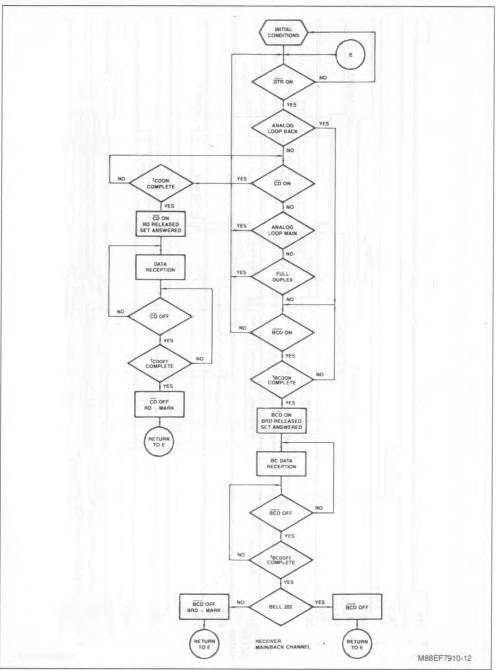

Figures 6 and 7 depict the sequencing of the two state machines. State machine 1 implements main or back channel transmission and the auto-answer sequence. State machine 2 implements reception on main or back channel.

The state machine powers on to the state labelled INITIAL CONDITIONS. Handshake signals are set to or assumed to be the levels listed in table 2. The machine then waits for DATA TERMINAL READY (DTR) to be turned on. Whenever DTR is turned to the OFF state from an ON condition, each state machine and external signals return to the initial conditions within 25 microseconds. After DTR is turned

ON the EF7910 becomes operational as a modem and the state machines proceed as depicted in the flowcharts.

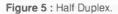

The definitions of the terms Full Duplex and Half Duplex used in these flowcharts are depicted below (figs. 4 and 5). "Full Duplex" applies to all 103/113, V.21 modes. "Hall Duplex" applies to 202 and V.23, both forward and backward channel.

**Full Duplex :** Data can be transmitted and received simultaneously at a rate of 300 baud. Two independent 300 Hz channels are frequency multiplexed into the 3000 Hz bandwidth of the phone line. The EF7910 configurations for the Bell 103/113 and CCITT V.21 can be operated full duplex.

Half Duplex : In half duplex with back channel, the modem may transmit at 1200/600 baud and receive at 5/75 baud. Alternatively it may transmit at 5/75 baud and receive at 1200/600 baud. Examples are Bell 202 and CCITT V.23.

#### Table 2 : Initial Conditions

| Data Terminal Ready (DTR)           | OFF     |

|-------------------------------------|---------|

| Request to Send (RTS)               | OFF     |

| Clear to Send (CTS)                 | OFF     |

| Transmitted Data (TD)               | Ignored |

| Back Channel Request to Send (BRTS) | OFF     |

| Back Channel Clear to Send (BCTS)   | OFF     |

| Back Channel Transmitted Data (BTD) | Ignored |

| Ring (RING)                         | OFF     |

| Carrier Detect (CD)                 | OFF     |

| Received Data (RD)                  | MARK    |

| Back Channel Carrier Detect (BCD)   | OFF     |

| Back Channel Received Data (BRD)    | MARK    |

## Figure 4 : Full Duplex.

Table 3 (a) : Frequency Parameters.

|                             | Baud          |        | Transmit<br>Frequency |            | Rec<br>Frequ | Answer     |             |

|-----------------------------|---------------|--------|-----------------------|------------|--------------|------------|-------------|

| Modem                       | Rate<br>(BPS) | Duplex | Space<br>Hz           | Mark<br>Hz | Space<br>Hz  | Mark<br>Hz | Freq.<br>Hz |

| Bell 103 Orig               | 300           | Full   | 1070                  | 1270       | 2025         | 2225       |             |

| Bell 103 Ans                | 300           | Full   | 2025                  | 2225       | 1070         | 1270       | 2225        |

| CCITT V.21 Orig             | 300           | Full   | 1180                  | 980        | 1850         | 1650       |             |

| CCITT V.21 Ans              | 300           | Full   | 1850                  | 1650       | 1180         | 950        | 2100        |

| CCITT V.23 Mode 1           | 600           | Half   | 1700                  | 1300       | 1700         | 1300       | 2100        |

| CCITT V.23 Mode 2           | 1200          | Half   | 2100                  | 1300       | 2100         | 1300       | 2100        |

| CCITT V.23 Mode 2 Equalized | 1200          | Half   | 2100                  | 1300       | 2100         | 1300       | 2100        |

| Bell 202                    | 1200          | Half   | 2200                  | 1200       | 2200         | 1200       | 2025        |

| Bell 202 Equalized          | 1200          | Half   | 2200.                 | 1200       | 2200         | 1200       | 2025        |

| CCITT V.23 Back             | 75            |        | 450                   | 390        | 450          | 390        |             |

| Bell 202 Back               | 5             |        |                       | •          | • •          | **         |             |

\* (BRTS LOW) and (BTD HIGH) : 387 Hz at TC \* (BRTS HIGH) or (BTD LOW) : 0 volt at TC \*\* No 387 Hz at RC : BCD LOW

\* Meets new CCITT R20 frequency tolerance.

Frequency tolerance is less than ± 0.4 Hz with 2.4576 MHz Crystal. Except Bell 202 which is + 1 Hz (1200 Hz, mark)

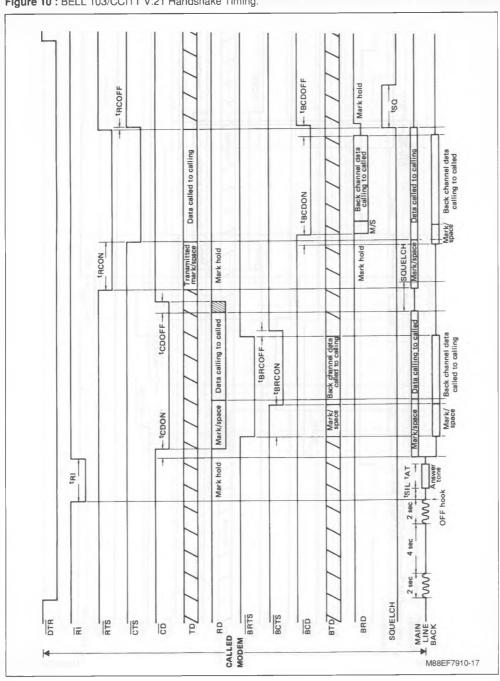

| Table 3 (b): Timing | Parameters (r | refer to figures 9, | 10 and 11 | for timing | diagrams). |

|---------------------|---------------|---------------------|-----------|------------|------------|

|---------------------|---------------|---------------------|-----------|------------|------------|

| Symbol           | Description                                                | Bell 103<br>Orig | Bell 103<br>Ans | Bell 202  | Bell 202<br>EQ | Bell 202<br>Back | Unit             |

|------------------|------------------------------------------------------------|------------------|-----------------|-----------|----------------|------------------|------------------|

| tac (on)         | Request-to-Send to<br>Clear-to-Send ON Delay               | 208.3            | 208.3           | 183.3     | 183.3          |                  | msec<br>± 0.3 %  |

| tRC (off)        | Request-to-Send to<br>Clear-to-Send OFF Delay              | 0.5              | 0.5             | 0.5       | 0.5            |                  | msec<br>± 0.25 % |

| tBRC (on)        | Back Channel Request-to-Send<br>to Clear-to-Send ON Delay  |                  |                 |           |                |                  | msec<br>± 0.64 % |

| tBRC (off)       | Back Channel Request-to-Send<br>to Clear-to-Send OFF Delay |                  |                 |           |                |                  | msec<br>± 25 %   |

| tcD (on)         | Carrier Detect ON Delay                                    | 94-106           | 94-106          | 18-22     | 18-22          |                  | msec             |

| tcD (off)        | Carrier Detect OFF Delay                                   | 21-40            | 21-40           | 12.4-23.4 | 12.4-23.4      |                  | msec             |

| tBCD (on)        | Back Channel Carrier Detect<br>ON Delay                    |                  |                 |           |                | 17-25            | msec             |

| tBCD (off)       | Back Channel Carrier Detect<br>OFF Delay                   |                  |                 |           |                | 21-38            | msec             |

| t <sub>AT</sub>  | Answer Tone Duration                                       |                  | 1.9             | 1.9       | 1.9            |                  | sec ± 0.44<br>%  |

| t <sub>SIL</sub> | Silence Interval before<br>Transmission                    | 1.3              | 1.3             | 1.3       | 1.3            |                  | sec ± 0.64<br>%  |

| tsa              | Receive Squelch Duration                                   |                  |                 | 156.3     | 156.3          |                  | msec<br>± 3.3 %  |

| tsro             | Transmitter Soft Turn-Off<br>Duration                      |                  |                 | 24        | 24             |                  | msec<br>± 2.3 %  |

| t <sub>RI</sub>  | Minimum RI Low Duration                                    |                  | 25              | 25        | 25             |                  | μS               |

| Table | 3 | (c): | (continued). |

|-------|---|------|--------------|

|-------|---|------|--------------|

| Symbol                | Description                                                      | CCITT<br>V.21<br>Orig | CCITT<br>V.21<br>Ans | CCITT<br>V.23<br>Mode 1 | CCITT<br>V.23<br>Mode 2 | CCITT<br>V.23<br>Mode 2<br>EQ | CCITT<br>V.23<br>Back | Unit             |

|-----------------------|------------------------------------------------------------------|-----------------------|----------------------|-------------------------|-------------------------|-------------------------------|-----------------------|------------------|

| t <sub>RC (on)</sub>  | Request-to-Send to<br>Clear-to-Send ON Delay                     | 400                   | 400                  | 208.3                   | 208.3                   | 208.3                         |                       | msec<br>± 0.3 %  |

| t <sub>RC (off)</sub> | Request-to-Send to<br>Clear-to-Send OFF<br>Delay                 | 0.5                   | 0.5                  | 0.5                     | 0.5                     | 0.5                           |                       | msec<br>± 0.25 % |

| tBRC (on)             | Back Channel<br>Request-to-Send to<br>Clear-to-Send ON Delay     |                       |                      |                         |                         |                               | 82.3                  | msec<br>± 0.64 % |

| tBRC (off)            | Back Channel<br>Request-to-Send to<br>Clear-to-Send OFF<br>Delay |                       |                      |                         |                         |                               | 0.5                   | msec<br>± 25 %   |

| t <sub>CD</sub> (on)  | Carrier Detect ON<br>Delay                                       | 301-312               | 301-312              | 11.4-15.4               | 11.4-15.4               | 11.4-15.4                     |                       | msec             |

| t <sub>CD (off)</sub> | Carrier Detect OFF<br>Delay                                      | 21-40                 | 21-40                | 5.4-13.3                | 5.4-13.3                | 5.4-13.3                      |                       | msec             |

| tBCD (on)             | Back Channel Carrier<br>Detect ON Delay                          |                       |                      |                         |                         |                               | 17-25                 | msec             |

| tBCD (off)            | Back Channel Carrier<br>Detect OFF Delay                         |                       |                      |                         |                         |                               | 21-38                 | msec             |

| t <sub>AT</sub>       | Answer Tone Duration                                             |                       | 3.0                  | 3.0                     | 3.0                     | 3.0                           |                       | sec<br>± 0.44 %  |

| tsiL                  | Silence Interval before<br>Transmission                          | 1.9                   | 1.9                  | 1.9                     | 1.9                     | 1.9                           |                       | sec<br>± 0.64 %  |

| tsa                   | Receiver Squelch<br>Duration                                     |                       |                      | 156.3                   | 156.3                   | 156.3                         |                       | msec<br>± 3.3 %  |

| tsto                  | Transmitter Soft<br>Turn-Off Duration                            |                       |                      |                         |                         |                               |                       | msec<br>± 2.3 %  |

| t <sub>RI</sub>       | Minimum RI Low<br>Duration                                       |                       | 25                   | 25                      | 25                      | 25                            |                       | μS               |

## CALL ESTABLISHMENT

Before two modems can exchange data, an electrical connection through the phone system must be established. Although it may assist in call establishment, a modem typically does not play a major role. A call may be originated manually or automatically and it may be answered manually or automatically.

Manual Calling - Manual calling is performed by a person who dials the number, waits for an answer, then places the calling modem into data transmission mode.

Automatic Calling - Automatic calling is typically performed by an automatic calling unit (ACU) which generates the appropriate dialing pulse or dual-tone sequence required to call the remote (called) modem. The ACU also has the ability to detect an answer tone from the called modem and place the calling modem into data transmission mode.

Manual Answering - Manual answering is performed by a person who hears the phone ring, lifts the receiver, causes the called modern to send an answer tone to the calling modern, and places the called modem into data transmission mode.

Automatic Answering - Automatic answering is performed by a called modem with a data access arrangement (DAA). The DAA detects a ringing signal, takes the phone circuit off-hook (corresponding to lifting the receiver) and instructs the called modem to commence the auto-answer sequence. Next the called modem sends out silence on the line, followed by an answer tone. When this tone is detected

by the calling modem, the connection is considered to have been established.

The EF7910 provides assistance for automatic answering through the RING signal as follows. Observe the upper right-hand portion of Figure 6 (a). Assume that DATA TERMINAL READY (DTR) has recently been asserted to cause exit from the initial conditions. Note that if DTR remains OFF, RING is ignored. Assume also that RTS and BRTS are OFF and that the mode control lines (MC0-MC4) select a normal modem configuration, not a loopback mode. Automatic answering is initiated by receipt of a LOW level at the RING input, causing entrance to the auto-answer sequence depicted in Figure 6 (c).

The EF7910 outputs silence (0.0 volt) at its TRANS-MITTED CARRIER (TC) output for a time, tsil followed by the answer tone for a time, tar. The CAR-RIER DETECT (CD) pin is clamped OFF and the RECEIVED DATA (RD) signal is therefore clamped to a MARK (HIGH) during the auto-answer sequence. Upon completion of the answer tone, CD is released. If the mode lines (MC0-MC4) select a 202 or V.23 mode, the transmit filters are set to the forward channel and the receive filters are set to the back channel during the auto answer sequence.

At the end of the auto-answer sequence, return is made to point A in the loop at the upper right-hand portion of Fig. 6 (a). Note that since the answer flag has been set, the auto-answer sequence cannot be entered again unless DTR is first turned OFF, then ON. At this point the phone line connection has been established and data transmission or reception may begin.

The RING input may be activated from a conditioned DAA Ring indicator output for automatic answering or it may be <u>activa</u>ted by a switch for manual answering. Tying RING HIGH will disable the autoanswer function of the EF7910.

#### DATA TRANSMISSION

FULL DUPLEX. Following call establishment, full duplex data transmission can be started by either the called or calling modem. In other words, if the connection has been established and the modem is looping through point A in figure 6 (a), it no longer matters which is the called and which is the calling modem. Data transmission is initiated by asserting REQUEST TO SEND (RTS). At this time the TRANSMITTED DATA (TD) input will be released and a modulated carrier can appear at the TRANS-MITTED CARRIER (TC) output. Following a delay, t<sub>RCON</sub>, CLEAR TO SEND (CTS) will turn ON. At this time, data may be transmitted through the TD input. It is a common protocol for the user to always pre-

sent a MARK at the TD input before RTS is asserted and during the tRCON delay.

Data transmission continues until RTS is turned OFF. Following a short delay,  $t_{RCOFF}$ , CTS turns OFF. As soon as RTS goes OFF, the TD input is ignored and the TC output is set to 0.0 volt (silence). After CTS turns OFF, the state machine returns to point A in Figure 6 (a).

HALF DUPLEX. When a half duplex mode is selected (202 or V.23), data transmission can be either on the main channel at 1200/600 baud or on the back channel at 5/75 baud. In normal half duplex operation a single modem is either transmitting on the main and receiving on the back channel or vice versa. In the EF7910 control of the transmitter and receiver filters to the proper channel is performed by RTS. When RTS is asserted, the transmitter filters and synthesizer are set to transmit on the main channel; the receiver filters are set to receive on the back channel. Therefore, whenever RTS is on, BRTS should not be asserted since the transmitter cannot be used for the back channel. When RTS is OFF and a half duplex mode is selected, the transmitter filters and synthesizer are set to the back channel ; the receiver filters are set to the main channel. If RTS and BRTS are asserted simultaneously, RTS will take precedence. However, if BRTS is asserted before RTS and the back channel data transmission sequence has been entered (Figure 6 (b)). RTS will be ignored until BRTS is turned OFF.

The state machine sequences for main and back channel transmission differ slightly and are depicted in figure 6. Assume the state machine is idling through point A in Figure 6 (a).

MAIN CHANNEL. This transmission sequence is entered if a 202 or V.23 mode is selected and RTS is asserted. Since the receiver is now forced to the back channel, the RECEIVED DATA (RD) signal is clamped to a MARK ; and the CARRIER DETECT signal is clamped OFF. The TRANSMITTED DATA input (TD) is released and a carrier appears at the TRANSMITTED CARRIER output which follows the MARK/SPACE applied to TD. RTS turning ON initiates a delay, tRCON, at the end of which the CLEAR TO SEND (CTS) output goes LOW. When CTS goes LOW data may be transmitted through input TD. Data transmission continues until RTS is turned OFF. At this time several events are initiated. First a delay, tRCOFF, is initiated at the end of which CTS turns OFF. The TD input is ignored as soon as RTS goes OFF. If a 202 mode is selected, a soft turn-off tone appears at the TC output for a time, tsto, followed by silence (0.0 volt). For both 202 and V.23 modes a squelch period, tso, is initiated when RTS

goes OFF. During this period the CD output is clamped OFF, forcing the RD output to a MARK condition. The squelch period begins as soon as RTS goes OFF and thus overlaps both  $t_{RCOFF}$  and  $t_{STO}$ . At the end of the squelch period, the state machine returns to the idle loop at point A in Figure 6 (a).

The reasons for squelch and soft-turnoff are as follows :

Soft Turn-Off : When RTS is turned OFF at the end of a message, transients occur which may cause spurious space signals to be received at a remote modem. During soft turn-off the modem transmits a soft carrier frequency for a period, t<sub>STO</sub>, after RTS is turned OFF. This results in a steady MARK on the RECEIVED DATA (RD) line of the remote modem.

Squelch : The local receiver must be turned OFF after RTS is OFF, until the start of carrier detect, so that the line transients are not demodulated. The process of disabling the receiver after RTS is turned OFF is called squelching.

BACK CHANNEL. This transmission sequence, shown in Figure 6 (b), is entered if a 202 or V.23 mode is selected, RTS is OFF, and BRTS is asserted. The BACK CARRIER DETECT (BCD) output is forced OFF and the BACK RECEIVED DATA (BRD) output is clamped to a MARK. The BACK TRANS-MITTED DATA input (BTD) is released and a carrier appears at the TC output which follows the MARK/SPACE applied to BTD. Turning on BRTS initiates a delay, tBRCON, at the end of which the BACK CLEAR TO SEND (BCTS) output goes LOW. When BCTS goes LOW data may be transmitted through input BTD. Data transmission continues until BRTS is turned OFF. The input BTD is immediatly ignored and the TC output is silenced (set to 0.0 volt). Following a short delay, tBRCOFF, the output BCTS goes OFF. The signals BCD and BRD are released and the state machine returns to idle at point A of figure 6 (a).

In 202 back channel mode, BTD should be tied HIGH. Then BRTS controls the ON/OFF keying modulation. When BRTS is LOW, 387 Hz appears at the TC output ; when BRTS is HIGH, 0 volt appears at TC.

## DATA RECEPTION

Data reception is controlled by state machine 2 and depicted in figure 7. At power on the machine enters initial conditions and remains there until DTR is asserted. If then loops until either CARRIER DETECT (CD) or BACK CARRIER DETECT (BCD) occurs.

FULL DUPLEX. In full duplex data reception, CAR-RIER DETECT may appear at any time after the phone connection has been established. Reception is independent of transmission. When the receiver detects a valid carrier for at least a time, t<sub>CDON</sub>, the output CD is turned ON, the RECEIVED DATA (RD) output is released, and valid data can be obtained at RD. Data is received until the receiver detects loss of carrier for at least a time, t<sub>CDOFF</sub>. At this time the CD output is turned OFF and RD is clamped to a MARK. The state machine returns to the idle loop at point E.

HALF DUPLEX. As discussed in the data transmission section above, when a half duplex mode has been selected, the signal RTS controls whether the main channel is transmitting or receiving. The back channel can only do the opposite from the main. If RTS is OFF, then CARRIER DETECT may be asserted and the data reception sequence is identical to that discussed above for full duplex reception. As long as RTS remains OFF, BACK CARRIER DE-TECT will never be asserted. If RTS is ON, then CARRIER DETECT will never be asserted. Instead the receiver will look for a valid carrier in the back channel frequency band. If a valid carrier exists for at least a time, tector, the output BACK CARRIER DETECT (BCD) is turned ON, the BACK RECEI-VED DATA (BRD) output is released and valid data can be obtained at BRD. Data is received until the receiver detects loss of back channel received signal for at least time, tBCDOFF. At this time the BCD output is turned OFF. Data output, BRD, is clamped to a MARK if a V.23 mode is selected. For 202 back channel mode, BCD represents the received data. The BRD output can be ignored. The state machine returns to the idle loop at point E.

## LOOPBACK

Ten modes exist to allow both analog and digital loopback for each modem specification met by the EF7910. When a loopback mode is selected, the signal processing (filters, etc.) for both the transmitter and receiver is set to process the same channel or frequency band. This allows the analog output, TRANSMITTED CARRIER. and the analog input, RECEIVED CARRIER, to be connected for local analog loopback. Alternatively the digital data signals, TD and RD or BTD and BRD, can be connected externally, allowing a remote modem to test the local modem with its digital data signals looped back.

When a loopback mode is selected, the state machine sequences are altered slightly. First, autoanswer is disabled. Second, if a half duplex loopback mode is selected (202 or V.23), the local CAR-<u>RIER\_DETECT/BCD</u> is not forced OFF when RTS/BRTS is asserted.

SGS-THOMSON MICROELECTRONICS

Figure 6 (b) : Transmit Back Channel State Diagram.

Figure 7 : Receiver Main/Back Channel State Diagram.

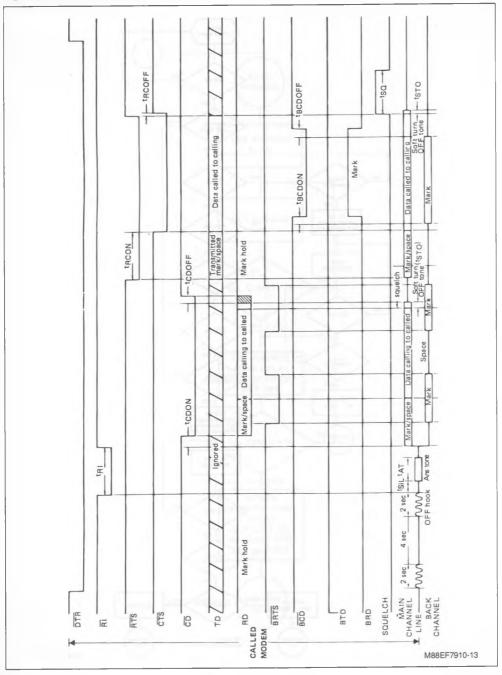

Figure 8 : BELL 202 Handshake Timing.

57

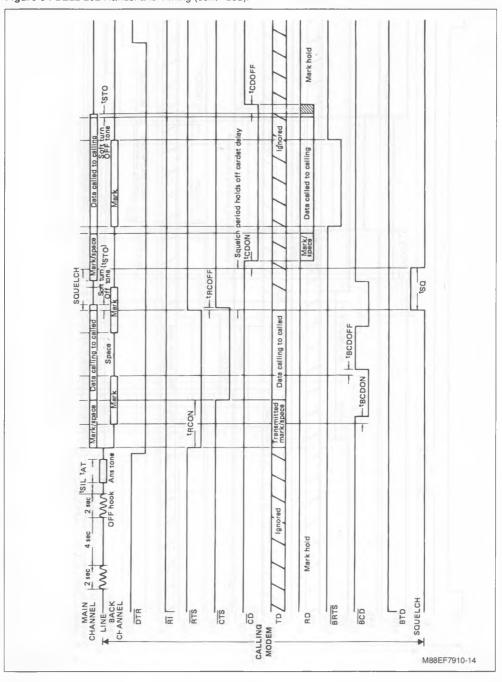

Figure 8 : BELL 202 Handshake Timing (continued).

19/31

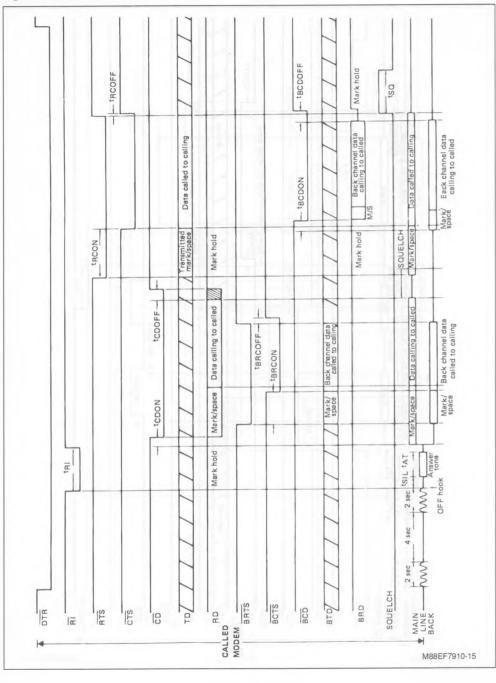

## Figure 9 : CCITT V.23 Handshake Timing.

SGS-THOMSON MICROELECTRONICS

51

SGS-THOMSON MICROELECTROMICS

57

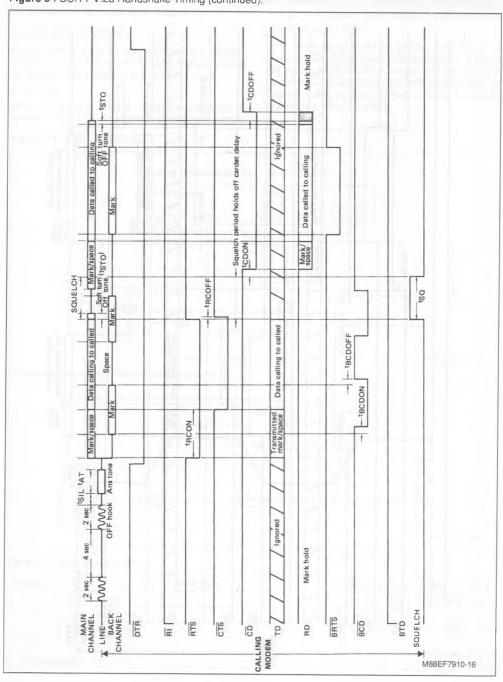

Figure 9 : CCITT V.23 Handshake Timing (continued).

21/31

SGS-THOMSON MICROELECT ROMICS

57

# EF7910

Figure 10 : BELL 103/CCITT V.21 Handshake Timing.

22/31

The 202 and V.23 main loopback modes allow use in a 4-wire configuration at 1200 bps.

## CLOCK GENERATION

Master timing of the modem is provided by either a crystal connected to the XTAL1 and XTAL2 inputs or an external clock applied to the XTAL1 input.

#### CRYSTAL.

When a crystal is used it should be connected as shown in figure 11. The crystal should be a parallel

#### Figure 11 : Clock Generation.

resonance type, and its value must be 2.4576 MHz  $\pm$  0.01 %. A list of crystal suppliers is shown below.

## EXTERNAL CLOCK

This clock signal could be derived from one of several crystal-driven baud rate generators. It should be connected to the XTAL<sub>1</sub> input and the XTAL<sub>2</sub> input must be left floating. The timing parameters required of this clock are shown in figure 11 and the values are listed in table 4.

## Table 4 : Clock Parameters.

| Symbol | Parameter       | Min.   | Тур.  | Max.   | Unit |

|--------|-----------------|--------|-------|--------|------|

| tcy    | Clock Period    | 406.86 | 406.9 | 406.94 | ns   |

| tсн    | Clock High Time | 165    |       |        | ns   |

| tcL    | Clock Low Time  | 165    |       |        | ns   |

| tcR    | Clock Rise Time |        |       | 20     | ns   |

| tor    | Clock Fall Time |        |       | 20     | ns   |

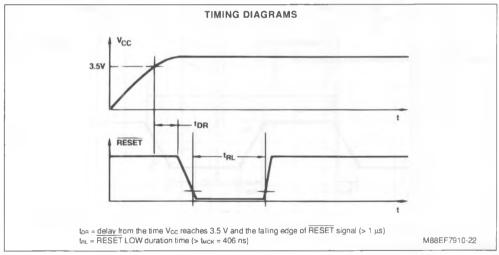

## POWER ON RESET

The reset circuit operates in either of two modes. AUTOMATIC RESET

In this mode an internal reset sequence is automatically entered when power is applied to the device.

## Figure 12 : Automatic Reset.

One resistor and one capacitor must be connected externally as shown in Figure 12. Values shown will work with most power supplies. Power supply (Vcc) rise time should be less than one half the RC time constant.

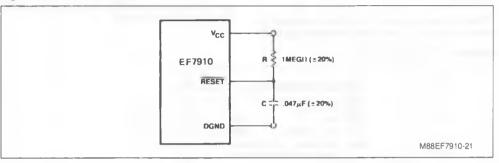

## EXTERNAL RESET

In this mode the device may be forced into the reset sequence by application of an active LOW pulse applied to the RESET input. The reset must not be applied until the  $V_{CC}$  supply has reached at least 3.5 V. Timing is diagrammed in figure 13.

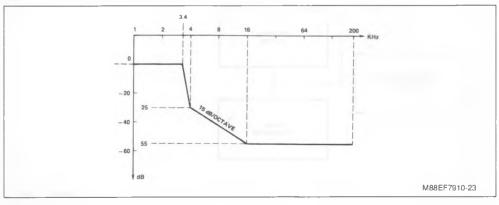

## NOMINAL PERFORMANCE SPECIFICATIONS TRANSMITTER (all modem types)

Input Data Format : Serial, asynchronous, standard TTL levels Modulation Technique :

Binary, phase-coherent Frequency Shift Keying (FSK)

TC Output Level : - 3 dBm into 600 Ω

Frequency Accuracy :

± 0.4 Hz all modems except Bell 202 (mark)

+ 1.0 Hz Bell 202 (mark)

Harmonics : - 45 dB from fundamental for single tones

Delay uncertainty for TD logic input change to TC frequency change :  $\leq 8.3 \ \mu s$

Out-of-band energy : see figure 14

## RECEIVER

Output Data Format : Serial, asynchronous, TTL levels Demodulation Technique : Differential FM Detection

Sensitivity at Receiver Input : 0 dBm to - 48 dBm Frequency Deviation Tolerance : ± 16 Hz Carrier Detect Threshold :

ON > - 40 dBm ± 1 dB OFF < - 43 dBm ± 1 dB Hysteresis > 2.5 dB

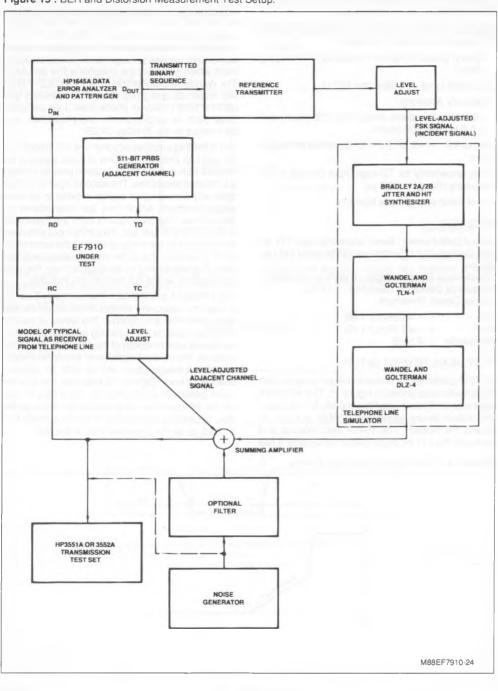

## TEST MEASUREMENT SETUP

EF7910 performance is characterized using the test equipment setup shown in Figure 15. The HP1645A data error analyzer is used to generate 511-bit pseudo random binary sequences (PRBS) at  $D_{OUT}$  for testing the modem. The 1645A also receives and analyzes the 511-bit digital pattern at  $D_{IN}$  after it has

Figure 14 : Out-of-band Transmitter Energy.

progressed around the test loop. A reference transmitter converts the digital sequence generated by the HP1645A into an FSK signal. The FSK signal is typically adjusted to different levels from – 12 to – 45 dBm. The level-adjusted FSK signal or incident signal then passes through three pieces of equipment which comprise the telephone line simulator. The Wandel and Golterman TLN-1 and DLZ-4 simulate amplitude and group delay characteristics typical of a wide variety of phone lines. Line perturbations, such as amplitude hits and phase hits, may be injected by the Bradley 2A/2B.

The summing amplifier which drives the moder under test has three inputs. One of these inputs is the incident FSK signal which has been passed through a simulated phone line. The second input is from an optionally filtered noise source in order to simulate noise conditions which may be encountered on phone lines. The third input is from the transmitter of the EF7910 under test. This third input simulates the adjacent channel signal seen at the input of the EF7910 receiver due to the duplexer used on 2-wire lines. If 4-wire testing is being performed, the adjacent channel would not normally be included.

The HP3551A or HP3552A Transmission Test Set is used for measuring various levels which the modem under test is to receive. The levels of each of the three inputs to the summing amplifier should be measured independently of the other two inputs. For instance, the incident signal level should be measured by the transmission test set with no adjacent channel or noise present. The dashed line from the noise generator shows that the noise may or may not be measured at the output of the noise generator, depending on whether or not an optional filter is used, or on the characteristics of the filter.

26/31

## STANDARD LOAD CIRCUIT

Notes: 1. C1 = 50 pF including stray and wiring capacitance.

2. All diodes are 1N3064 or equivalent

3. All resistors are 1/8 watt.

V<sub>CC</sub> = 5 volts ± 1 %.

## APPLICATIONS

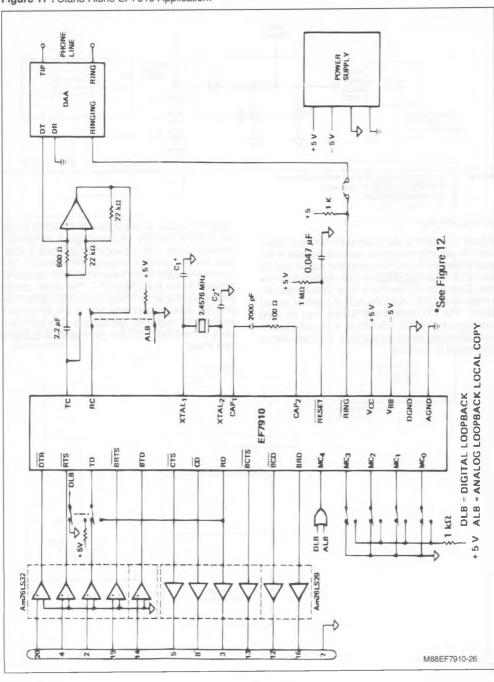

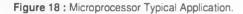

Figure 17 depicts a stand-alone EF7910 configuration. An op amp and three resistors provide a duplexor function to put the transmitter output into the line while receiving adjacent channel data from the line. Connection to the line is via a Data Access Arrangement (DAA). Note the lack of external analog filters. The TTL handshake signals may be level converted to RS-232, RS-422, or V.24 using appropriate devices. Mode control lines are hardwired or connected to switches. Figure 18 depicts an application of the EF7910 with the SGS-THOMSON Microelectronics EF6805CT microcomputer. The duplexor/line interface is identical to the above configuration. However, the handshake signals interface directly with the UART included inside the EF6805CT. The mode control lines might also be controlled by the MCU while keeping the address and data bus of the EF6805CT available for customer applications. The main features of the EF6805CT are given at the end of this data sheet.

SGS-THOMSON MICROELECTROMICS

57

Figure 17 : Stand-Alone EF7910 Application.

# ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter                                         | Value         | Unit |

|--------|---------------------------------------------------|---------------|------|

| Tstg   | Storage Temperature                               | - 65 to + 125 | °C   |

| Tamb   | Ambient Temperature under Bias                    | 0 to + 70     | °C   |

| Vcc    | V <sub>CC</sub> with Respect to V <sub>DGND</sub> | + 6 / - 0.4   | V    |

| VBB    | V <sub>BB</sub> with Respect to V <sub>DGND</sub> | - 6 / + 0.4   | V    |

|        | All Signal Voltages with Respect to VDGND         | ± 5           | V    |

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of charge. It is suggested, nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages. mum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Stresses above those listed under "Absolute Maxi-

## ELECTRICAL DC CHARACTERISTICS over operating range, referred to VDGND

$0 \text{ }^{\circ}\text{C} \le T_A \le +70 \text{ }^{\circ}\text{C}, V_{CC} = +5.0 \text{ } V \pm 5 \text{ } \%, V_{BB} = -5.0 \text{ } V \pm 5 \text{ } \%, V_{AGND} = 0 \text{ } V \pm 50 \text{ } \text{mV}, V_{DGND} = 0 \text{ } V$ Digital Inputs : TD, RTS, MC<sub>0</sub>-MC<sub>4</sub>, DTR, RING, BTD, BRTS

Digital Outputs : RD, CTS, CD, BRD, BCTS, BCD

| Symbol          | Parameter                                                                | Min.  | Тур. | Max.  | Unit |

|-----------------|--------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>он</sub> | Output HIGH Voltage (I <sub>OH</sub> = - 50 μA, C <sub>LD</sub> = 50 pF) | 2.4   |      |       | V    |

| VOL             | Output LOW Voltage (I <sub>OL</sub> = + 2 mA, C <sub>LD</sub> = 50 pF)   |       |      | 0.4   | V    |

| VIH             | Input HIGH Voltage                                                       | 2.0   |      | Vcc   | V    |

| VIL             | Input LOW Voltage                                                        | - 0.5 |      | + 0.8 | V    |

| VIHC            | External Clock Input HIGH (XTAL <sub>1</sub> )                           | 3.8   |      | Vcc   | V    |

| VILC            | External Clock Input LOW (XTAL <sub>1</sub> )                            | - 0.5 |      | 0.8   | V    |

| VIHR            | External Reset Input HIGH (RESET)                                        | 3.8   |      | Vcc   | V    |

| VILR            | External Reset Input LOW (RESET)                                         | - 0.5 |      | 0.8   | V    |

| L               | Digital Input Leakage Current (0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> )   | - 10  |      | + 10  | μA   |

| Icc             | V <sub>CC</sub> Supply Current                                           |       |      | 125   | mA   |

| IBB             | VBB Supply Current                                                       |       |      | 25    | mA   |

| COUT            | Output Capacitance (f <sub>C</sub> = 1.0 MHz)                            |       | 5    | 15    | pF   |

| CIN             | Input Capacitance (f <sub>C</sub> = 1.0 MHz)                             |       | 5    | 15    | pF   |

#### ANALOG INPUT (RC) :

| R <sub>IN</sub> | Input Resistance (- 1.6 V < V <sub>RC</sub> < + 1.6 V) | 50    |       | kΩ |

|-----------------|--------------------------------------------------------|-------|-------|----|

| VRC             | Operating Input Signal                                 | - 1.6 | + 1.6 | V  |

| VRCOS           | Allowed DC Input Offset (REF VAGND)                    | - 30  | + 30  | mV |

#### ANALOG OUTPUT (TC) :

| VTC   | Output Voltage ( $R_L = 600 \Omega$ ) | - 1.1 |       | + 1.1 | V  |

|-------|---------------------------------------|-------|-------|-------|----|

| VTCOS | Output DC Offset                      |       | ± 200 |       | mV |

# ORDERING INFORMATION

| Part Number | Temperature Range | Package  |

|-------------|-------------------|----------|

| EF7910PL    | 0 to 70 °C        | DIP 28   |

| EF7910JL    | 0 to 70 °C        | CERDIP28 |

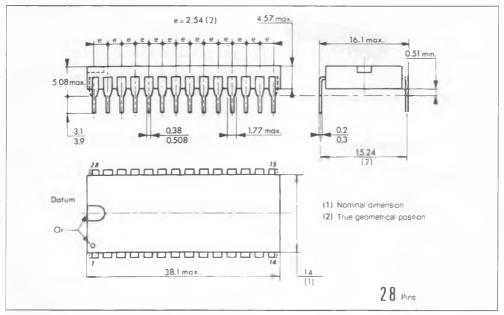

# PACKAGE MECHANICAL DATA

28 PINS – PLASTIC PACKAGE