Data Sheet September 2000 File Number 4102.2

# 6-Bit, 20MSPS, Video A/D Converter (CMOS)

HI1172 is a 6-bit, CMOS A/D converter for video use. The adoption of a 2-step parallel conversion achieves speeds of 20MSPS minimum, 35MSPS typical.

## **Ordering Information**

| PART TEMP. RANGE (°C) |           | PACKAGE    | PKG. NO. |  |

|-----------------------|-----------|------------|----------|--|

| HI1172JCB             | -20 to 75 | 16 Ld SOIC | M16.2-S  |  |

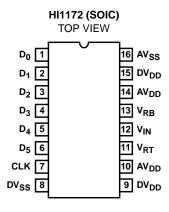

#### **Pinout**

#### **Features**

| • Resolution                                                          |

|-----------------------------------------------------------------------|

| Maximum Sampling Frequency                                            |

| Low Power Consumption at 20MSPS (Typ)<br>(Reference Current Excluded) |

| Built-In Sample and Hold Circuit                                      |

| Three-State TTL Compatible Output                                     |

| Power Supply 5V Single                                                |

| • Low Input Capacitance4pF                                            |

| • Reference Impedance                                                 |

#### **Applications**

- · Video Digitizing

- · Wireless Communications

#### Related Literature

Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

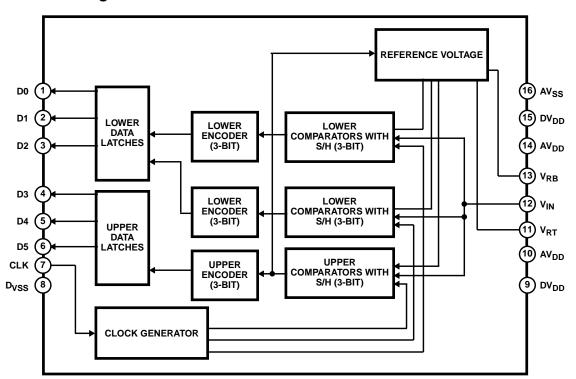

## Functional Block Diagram

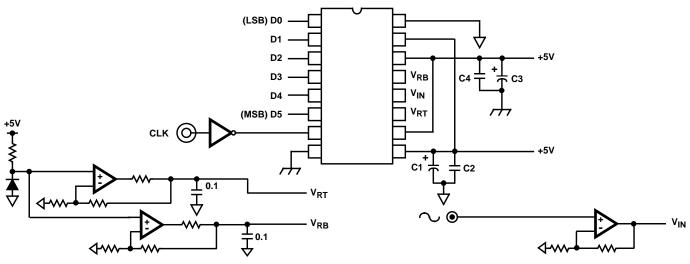

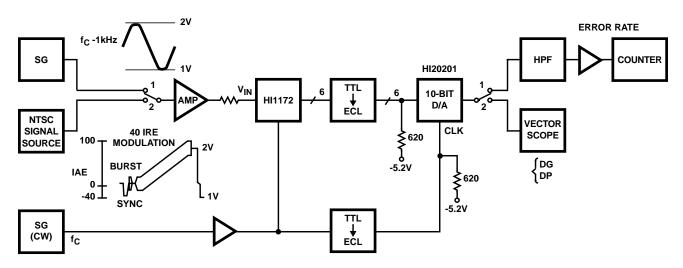

## Typical Application Circuit

## Pin Descriptions

| PIN<br>NUMBER SYMBOL |                  | EQUIVALENT CIRCUIT                                 | DESCRIPTION                  |  |  |

|----------------------|------------------|----------------------------------------------------|------------------------------|--|--|

| 1 to 6               | D0 to D5         |                                                    | D0 (LSB) to D5 (MSB) Output. |  |  |

| 7                    | CLK              | 7 —W DV <sub>DD</sub>                              | Clock Input.                 |  |  |

| 8                    | DV <sub>SS</sub> |                                                    | Digital GND.                 |  |  |

| 9, 15                | DV <sub>DD</sub> |                                                    | Digital +5V.                 |  |  |

| 10, 14               | AV <sub>DD</sub> |                                                    | Analog +5V.                  |  |  |

| 11                   | V <sub>RT</sub>  | φ AV <sub>DD</sub>                                 | Reference Voltage (Top).     |  |  |

| 13                   | V <sub>RB</sub>  | 11 AV <sub>SS</sub>                                | Reference Voltage (Bottom).  |  |  |

| 12                   | V <sub>IN</sub>  | AV <sub>DD</sub> AV <sub>DD</sub> AV <sub>SS</sub> | Analog Input.                |  |  |

| 16                   | AV <sub>SS</sub> | <del></del>                                        | Analog GND.                  |  |  |

## **Absolute Maximum Ratings** $T_A = 25^{\circ}C$

| Supply Voltage (V <sub>DD</sub> )                           | 7 V                                                        |

|-------------------------------------------------------------|------------------------------------------------------------|

| Reference Voltage (V <sub>RT</sub> , V <sub>RB</sub> )      | $V_{\mbox{\scriptsize DD}}$ to $V_{\mbox{\scriptsize SS}}$ |

| Analog Input Voltage (V <sub>IN</sub> )                     | $V_{DD}$ to $V_{SS}$                                       |

| Digital Input Voltage (CLK)                                 | $V_{DD}$ to $V_{SS}$                                       |

| Digital Output Voltage (V <sub>OH</sub> , V <sub>OL</sub> ) | $V_{DD}$ to $V_{SS}$                                       |

#### **Operating Conditions**

| Supply Voltage Range, AV <sub>DD</sub> , AV <sub>SS</sub> 4.75V to 5.25V   |

|----------------------------------------------------------------------------|

| Reference Voltage, DV <sub>DD</sub> , DV <sub>SS</sub>                     |

| V <sub>RT</sub> 0.9V to 5V                                                 |

| V <sub>RB</sub>                                                            |

| V <sub>RT</sub> - V <sub>RB</sub>                                          |

| Analog Input Voltage (V <sub>IN</sub> ) V <sub>RB</sub> to V <sub>RT</sub> |

| Clock Pulse Width                                                          |

| t <sub>PW1</sub>                                                           |

| t <sub>PW0</sub>                                                           |

| Temperature Range20°C to 75°C                                              |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | θ <sub>JA</sub> (°C/W) |

|------------------------------------------------|------------------------|

| SOIC Package                                   | 120                    |

| Maximum Junction Temperature (Plastic Package) | 150 <sup>o</sup> C     |

| Maximum Storage Temperature Range6             | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                  |

| (SOIC - Lead Tips Only)                        |                        |

|                                                |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $V_{DD} = +5V$ , $V_{RB} = 1V$ , $V_{RT} = 2V$ , $T_A = 25^{\circ}C$

| PARAMETER                                                  | SYMBOL           | TEST CONDITIONS                                           |                          | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------|------------------|-----------------------------------------------------------|--------------------------|------|------|------|-------|

| Conversion Speed, f <sub>C</sub>                           | f <sub>C</sub>   | V <sub>IN</sub> = 1V to 2V<br>f <sub>IN</sub> = 1kHz Ramp |                          | 0.5  | -    | 20   | MSPS  |

| Integral Non-Linearity                                     | EL               | $f_C = 20MSPS$<br>$V_{IN} = 1V \text{ to } 2V$            | ,                        | -    | ±0.3 | ±0.5 | LSB   |

| Differential Non-Linearity                                 | E <sub>D</sub>   | $f_C = 20MSPS$<br>$V_{IN} = 1V \text{ to } 2V$            | ,                        | -    | ±0.3 | ±0.5 | LSB   |

| Supply Current                                             | I <sub>DD</sub>  | f <sub>C</sub> = 20MSPS<br>NTSC Ramp V                    | Vave Input               | -    | 7    | 12   | mA    |

| Reference Pin Current                                      | I <sub>REF</sub> |                                                           |                          | 3    | 4    | 5.7  | mA    |

| Analog Input (-1dB)                                        | BW               |                                                           |                          | -    | 18   | -    | MHz   |

| Analog Input Capacitance                                   | C <sub>IN</sub>  | V <sub>IN</sub> = 1.5V + 0.07V <sub>RMS</sub>             |                          | -    | 4    | -    | pF    |

| Reference Resistance (V <sub>RT</sub> to V <sub>RB</sub> ) | R <sub>REF</sub> |                                                           |                          | 175  | 250  | 325  | Ω     |

| Offset Voltage                                             | E <sub>OT</sub>  |                                                           |                          | 0    | -20  | -40  | mV    |

|                                                            | E <sub>OB</sub>  |                                                           |                          | 15   | 35   | 55   | mV    |

| Digital Input Voltage                                      | V <sub>IH</sub>  |                                                           |                          | 4.0  | -    | -    | V     |

|                                                            | V <sub>IL</sub>  |                                                           |                          | -    | -    | 1.0  | V     |

| Digital Input Current                                      | I <sub>IH</sub>  | V <sub>DD</sub> = Max                                     | $V_{IH} = V_{DD}$        | -    | -    | 5    | μΑ    |

|                                                            | I <sub>IL</sub>  |                                                           | V <sub>IL</sub> = 0V     | -    | -    | 5    | μΑ    |

| Digital Output Current                                     | I <sub>OH</sub>  | V <sub>DD</sub> = Min                                     | $V_{OH} = V_{DD} = 0.5V$ | -1.1 | -    | -    | mA    |

|                                                            | l <sub>OL</sub>  |                                                           | $V_{OL} = 0.4V$          | 3.7  | -    | -    | mA    |

| Output Data Delay                                          | T <sub>DL</sub>  | With TTL 1 Gate and 10pF Load                             |                          | -    | 18   | 30   | ns    |

| Differential Gain Error                                    | DG               | NTSC 40 IRE Mod                                           |                          | -    | 1.0  | -    | %     |

| Differential Phase Error                                   | DP               | Ramp, f <sub>C</sub> = 14.3MSPS                           |                          | -    | 1.0  | -    | deg   |

| Aperture Jitter                                            | t <sub>AJ</sub>  |                                                           |                          | -    | 40   | -    | ps    |

| Sampling Delay                                             | t <sub>SD</sub>  |                                                           |                          | -    | 4    | -    | ns    |

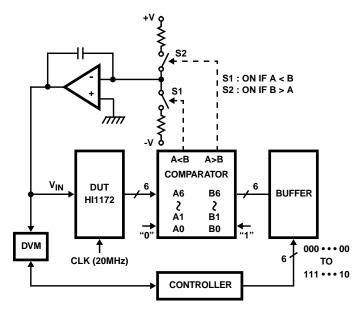

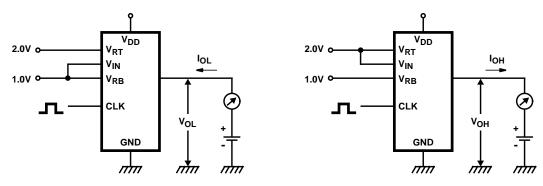

#### **Test Circuits**

FIGURE 1. INTEGRAL NON-LINEARITY ERROR, DIFFERENTIAL NON-LINEARITY, OFFSET VOLTAGE

FIGURE 2. MAXIMUM OPERATIONAL SPEED, DIFFERENTIAL GAIN ERROR, DIFFERENTIAL PHASE ERROR

FIGURE 3. DIGITAL OUTPUT CURRENT TEST CIRCUIT

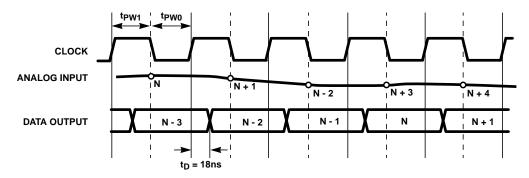

## **Timing Diagrams**

FIGURE 4. TIMING CHART 1

### Digital Output

Compatibility between analog input voltage and the digital output code is indicated in the chart below.

| INPUT SIGNAL    |      | DIGITAL OUTPUT CODE |         |   |   |   |     |

|-----------------|------|---------------------|---------|---|---|---|-----|

| VOLTAGE         | STEP | MSB                 |         |   |   |   | LSB |

| V <sub>RT</sub> | 0    | 1                   | 1 1 1 1 |   | 1 | 1 |     |

| •               | •    | •                   |         |   |   |   |     |

| •               | •    | •                   |         |   |   |   |     |

| •               | •    | •                   |         |   |   |   |     |

| •               | 31   | 1                   | 0       | 0 | 0 | 0 | 1   |

| •               | 32   | 0                   | 1       | 1 | 1 | 1 | 1   |

| •               | •    |                     |         | • | • |   |     |

| •               | •    |                     |         |   | • |   |     |

| •               | •    |                     |         |   | • |   |     |

| V <sub>RB</sub> | 63   | 0                   | 0       | 0 | 0 | 0 | 0   |

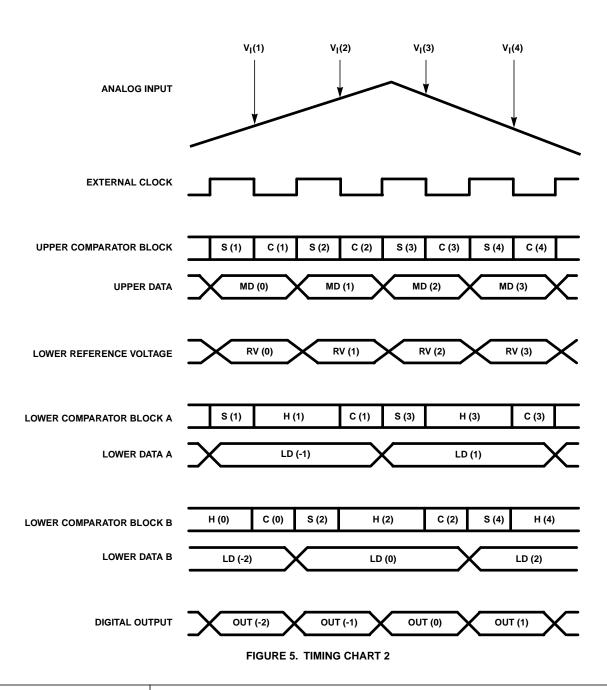

## **Operation** (See Block Diagram and Waveform)

The HI1172 is a 2-step parallel system A/D converter featuring a 3-bit upper comparators group and 2 lower comparators groups of 3-bit each. The reference voltage that is equal to the voltage between  $V_{RT}$ - $V_{RB}$ /8 is constantly applied to the upper 3-bit comparator block. Voltage that corresponded to the upper data is fed through the reference supply to the lower data.

This IC uses an offset cancel type comparator and operates synchronously with an external clock. It features the following operating modes which are respectively indicated on the timing chart with S, H, C symbols, i.e., input sampling (auto zero) mode, input hold mode and comparison mode.

The operation of respective parts is as indicated in the chart. Input voltage Vi (1) is sampled with the falling edge of the first clock by means of the upper comparator block and the lower comparator A block.

The upper comparators block finalizes comparison data MD (1) with the rising edge of the first clock. simultaneously the reference supply generates the lower reference voltage RV (1) that corresponded to the upper results. The lower comparator block finalizes comparison data LD (1) with the rising edge of the second clock. MD (1) and LD (1) are combined and output as Out (1) with the rising edge of the 3rd clock. Accordingly there is a 2.5 clock delay from the analog input sampling point to the digital data output.

### Notes On Operation

- V<sub>DD</sub>, V<sub>SS</sub> To reduce noise effects, separate the analog and digital systems close to the device. For both the digital and analog V<sub>DD</sub> pins, use a ceramic capacitor of about 0.1μF set as close as possible to the pin to bypass to the respective GNDs.

- Analog Input Compared with a flash type A/D converter, the input capacitance of the analog input is rather small. However it is necessary to drive with an amplifier featuring sufficient bandwidth and drive capability. When driving with an amplifier of low output impedance, parasitic oscillation may occur. That may be prevented by inserting a resistance of about  $100\Omega$  in series between the amplifier output and A/D input.

- Clock Input The clock line wiring should be as short as possible. Also, to avoid any interference with other signals, separate it from the other circuits.

- Reference Input Voltage between  $V_{RT}$  to  $V_{RB}$  is compatible with the dynamic range of the analog input. By bypassing  $V_{RT}$  and  $V_{RB}$  pins to GND with a capacitor of about  $0.1\mu F$ , stable characteristics are obtained.

- Timing Analog input is sampled with the falling edge of CLK and output as digital data with a delay of 2.5 clocks and with the following rising edge. The delay from the clock rising edge to the data output is about 18ns.

- About Latch Up It is necessary that AV<sub>DD</sub> and DV<sub>DD</sub> pins to be the common source of power supply. This is to avoid latch up due to the voltage difference between AV<sub>DD</sub> and DV<sub>DD</sub> pins when power is ON.

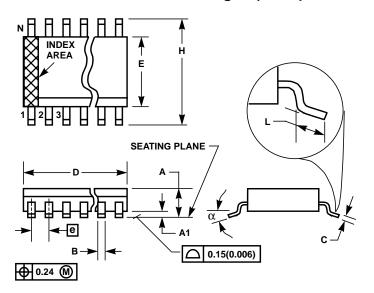

## Small Outline Plastic Packages (SOIC)

NOTES:

- 1. Dimension "D" does not include mold flash, protrusions or gate burrs.

- 2. Dimension "E" does not include interlead flash or protrusions.

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. "N" is the number of terminal positions.

- 5. Terminal numbers are shown for reference only.

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M16.2-S

16 LEAD SMALL OUTLINE PLASTIC PACKAGE (200 MIL)

|        | INCHES    |                 | MILLIM   |                 |       |

|--------|-----------|-----------------|----------|-----------------|-------|

| SYMBOL | MIN       | MAX             | MIN      | MAX             | NOTES |

| Α      | 0.067     | 0.078           | 1.70     | 2.00            | -     |

| A1     | 0.002     | 0.011           | 0.05     | 0.30            | -     |

| В      | 0.014     | 0.021           | 0.35     | 0.55            | -     |

| С      | 0.006     | 0.011           | 0.15     | 0.30            | -     |

| D      | 0.386     | 0.405           | 9.80     | 10.30           | 1     |

| Е      | 0.205     | 0.220           | 5.20     | 5.60            | 2     |

| е      | 0.050 BSC |                 | 1.27 BSC |                 | -     |

| Н      | 0.296     | 0.326           | 7.50     | 8.3             | -     |

| L      | 0.012     | 0.027           | 0.30     | 0.70            | 3     |

| N      | 16        |                 | 1        | 6               | 4     |

| α      | 0°        | 10 <sup>0</sup> | 0°       | 10 <sup>0</sup> | -     |

Rev. 0 2/96

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902

TEL: (321) 724-7000 FAX: (321) 724-7240 **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium

TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

ASIA

Intersil Ltd. 8F-2, 96, Sec. 1, Chien-kuo North,

Taipei, Taiwan 104 Republic of China TEL: 886-2-2515-8508 FAX: 886-2-2515-8369