Data Sheet January 1999 File Number 4114.2

# 8-Bit, 40MSPS, 2-Channel D/A Converter

The HI1177 is a dual 8-bit CMOS digital-to-analog converter. It has input/output equivalent to 2 channels of Y and C for video use or I and Q for modulators.

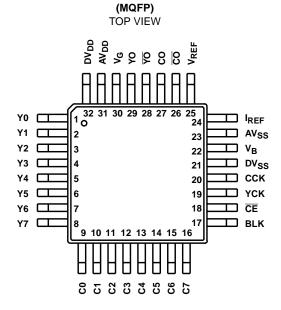

The HI1177 is available in the industrial temperature range and is supplied in a 32 lead plastic metric quad flatpack (MQFP) package.

# **Ordering Information**

| PART<br>NUMBER |           |            | PKG. NO.  |  |

|----------------|-----------|------------|-----------|--|

| HI1177JCQ      | -40 to 85 | 32 Ld MQFP | Q32.7x7-S |  |

HI1177

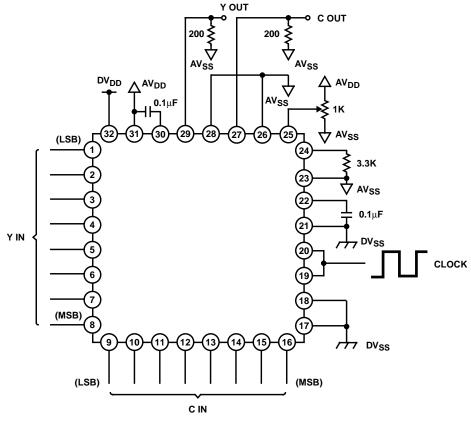

#### **Pinout**

#### **Features**

| • Resolution                   |

|--------------------------------|

| Maximum Conversion Speed 40MHz |

| YC 2-Channel Input/Output      |

| Differential Linearity Error.  |

| Low Power Consumption          |

| Power Supply +5V Single        |

| Power-Down Mode                |

| Low Glitch Noise               |

## **Applications**

• Direct Replacement for Sony CXD1177

- I/Q Modulation

- YC Video

- · Digital TV

- · Wireless Transmitters

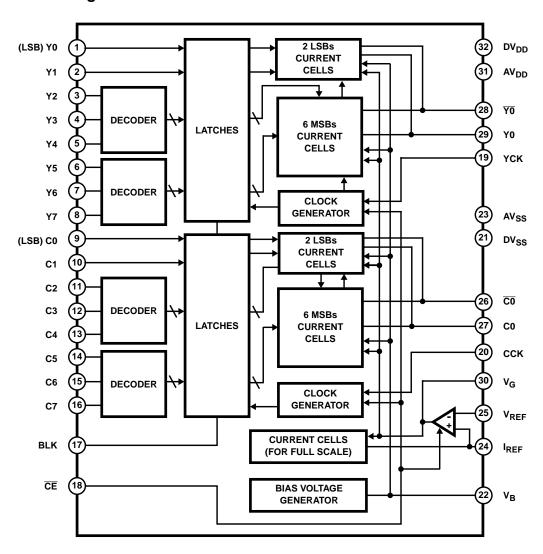

# Functional Block Diagram

# Pin Descriptions

| NUMBER  | SYMBOL   | EQUIVALENT CIRCUIT  | DESCRIPTION                                                          |  |  |

|---------|----------|---------------------|----------------------------------------------------------------------|--|--|

| 1 to 8  | Y0 to Y7 | o DV <sub>DD</sub>  | Digital Input.                                                       |  |  |

| 9 to 16 | C0 to C7 | 16 DV <sub>SS</sub> |                                                                      |  |  |

| 17      | BLK      | 17 DV <sub>DD</sub> | Blanking Pin. No signal at "H" (Output 0V). Output condition at "L". |  |  |

# Pin Descriptions (Continued)

| NUMBER | SYMBOL           | EQUIVALENT CIRCUIT                                                                   | DESCRIPTION                                                                    |  |  |

|--------|------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| 22     | V <sub>B</sub>   | DV <sub>DD</sub> DV <sub>DD</sub> DV <sub>DD</sub> DV <sub>DD</sub> DV <sub>DD</sub> | Connect a capacitor of about 0.1μF.                                            |  |  |

| 19     | YCK              | o DV <sub>DD</sub>                                                                   | Clock Pin. Moreover all input pins are                                         |  |  |

| 20     | CLK              | 10 DV <sub>SS</sub>                                                                  | TTL-CMOS compatible.                                                           |  |  |

| 21     | DV <sub>SS</sub> |                                                                                      | Digital GND.                                                                   |  |  |

| 23     | AV <sub>SS</sub> |                                                                                      | Analog GND.                                                                    |  |  |

| 18     | CE               | (B) DV <sub>DD</sub> DV <sub>SS</sub>                                                | Chip Enable Pin. No signal (Output 0V) at "H" and minimizes power consumption. |  |  |

| 24     | I <sub>REF</sub> | AV <sub>DD</sub> o AV <sub>DD</sub>                                                  | Connect a resistance 16 times "16R" that of output resistance value "R".       |  |  |

| 25     | V <sub>REF</sub> |                                                                                      | Set full scale output value.                                                   |  |  |

| 30     | V <sub>G</sub>   | AV <sub>DD</sub> Q <sup>(24)</sup>                                                   | Connect a capacitor of about 0.1µF.                                            |  |  |

| 31     | AV <sub>DD</sub> | 25 AV <sub>SS</sub> 30 AV <sub>SS</sub>                                              | Analog V <sub>DD</sub> .                                                       |  |  |

| 27     | СО               | AV <sub>DD</sub> Ŷ 1                                                                 | Current Output Pin. Voltage output can be                                      |  |  |

| 29     | YO               |                                                                                      | obtained by connecting a resistance.                                           |  |  |

| 26     | CO               |                                                                                      | Inverted Current Output Pin. Normally                                          |  |  |

| 28     | ΫO               | 29<br>AV <sub>SS</sub><br>AV <sub>DD</sub><br>AV <sub>SS</sub>                       | dropped to analog GND.                                                         |  |  |

| 32     | DV <sub>DD</sub> |                                                                                      | Digital V <sub>DD</sub> .                                                      |  |  |

## **Absolute Maximum Ratings** $T_A = 25^{\circ}C$

| Supply Voltage, V <sub>DD</sub>          |                                    |

|------------------------------------------|------------------------------------|

| Input Voltage, V <sub>IN</sub>           | V <sub>DD</sub> to V <sub>SS</sub> |

| Output Current (For Each Channel), IOLIT | . 0mA to 15mA                      |

#### **Operating Conditions**

| Supply Voltage                                     |

|----------------------------------------------------|

| AV <sub>DD</sub> , AV <sub>SS</sub> 4.75V to 5.25V |

| DV <sub>DD</sub> , DV <sub>SS</sub> 4.75V to 5.25V |

| Reference Input Voltage, V <sub>REF</sub>          |

| Clock Pulse Width                                  |

| t <sub>PW1</sub>                                   |

| t <sub>PW0</sub> 12.5ns (Min)                      |

| Temperature Range, T <sub>OPR</sub> 40°C to 85°C   |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 7)           | $\theta_{JA}$ (°C/W)                   |

|------------------------------------------------|----------------------------------------|

| MQFP Package                                   | 122                                    |

| Maximum Junction Temperature (Plastic Package) | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range65            | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                                  |

| (MQFP - Lead Tips Only)                        |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $f_{CLK} = 40 MHz$ , $V_{DD} = 5 V$ , $R_{OUT} = 200 \Omega$ , $V_{REF} = 2.0 V$ , $T_A = 25 ^{\circ} C$

| PARAI                     | METER       | SYMBOL           | TEST CONDITIONS                  | TEST<br>LEVEL<br>OR NOTES | MIN  | TYP | MAX | UNITS |

|---------------------------|-------------|------------------|----------------------------------|---------------------------|------|-----|-----|-------|

| Resolution                |             | n                |                                  |                           | -    | 8   | -   | bit   |

| Maximum Conve             | rsion Speed | f <sub>MAX</sub> |                                  |                           | 40   | -   | -   | MHz   |

| Linearity Error           |             | EL               |                                  |                           | -2.5 | -   | 2.5 | LSB   |

| Differential Linea        | rity Error  | E <sub>D</sub>   |                                  |                           | -0.3 | -   | 0.3 | LSB   |

| Full Scale Output Voltage |             | V <sub>FS</sub>  |                                  |                           | 1.9  | 2.0 | 2.2 | V     |

| Full Scale Outpu          | t Ratio     | F <sub>SR</sub>  |                                  | Note 1                    | 0    | 1.5 | 3   | %     |

| Full Scale Outpu          | t Current   | I <sub>FS</sub>  |                                  |                           | -    | 10  | 15  | mA    |

| Offset Output Voltage     |             | Vos              |                                  |                           | -    | -   | 1   | mV    |

| Power Supply Current      |             | I <sub>DD</sub>  | 14.3MHz, at Color Bar Data Input |                           | -    | -   | 32  | mA    |

| Digital Input             | High Level  | lн               |                                  |                           | -    | -   | 5   | μΑ    |

| Current                   | Low Level   | I <sub>IL</sub>  |                                  |                           | -5   | -   | -   | μΑ    |

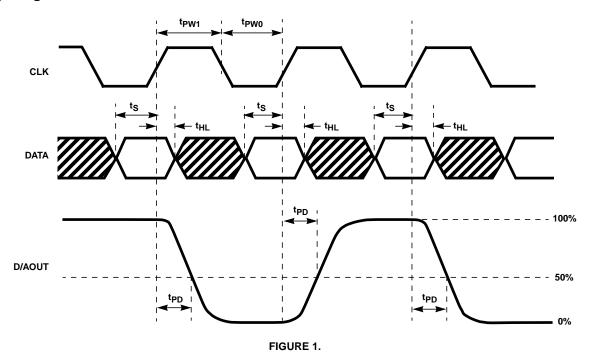

| Setup Time                |             | t <sub>S</sub>   |                                  |                           | 5    | -   | -   | ns    |

| Hold Time                 |             | t <sub>H</sub>   |                                  |                           | 10   | -   | -   | ns    |

| Propagation Delay Time    |             | t <sub>PD</sub>  |                                  |                           | -    | 10  | -   | ns    |

| Glitch Energy             |             | GE               | $R_{OUT} = 75\Omega$             |                           | -    | 30  | -   | pV-s  |

| Cross Talk                |             | CT               | 1MHz Sin Wave Output             |                           | -    | 57  | -   | dB    |

#### NOTE:

1. Full scale output ratio =  $\frac{\text{Full-scale voltage of channel}}{\text{Average of the full-scale voltage of the channels}} (-1) x 100 (%) .$

# I/O Correspondence Table (Output Full Scale Voltage: 2V)

|     |   | IN | PUT | CO | DE  | OUTPUT VOLTAGE |   |       |

|-----|---|----|-----|----|-----|----------------|---|-------|

| MSB |   |    |     |    | LSB |                |   |       |

| 1   | 1 | 1  | 1   | 1  | 1   | 1              | 1 | 2.0V  |

|     |   |    |     | •  |     |                |   |       |

|     |   |    | •   | •  |     |                |   |       |

|     | ^ | ^  | ,   | •  | ^   | ^              | ^ | 4.0)/ |

| 1   | 0 | 0  | 0   | U  | 0   | 0              | 0 | 1.0V  |

|     |   |    |     | •  |     |                |   |       |

|     |   |    | ·   | •  |     |                |   |       |

| 0   | 0 | 0  | 0   | 0  | 0   | 0              | 0 | 0V    |

# Timing Diagram

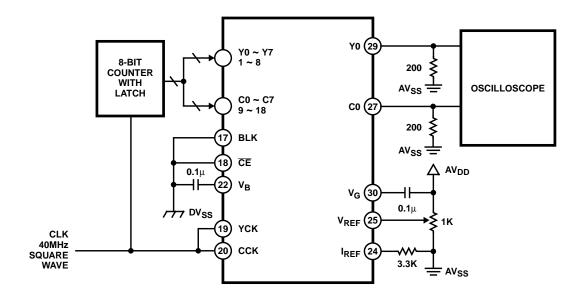

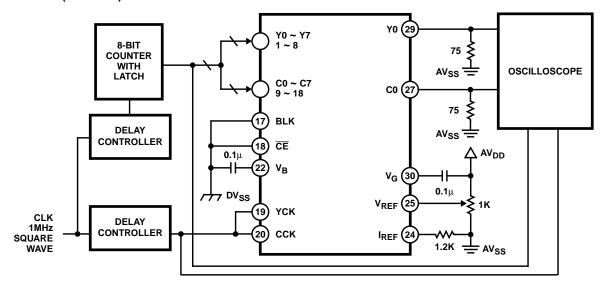

# **Test Circuits**

FIGURE 2. MAXIMUM CONVERSION

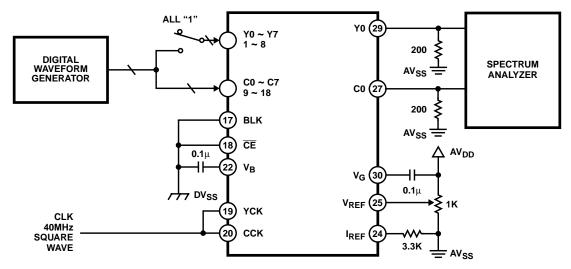

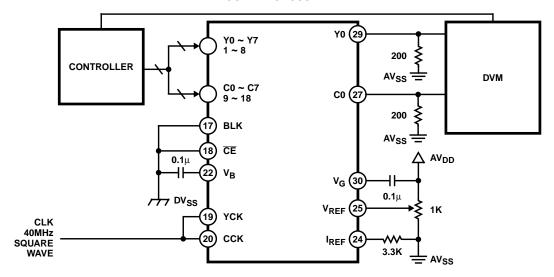

## Test Circuits (Continued)

FIGURE 3. SETUP HOLD TIME AND GLITCH ENERGY

FIGURE 4. CROSSTALK

FIGURE 5. DC CHARACTERISTICS

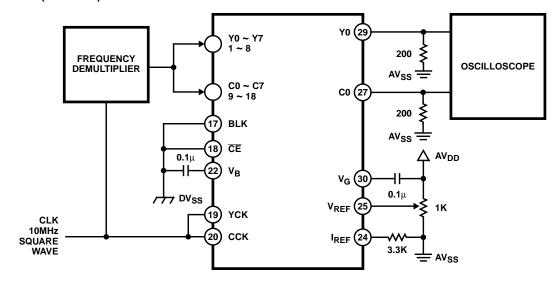

# Test Circuits (Continued)

FIGURE 6. PROPAGATION DELAY TIME

# **Typical Performance Curves**

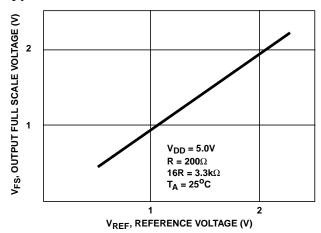

FIGURE 7. OUTPUT FULL SCALE VOLTAGE vs REFERENCE VOLTAGE

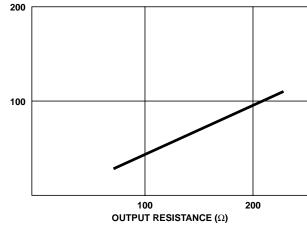

FIGURE 8. GLITCH ENERGY vs OUTPUT RESISTANCE

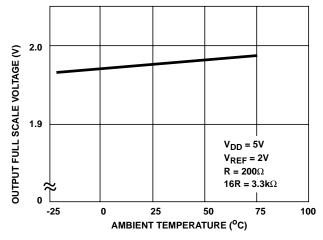

FIGURE 9. OUTPUT FULL SCALE VOLTAGE vs AMBIENT TEMPERATURE

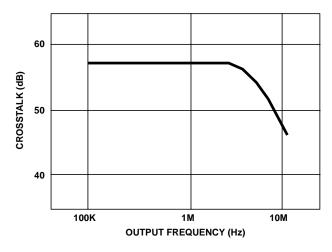

FIGURE 10. CROSSTALK vs OUTPUT FREQUENCY

## **Application Circuit**

FIGURE 11.

## Operation

- · How to select the output resistance:

- The HI1177 is a D/A converter of the current output type.

To obtain the output voltage connect the resistance to IO pin (Y0, C0). For specifications we have:

Output full scale voltage  $V_{FS}$  = less than 2V Output full scale current  $I_{FS}$  = less than 15mA

- Calculate the output resistance value from the relation of  $V_{FS} = I_{FS} \ X \ R$ . Also, 16 times resistance of the output resistance is connected to reference current pin  $I_{REF}$ . In some cases, however, this turns out to be a value that does not actually exist. In such a case a value close to it can be used as a substitute. Here please note that  $V_{FS}$  becomes  $V_{FS} = V_{REF} \ X \ 16R/R'$ . R is the resistance connected to IO while R' is connected to  $I_{REF}$ . Increasing the resistance value can curb power consumption. On the other hand glitch energy and data settling time will inversely increase. Set the most suitable value according to the desired application.

- · Phase relation between data and clock:

- To obtain the expected performance as a D/A converter, it is necessary to set properly the phase relation between data and clock applied from the exterior. Be sure to satisfy the provisions of the set up time (t<sub>S</sub>) and hold time (t<sub>H</sub>) as stipulated in the Electrical Characteristics.

- V<sub>DD</sub>, V<sub>SS</sub>:

- To reduce noise effects separate analog and digital systems in the device periphery. For  $V_{DD}$  pins, both digital and analog, bypass respective GNDs by using a ceramic capacitor of about  $0.1\mu F$ , as close as possible to the pin.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com