Data Sheet June 1999 FN3147.2

## 8-Channel/Differential 4-Channel, CMOS High Speed Analog Multiplexer

The HI-518 is a monolithic, dielectrically isolated, high speed, high performance CMOS analog multiplexer. It offers unique built-in channel selection decoding plus an inhibit input for disabling all channels. The dual function of address input A2 enables the HI-518 to be user programmed either as a single ended 8-Channel multiplexer by connecting 'Out A' to 'Out B' and using A2 as a digital address input, or as a 4-Channel differential multiplexer by connecting A2 to the Vsupply. The substrate leakages and parasitic capacitances are reduced substantially by using the Intersil Dielectric Isolation process to achieve optimum performance in both high and low level signal applications. The low output leakage current (I<sub>D(OFF)</sub> < 100pA at 25<sup>o</sup>C) and fast settling (t<sub>SETTLE</sub> = 800ns to 0.01%) characteristics of the device make it an ideal choice for high speed data acquisition systems, precision instrumentation, and industrial process control.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE      | PKG.<br>NO. |

|-------------|---------------------|--------------|-------------|

| HI3-0518-5  | 0 to 75             | 18 Ld PDIP   | E18.3       |

| HI1-0518-5  | 0 to 75             | 18 Ld CERDIP | F18.3       |

| HI1-0518-8  | -55 to 125          | 18 Ld CERDIP | F18.3       |

#### **Features**

| Access Time (Typical)                         |

|-----------------------------------------------|

| • Settling Time                               |

| Low Leakage (Typical)                         |

| - I <sub>S(OFF)</sub>                         |

| - I <sub>D(OFF)</sub>                         |

| Low Capacitance (Max)                         |

| - C <sub>S(OFF)</sub> 5pF                     |

| - C <sub>D(OFF)</sub>                         |

| Off Isolation at 500kHz                       |

| Low Charge Injection Error                    |

| Single Ended to Differential Selectable (SDS) |

| Logic Level Selectable (LLS)                  |

## **Applications**

- Data Acquisition Systems

- · Precision Instrumentation

- Industrial Control

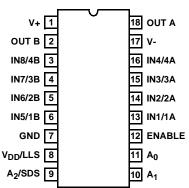

#### **Pinout**

#### HI-518 (CERDIP, PDIP) TOP VIEW

### **Truth Tables**

TABLE 1. HI-518 USED AS AN 8-CHANNEL MULTIPLEXER OR DUAL 4-CHANNEL MULTIPLEXER (NOTE 1)

| USE A <sub>2</sub> AS I | DIGITAL A      | ON CHA         | NNEL TO        |             |      |  |

|-------------------------|----------------|----------------|----------------|-------------|------|--|

| ENABLE                  | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | OUT A OUT E |      |  |

| L                       | Х              | Х              | Х              | None        | None |  |

| Н                       | L              | L              | L              | 1A          | None |  |

| Н                       | L              | L              | Н              | 2A          | None |  |

| Н                       | L              | Н              | L              | 3A          | None |  |

| Н                       | L              | Н              | Н              | 4A          | None |  |

| Н                       | Н              | L              | L              | None        | 1B   |  |

| Н                       | Н              | L              | Н              | None        | 2B   |  |

| Н                       | Н              | Н              | L              | None        | 3B   |  |

| Н                       | Н              | Н              | Н              | None        | 4B   |  |

|     | _      | _ | _ |   |

|-----|--------|---|---|---|

| NI  | 1      |   | ᄂ | • |

| 1 4 | $\sim$ |   | ᆫ |   |

For 8-Channel single ended function, tie "Out A" to "Out B"; for dual 4-Channel function, use the A<sub>2</sub> address pin to select between Mux A and Mux B, where Mux A is selected with A<sub>2</sub> low.

# TABLE 2. HI-518 USED AS A DIFFERENTIAL 4-CHANNEL MULTIPLEXER

| A <sub>2</sub> CONNECTE | D TO V- S      | ON CHANNEL TO  |       |       |

|-------------------------|----------------|----------------|-------|-------|

| ENABLE                  | A <sub>1</sub> | A <sub>0</sub> | OUT A | OUT B |

| L                       | Х              | Х              | None  | None  |

| Н                       | L              | L              | 1A    | 1B    |

| Н                       | L              | Н              | 2A    | 2B    |

| Н                       | Н              | L              | 3A    | 3B    |

| Н                       | Н              | Н              | 4A    | 4B    |

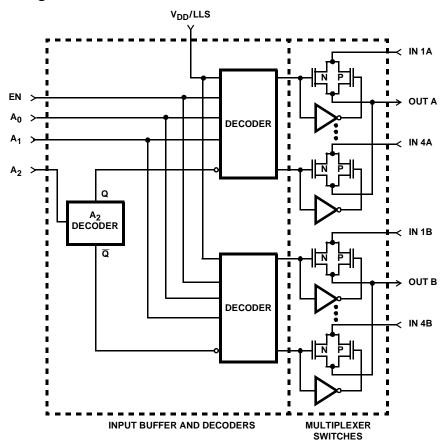

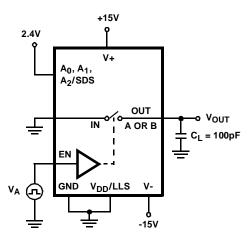

## Functional Block Diagram

| A <sub>2</sub> DECODE |   |   |  |  |  |  |  |

|-----------------------|---|---|--|--|--|--|--|

| A <sub>2</sub>        | Q | Q |  |  |  |  |  |

| Н                     | Н | L |  |  |  |  |  |

| L                     | L | Н |  |  |  |  |  |

| V-                    | L | L |  |  |  |  |  |

#### **Absolute Maximum Ratings**

| V+ to V                                                            |

|--------------------------------------------------------------------|

| Analog (V <sub>IN</sub> , V <sub>OUT</sub> ) (V-) -2V to (V+) +2V  |

| Digital Input Voltage:                                             |

| TTL Levels Selected (V <sub>DD</sub> /LLS Pin = GND or Open)       |

| V <sub>A0-1</sub> 6V to +6V                                        |

| V <sub>A2/SDS</sub> (V-) -2V to (V+) +2V                           |

| CMOS Levels Selected (V <sub>DD</sub> /LLS Pin = V <sub>DD</sub> ) |

| V <sub>A0-2</sub> 2V to (V+) +2V                                   |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2) $\theta_J$ | A (OC/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W) |

|-------------------------------------------------|----------|-------------------------------------|

| PDIP Package                                    | 90       | N/A                                 |

| CERDIP Package                                  |          | 18                                  |

| Maximum Junction Temperature                    |          |                                     |

| Ceramic Package                                 |          | 175 <sup>0</sup> C                  |

| Plastic Package                                 |          |                                     |

| Maximum Storage Temperature Range               |          | 65°C to 150°C                       |

| Maximum Lead Temperature (Soldering 10s         |          |                                     |

## **Operating Conditions**

| Temperature Ranges |                |

|--------------------|----------------|

| HI-518-8           | -55°C to 125°C |

| HI-518-5           | 0°C to 75°C    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

2.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

|                                                   | TEST       | TEMP |                    | -8    |                    |                    | -5    |                    |       |

|---------------------------------------------------|------------|------|--------------------|-------|--------------------|--------------------|-------|--------------------|-------|

| PARAMETER                                         | CONDITIONS | (°C) | MIN                | TYP   | MAX                | MIN                | TYP   | MAX                | UNITS |

| DYNAMIC CHARACTERISTICS                           |            |      | •                  |       |                    |                    |       |                    | •     |

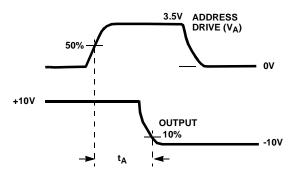

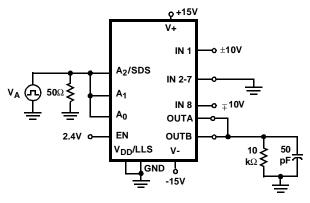

| Access Time, t <sub>A</sub>                       |            | 25   | -                  | 130   | 175                | -                  | 130   | 175                | ns    |

|                                                   |            | Full | -                  | -     | 225                | -                  | -     | 225                | ns    |

| Break-Before-Make Delay, t <sub>OPEN</sub>        |            | 25   | 10                 | 20    | -                  | 10                 | 20    | -                  | ns    |

| Enable Delay (ON), t <sub>ON(EN)</sub>            |            | 25   | -                  | 120   | 175                |                    | 120   | 175                | ns    |

| Enable Delay (OFF), t <sub>OFF(EN)</sub>          |            | 25   | -                  | 140   | 175                |                    | 140   | 175                | ns    |

| Settling Time                                     | To 0.1%    | 25   | -                  | 250   | -                  | -                  | 250   | -                  | ns    |

|                                                   | To 0.01%   | 25   | -                  | 800   | -                  | -                  | 800   | -                  | ns    |

| Charge Injection Error                            | Note 6     | 25   | -                  | -     | 25                 | -                  | -     | 25                 | mV    |

| Off Isolation                                     | Note 7     | 25   | 45                 | -     | -                  | 45                 | -     | -                  | dB    |

| Channel Input Capacitance, C <sub>S(OFF)</sub>    |            | 25   | -                  | -     | 5                  | -                  | -     | 5                  | pF    |

| Channel Output Capacitance, C <sub>D(OFF)</sub>   |            | 25   | -                  | -     | 10                 | -                  | -     | 10                 | pF    |

| Digital Input Capacitance, CA                     |            | 25   | -                  | -     | 5                  | -                  | -     | 5                  | pF    |

| Input to Output Capacitance, C <sub>DS(OFF)</sub> |            | 25   | -                  | 0.02  | -                  | -                  | 0.02  | -                  | pF    |

| DIGITAL INPUT CHARACTERISTICS                     |            |      |                    |       | 1                  |                    |       |                    |       |

| Input Low Threshold, V <sub>AL</sub> (TTL)        | Note 3     | Full | -                  | -     | 0.8                | -                  | -     | 0.8                | V     |

| Input High Threshold, V <sub>AH</sub> (TTL)       | Note 3     | Full | 2.4                | -     | -                  | 2.4                | -     | -                  | V     |

| Input Low Threshold, V <sub>AL</sub> (CMOS)       | Note 3     | Full | -                  | -     | 0.3V <sub>DD</sub> | -                  | -     | 0.3V <sub>DD</sub> | V     |

| Input High Threshold, V <sub>AH</sub> (CMOS)      | Note 3     | Full | 0.7V <sub>DD</sub> | -     | -                  | 0.7V <sub>DD</sub> | -     | -                  | V     |

| Input Leakage Current, I <sub>AH</sub> (High)     |            | Full | -                  | -     | 1                  | -                  | -     | 1                  | μΑ    |

| Input Leakage Current, I <sub>AL</sub> (Low)      |            | Full | -                  | -     | 20                 | -                  | -     | 20                 | μΑ    |

| ANALOG CHANNEL CHARACTERISTIC                     | S          |      |                    |       |                    |                    |       |                    |       |

| Analog Signal Range, V <sub>IN</sub>              | Note 4     | Full | -14                | -     | +14                | -15                | -     | +15                | V     |

| On Resistance, r <sub>ON</sub>                    | Note 5     | 25   | -                  | 480   | 750                | -                  | 480   | 750                | Ω     |

|                                                   |            | Full | -                  | -     | 1,000              | -                  | -     | 1,000              | Ω     |

| Off Input Leakage Current, I <sub>S(OFF)</sub>    |            | 25   | -                  | 0.01  | -                  | -                  | 0.01  | -                  | nA    |

|                                                   |            | Full | -                  | -     | 50                 | -                  | -     | 50                 | nA    |

| Off Output Leakage Current, I <sub>D(OFF)</sub>   |            | 25   | -                  | 0.015 | -                  | -                  | 0.015 | -                  | nA    |

|                                                   |            | Full | -                  | -     | 50                 | -                  | -     | 50                 | nA    |

| On Channel Leakage Current, I <sub>D(ON)</sub>    |            | 25   | -                  | 0.015 | -                  | -                  | 0.015 | -                  | nA    |

| - D(ON)                                           |            | Full | -                  | -     | 50                 | -                  | -     | 50                 | nA    |

| POWER SUPPLY CHARACTERISTICS                      |            |      |                    |       |                    |                    |       |                    |       |

| Power Dissipation, PD                             |            | Full | -                  | -     | 450                | -                  | -     | 540                | mW    |

#### **Electrical Specifications**

Supplies = +15V, -15V;  $V_{AH}$  (Logic Level High) = 2.4V,  $V_{AL}$  (Logic Level Low) = 0.8V;  $V_{DD}/LLS$  = GND (Note 3), Unless Otherwise Specified (Continued)

|             | TEST                   | TEMP |     | -8  |     |     | -5  |     |       |

|-------------|------------------------|------|-----|-----|-----|-----|-----|-----|-------|

| PARAMETER   | CONDITIONS             | (°C) | MIN | TYP | MAX | MIN | TYP | MAX | UNITS |

| I+, Current | V <sub>EN</sub> = 2.4V | Full | -   | -   | 15  | -   | -   | 18  | mA    |

| I-, Current |                        | Full | -   | -   | 15  | -   | -   | 18  | mA    |

#### NOTES:

- 3.  $V_{DD}/LLS$  pin = open or grounded for TTL compatibility.  $V_{DD}/LLS$  pin =  $V_{DD}$  for CMOS compatibility.

- 4. At temperatures above  $90^{\circ}$ C, care must be taken to assure  $V_{IN}$  remains at least 1.0V below the  $V_{SUPPLY}$  for proper operation.

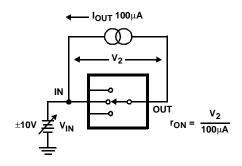

- 5.  $V_{IN} = \pm 10V$ ,  $I_{OUT} = -100\mu A$ .

- 6.  $V_{IN} = 0V$ ,  $C_L = 100pF$ , enable input pulse = 3V, f = 500kHz.

- 7. C<sub>L</sub> = 40pF, R<sub>L</sub> = 1K, V<sub>EN</sub> = 0.8V, V<sub>IN</sub> = 3V<sub>RMS</sub>, f = 500kHz. Due to the pin to pin capacitance between IN 8/4B and OUT B, channel 8/4B exhibits 60dB of OFF isolation under the above test conditions.

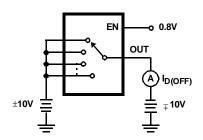

### Test Circuits and Waveforms V<sub>DD</sub>/LLS = GND, Unless Otherwise Specified

FIGURE 1. ON RESISTANCE TEST CIRCUIT

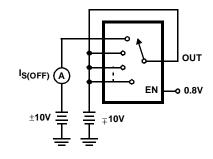

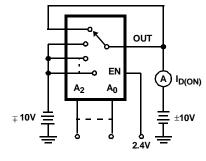

FIGURE 2. ID(OFF) TEST CIRCUIT (NOTE 8)

FIGURE 3. I<sub>S(OFF)</sub> TEST CIRCUIT (NOTE 8)

FIGURE 4. I<sub>D(ON)</sub> TEST CIRCUIT (NOTE 8)

FIGURE 5A. MEASUREMENT POINTS

FIGURE 5B. TEST CIRCUIT

#### FIGURE 5. ACCESS TIME

#### NOTE:

8. Two measurements per channel: ±10V and ∓10V. (Two measurements per device for I<sub>D(OFF)</sub> ±10V and ∓10V.)

## $\textbf{\textit{Test Circuits and Waveforms}} \ \ V_{DD}/LLS = GND, \ Unless \ Otherwise \ Specified \ \ \textbf{(Continued)}$

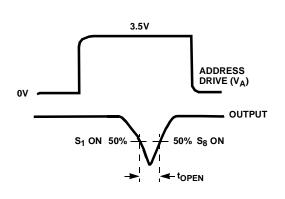

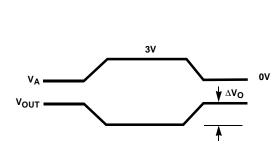

FIGURE 6A. MEASUREMENT POINTS

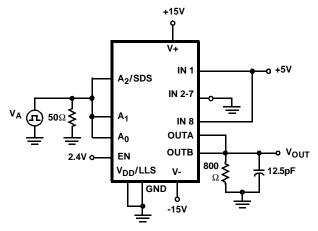

FIGURE 6B. TEST CIRCUIT

FIGURE 6. BREAK-BEFORE-MAKE DELAY

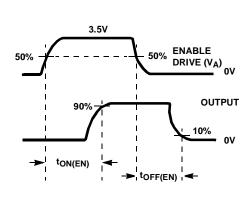

FIGURE 7A. MEASUREMENT POINTS

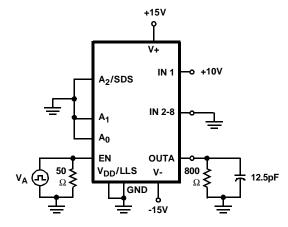

FIGURE 7B. TEST CIRCUIT

FIGURE 7. ENABLE DELAY

FIGURE 8A. MEASUREMENT POINTS

FIGURE 8B. TEST CIRCUIT

$\Delta V_O$  is the measured voltage error due to charge injection. The error in coulombs is Q =  $C_L \ x \ \Delta V_O$ .

FIGURE 8. CHARGE INJECTION

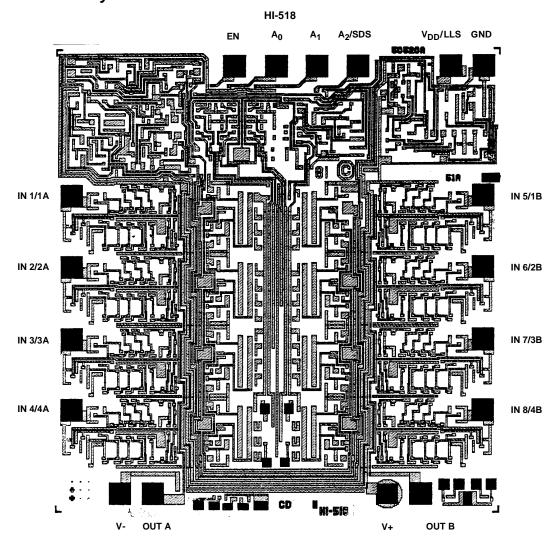

#### Die Characteristics

**DIE DIMENSIONS:**

89 mils x 93 mils

**METALLIZATION:**

Type: AlCu

Thickness: 16kÅ ±2kÅ

**SUBSTRATE POTENTIAL (NOTE):**

-V<sub>SUPPLY</sub>

**PASSIVATION:**

Type: Nitride Over Silox

Nitride Thickness: 3.5kÅ ±1.0kÅ Silox Thickness: 12kÅ ±2.0kÅ

**WORST CASE CURRENT DENSITY:**

$1.43 \times 10^5 \text{ A/cm}^2$

TRANSISTOR COUNT:

356

**PROCESS:**

CMOS-DI

NOTE: The substrate appears resistive to the -V<sub>SUPPLY</sub> terminal, therefore it may be left floating (Insulating Die Mount) or it may be mounted on a conductor at -V<sub>SUPPLY</sub> potential.

### Metallization Mask Layout

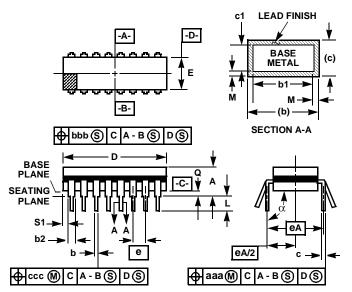

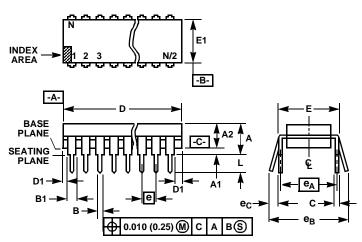

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

#### NOTES:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

F18.3 MIL-STD-1835 GDIP1-T18 (D-6, CONFIGURATION A)

18 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INC   | HES              | MILLIM          |                  |       |

|--------|-------|------------------|-----------------|------------------|-------|

| SYMBOL | MIN   | MAX              | MIN             | MAX              | NOTES |

| Α      | -     | 0.200            | -               | 5.08             | -     |

| b      | 0.014 | 0.026            | 0.36            | 0.66             | 2     |

| b1     | 0.014 | 0.023            | 0.36            | 0.58             | 3     |

| b2     | 0.045 | 0.065            | 1.14            | 1.65             | -     |

| b3     | 0.023 | 0.045            | 0.58            | 1.14             | 4     |

| С      | 0.008 | 0.018            | 0.20            | 0.46             | 2     |

| c1     | 0.008 | 0.015            | 0.20            | 0.38             | 3     |

| D      | -     | 0.960            | -               | 24.38            | 5     |

| Е      | 0.220 | 0.310            | 5.59            | 7.87             | 5     |

| е      | 0.100 | BSC              | 2.54            | BSC              | -     |

| eA     | 0.300 | BSC              | 7.62 BSC        |                  | -     |

| eA/2   | 0.150 | BSC              | 3.81            | BSC              | -     |

| L      | 0.125 | 0.200            | 3.18            | 5.08             | -     |

| Q      | 0.015 | 0.070            | 0.38            | 1.78             | 6     |

| S1     | 0.005 | -                | 0.13            | -                | 7     |

| α      | 90°   | 105 <sup>0</sup> | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |

| aaa    | -     | 0.015            | -               | 0.38             | -     |

| bbb    | -     | 0.030            | -               | 0.76             | -     |

| ccc    | -     | 0.010            | -               | 0.25             | -     |

| М      | -     | 0.0015           | -               | 0.038            | 2, 3  |

| N      | 1     | 8                | 18              |                  | 8     |

Rev. 0 4/94

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and eA are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E18.3 (JEDEC MS-001-BC ISSUE D)

18 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α              | -         | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.115     | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045     | 0.070 | 1.15        | 1.77  | 8, 10 |

| С              | 0.008     | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.845     | 0.880 | 21.47       | 22.35 | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| Е              | 0.300     | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240     | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.300 BSC |       | 7.62 BSC    |       | 6     |

| e <sub>B</sub> | -         | 0.430 | -           | 10.92 | 7     |

| L              | 0.115     | 0.150 | 2.93        | 3.81  | 4     |

| N              | 18        |       | 18          |       | 9     |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## Sales Office Headquarters

**NORTH AMERICA**

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618

TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 **EUROPE**

Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland

TEL: +41 21 6140560 FAX: +41 21 6140579 ASIA

Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road

TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433