Data Sheet January 1999 File Number 2936.4

# Microprocessor-Compatible, 5-1/2 Digit A/D Converter

The Intersil HI-7159A is a monolithic A/D converter that uses a unique dual slope technique which allows it to resolve input changes as small as 1 part in 200,000 (10µV) without the use of critical external components. Its digital autozeroing feature virtually eliminates zero drift over temperature. The device is fabricated in Intersil' proprietary low noise BiMOS process, resulting in exceptional linearity and noise performance. The HI-7159A's resolution can be switched between a high resolution 200,000 count (5<sup>1</sup>/<sub>2</sub> digit) mode, and a high speed 20,000 count  $(4^{1}/_{2})$  digit) mode without any hardware modifications. In the  $4^{1}/_{2}$  digit uncompensated mode, speeds of 60 conversions per second can be achieved. The HI-7159A is designed to be easily interfaced with most microprocessors through either of its three serial and one parallel interface modes. In the serial modes, any one of four common baud rates is available.

# Ordering Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|-------------|---------------------|------------|-------------|

| HI3-7159A-5 | 0 to 70             | 28 Ld PDIP | E28.6       |

### Features

- ±200,000 Count A/D Converter

- 2V Full Scale Reading With 10μV Resolution

- 15 Conversions Per Second in 5<sup>1</sup>/<sub>2</sub> Digit Mode

- 60 Conversions Per Second in 4<sup>1</sup>/<sub>2</sub> Digit Mode

- Serial or Parallel Interface Modes

- · Four Selectable Baud Rates

- · Differential Analog Input

- Differential Reference Input

- · Digital Autozero

# **Applications**

- · Weigh Scales

- Part Counting Scales

- · Laboratory Instruments

- Process Control/Monitoring

- · Energy Management

- Seismic Monitoring

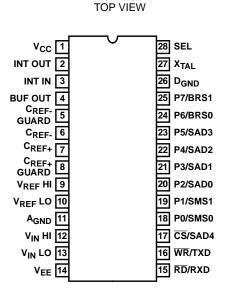

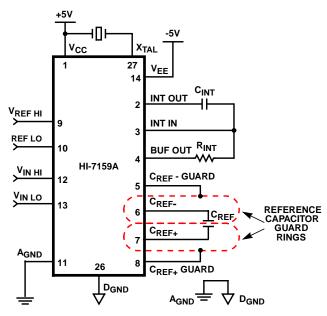

### Pinout

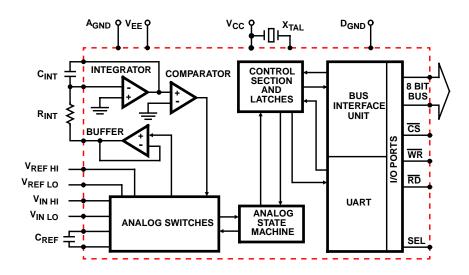

# Functional Block Diagram

HI-7159A (PDIP)

### **Absolute Maximum Ratings**

### **Thermal Information**

| Supply Voltage                                                    |                            |

|-------------------------------------------------------------------|----------------------------|

| V <sub>CC</sub> to GND (A <sub>GND</sub> /D <sub>GND</sub> )0.3   | √ < V <sub>CC</sub> < +6V  |

| V <sub>EE</sub> to GND (A <sub>GND</sub> /D <sub>GND</sub> ) +0.3 | V < V <sub>CC</sub> < -6V  |

| Digital Pins, (pins 15 - 28) D <sub>GND</sub> -0.3V < V           | $_{D}$ < $V_{CC}$ +0.3 $V$ |

| Analog Pins, (pins 2 - 13)V <sub>EE</sub> -0.3V < V               | $A < V_{CC} + 0.3V$        |

| Thermal Resistance (Typical, Note 1)          | θ <sub>JA</sub> (°C/W) |

|-----------------------------------------------|------------------------|

| PDIP Package                                  | 50                     |

| Maximum Junction Temperature                  | 150 <sup>0</sup> C     |

| Maximum Storage Temperature, T <sub>STG</sub> | -65°C to 150°C         |

| Maximum Lead Temperature (Soldering 10s)      |                        |

### **Operating Conditions**

Temperature Range . . . . . . . . . . . . . . . . 0 °C to 70 °C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications**

Test Conditions: V<sub>CC</sub> = +5V, V<sub>EE</sub> = -5V, D<sub>GND</sub> = 0V, A<sub>GND</sub> = 0V, V<sub>REF HI</sub> = +1.00000V, V<sub>REF LQ</sub> = AGND, f<sub>CLOCK</sub> = 2.40MHz, R<sub>INT</sub> = 400k $\Omega$ , C<sub>INT</sub> = 0.01 $\mu$ F, T<sub>A</sub> = 25°C, V<sub>IN LO</sub> = A<sub>GND</sub>, C<sub>REF</sub> = 1.0 $\mu$ F, 5<sup>1</sup>/<sub>2</sub> Digit Compensated Mode, Unless Otherwise Specified

| PARAMETER                                                                 | TEST CONDITIONS                                                                                                                            | MIN                    | TYP     | MAX                    | UNITS     |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|------------------------|-----------|

| Integral Non-Linearity, INL                                               | 0V to +2V (Notes 2, 3, 4, 5)                                                                                                               | -                      | ±0.0015 | ±0.0035                | % FS      |

|                                                                           | -2V to 0V (Notes 2, 3, 4, 5)                                                                                                               | -                      | ±0.0015 | ±0.0035                | % FS      |

| Ratiometric Reading                                                       | V <sub>IN HI</sub> = V <sub>REF HI</sub> = 1.00000V                                                                                        | 99996                  | 100000  | 100003                 | Counts    |

| Zero Error, ZE                                                            | V <sub>IN HI</sub> = 0.00000V                                                                                                              | -                      | 0       | ±1                     | Counts    |

| Voltage Range of V <sub>IN LO</sub> Input (Pin 13), V <sub>IN LO</sub>    | -2V ≤ V <sub>IN HI</sub> - V <sub>IN LO</sub> ≤ 2V                                                                                         | -1                     | -       | 1                      | V         |

| Voltage Range of V <sub>IN HI</sub> Input<br>(Pin 12), V <sub>IN HI</sub> | -2V ≤ V <sub>IN HI</sub> - V <sub>IN LO</sub> ≤ 2V                                                                                         | V <sub>IN LO</sub> -2V | -       | V <sub>IN LO</sub> +2V | V         |

| Common Mode Rejection, CMR                                                | $V_{IN HI} = V_{IN LO} = -3V \text{ to } +3V$                                                                                              | -                      | 3       | -                      | Counts    |

| Input Leakage Current, I <sub>IN</sub>                                    | Pins 9, 10, 12, 13, V <sub>IN</sub> = +3V, -3V                                                                                             | -                      | -       | ±0.1                   | μΑ        |

| Input Capacitance, C <sub>IN</sub>                                        | Pins 9, 10, 12, 13                                                                                                                         | -                      | 5       | -                      | pF        |

| Noise (Peak-to-Peak Value, Not<br>Exceeded 95% of Time), e <sub>N</sub>   |                                                                                                                                            | -                      | ±1      | -                      | Counts    |

| Zero Drift, T <sub>C(ZE)</sub>                                            | V <sub>IN HI</sub> = 0.00000V                                                                                                              | -                      | 0       | -                      | Counts/OC |

| Full Scale Error Tempco, T <sub>C(FSE)</sub>                              | V <sub>IN HI</sub> = ±2.00000V                                                                                                             | -                      | ±0.1    | -                      | Counts/OC |

| Supply Range, V <sub>SUPPLY</sub>                                         |                                                                                                                                            |                        |         |                        |           |

| Vcc                                                                       |                                                                                                                                            | +4.75                  | +5.0    | +5.5                   | V         |

| V <sub>EE</sub>                                                           |                                                                                                                                            | -4.75                  | -5.0    | -5.5                   | V         |

| V <sub>CC</sub> Supply Current, I <sub>CC</sub>                           |                                                                                                                                            | -                      | -       | 10                     | mA        |

| V <sub>EE</sub> Supply Current, I <sub>EE</sub>                           |                                                                                                                                            | -                      | -       | 4.5                    | mA        |

| Digital GND Current, IDGND                                                |                                                                                                                                            | -                      | -       | 5.5                    | mA        |

| Analog GND Current, I <sub>AGND</sub>                                     |                                                                                                                                            | -                      | +3      | -                      | μΑ        |

| V <sub>CC</sub> , V <sub>EE</sub> Power Supply Rejection, PSR             | wer Supply Rejection, $V_{IN~HI} = V_{REF~HI} = 1.00000V$ , $V_{CC} = +4.75V$ , $V_{EE} = -4.75V$ to $V_{CC} = +5.50V$ , $V_{EE} = -5.50V$ |                        | 3       | -                      | Counts    |

| Guard Driver Pins 5, 8<br>Output Current, I <sub>OGD</sub>                | V <sub>IN</sub> (Pins 9, 10) = +3V, -3V                                                                                                    | ±10                    | -       | -                      | μА        |

### NOTES:

- 2. All typical values have been characterized but are not production tested.

- 3. Not production tested, guaranteed by design and characterization.

- 4. Reference adjusted for correct full-scale reading.

- 5.  $V_{IN} = V_{IN HI} V_{IN LO}$ .

## **DC Electrical Specifications**

Test Conditions:  $V_{CC}$  = +5V,  $V_{EE}$  = -5V,  $D_{GND}$  = 0V,  $A_{GND}$  = 0V,  $V_{REF\ HI}$  = +1.00000V,  $V_{REF\ LO}$  =  $A_{GND}$ ,  $V_{CLOCK}$  = 2.40MHz,  $V_{RINT}$  = 400k $V_{RINT}$  = 0.01 $V_{RINT}$  = 0.01

| PARAMETER                                                   | TEST CONDITIONS                                                                                      | MIN       | TYP | MAX | UNITS |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------|-----|-----|-------|

| Input Low Voltage, V <sub>IL</sub>                          | Pins 15-25, 28                                                                                       | -         | -   | 0.8 | V     |

| Input High Voltage, VIH                                     | Pins 15-25, 28                                                                                       | -         | -   | V   |       |

| Output Low Voltage, V <sub>OL</sub>                         | Pins 16, 18-25, I <sub>OL</sub> = 1.6mA                                                              | -         | -   | 0.4 | V     |

| Output High Voltage, V <sub>OH</sub>                        | Pins 16, 18-25, I <sub>OH</sub> = -400μA                                                             | 400μΑ 2.4 |     |     | V     |

| Three-State Leakage Current,<br>Pins 18-25, I <sub>OL</sub> | All Digital Drivers In High Impedance State, Parallel Mode. $CS = V_{CC}$ , $V_{IN} = 0V$ , $V_{CC}$ |           | -   | ±10 | μА    |

| Leakage, Pins 15-17, 28, I <sub>IN</sub>                    | V <sub>IN</sub> = 0V, V <sub>CC</sub>                                                                | -         | -   | ±1  | μΑ    |

| Input Capacitance, C <sub>IN</sub>                          | Pins 15, 17-25, 28                                                                                   | -         | 5   | -   | pF    |

|                                                             | Pin 16                                                                                               | -         | 10  | -   | pF    |

| Input Pullup Current (Pins 18-25), I <sub>PU</sub>          | Pins 18-25 at D <sub>GND</sub><br>SEL = D <sub>GND</sub> (Serial Modes)                              | -         | -5  | -   | μА    |

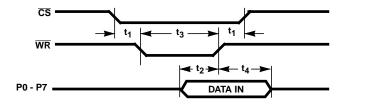

### **AC Electrical Specifications**

$T_A=0^{o}\text{C to }75^{o}\text{C}; \text{ Test Conditions: } V_{CC}=+4.75\text{V}, V_{EE}=-5.00\text{V (Note 8), } D_{GND}=0\text{V}, A_{GND}=0\text{V}, V_{IN LO}=A_{GND}, V_{REF HI}=+1.00000\text{V}, V_{REF LO}=A_{GND}, f_{CLOCK}=2.40\text{MHz}, R_{INT}=400\text{k}\Omega, C_{INT}=0.01\mu\text{F}, V_{IL}=0\text{V}, V_{IH}=4\text{V}, V_{OL}=V_{OH}=1.5\text{V}, t_r=t_f<10\text{ns}, 5^1/_2 \text{ Digit Compensated Mode, Unless Otherwise Specified}$

| PARAMETER                                                                                                   | TEST CONDITIONS                              | MIN                  | TYP | MAX | UNITS |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------|-----|-----|-------|

| CS Setup/Hold of WR, t <sub>1</sub>                                                                         |                                              | 0                    | -   | -   | ns    |

| WR Setup of Data In, t <sub>2</sub>                                                                         |                                              | 50                   | -   | -   | ns    |

| WR Pulse Width, t <sub>3</sub>                                                                              |                                              | 150                  | -   | -   | ns    |

| Data Hold After WR, t <sub>4</sub>                                                                          |                                              | 20                   | -   | -   | ns    |

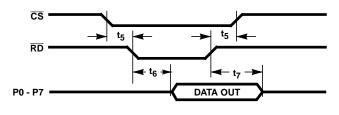

| CS Setup/Hold of RD, t₅                                                                                     | (Note 7)                                     | 25                   | -   | -   | ns    |

| RD to Data Out, t <sub>6</sub>                                                                              | C <sub>L</sub> = 50pF, V <sub>O</sub> = 1.5V | -                    | -   | 100 | ns    |

| RD to Hi-Z State, t <sub>7</sub>                                                                            |                                              | -                    | -   | 70  | ns    |

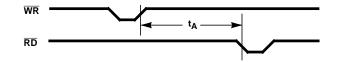

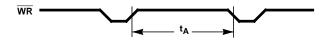

| $\overline{\text{WR}}$ to $\overline{\text{RD}}$ , $\overline{\text{WR}}$ to $\overline{\text{WR}}$ , $t_A$ | (Note 7)                                     | 5/f <sub>CLOCK</sub> | -   | -   | s     |

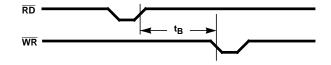

| RD to WR, t <sub>B</sub>                                                                                    | (Note 7)                                     | 200                  | -   | -   | ns    |

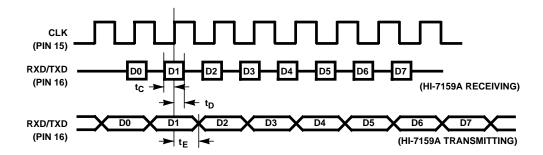

| RXD Setup of Data In, t <sub>C</sub>                                                                        | (Note 7)                                     | 60                   | -   | -   | ns    |

| Data Hold After EXT CLK, t <sub>D</sub>                                                                     |                                              | 40                   | -   | -   | ns    |

| EXT CLK to DATA OUT, t <sub>E</sub>                                                                         |                                              | -                    | -   | 300 | ns    |

| CS Setup of TXD, t <sub>f</sub>                                                                             |                                              | 100                  | -   | -   | ns    |

### NOTES:

- 6. All typical values have been characterized but are not production tested.

- 7. Not production tested, guaranteed by design and characterization.

- 8. All AC characteristics are guaranteed for  $V_{CC}$  = +5V 15%,  $V_{EE}$  = -5V 15%, over  $T_A$  = 0°C to 75°C.

# **Timing Waveforms**

FIGURE 1A. WRITE

FIGURE 1B. WRITE TO READ CYCLE

FIGURE 1C. WRITE TO WRITE CYCLE

FIGURE 1D. READ

FIGURE 1E. READ TO WRITE CYCLE

FIGURE 1. PARALLEL MODE TIMING

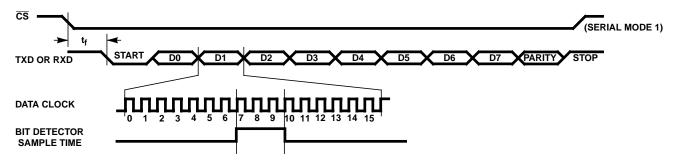

FIGURE 2A. SERIAL MODE 0 TIMING

NOTE: All input timing shown is defined at 50% points.

FIGURE 2B. SERIAL MODE TIMING

# Pin Descriptions

| PIN | SYMBOL                   | DESCRIPTION       |                                                           |                      |                    |  |  |  |  |

|-----|--------------------------|-------------------|-----------------------------------------------------------|----------------------|--------------------|--|--|--|--|

| 1   | V <sub>CC</sub>          | Posit             | Positive 5V Power Supply for analog and digital sections. |                      |                    |  |  |  |  |

| 2   | INT OUT                  | Integ             | rator Output; external com                                | ponent terminal.     |                    |  |  |  |  |

| 3   | INT IN                   | Integ             | rator Input; external compo                               | onent terminal.      |                    |  |  |  |  |

| 4   | BUF OUT                  | V <sub>IN F</sub> | Il Voltage Buffer Output; e                               | xternal componen     | t terminal.        |  |  |  |  |

| 5   | C <sub>REF</sub> - Guard | Refe              | Reference Capacitor guard ring terminal (negative).       |                      |                    |  |  |  |  |

| 6   | C <sub>REF</sub> -       | Refe              | rence Capacitor negative t                                | erminal.             |                    |  |  |  |  |

| 7   | C <sub>REF</sub> +       | Refe              | Reference Capacitor positive terminal.                    |                      |                    |  |  |  |  |

| 8   | C <sub>REF</sub> + Guard | Refe              | Reference Capacitor guard ring terminal (positive).       |                      |                    |  |  |  |  |

| 9   | V <sub>REF HI</sub>      | Posit             | ive Reference Input termin                                | al.                  |                    |  |  |  |  |

| 10  | V <sub>REF</sub> LO      | Nega              | ative Reference Input termi                               | nal.                 |                    |  |  |  |  |

| 11  | A <sub>GND</sub>         | Analo             | og Ground (0V).                                           |                      |                    |  |  |  |  |

| 12  | V <sub>IN HI</sub>       | Posit             | ive Analog Input Voltage to                               | erminal.             |                    |  |  |  |  |

| 13  | V <sub>IN LO</sub>       | Nega              | ative Analog Input Voltage                                | terminal.            |                    |  |  |  |  |

| 14  | V <sub>EE</sub>          | Nega              | ative 5V Power Supply for a                               | analog section.      |                    |  |  |  |  |

| 15  | RD/RXD                   | Para              | llel Read; serial receive (m                              | odes 1 and 2), se    | rial clock (mode   |  |  |  |  |

| 16  | WR/TXD                   | Para              | llel Write; serial transmit (n                            | nodes 1 and 2), se   | erial receive/tran |  |  |  |  |

| 17  | CS/SAD4                  | Chip              | Select (parallel and serial                               | modes 0 and 1), s    | erial address bi   |  |  |  |  |

| 18  | P0/SMS0                  | Para              | llel I/O Port (P0); serial mo                             | de select pin.       |                    |  |  |  |  |

| 19  | P1/SMS1                  | Para              | llel I/O Port (P1); serial mo                             | de select pin.       | ·                  |  |  |  |  |

|     |                          |                   |                                                           |                      |                    |  |  |  |  |

|     |                          |                   | MODE                                                      | SMS0                 | SMS1               |  |  |  |  |

|     |                          |                   | Serial Mode 0                                             | 0                    | 0                  |  |  |  |  |

|     |                          |                   | Serial Mode 1                                             | 0                    | 1                  |  |  |  |  |

|     |                          |                   | Serial Mode 2                                             | 1                    | 0                  |  |  |  |  |

|     |                          |                   | Reserved                                                  | 1                    | 1                  |  |  |  |  |

|     |                          |                   |                                                           |                      |                    |  |  |  |  |

| 20  | P2/SAD0                  | Para              | llel I/O Port (P2); serial add                            | dress bit 0.         |                    |  |  |  |  |

| 21  | P3/SAD1                  |                   | llel I/O Port (P3); serial add                            |                      |                    |  |  |  |  |

| 22  | P4/SAD2                  | _                 | llel I/O Port (P4); serial add                            |                      |                    |  |  |  |  |

| 23  | P5/SAD3                  |                   | llel I/O Port (P5); serial add                            |                      |                    |  |  |  |  |

| 24  | P6/BRS0                  | _                 | llel I/O Port (P6); serial bau                            |                      |                    |  |  |  |  |

| 25  | P7/BRS1                  | _                 | llel I/O Port (P7); serial bau                            |                      |                    |  |  |  |  |

|     |                          |                   |                                                           |                      |                    |  |  |  |  |

|     |                          |                   | BAUD RATE                                                 | BRS0                 | BRS1               |  |  |  |  |

|     |                          |                   | 300                                                       | 0                    | 0                  |  |  |  |  |

|     |                          |                   | 1200                                                      | 0                    | 1                  |  |  |  |  |

|     |                          |                   | 9600                                                      | 1                    | 0                  |  |  |  |  |

|     |                          |                   | 19200 1 1                                                 |                      |                    |  |  |  |  |

|     |                          |                   | 13200                                                     |                      |                    |  |  |  |  |

| 26  | D <sub>GND</sub>         | Digita            | al Ground (0V).                                           |                      |                    |  |  |  |  |

| 27  | X <sub>TAL</sub>         | -                 | lator Out; crystal connection                             | on pin (other crysta | al pin connected   |  |  |  |  |

| 28  | SEL                      | _                 | ct pin for parallel or serial of                          |                      | F 55100104         |  |  |  |  |

| -   |                          | Para              | llel SEL = 1                                              |                      |                    |  |  |  |  |

|     |                          | Seria             | Serial Modes SEL = 0                                      |                      |                    |  |  |  |  |

## Theory of Operation

The HI-7159A attains its  $5^{1}/_{2}$  digit resolution through the use of multiple integrations per conversion, creating an effective integrator swing greater than the supply rails, and a successive integration technique used to measure the residue on the integrator capacitor to  $5^{1}/_{2}$  digit accuracy.

In the  $5^{1}/_{2}$  digit mode, the input voltage is integrated and reference de-integrated four times. This results in a count with the same effective resolution as a single integration with four times the integrator swing amplitude. In this manner effective integrator swings of  $\pm 12$ V or greater can be achieved with  $\pm 5$ V supplies. The four integrations are spaced so that commonmode signals whose frequency is an integer multiple of fCRYSTAL/40,000 are rejected. In the  $4^{1}/_{2}$  digit mode, only one input integration is performed, thus the minimum frequency for common-mode rejection becomes fCRYSTAL/10,000.

These first four integrations measure the input voltage to an resolution of  $3^{1}/_{2}$  digits, or 1mV/count. To achieve  $5^{1}/_{2}$  digit accuracy (10µV/count), the error voltage remaining on the integrator capacitor (representing the overshoot of the integrator due to comparator delay and clock quantization) must be measured and subtracted from the  $3^{1}/_{2}$  digit result. This is accomplished by multiplying the residue by a factor of 10, then integrating and reference de-integrating the error. This error is subtracted from the  $3^{1}/_{2}$  digit result, yielding a  $4^{1}/_{2}$  digit accurate result. The error remaining from this step is then multiplied by 10 and subtracted, and the process is repeated a third time to achieve an internal accuracy of  $6^{1}/_{2}$  digits. This result is rounded to  $5^{1}/_{2}$  digits and transferred to the holding register, where it can be accessed by the user through one of the three communications modes.

# Conversion Types

The HI-7159A offers the user a choice of three different conversion types. They are: (1) the converter's internal offset voltage, measured by internally connecting  $V_{\mbox{\footnotesize{IN}}\mbox{\footnotesize{HI}}}$  and  $V_{\mbox{\footnotesize{IN}}\mbox{\footnotesize{LO}}}$  to  $A_{\mbox{\footnotesize{GND}}}$  and doing a conversion (Error Only Mode); (2) the input voltage ( $V_{\mbox{\footnotesize{IN}}\mbox{\footnotesize{HI}}}$  minus  $V_{\mbox{\footnotesize{IN}}\mbox{\footnotesize{LO}}}$ ) including the converter's internal offset (Uncompensated Mode); and (3) the input voltage including internal offset errors, minus the internal offset errors (Compensated Mode). This last measurement is a digital subtraction of an Error Only conversion from an Uncompensated conversion, and is the default conversion type. Since a Compensated conversion consists of two conversions, it takes twice as long to perform as the first two types.

Under some conditions, it may be desirable to increase the conversion rate without loss of resolution or accuracy. Since the short term drift of the internal offset error is slight when temperature is controlled, it is not always necessary to convert the error voltage once for every input voltage conversion. It is possible for the host processor to do an error conversion periodically, store the result, and subtract the error from a stream of uncompensated input conversions with its own internal ALU. In this way the conversion rate can be effectively doubled.

### Communication Modes

The HI-7159A A/D converter receives instructions from and transmits data to the user host processor through one of four communication modes. The modes are: parallel microprocessor (Parallel); synchronous serial (Serial Mode 0); serial non-addressed (Serial Mode 1); and serial addressed (Serial Mode 2). The mode is determined by the states of the SEL, SMS0, and SMS1 pins as shown in Table 1.

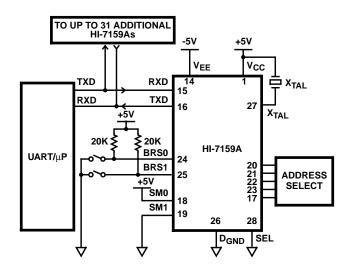

The parallel mode allows the converter to be attached directly to a microprocessor data bus. Data is read and written to the device under control of the microprocessor's  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$  and  $\overline{\text{CS}}$  signals. Serial Mode 0 permits high speed serial data transfer at up to 1 megabits/s. Serial Mode 1 reads and writes industry standard serial data packets consisting of 1 start bit, 8 data bits, 1 parity bit (EVEN), and 1 stop bit, at one of 4 hardware selectable baud rates. Serial Mode 2 is identical to Serial Mode 1 with the addition of addressing capabilities which allow up to 32 HI-7159As to share the same serial line, with each assigned a unique address.

**TABLE 1. COMMUNICATION MODE SELECTION**

| COMMUNICATION MODE | SEL PIN<br>28    | SM S0<br>PIN 18  | SM S1<br>PIN 19  |

|--------------------|------------------|------------------|------------------|

| Parallel           | Vcc              | N/A              | N/A              |

| Serial 0           | D <sub>GND</sub> | D <sub>GND</sub> | D <sub>GND</sub> |

| Serial 1           | D <sub>GND</sub> | D <sub>GND</sub> | V <sub>CC</sub>  |

| Serial 2           | D <sub>GND</sub> | V <sub>CC</sub>  | D <sub>GND</sub> |

All four modes follow the same interface protocol: a request or a command is sent from the host to the HI-7159A, and the converter responds with the requested data and, in the case of a command, begins a new conversion.

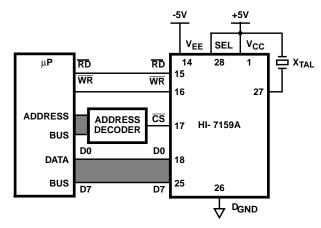

### Parallel Mode Operation

The parallel communication mode (Figure 3) is selected when SEL (Pin 28) is high. Pins 18-25 become the eight bidirectional data bits, P0-P7. Pins 15, 16, and 17 respectively become read ( $\overline{\text{RD}}$ ), write ( $\overline{\text{WR}}$ ), and chip select ( $\overline{\text{CS}}$ ). Timing parameters for the parallel mode are shown in Figure 1.

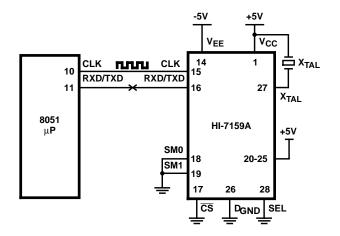

### Serial Mode 0

Serial Mode 0 is the high speed synchronous serial interface, directly compatible with the MCS-51 series of microcontrollers. It is enabled by tying SEL (Pin 28), SMS0 (Pin 18) and SMS1 (Pin 19) low (Figure 4A). Pin 16 is the bidirectional serial data path, and pin 15 is the data clock input. Data sent to the HI-7159A is latched on the rising edge of the serial clock. See Figure 2A for detailed timing information.

Only 8 data bits are used in this mode - no start, stop, or parity bits are transmitted or received.  $\overline{\text{CS}}$  must either be tied to D<sub>GND</sub> or pulled low to access the device. The SAD0 - SAD3 and BRS0 - BRS1 pins are unused in this mode and should be tied high.

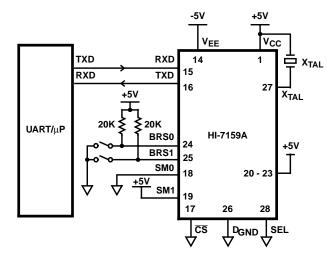

### Serial Mode 1

Serial Mode 1 is selected by tying SMS0 (Pin 18) low, SMS1 (Pin 19) high, and SEL (Pin 28) low (Figure 4B). In this mode the HI-7159A interface emulates a UART, reading and writing data in serial data packets of 1 start bit, 8 data bits, 1 parity bit (EVEN), and 1 stop bit. The baud rate is determined by the state of BRS0 and BRS1 (Pins 24 and 25) as shown in Table 2. Pin 15 becomes the serial receiver pin (RXD) and pin 16 the serial transmitter pin (TXD).  $\overline{\text{CS}}$  (Pin 17) remains a chip select and must either be tied to DGND or pulled low (see Figure 2B) to access the device. SAD0-SAD3 (Pins 20-23) are unused in this mode and should be tied high.

TABLE 2. BAUD RATE SELECTION FOR MODES 1 AND 2

| BRS0<br>PIN 24   | BRS1<br>PIN 25   | BAUD RATE<br>(f <sub>XTAL</sub> = 2.4576MHz) | BAUD RATE vs<br>f <sub>XTAL</sub> |

|------------------|------------------|----------------------------------------------|-----------------------------------|

| D <sub>GND</sub> | D <sub>GND</sub> | 300                                          | f <sub>XTAL</sub> /8192           |

| D <sub>GND</sub> | V <sub>CC</sub>  | 1200                                         | f <sub>XTAL</sub> /2048           |

| V <sub>CC</sub>  | D <sub>GND</sub> | 9600                                         | f <sub>XTAL</sub> /256            |

| V <sub>CC</sub>  | V <sub>CC</sub>  | 19200                                        | f <sub>XTAL</sub> /128            |

FIGURE 3. PARALLEL MODE CONFIGURATION

# Design Hints for Operating in the Parallel Mode

- Always read the status byte twice to make sure that it is cleared.

- 2. Make sure the status byte is cleared before issuing a command to change modes.

- 3. Read each digit pair five times before reading the next byte to ensure that the output data is correct.

- Use a watchdog timer to monitor conversion time. If conversion time is either too long or too short, reissue the conversion command.

FIGURE 4A. SERIAL MODE 0

FIGURE 4B. SERIAL MODE 1

FIGURE 4C. SERIAL MODE 2

FIGURE 4. SERIAL MODE CONFIGURATIONS

### Serial Mode 2

Serial Mode 2 is selected by tying SEL (pin 28) low, SMS0 (pin 18) high, and SMS1 (pin 19) low, as shown in Figure 4C. This mode of operation is identical to Serial Mode 1, except that each device now has one of 32 unique addresses determined by the state of pins 20-23 and 17, as shown in Table 3. This allows multiple HI-7159As to be attached to the same pair of serial lines.

When the microprocessor sends out an Address Byte (Table 4) that matches one of the HI-7159As' hardwired addresses, that particular HI-7159A is selected for all further I/O until another Address Byte with a different address is transmitted.

TABLE 3. HARDWARE ADDRESS SELECTION FOR MODE 2

| PIN 17   | PIN 23      | PIN 22 | PIN 21 | PIN 20   |  |

|----------|-------------|--------|--------|----------|--|

| B4 (MSB) | B4 (MSB) B3 |        | B1     | B0 (LSB) |  |

# Reading the HI-7159A

Despite the wide variety of interface options available on the HI-7159A, the procedure for communicating with it is essentially the same in all four modes. (Serial Mode 2 differs from the rest in two respects: the chip to be communicated with must first be sent an address byte to select it, and the digit bytes are sent one by one, for a total of six bytes, instead of in pairs.) There are two types of bytes that can be sent to the converter, commands and requests. A command byte (Table 5) sets the parameters of and initiates a conversion. Those parameters are: continuity of the conversion (single or continuous), resolution  $(5^{1}/_{2} \text{ or } 4^{1}/_{2})$

digits), and type of conversion (Compensated, Uncompensated, or Error Only). Bit D0 = 0 indicates that this is a command byte and a new conversion(s) should be started.

A request byte (Table 6) asks for either the status of the converter or the result of a conversion. All bits of a request should be set to 0 except D3, D2, and D0. D3 and D2 determine the type of request (status or digit pair), and D0 = 1 indicates to the HI-7159A that this is a request byte. Serial Mode 2 uses a slightly modified request byte, shown in Table 7, allowing it to individually select each of the six digit bytes.

Upon receipt of a request, the HI-7159A will respond with either a status or a digit byte. The status byte (Table 8) returns the current state of the converter. Bit D6 = 1 indicates that a new conversion has been completed since the last time the status byte was read. Bit D6 is cleared after it is read. Bit D4 shows the current continuity (single or continuous). Bit D3 indicates the resolution  $(5^1/_2 \text{ or } 4^1/_2 \text{ digits})$  of the conversion, and bits D2 and D1 indicate the type (Compensated, Uncompensated, or Error Only). Bit D0 = 0 indicates that there was no parity error detected in the last request byte.

The three digit bytes (Table 9) each contain two nibbles representing two digits of the conversion. The sixth nibble contains the MSD (most significant digit), polarity (1 = positive) and overrange (1 = overrange) information. In Serial Mode 2 the digits (Table 10) are requested and received individually, so a total of six requests and six reads is necessary to obtain all  $5^{1}/_{2}$  digits.

TABLE 4. SERIAL MODE 2 ADDRESS BYTE FORMAT (SENT TO HI-7159A)

| ADDRESS BIT | (RESE | RVED) | (MSB) |    |    |    | (LSB) |

|-------------|-------|-------|-------|----|----|----|-------|

| D7          | D6    | D5    | D4    | D3 | D2 | D1 | D0    |

| 1           | 0     | 0     | B4    | В3 | B2 | B1 | В0    |

TABLE 5. COMMAND BYTE FORMAT (SENT TO HI-7159A)

| (R | (RESERVED) |    | CONTINUITY |    | RESOLUTION                    |    | CONVERSION TYPE |    | COMMAND BIT |    |

|----|------------|----|------------|----|-------------------------------|----|-----------------|----|-------------|----|

| D7 | D6         | D5 |            | D4 |                               | D3 |                 | D2 | D1          | D0 |

| 0  | 0          | 0  | Single     | 0  | 5 <sup>1</sup> / <sub>2</sub> | 1  | Comp            | 1  | 1           | 0  |

|    |            |    | Continuous | 1  | 4 <sup>1</sup> / <sub>2</sub> | 0  | Uncomp          | 1  | 0           |    |

|    |            |    |            |    |                               |    | Error Only      | 0  | 1           |    |

TABLE 6. REQUEST BYTE FORMAT, PARALLEL AND SERIAL MODE 1 (SENT TO HI-7159A)

| (RESERVED) |    | BYTE REQUEST |    |                  | (RESERVED) | REQUEST BIT |    |    |

|------------|----|--------------|----|------------------|------------|-------------|----|----|

| D7         | D6 | D5           | D4 |                  | D3         | D2          | D1 | D0 |

| 0          | 0  | 0            | 0  | Digit Pair 0, 1  | 0          | 0           | 0  | 1  |

|            |    |              |    | Digit Pair 2, 3  | 0          | 1           |    |    |

|            |    |              |    | Digit Pair 4, 5  | 1          | 0           |    |    |

|            |    |              |    | Converter Status | 1          | 1           |    |    |

TABLE 7. REQUEST BYTE FORMAT, SERIAL MODE 2 (SENT TO HI-7159A)

| (RESERVED) |    |    |    | BYTE REQUEST     |    |    |    |    |

|------------|----|----|----|------------------|----|----|----|----|

| D7         | D6 | D5 | D4 |                  | D3 | D2 | D1 | D0 |

| 0          | 0  | 0  | 0  | Digit 0          | 0  | 0  | 0  | 1  |

|            |    |    |    | Digit 1          | 0  | 0  | 1  |    |

|            |    |    |    | Digit 2          | 0  | 1  | 0  |    |

|            |    |    |    | Digit 3          | 0  | 1  | 1  |    |

|            |    |    |    | Digit 4          | 1  | 0  | 0  |    |

|            |    |    |    | Digit 5          | 1  | 0  | 1  |    |

|            |    |    |    | Converter Status | 1  | 1  | 0  |    |

### TABLE 8. STATUS BYTE FORMAT (RECEIVED FROM HI-7159A)

| (†) | CONVERTER<br>UPDATE STATUS |    | (†) | CONTINUI   | TY | RESOLUTION                    |    | CONVERSION TYPE |    | ΡΈ | PAR<br>ERR | I  |

|-----|----------------------------|----|-----|------------|----|-------------------------------|----|-----------------|----|----|------------|----|

| D7  |                            | D6 | D5  |            | D4 |                               | D3 |                 | D2 | D1 |            | D0 |

| 0   | No Update                  | 0  | 0   | Single     | 0  | 5 <sup>1</sup> / <sub>2</sub> | 1  | Comp            | 1  | 1  | No         | 0  |

|     | Updated                    | 1  |     | Continuous | 1  | 4 <sup>1</sup> / <sub>2</sub> | 0  | Uncomp          | 1  | 0  | Yes        | 1  |

|     |                            |    |     |            |    |                               |    | Error           | 0  | 1  |            |    |

$(\dagger = Reserved)$

### TABLE 9. DIGIT BYTE FORMAT, PARALLEL AND SERIAL MODE 1 (RECEIVED FROM HI-7159A)

| DIGIT BYTE      | D7                    | D6                    | D5   | D4   | D3   | D2 | D1 | D0   |

|-----------------|-----------------------|-----------------------|------|------|------|----|----|------|

| Digit Pair 0, 1 | MSB1                  |                       |      | LSB1 | MSB0 |    |    | LSB0 |

| Digit Pair 2, 3 | MSB3                  |                       |      | LSB3 | MSB2 |    |    | LSB2 |

| Digit Pair 4, 5 | Polarity<br>(1 = POS) | Overrange<br>(1 = OR) | MSB5 | LSB5 | MSB4 |    |    | LSB4 |

### TABLE 10. DIGIT BYTE FORMAT, SERIAL MODE 2 (RECEIVED FROM HI-7159A)

| DIGIT BYTE   | D7 | D6 | D5 | D4 | D3                    | D2                    | D1  | D0  |

|--------------|----|----|----|----|-----------------------|-----------------------|-----|-----|

| Digits 0 - 4 | 0  | 0  | 1  | 1  | MSB                   |                       | LSB |     |

| Digit 5      | 0  | 0  | 1  | 1  | Polarity<br>(1 = POS) | Overrange<br>(1 = OR) | MSB | LSB |

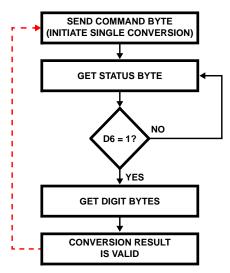

## Single Conversion Mode

The suggested algorithm for reading the HI-7159A in its single conversion mode of operation is shown in Figure 5. Essentially it consists of initiating a conversion, waiting until the conversion is complete, and then reading the results. Since no further conversions take place, the data may be read out at any time and at any speed. This is the most straightforward method of reading the HI-7159A.

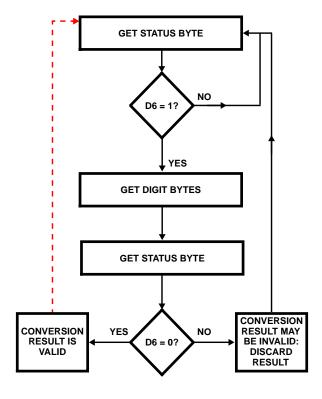

### **Continuous Conversion Mode**

Once a command byte is sent to the HI-7159A initiating the continuous conversion mode, the output data registers will be updated continuously after every conversion. This makes obtaining a valid reading more difficult, since the possibility exists that the current data could be overwritten by a new conversion before all the digit bytes are read. To prevent this, the status byte should be read before and after the data is read from the converter, to ensure that the converter has not updated during the reads. This is demonstrated in Figure 6.

FIGURE 5. READING THE HI-7159A IN THE SINGLE CONVERSION MODE

FIGURE 6. READING THE HI-7159A IN THE CONTINUOUS CONVERSION MODE

Due to the wide range of baud rates available in the serial modes, some of the lower baud rates will take longer to transfer the output data than it takes to perform a conversion. In these cases the continuous mode should not be used. Table 11 shows the percentage of the total conversion time that it takes to read all the data from the converter for the two serial modes. These are best case numbers, assuming that the bytes are transmitted and received end-to-end. An asterisk indicates that it is impossible to get all the data out within one conversion.

Percentages in the 20-50% range indicate that it is possible to get valid data out with very tight code. In all cases the status byte should be checked before and after the reading to ensure data integrity.

TABLE 11. SERIAL MODES 1/2

|              | CONVERSION TYPE                    |                                         |                                    |                                         |  |  |  |  |

|--------------|------------------------------------|-----------------------------------------|------------------------------------|-----------------------------------------|--|--|--|--|

| BAUD<br>RATE | 5 <sup>1</sup> / <sub>2</sub> COMP | 5 <sup>1</sup> / <sub>2</sub><br>UNCOMP | 4 <sup>1</sup> / <sub>2</sub> COMP | 4 <sup>1</sup> / <sub>2</sub><br>UNCOMP |  |  |  |  |

| 300          | */*                                | */*                                     | */*                                | */*                                     |  |  |  |  |

| 1200         | 54%/*                              | */*                                     | */*                                | */*                                     |  |  |  |  |

| 9600         | 7%/13%                             | 14%/25%                                 | 27%/50%                            | 54%/*                                   |  |  |  |  |

| 19200        | 4%/7%                              | 7%/13%                                  | 14%/25%                            | 27%/50%                                 |  |  |  |  |

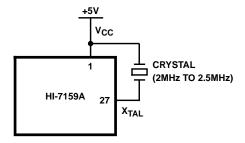

# Crystal Oscillator

The HI-7159A uses a single pin crystal oscillator design (Figure 7). The crystal is connected between Pin 27 and  $V_{CC}$ ; no load capacitors or other components are necessary. The user has a choice of crystal frequencies: 2.4576MHz or 2.4MHz. An off-the-shelf 2.4576MHz crystal works well and provides baud rates of exactly 19.2K, 9600, 1200, and 300. However its total integration period will be 16.28ms, or 0.39ms shorter than a 60Hz cycle. This effectively reduces the normal mode AC rejection.

FIGURE 7. SINGLE-PIN OSCILLATOR

A 2.4MHz crystal results in an integration period of 16.67ms, exactly the length of one 60Hz AC cycle. Normal mode AC rejection is greatest at this frequency. At 2.4MHz, however, the Baud rates will be off by -2.34%. This error is not large enough to cause any errors with most peripherals, and only applies to operation in Serial Modes 1 and 2. Communication in Serial Mode 0 and the Parallel Mode is independent of the crystal frequency. For this mode a 2.4MHz crystal is recommended.

While the oscillator was designed to operate at 2MHz - 2.5MHz, the HI-7159A itself will operate reliably down to less than 600kHz when driven with an external clock. Benefits at lower clock frequencies include reduced rollover error (gain error for negative input voltages) and lower noise. The baud rates mentioned throughout this data sheet correspond to a crystal frequency of 2.4576MHz. At 1.2MHz, the actual baud rates will be half the speed they were at 2.4MHz, i.e., 9600, 4800, 600 and 150 baud. At 600kHz they will be one-fourth.

It may also be possible to directly program the host's serial hardware for operation at nonstandard baud rates, allowing HI-7159A operation at any arbitrary frequency. For example: 50Hz AC rejection requires a 2MHz clock. At this frequency the "9600" baud rate becomes 7812.5 baud. The host's UART must be programmed with the proper divider to operate at this baud rate. The data clock (see Figure 2) is defined as 16 times the baud rate, so the data clock of this configuration would be 125kHz. The data clock can also be determined by dividing the oscillator (clock) frequency by the correct divider from Table 12.

**TABLE 12. CRYSTAL DIVIDER RATIOS**

| BAUD RATE SELECTED | CRYSTAL DIVIDER |

|--------------------|-----------------|

| "300"              | 512             |

| "1200"             | 128             |

| "9600"             | 16              |

| "19200"            | 8               |

The following equation determines the divider needed to operate the HI-7159A at any given crystal frequency:

$$\frac{f_{CLOCK}(7159A)}{Divider(7159A)} = \frac{f_{CRYSTAL}(Host UART)}{Divider(Host UART)} = Data Clock$$

Once determined, the new divider must be written directly to the Host's UART. Most PC compatibles use an 8250 UART with a 1.8432MHz crystal, so the proper divider for the 2MHz example given above would be 15. Again, these considerations apply only to Serial Modes 1 and 2. Parallel and Serial Mode 0 communication rates are independent of crystal frequency.

### **Conversion Time**

The conversion time of the HI-7159A is a function of the crystal frequency and the type of conversion being made. The conversion times for  $f_{CLOCK} = 2.4 MHz$  are shown in Table 13. At other clock frequencies the times may be calculated from the following formula:

$$t_{CONV} = \frac{C}{f_{CLOCK}}$$

where the constant C is determined from Table 13.

**TABLE 13. CONVERSION TIMES**

|            | CONVERSION TYPE                       |                                         |                                       |                                         |  |  |  |  |

|------------|---------------------------------------|-----------------------------------------|---------------------------------------|-----------------------------------------|--|--|--|--|

|            | 5 <sup>1</sup> / <sub>2</sub><br>COMP | 5 <sup>1</sup> / <sub>2</sub><br>UNCOMP | 4 <sup>1</sup> / <sub>2</sub><br>COMP | 4 <sup>1</sup> / <sub>2</sub><br>UNCOMP |  |  |  |  |

| f = 2.4MHz | 133ms                                 | 66.7ms                                  | 33.3ms                                | 16.7ms                                  |  |  |  |  |

| С          | 320,000                               | 160,000                                 | 80,000                                | 40,000                                  |  |  |  |  |

### Component Selection

Three external passive components must be chosen for the HI-7159A: the integrating capacitor ( $C_{INT}$ ), the integrating resistor ( $R_{INT}$ ), and the reference capacitor ( $R_{INT}$ ). They are chosen based on the crystal frequency, the reference voltage ( $R_{INT}$ ), and the desired integrating current. Figure 8 illustrates the analog components necessary for the HI-7159A to function.

FIGURE 8. ANALOG COMPONENTS AND INPUTS

TABLE 14. RECOMMENDED COMPONENT VALUES vs CLOCK FREQUENCY

| fCLOCK | R <sub>INT</sub> | C <sub>INT</sub> | C <sub>REF</sub> |

|--------|------------------|------------------|------------------|

| 2.4MHz | 400kΩ            | 0.01μF           | 1.0μF            |

| 1.2MHz | 360kΩ            | 0.022μF          | 2.2μF            |

| 600kHz | 330kΩ            | 0.047μF          | 4.7μF            |

NOTE: C<sub>INT</sub> MUST be a high quality polypropylene capacitor or performance may be degraded.

The reference capacitor and integrating components can either be selected from Table 14, or calculated from the following equations.

$C_{REF}$  acts as a voltage source at different times during a conversion. Its value is determined by two considerations: it must be small enough to be fully charged from its discharged state at power-on; yet it also must be large enough to supply current to the circuit during conversion without significantly drooping from its initial value. For 2.4MHz operation, a  $1\mu F$  capacitor is recommended. The equation for other frequencies is:

$$C_{REF} = \frac{2.5}{f_{CLOCK}}$$

The values of  $R_{INT}$  and  $C_{INT}$  are selected by choosing the maximum integration current and the maximum integrator output voltage swing. The maximum integration current and voltage swing occurs when  $V_{IN}$  = full scale = 2 X  $V_{REF}$ . The recommended integration current for the HI-7159A is 5mA - 10mA. This will help determine the value of  $R_{INT}$ , since:

$$I_{INT} = \frac{V_{IN}}{R_{INT}} \quad \text{so} \quad R_{INT} = \frac{V_{IN}}{I_{INT}},$$

where  $V_{IN} = V_{IN HI} - V_{IN LO} = 2 \times V_{REF}$ .

Therefore values of  $R_{INT}$  should be between  $200k\Omega$  and  $400k\Omega$ . The exact value of  $R_{INT}$  may be altered to get the exact integrator swing desired after choosing a standard capacitor value for  $C_{INT}$ .

The most critical component in any integrating A/D converter is the integrating capacitor,  $C_{INT}.$  For a converter of this resolution, it is imperative that this component perform as closely to an ideal capacitor as possible. Any amount of leakage or dielectric absorption will manifest itself as linearity errors. For this reason  $C_{INT}$  must be a high quality polypropylene capacitor. Use of any other type may degrade performance. The value of  $C_{INT}$  is determined by the magnitude of the desired maximum integrator output voltage swing as shown below:

$$V_{SWING} = \frac{(V_{IN})(t_{INT})}{(R_{INT})(C_{INT})}$$

Solving for CINT yields:

$$C_{INT} = \frac{(V_{IN})(t_{INT})}{(R_{INT})(V_{SWING})}$$

where  $V_{SWING}$  is the maximum output voltage swing of the integrator,  $V_{IN}$  is the full scale input voltage ( $V_{IN \ HI}$  -  $V_{IN \ LO}$ ) to the converter (equal to 2 X  $V_{REF}$ ), and  $t_{INT}$  is the time in which  $V_{IN}$  is integrated. The best results are achieved when the maximum integrator output voltage is made as large as possible, yet still less than the nonlinear region in the vicinity of the power supply limit. A full scale output swing of about 3V provides the greatest accuracy and linearity.

NOTE: The integrator is auto-zeroed to the voltage at V<sub>IN LO</sub>. If <sub>VIN LO</sub> is negative with respect to A<sub>GND</sub>, the integrator will have | V<sub>IN LO</sub> | less headroom for positive input voltages (inputs where V<sub>IN HI</sub> - V<sub>IN LO</sub> > 0). If V<sub>IN LO</sub> is positive with respect to A<sub>GND</sub>, the integrator will have | V<sub>IN LO</sub> | less headroom for negative input voltages (inputs where V<sub>IN HI</sub> - V<sub>IN LO</sub> < 0). In most applications V<sub>IN LO</sub> is at or near A<sub>GND</sub> and the above equations will be adequate. In applications where V<sub>IN LO</sub> may be more than 0.1V away from A<sub>GND</sub>, it should be included in the integrator swing considerations. The following formula combines all the above considerations:

$$\left| V_{\text{IN LO}} - \frac{(V_{\text{IN HI}} - V_{\text{IN LO}})(10,000)}{(R_{\text{INT}})(C_{\text{INT}})(f_{\text{OSC}})} \right| \le 3V$$

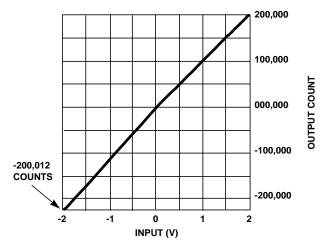

# Gain Error Adjustments

While the HI-7159A has a very linear transfer characteristic in both the positive and negative directions, the slope of the line is slightly greater for negative inputs than for positive. This results in the transfer characteristic shown in Figure 9. One end point of this curve, typically the positive side, can be adjusted to zero error by trimming the reference voltage. The other (negative) side will have a fixed gain error. This error can be removed in software by multiplying all negative readings by a scale factor, determined by dividing the ideal full scale reading (-200,000 counts) by the actual full scale reading when  $V_{\mbox{\footnotesize{IN}}} = -2.00000V.$

FIGURE 9. TYPICAL HI-7159A TRANSFER CHARACTERISTIC

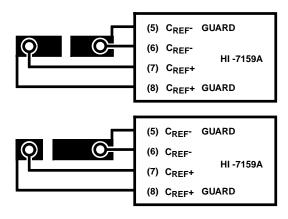

# C<sub>REF</sub> Guard Pins

Depending on the polarity of the input signal, either the negative or the positive terminal of the reference capacitor will be connected to  $A_{GND}$  to provide the correct polarity for reference deintegration. In systems where  $V_{REF\ LO}$  is tied to analog ground, the reference capacitor is effectively shifted down by  $|\ V_{REF}\ |$  for positive input voltages, and is not shifted at all for negative input voltages. This shift can cause some charge on the reference capacitor to be lost due to stray capacitance between the reference capacitor leads and ground traces or other fixed potentials on the board. The reference voltage will now be slightly smaller for positive inputs. This difference in reference voltages for positive and negative inputs appears as rollover error.

The HI-7159A provides two guard ring outputs to minimize this effect. Each guard ring output is a buffered version of the voltage at its respective  $C_{REF}$  pin. If the traces going to the  $C_{REF}$  pins and under  $C_{REF}$  itself are surrounded by their corresponding guard rings, no charge will be lost as  $C_{REF}$  is moved. Figure 10 shows two slightly different patterns. The first one is for capacitors of symmetrical construction, the second is for capacitors with outside foils (one end of the capacitor is the entire outside.

FIGURE 10. TYPICAL GUARD RING LAYOUT

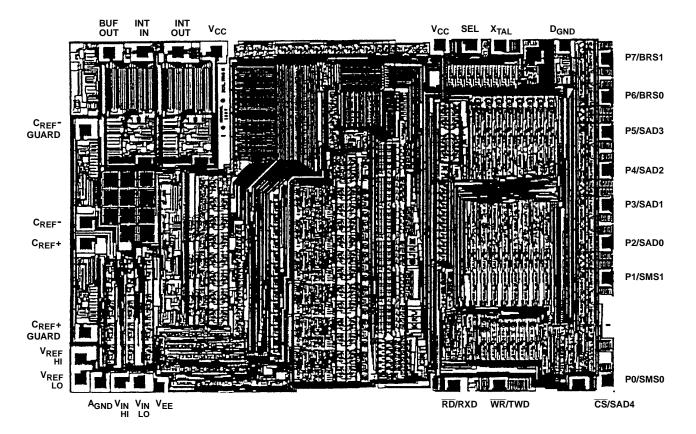

## Die Characteristics

**DIE DIMENSIONS:**

$5817 \mu m \ x \ 3988 \mu m$

## **METALLIZATION:**

Type: SiAI

Thickness: 10kÅ ±1kÅ

### PASSIVATION:

Type: PSG/Nitride Thickness: 15kÅ ±1kÅ

# Metallization Mask Layout

HI-7159A

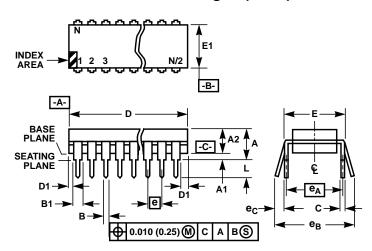

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and  $\boxed{e_A}$  are measured with the leads constrained to be perpendicular to datum  $\boxed{-C^-}$ .

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E28.6 (JEDEC MS-001-BF ISSUE D)

28 LEAD NARROW BODY DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES |       | MILLIM |       |       |

|----------------|--------|-------|--------|-------|-------|

| SYMBOL         | MIN    | MAX   | MIN    | MAX   | NOTES |

| А              | -      | 0.250 | -      | 6.35  | 4     |

| A1             | 0.015  | -     | 0.39   | -     | 4     |

| A2             | 0.125  | 0.195 | 3.18   | 4.95  | -     |

| В              | 0.014  | 0.022 | 0.356  | 0.558 | -     |

| B1             | 0.030  | 0.070 | 0.77   | 1.77  | 8     |

| С              | 0.008  | 0.015 | 0.204  | 0.381 | -     |

| D              | 1.380  | 1.565 | 35.1   | 39.7  | 5     |

| D1             | 0.005  | -     | 0.13   | -     | 5     |

| E              | 0.600  | 0.625 | 15.24  | 15.87 | 6     |

| E1             | 0.485  | 0.580 | 12.32  | 14.73 | 5     |

| е              | 0.100  | BSC   | 2.54   | BSC   | -     |

| e <sub>A</sub> | 0.600  | BSC   | 15.24  | BSC   | 6     |

| e <sub>B</sub> | -      | 0.700 | -      | 17.78 | 7     |

| L              | 0.115  | 0.200 | 2.93   | 5.08  | 4     |

| N              | 28     |       | 28     |       | 9     |

Rev. 0 12/93

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

**NORTH AMERICA**

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902

TEL: (321) 724-7000 FAX: (321) 724-7240 **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111

FAX: (32) 2.724.2111

**ASIA**

Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029