Data Sheet May 1999 FN4516.2

# Low Cost Dual Power Distribution Controller

The HIP1013 is a low cost HOT SWAP dual supply power distribution controller. Two external N-Channel MOSFETs are driven to distribute power while providing load fault isolation. At turn-on, the gate of each external N-Channel MOSFET is charged with a  $10\mu A$  current source. Capacitors on each gate (see the Typical Application Diagram), create a programmable ramp (soft turn-on) to control inrush currents. A built in charge pump supplies the gate drive for the 12V supply N-Channel MOSFET switch.

Over current protection is facilitated by two external current sense resistors. When the current through either resistor exceeds the user programmed value the N-Channel MOSFETs are latched off by the HIP1013. The controller is reset by a rising edge on either  $\overline{\text{PWRON}}$  pin.

Choosing the voltage selection mode the HIP1013 controls either +12V/5V or +3.3V/+5V supplies.

Although pin compatible with the HIP1012 device, the HIP1013 does not offer current regulation during an OC event.

# Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>(°C) | PACKAGE                     | PKG. NO. |  |

|----------------|---------------------|-----------------------------|----------|--|

| HIP1013CB      | -0 to 70            | 14 Ld SOIC                  | M14.15   |  |

| HIP1013CB-T    | -0 to 70            | 14 Ld SOIC<br>Tape and Reel | M14.15   |  |

#### **Features**

- HOT SWAP Dual Power Distribution Control for +5V and +12V or +5V and +3.3V

- · Provides Fault Isolation

- Charge Pump Allows the Use of N-Channel MOSFETs

- · Redundant Power On Controls

- Power Good and Over Current Latch Indicators

- · Adjustable Turn-On Ramp

- · Protection During Turn-On

## **Applications**

- · Power Distribution Control

- Hot Plug™ Components

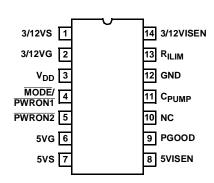

#### **Pinout**

#### HIP1013 (SOIC) TOP VIEW

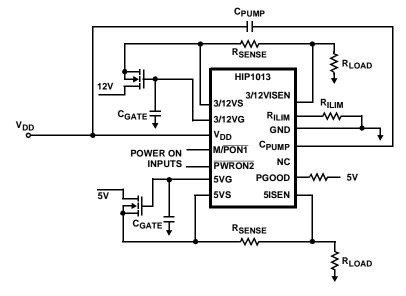

# Typical Application Diagram

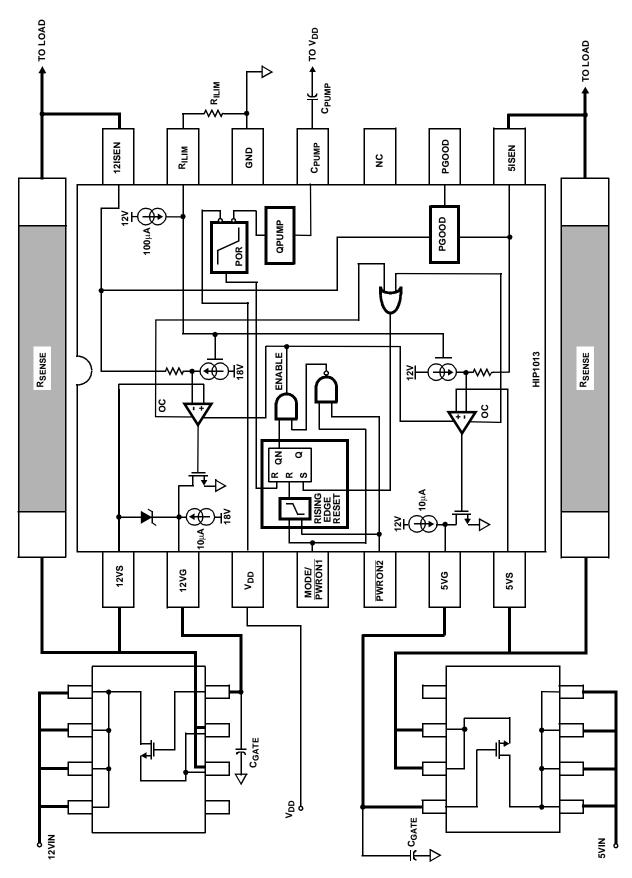

# Functional Diagram

# HIP1013

# Pin Description

| PIN NO. | SYMBOL            | FUNCTION                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |  |

|---------|-------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | 12VS              | 12V Source                                                                      | Connect to source of associated external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                       |  |

| 2       | 12VG              | 12V Gate                                                                        | Connect to the gate of associated N-Channel MOSFET switch. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to $\approx$ 17.4V by a 10 $\mu$ A current source when in 5V/12V mode of operation, otherwise capacitor will be charged to $\approx$ 11.4V.                                    |  |

| 3       | V <sub>DD</sub>   | Chip Supply                                                                     | Connect to 12V supply. This can be either connected directly to the +12V rail supplying the load voltage or to a dedicated V <sub>DD</sub> +12V supply.                                                                                                                                                                                         |  |

| 4       | MODE/<br>PWRON1   | Power ON/ Reset invokes 3.3V operation when shorted to V <sub>DD</sub> , Pin 3. | PWRON1 and PWRON2 are used to turn-on and reset the chip. Both outputs turn-on when either pin is driven low. After an over current limit fault, the chip is reset by the riedge of a reset signal applied to either PWRON pin. Each input has 100μA pull up capability which is compatible with 3V and 5V open drain and standard logic. PWRON |  |

| 5       | PWRON2            | Power ON/Reset                                                                  | is also used to invoke 3.3V control operation in preference to +12V control. By tying pin 4 to pin 3 the charge pump is disabled and the UV threshold also shifts to ≈2.8V.                                                                                                                                                                     |  |

| 6       | 5VG               | 5V Gate                                                                         | Connect to the gate of the external 5V N-Channel MOSFET. A capacitor from this not to ground sets the turn-on ramp. At turn-on this capacitor will be charged to ≈11.4V by 10µA current source.                                                                                                                                                 |  |

| 7       | 5VS               | 5V Source                                                                       | Connect to the source side of 5V external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                      |  |

| 8       | 5VISEN            | 5V Current Sense                                                                | Connect to the load side of the 5V sense resistor to measure the voltage drop across this resistor between 5VS and 5VISEN pins.                                                                                                                                                                                                                 |  |

| 9       | PGOOD             | Power Good Indicator                                                            | PGOOD is driven by an open drain N-Channel MOSFET. It is pulled low when either output voltage is not within specification or and OC condition exists.                                                                                                                                                                                          |  |

| 10      |                   |                                                                                 | No Connection.                                                                                                                                                                                                                                                                                                                                  |  |

| 11      | C <sub>PUMP</sub> | Charge Pump Capacitor                                                           | Connect a 0.1μF capacitor between this pin and V <sub>DD</sub> (Pin 3).                                                                                                                                                                                                                                                                         |  |

| 12      | GND               | Chip Ground                                                                     |                                                                                                                                                                                                                                                                                                                                                 |  |

| 13      | R <sub>ILIM</sub> | Current Limit Set Resistor                                                      | A resistor connected between this pin and ground determines the current level at which current limit is activated. This current is determined by the ratio of the $R_{ILIM}$ resistor to the sense resistor ( $R_{SENSE}$ ). The current at current limit onset is equal to $10\mu A \times (R_{ILIM}/R_{SENSE})$ .                             |  |

| 14      | 12VISEN           | 12V Current Sense                                                               | Connect to the load side of sense resistor to measure the voltage drop across this resistor.                                                                                                                                                                                                                                                    |  |

### **Absolute Maximum Ratings** $T_A = 25^{\circ}C$

| V <sub>DD</sub> 0.3V to +13.2V                                              |

|-----------------------------------------------------------------------------|

| 3/12VG, C <sub>PUMP</sub> 0.3V to 18.5V                                     |

| 3/12VISEN, 3/12VS5V to V <sub>DD</sub> + 0.3V                               |

| 5VISEN, 5VS                                                                 |

| PGOOD, R <sub>ILIM</sub> 0.3V to 7.5V                                       |

| $MODE/\overline{PWRON1}$ , $\overline{PWRON2}$ , 5VG0.3V to $V_{DD}$ + 0.3V |

| ESD Classification                                                          |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | θ <sub>JA</sub> ( <sup>o</sup> C/W)    |

|------------------------------------------------|----------------------------------------|

| SOIC Package                                   | 120                                    |

| Maximum Junction Temperature (Plastic Package) |                                        |

| Maximum Storage Temperature Range65            | 5 <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                                  |

| (SOIC - Lead Tips Only)                        |                                        |

### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +10.5V to +13.2V |

|--------------------------------------|------------------|

| Temperature Range (T <sub>A</sub> )  | 0°C to 70°C      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

- 2. All voltages are relative to GND, unless otherwise specified.

##

| Otherw                                                             | ise Specified         |                                                                    |      |      |      |       |

|--------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|------|------|------|-------|

| PARAMETER                                                          | SYMBOL                | TEST CONDITIONS                                                    | MIN  | TYP  | MAX  | UNITS |

| CONTROL SECTION                                                    | 1                     |                                                                    |      | !    | !    | -     |

| Current Limit Threshold Voltage<br>(Voltage Across Sense Resistor) | V <sub>IL</sub>       | R <sub>ILIM</sub> = 10kΩ                                           | 85   | 100  | 115  | mV    |

| Over Current Limit Response Time                                   | OC <sub>Lrt</sub>     | Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 6.0\Omega$ | -    | 2    | -    | μs    |

| Response Time To Dead Short                                        | RT <sub>SHORT</sub>   | C <sub>VG</sub> = 0.01μF                                           | -    | 500  | 1000 | ns    |

| 12V Gate Turn-On Time                                              | t <sub>ON12V</sub>    | C <sub>VG</sub> = 0.01μF                                           | -    | 12   | -    | ms    |

| 5V Gate Turn-On Time                                               | t <sub>ON5V</sub>     | $C_{VG} = 0.01 \mu F$                                              | -    | 5    | -    | ms    |

| Gate Turn-On Current                                               | I <sub>ON</sub>       | C <sub>VG</sub> = 0.01μF                                           | 8    | 10   | 12   | μА    |

| 12V Under Voltage Threshold                                        | 12V <sub>VUV</sub>    |                                                                    | 10.5 | 10.8 | 11.0 | V     |

| 5V Under Voltage Threshold                                         | 5V <sub>VUV</sub>     |                                                                    | 4.35 | 4.5  | 4.65 | V     |

| 3.3V Under Voltage Threshold                                       | 3.3V <sub>VUV</sub>   |                                                                    | 2.65 | 2.8  | 2.95 | V     |

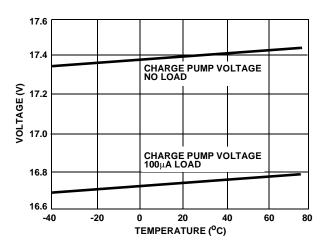

| Charge pumped 12VG Voltage                                         | V12VG                 | C <sub>PUMP</sub> = 0.1μF                                          | 16.8 | 17.3 | 17.9 | V     |

| 3/5VG High Voltage                                                 | 3/5VG                 |                                                                    | 11.2 | 11.9 | -    | V     |

| SUPPLY CURRENT AND IO SPECIFICA                                    | TIONS                 |                                                                    |      |      |      | ,     |

| V <sub>DD</sub> Supply Current                                     | I <sub>VDD</sub>      |                                                                    | 4    | 8    | 10   | mA    |

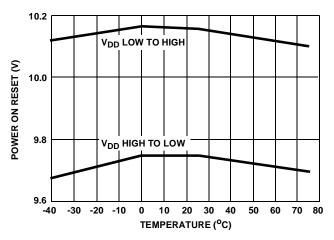

| V <sub>DD</sub> POR Rising Threshold                               | POR <sub>rvth</sub>   |                                                                    | 9.5  | 10.0 | 10.5 | V     |

| V <sub>DD</sub> POR Falling Threshold                              | POR <sub>fvth</sub>   |                                                                    | 9.3  | 9.8  | 10.3 | V     |

| PWRON Pull-up Voltage                                              | PWRN_V                | PWRON pins open                                                    | 1.8  | 2.4  | 3.2  | V     |

| PWRON Rising Threshold                                             | PWR_Vth               |                                                                    | 1.1  | 1.5  | 2    | V     |

| PWRON Hysteresis                                                   | PWR_hys               |                                                                    | 0.1  | 0.2  | 0.3  | V     |

| PWRON Pull-Up Current                                              | PWRN_I                |                                                                    | 60   | 80   | 100  | μΑ    |

| R <sub>ILIM</sub> Pin Current Source Output                        | R <sub>ILIM</sub> _Io |                                                                    | 90   | 100  | 110  | μΑ    |

| Charge Pump Output Current                                         | Qpmp_lo               | C <sub>PUMP</sub> = 0.1μF, C <sub>PUMP</sub> = 16V                 | 400  | 590  | 800  | μΑ    |

| Charge Pump Output Voltage                                         | Qpmp_Vo               | No load                                                            | 17.2 | 17.4 | -    | V     |

| Charge Pump Output Voltage - Loaded                                | Qpmp_VIo              | Load current = 100μA                                               | 16.2 | 16.7 | -    | V     |

| Charge Pump POR Rising Threshold                                   | Qpmp+Vth              |                                                                    | 15.6 | 16   | 16.5 | V     |

| Charge Pump POR Falling Threshold                                  | Qpmp-Vth              |                                                                    | 15.2 | 15.7 | 16.2 | V     |

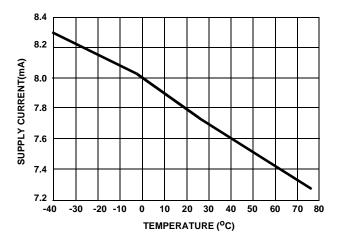

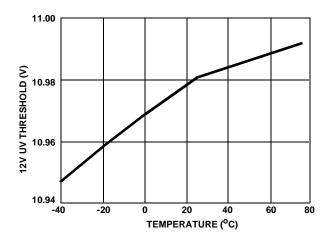

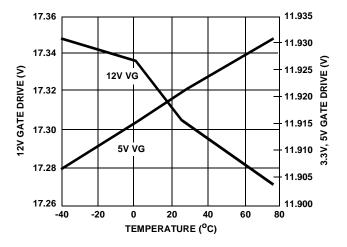

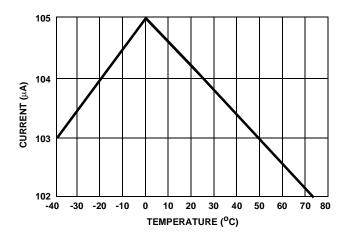

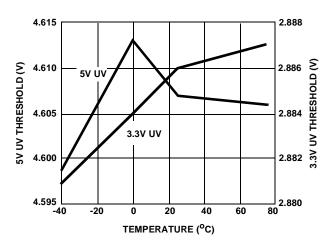

# **Typical Performance Curves**

FIGURE 1. SUPPLY CURRENT

FIGURE 3. 12V UV THRESHOLD

FIGURE 5. 12V, 5V GATE DRIVE

FIGURE 2. R<sub>ILIM</sub> SOURCE CURRENT

FIGURE 4. 3.3V/5V UV THRESHOLD

FIGURE 6. CHARGE PUMP VOLTAGE

## Typical Performance Curves (Continued)

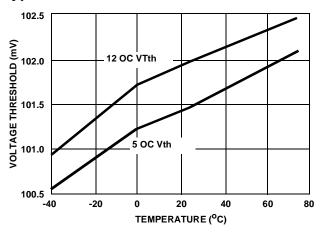

FIGURE 7. OC VOLTAGE THRESHOLD WITH =  $R_{ILIM}\,10k\Omega$

## HIP1013 Description and Operation

The HIP1013 offers the designer a cost efficient 5V and 12V true hot plug controller. This device drives two external N-Channel MOSFET switches and uses a charge pump to provide  $\approx\!17V$  to drive the gate of the 12V supply switch. The HIP1013 features Over Current (OC) programing with a single external resistor,  $R_{ILIM}$  and during turn-on, the gate capacitor of each external N-Channel MOSFET is charged with a 10 $\mu$ A current source. These capacitors create a programmable ramp (soft turn-on).

Upon initial power up, the HIP1013 can either isolate the voltage supply from the load by holding the external N-Channel MOSFET switches off or apply the supply rail voltage directly to the load for true hot swap capability. In either case the HIP1013 turns on in a soft start mode protecting the supply rail from sudden current loading.

The load currents pass through two external current sense resistors. When the voltage across either resistor exceeds the user programmed Over Current (OC) voltage threshold

FIGURE 8. POWER ON RESET VOLTAGE THRESHOLD

value, (see Table 1) the HIP1013 controller turns both N-Channel MOSFETs off in  $\approx 2\mu s$ .

TABLE 1.

| R <sub>ILIM</sub> RESISTOR | NOMINAL OC VTH |  |  |

|----------------------------|----------------|--|--|

| 15K                        | 150mv          |  |  |

| 10K                        | 100mV          |  |  |

| 7.5K                       | 75mV           |  |  |

| 4.99K                      | 50mV           |  |  |

NOTE: Nominal OC Vth =  $R_{ILIM} \times 10 \mu A$

The HIP1013 is reset by a rising edge on either  $\overline{PWRON}$  pin and is turned on by either  $\overline{PWRON}$  pin being driven low. The HIP1013 can control either +12V/5V or +3.3V/+5V supplies. Tying the  $\overline{PWRON1}$  pin to  $V_{DD}$ , invokes the +3.3V/+5V voltage mode. In this mode, the external charge pump capacitor is not needed and  $C_{PUMP}$ , pin 11 is also tied directly to  $V_{DD}$ . Upon any OC or Under Voltage (UV) condition the PGOOD fault indicating signal will pull low when tied high through a resistor to the logic supply.

## **HIP1013 Application Considerations**

There is no unique and specific HIP1013 application evaluation board. Since the HIP1013 is pin compatible with the HIP1012 device, you can substitute a HIP1013 for the existing HIP1012 in either of the HIP1012EVAI1 or EVAL2 boards. Otherwise contact your Intersil Corporation sales office and an already modified board will be provided. Although pin compatible to the HIP1012, the HIP1013 is a less featured dual power supply distribution controller and does not include programmable current limiting regulation and delay time to latch off.

**Random resets** can also occur if the HIP1013 (PINS 8 and 14) sense pins are pulled below ground when turning off a highly inductive load. Place a large load capacitor (10-50 $\mu$ F) on the output to eliminate unintended resets.

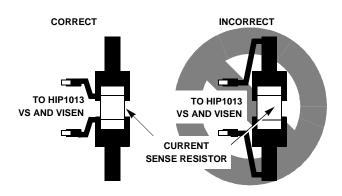

Physical layout of R<sub>SENSE</sub> resistors is critical to avoid the possibility of false over current occurrences. Ideally trace routing between the R<sub>SENSE</sub> resistors and the HIP1013 VS and VISEN pins are direct and as short as possible with zero current in the sense lines.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## Sales Office Headquarters

#### **NORTH AMERICA**

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000

TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946

#### **EUROPE**

Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland TEL: +41 21 6140560

FAX: +41 21 6140579

#### ASIA

Intersil Corporation

Unit 1804 18/F Guangdong Water Building

83 Austin Road

TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433