August 1998

File Number

3208.2

# Power Control IC Single Chip Dual Switching Power Supply

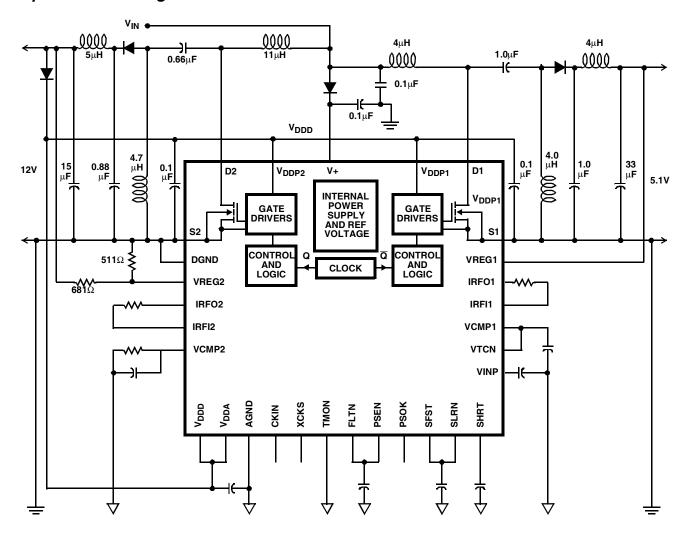

The HIP5062 is a complete power control IC, incorporating two high power DMOS transistors, CMOS logic and two low level analog control circuits on the same Intelligent Power IC. Both the standard "Boost" and the "SEPIC" (Single-Ended Primary Inductance Converter) power supply topologies are easily implemented with this single control IC.

Special power transistor current sensing circuitry is incorporated that minimizes losses due to the monitoring circuitry. Moreover, over-temperature and over-voltage detection circuitry is incorporated within the IC to monitor the chip temperature and the actual power supply output voltage. These circuits can disable the drive to the power transistor to protect both the transistor and, most importantly, the load from over-voltage.

As a result of the power DMOS transistor's current and voltage capability (5A and 60V), multiple output power supplies with total output power capability up to 100W are possible.

#### **Features**

- · Two Current Mode Control Regulators

- Two 60V, 5A On-chip DMOS Transistors

- · Thermal Protection

- · Over-Voltage Protection

- Over-Current Protection

- 1MHz Operation or External Clock

- Synchronization Output

- On-Chip Reference Voltage 5.1V

- Output Rise and Fall Times ~ 3ns

- Designed for 26V to 42V Operation

## **Applications**

- Single Chip Power Supplies

- Current Mode PWM Applications

- Distributed Power Supplies

- Multiple Output Converters

### **Ordering Information**

| PART NUMBER | TEMPERATURE<br>RANGE | PACKAGE     |

|-------------|----------------------|-------------|

| HIP5062DY   | 0°C to +85°C         | 40 Pad Chip |

| HIP5062DW   | 0°C to +85°C         | Wafer       |

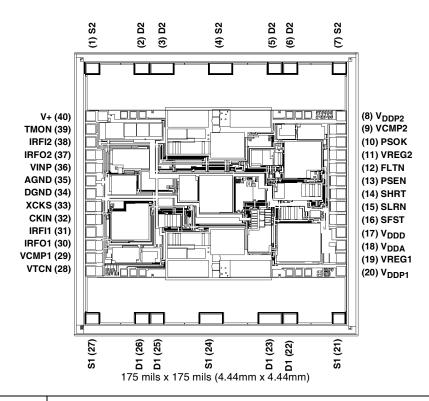

#### Chip

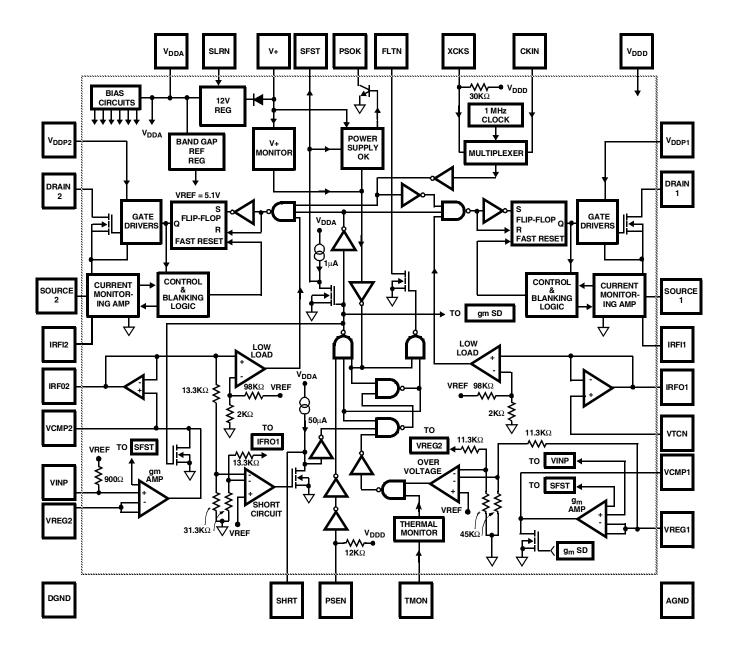

# Simplified Block Diagram

TYPICAL SEPIC CONFIGURATION

#### **Absolute Maximum Ratings**

#### **Thermal Information**

| DC Supply Voltage, V+0.3V to 42V                  | Thermal Resistar |

|---------------------------------------------------|------------------|

| DMOS Drain Voltage0.3V to 60V                     | (Solder Mounte   |

| DMOS Drain Current                                | 0.050" Thick Co  |

| DC Logic Supply0.3V to 16V                        | Maximum Junctio  |

| Output Voltage, Logic Outputs0.3V to 16V          | (Controlled By   |

| Input Voltage, Analog and Logic0.3V to 16V        |                  |

| Operating Junction Temperature Range0°C to +110°C |                  |

| Storage Temperature Range55°C to +150°C           |                  |

|                                                   |                  |

| Thermal Resistance                       | $\theta$ JC         |

|------------------------------------------|---------------------|

| (Solder Mounted to                       | 3°C/W Max           |

| 0.050" Thick Copper Heat Sink)           |                     |

| Maximum Junction Temperature             | +110 <sup>0</sup> C |

| (Controlled By Thermal Shutdown Circuit) |                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **Electrical Specifications** V+ = 36V, Channels 1 and 2, $T_J = 0^{\circ}C$ to $+110^{\circ}C$ ; Unless Otherwise Specified

| SYMBOL                 | PARAMETER                                                  | TEST CONDITIONS                                                     | MIN  | TYP  | MAX   | UNITS             |

|------------------------|------------------------------------------------------------|---------------------------------------------------------------------|------|------|-------|-------------------|

| DEVICE PARA            | AMETERS                                                    |                                                                     |      | •    | •     | •                 |

| l+                     | Supply Current                                             | V+ = 42V, PSEN = 12V                                                | -    | 24.7 | 30    | mA                |

| V <sub>DDA</sub>       | Internal Regulator Output                                  | V+ = 30V to 42V, I <sub>OUT</sub> = 0mA                             | 11.7 | -    | 13.3  | V                 |

|                        | Voltage                                                    | V+ = 30V to 42V, I <sub>OUT</sub> = 30mA                            | 11.5 | -    | 13.3  | V                 |

|                        |                                                            | SLRN = 12V, I <sub>OUT</sub> = 0mA                                  | 11.5 | -    | 13.3  | V                 |

| VINP                   | Reference Voltage                                          | VDDA = SLRN = 12V, I <sub>VINP</sub> = 0mA                          | 5.01 | 5.1  | 5.19  | V                 |

| R <sub>VINP</sub>      | VINP Resistance                                            | VINP = 0                                                            | =    | 900  | -     | Ω                 |

| ERROR AMPL             | IFIERS                                                     |                                                                     |      | •    | •     | •                 |

| V <sub>IO</sub>        | Input Offset Voltage<br>(REG - VINP)                       | I <sub>VCMP</sub> = 0mA                                             | -    | -    | 10    | mV                |

| R <sub>IN</sub> VREG   | Input Resistance to GND                                    | VREG = 5.1V                                                         | 39   | -    | 85    | kΩ                |

| g <sub>m</sub> (VREG)  | VREG Transconductance<br>(I <sub>VCMP</sub> /(VREG - VINP) | VCMP = 1V to 8V, SFST = 11V                                         | 15   | 30   | 50    | mS                |

| g <sub>m</sub> (SFST)  | SFST Transconductance<br>I <sub>VCMP</sub> /(VREG - SFST)  | V <sub>SFST</sub> < 4.9V                                            | 0.8  | -    | 6     | mS                |

| I <sub>VCMP</sub>      | Maximum Source Current                                     | VREG = 4.95V, VCMP = 8V                                             | -2.5 | -    | -0.75 | mA                |

|                        | Maximum Sink Current                                       | VREG = 5.25V, VCMP = 0.4V                                           | 0.75 | -    | 2.5   | mA                |

| OVTH                   | Over-Voltage Threshold                                     | Voltage at VREG for FLTN to be latched                              | 6.05 | -    | 6.5   | V                 |

| CLOCK                  | 1                                                          |                                                                     |      |      |       |                   |

| fq                     | Internal Clock Frequency                                   | XCKS = 12V, V <sub>DDD</sub> = 12V                                  | 0.9  | 1.0  | 1.1   | MHz               |

| V <sub>TH</sub> CKIN   | External Clock Input Threshold Voltages                    |                                                                     | 33   | -    | 66    | %V <sub>DDD</sub> |

| DMOS TRANS             | SISTORS                                                    |                                                                     |      |      |       | 1                 |

| r <sub>DS(on)</sub>    | Drain-Source On-State<br>Resistance                        | I Drain = 2.5A, V <sub>DDD</sub> = 11V,<br>T <sub>J</sub> = +25°C   | -    | -    | 0.22  | Ω                 |

| I <sub>DSS</sub>       | Drain-Source Leakage Current                               | Drain to Source Voltage = 60V                                       | -    | 1    | 100   | μΑ                |

| CURRENT CC             | NTROLED PWM                                                | •                                                                   |      |      |       |                   |

| V <sub>IO</sub>   VCMP | Buffer Offset Voltage (VCOMP - V <sub>IFRO</sub> )         | IFRO = 0mA to -5mA,<br>VTCN = 0.2V to 7.6V,<br>VCMP2 = 0.2V to 7.6V | -    | -    | 125   | mV                |

# $\textbf{Electrical Specifications} \ \ \text{V+} = 36 \text{V}, \ \text{Channels 1 and 2}, \ \ \text{T}_J = 0 \text{°C to +} 110 \text{°C}; \ \text{Unless Otherwise Specified} \ \ \textbf{(Continued)}$

| SYMBOL               | PARAMETER                                                                                       | TEST CONDITIONS                            | MIN          | TYP  | MAX   | UNITS |

|----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|------|-------|-------|

| V <sub>TH</sub> IFRO | Voltage at IRFO that disables<br>PWM. This is due to low load<br>current                        |                                            | 116          | -    | 250   | mV    |

| I <sub>TH</sub> IFRO | Voltage at IRFO to enable SHRT output current. This is due to Regulator Over Current Conditions |                                            | 6.85         | -    | 7.65  | V     |

| ISHRT                | SHRT Output Current, During<br>Over-Current                                                     | V <sub>IRFO</sub> = 7.7V                   | -75          | -    | -33   | μΑ    |

| V <sub>TH</sub> SHRT | Threshold voltage on SHRT to set FLTN latch                                                     | V <sub>DDD</sub> = 11V                     | -            | 5    | -     | V     |

| I <sub>GAIN</sub>    | I <sub>PEAK</sub> (DMOS <sub>DRAIN</sub> )/I <sub>IRFI</sub>                                    | $\Delta I (DMOS_{DRAIN})/\Delta t = 1A/ms$ | 2.0          | -    | 3.2   | A/mA  |

| R <sub>IRFI</sub>    | IRFI Resistance to GND                                                                          | I <sub>IRFI</sub> = 2mA                    | 150          | -    | 360   | Ω     |

| t <sub>RS</sub>      | Current Comparator Response<br>Time (Note 1)                                                    | ΔΙ (DMOS <sub>DRAIN</sub> )/Δt > 1A/μs     | -            | 30   | -     | ns    |

| MCPW                 | Minimum Controllable Pulse<br>Width (Note 1)                                                    |                                            | 25           | 50   | 100   | ns    |

| MCPI                 | Minimum Controllable DMOS<br>Peak Current (Note 1)                                              |                                            | 125          | 250  | 500   | mA    |

| START-UP             | •                                                                                               |                                            | <del>_</del> | •    | -     |       |

| V+                   | Rising V+ Power-On Reset<br>Voltage                                                             |                                            | 23           | -    | 26.3  | V     |

|                      | Falling V+ Power-Off Set<br>Voltage                                                             |                                            | -            | 15   | -     | V     |

|                      | V+ Power-On Hysteresis                                                                          |                                            | 9.5          | -    | 11.8  | V     |

| V <sub>TH</sub> PSEN | Voltage at PSEN to Enable<br>Supply                                                             | V <sub>DDD</sub> = 11V                     | 3.6          | -    | 6.5   | V     |

| <sup>r</sup> PSEN    | Internal Pull-Up Resistance, to V <sub>DDD</sub>                                                |                                            | -            | 12   | -     | ΚΩ    |

| I <sub>SFST</sub>    | Soft-Start Charging Current                                                                     | V <sub>SFST</sub> = 0V to 11V              | -1.5         | -1.0 | -0.65 | μΑ    |

| IPSOK                | PSOK High-State Leakage<br>Current                                                              | SFST = 11V, PSOK = 12V                     | -1           | -    | 1     | μΑ    |

| V <sub>PSOK</sub>    | PSOK Low-State Voltage                                                                          | SFST = 0V, I <sub>PSOK</sub> = 1mA         | -            | -    | 0.4   | V     |

| V <sub>TH</sub> SFST | PSOK Threshold, Rising V <sub>SFST</sub>                                                        | V <sub>DDD</sub> = 11V                     | 8.1          | -    | 9.9   | V     |

| THERMAL MC           | DNITOR                                                                                          |                                            | •            | •    |       | •     |

| TEMP                 | Substrate Temperature for Thermal Monitor to Trip (Note 1)                                      | TMON = 0V                                  | 105          | -    | 135   | °C    |

#### NOTE:

<sup>1.</sup> Determined by design, not a measured parameter.

# Pin Descriptions

| PAD NUMBER     | DESIGNATION       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 7        | S2                | Source pads for the channel 2 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2, 3, 5, 6     | D2                | Drain pads for the channel 2 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8              | V <sub>DDP2</sub> | This pad is the power input for the channel 2 DMOS gate driver and also is used to decouple the high current pulses to the output driver transistors. The decoupling capacitor should be at least a $0.1\mu F$ chip capacitor placed close to this pad and the DMOS source pads.                                                                                                                                                                                                                                 |

| 9              | VCMP2             | Output of the second channel transconductance amplifier. This node is used for both gain and frequency compensation of the loop.                                                                                                                                                                                                                                                                                                                                                                                 |

| 10             | PSOK              | This pad provides delayed positive indication when both supplies are enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11             | VREG2             | Input to the transconductance error amplifier. The other common input for both amplifiers is VINP, Pad 36.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12             | FLTN              | This is an open drain output that remains low when V+ is too low for proper operation. This node and PSEN are useful in multiple converter configurations. This pad will be latched low when overtemperature, over-voltage or over-current is experienced. V+ must be powered down to reset.                                                                                                                                                                                                                     |

| 13             | PSEN              | This terminal is provided to activate the converter. When the input is low, the DMOS drivers are disabled. There is an internal 12K pull-up resistor on this terminal.                                                                                                                                                                                                                                                                                                                                           |

| 14             | SHRT              | 50μA is internally applied to this node when there is an over-current condition.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15             | SLRN              | Control input to internal regulator that is used during the "start-up" of the supply. In normal operation this terminal starts at 0V and shuts down the internal regulator at approximately 9V. This pad is usually connected to SFST, pad 16.                                                                                                                                                                                                                                                                   |

| 16             | SFST              | Controls the rate of rise of both output voltages. Time is determined by an internal $1\mu A$ current source and an external capacitor.                                                                                                                                                                                                                                                                                                                                                                          |

| 17             | V <sub>DDD</sub>  | Voltage input for the chip's digital circuits. This pad also allows decoupling of this supply.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18             | V <sub>DDA</sub>  | This is the analog supply and internal 12V regulator output usually used only during the start-up sequence. The internal regulator reduced to a nominal 9.2V when SLRN is returned to 12V. Output current capability is 30mA at both voltages.                                                                                                                                                                                                                                                                   |

| 19             | VREG1             | Input to channel one transconductance error amplifier. The other, common input for both amplifiers is VINP, pad 36.                                                                                                                                                                                                                                                                                                                                                                                              |

| 20             | V <sub>DDP1</sub> | This pad is the power input for the channel 1 DMOS gate driver and also is used to decouple the high current pulses to the output driver transistors. The decoupling capacitor should be at least a $0.1\mu F$ chip capacitor placed close to this pad and the DMOS source pads.                                                                                                                                                                                                                                 |

| 22, 23, 25, 26 | D1                | Drain pads for the channel 1 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21, 24, 27     | S1                | Source pads for the channel 1 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28             | VTCN              | Input to transconductance amplifier buffer for channel 1 only. Normally connected to VCMP1, pad 29.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 29             | VCMP1             | Output of the first channel transconductance amplifier. This node is used for both gain and frequency compensation of the loop.                                                                                                                                                                                                                                                                                                                                                                                  |

| 30             | IRFO1             | A resistor placed between this pad and IRFI1 converts the VCMP1 signal to a current for the current sense comparator. The maximum current is set by the value of the resistor, according to the equation: IPEAK = 16/R. Where R is the value of the external resistor in K $\Omega$ and must be greater than 1.5K $\Omega$ but less than 10K $\Omega$ . For example, if the resistor chosen is 1.8K, the peak current will be 8.8A. This assumes VCMP1 is 7.3V. Maximum output current should be kept below 10A. |

| 31             | IRFI1             | See IRFO1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | 1                 | I .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

5

# Pin Descriptions (Continued)

| PAD NUMBER | DESIGNATION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32         | CKIN        | Clock input when XCKS is grounded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 33         | XCKS        | Grounding this terminal provides for the application of an external clock to CKIN input terminal. For normal internal clock operation, this terminal may be left floating or returned to 12V. There is an internal 30K pull-up resistor on this terminal.                                                                                                                                                                                                                                                     |

| 34         | DGND        | Ground of the DMOS gate drivers. This pad is used for bypassing.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 35         | AGND        | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 36         | VINP        | Internal 5.1V reference. This point is usually bypassed.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 37         | IRFO2       | A resistor placed between this pad and IRFI2 converts the VCMP2 signal to a current for the current sense comparator. The maximum current set by the value of the resistor, according to the equation: IPEAK = 16/R. Where R is the value of the external resistor in K $\Omega$ and must be greater than 1.5K $\Omega$ but less than 10K $\Omega$ . For example, if the resistor chosen is 1.8K, the peak current will be 8.8A. This assumes VCMP2 is 7.3V. Maximum output current should be kept below 10A. |

| 38         | IRFI2       | See IRFO2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 39         | TMON        | This is the thermal shut down pad than can be used to disable the thermal shutdown circuit. By returning this pad to $V_{DDA}$ or 12V the function is disabled. Returning this pad to ground will put the IC into the thermal shutdown state. Thermal shutdown occurs at a nominal junction temperature or +120 $^{\circ}$ C. This terminal is normally returned to ground.                                                                                                                                   |

| 40         | V+          | This is the main supply voltage input pad to the regulator IC. Because of the high peak currents this pad must be well bypassed with at least a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                              |

# Functional Block Diagram