# HM-6514

March 1997

# **1024 x 4 CMOS RAM**

# **Features**

- TTL Compatible Input/Output

- Common Data Input/Output

- · Three-State Output

- Standard JEDEC Pinout

- Fast Access Time ...... 120/200ns Max

- 18 Pin Package for High Density

- · On-Chip Address Register

- Gated Inputs No Pull Up or Pull Down Resistors Required

# Description

The HM-6514 is a 1024 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. The device utilizes synchronous circuitry to achieve high performance and low power operation.

On-chip latches are provided for addresses allowing efficient interfacing with microprocessor systems. The data output can be forced to a high impedance state for use in expanded memory arrays.

Gated inputs allow lower operating current and also eliminate the need for pull up or pull down resistors. The HM-6514 is a fully static RAM and may be maintained in any state for an indefinite period of time.

Data retention supply voltage and supply current are guaranteed over temperature.

# **Ordering Information**

| 120ns       | 200ns       | 300ns      | TEMPERATURE RANGE | PACKAGE | PKG. NO. |

|-------------|-------------|------------|-------------------|---------|----------|

| HM3-6514S-9 | HM3-6514B-9 | HM3-6514-9 | -40°C to +85°C    | PDIP    | E18.3    |

| HM1-6514S-9 | HM1-6514B-9 | HM1-6514-9 | -40°C to +85°C    | CERDIP  | F18.3    |

| 24502BVA    | -           | -          | -                 | JAN#    | F18.3    |

| 8102402VA   | 8102404VA   | 8102406VA  | -                 | SMD#    | F18.3    |

| -           | -           | -          | -40°C to +85°C    | CLCC    | J18.B    |

| -           | -           | HM4-6514-B | -55°C to +125°C   |         | J18.B    |

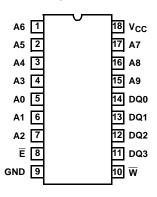

# **Pinouts**

#### HM-6514 (PDIP, CERDIP) TOP VIEW

| PIN            | DESCRIPTION   |

|----------------|---------------|

| А              | Address Input |

| Ē              | Chip Enable   |

| $\overline{W}$ | Write Enable  |

| D              | Data Input    |

| Q              | Data Output   |

# TOP VIEW 2 9 0 4 16 A8 A3 4 1 15 A9 A0 5 1 14 DQ0 A1 6 1 13 DQ1 A2 7 1 12 DQ2

HM-6514 (CLCC)

# Functional Diagram

# **Absolute Maximum Ratings**

# **Operating Conditions**

#### **Thermal Information**

| Thermal Resistance (Typical)          | $\theta_{\sf JA}$ | $_{	extsf{	heta}}$ JC |

|---------------------------------------|-------------------|-----------------------|

| CERDIP Package                        | 75°C/W            | 15 <sup>0</sup> C/W   |

| PDIP Package                          | 75°C/W            | N/A                   |

| CLCC Package                          | 90°C/W            | 33°C/W                |

| Maximum Storage Temperature Range     | 65                | OC to +150°C          |

| Maximum Junction Temperature          |                   |                       |

| Ceramic Package                       |                   | +175 <sup>0</sup> C   |

| Plastic Package                       |                   | +150 <sup>0</sup> C   |

| Maximum Lead Temperature (Soldering 1 | 0s)               | +300 <sup>0</sup> C   |

|                                       |                   |                       |

# **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**DC Electrical Specifications**  $V_{CC} = 5V \pm 10\%$ ;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$  (HM-6514S-9, HM-6514B-9, HM-6514-9)  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  (HM-6514B-8, HM-6514-8)

|        |                                  |                      | LIM                  | IITS                 |                                                                      |                                                               |

|--------|----------------------------------|----------------------|----------------------|----------------------|----------------------------------------------------------------------|---------------------------------------------------------------|

| SYMBOL | PARAMETE                         | MIN                  | MAX                  | UNITS                | TEST CONDITIONS                                                      |                                                               |

| ICCSB  | Standby Supply Current HM-6514-9 |                      | -                    | 25                   | μΑ                                                                   | $IO = 0mA$ , $\overline{E} = V_{CC} - 0.3V$ , $V_{CC} = 5.5V$ |

|        |                                  | HM-6514-8            | -                    | 50                   | μΑ                                                                   |                                                               |

| ICCOP  | Operating Supply Current (       | -                    | 7                    | mA                   | $\overline{E}$ = 1MHz, IO = 0mA, VI = GND,<br>V <sub>CC</sub> = 5.5V |                                                               |

| ICCDR  | Data Retention Supply            | HM-6514-9            | -                    | 15                   | μΑ                                                                   | $IO = 0mA$ , $V_{CC} = 2.0V$ , $\overline{E} = V_{CC}$        |

|        | Current                          |                      | -                    | 25                   | μΑ                                                                   |                                                               |

| VCCDR  | Data Retention Supply Voltage    |                      | 2.0                  | -                    | V                                                                    |                                                               |

| II     | Input Leakage Current            |                      | -1.0                 | +1.0                 | μΑ                                                                   | VI = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.5V           |

| IIOZ   | Input/Output Leakage Curr        | ent                  | -1.0                 | +1.0                 | μΑ                                                                   | $VIO = V_{CC}$ or GND, $V_{CC} = 5.5V$                        |

| VIL    | Input Low Voltage                |                      | -0.3                 | 0.8                  | V                                                                    | V <sub>CC</sub> = 4.5V                                        |

| VIH    | Input High Voltage               |                      | V <sub>CC</sub> -2.0 | V <sub>CC</sub> +0.3 | V                                                                    | V <sub>CC</sub> = 5.5V                                        |

| VOL    | Output Low Voltage               |                      | -                    | 0.4                  | V                                                                    | IO = 2.0mA, V <sub>CC</sub> = 4.5V                            |

| VOH1   | Output High Voltage              |                      | 2.4                  | -                    | V                                                                    | IO = -1.0mA, V <sub>CC</sub> = 4.5V                           |

| VOH2   | Output High Voltage (Note        | V <sub>CC</sub> -0.4 | -                    | V                    | IO = -100μA, V <sub>CC</sub> = 4.5V                                  |                                                               |

# **Capacitance** $T_A = +25^{\circ}C$

| SYMBOL | PARAMETER                         | MAX | UNITS | TEST CONDITIONS                |

|--------|-----------------------------------|-----|-------|--------------------------------|

| CI     | Input Capacitance (Note 2)        | 8   | pF    | f = 1MHz, All measurements are |

| CIO    | Input/Output Capacitance (Note 2) | 10  | pF    | referenced to device GND       |

#### NOTES:

- 1. Typical derating 5mA/MHz increase in ICCOP.

- 2. Tested at initial design and after major design changes.

# HM-6514

**AC Electrical Specifications**  $V_{CC} = 5V \pm 10\%$ ;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$  (HM-6514S-9, HM-6514B-9, HM-6514-9)  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  (HM-6514B-8, HM-6514-8)

|            |                                       | LIMITS |            |     |        |      |       |       |                 |

|------------|---------------------------------------|--------|------------|-----|--------|------|-------|-------|-----------------|

|            |                                       | HM-6   | HM-6514S-9 |     | 514B-9 | НМ-6 | 514-9 |       | TEST            |

| SYMBOL     | PARAMETER                             | MIN    | MAX        | MIN | MAX    | MIN  | MAX   | UNITS | CONDITIONS      |

| (1) TELQV  | Chip Enable Access Time               | -      | 120        | -   | 220    | -    | 300   | ns    | (Notes 1, 3)    |

| (2) TAVQV  | Address Access Time                   | -      | 120        | -   | 220    | -    | 320   | ns    | (Notes 1, 3, 4) |

| (3) TELQX  | Chip Enable Output Enable<br>Time     | 5      | -          | 5   | -      | 5    | -     | ns    | (Notes 2, 3)    |

| (4) TEHQZ  | Chip Enable Output Disable Time       | -      | 50         | -   | 80     | -    | 100   | ns    | (Notes 2, 3)    |

| (5) TELEH  | Chip Enable Pulse Negative<br>Width   | 120    | -          | 200 | -      | 300  | -     | ns    | (Notes 1, 3)    |

| (6) TEHEL  | Chip Enable Pulse Positive<br>Width   | 50     | -          | 90  | -      | 120  | -     | ns    | (Notes 1, 3)    |

| (7) TAVEL  | Address Setup Time                    | 0      | -          | 20  | -      | 20   | -     | ns    | (Notes 1, 3)    |

| (8) TELAX  | Address Hold Time                     | 40     | -          | 50  | -      | 50   | -     | ns    | (Notes 1, 3)    |

| (9) TWLWH  | Write Enable Pulse Width              | 120    | -          | 200 | -      | 300  | -     | ns    | (Notes 1, 3)    |

| (10) TWLEH | Chip Enable Write Pulse<br>Setup Time | 120    | -          | 200 | -      | 300  | -     | ns    | (Notes 1, 3)    |

| (11) TELWH | Chip Enable Write Pulse Hold<br>Time  | 120    | -          | 200 | -      | 300  | -     | ns    | (Notes 1, 3)    |

| (12) TDVWH | Data Setup Time                       | 50     | -          | 120 | -      | 200  | -     | ns    | (Notes 1, 3)    |

| (13) TWHDX | Data Hold Time                        | 0      | -          | 0   | -      | 0    | -     | ns    | (Notes 1, 3)    |

| (14) TWLDV | Write Data Delay Time                 | 70     | -          | 80  | -      | 100  | -     | ns    | (Notes 1, 3)    |

| (15) TWLEL | Early Output High-Z Time              | 0      | -          | 0   | -      | 0    | -     | ns    | (Notes 1, 3)    |

| (16) TEHWH | Late Output High-Z Time               | 0      | -          | 0   | -      | 0    | -     | ns    | (Notes 1, 3)    |

| (17) TELEL | Read or Write Cycle Time              | 170    | -          | 290 | -      | 420  | -     | -     | (Notes 1, 3)    |

# NOTES:

- 1. Input pulse levels: 0.8V to  $V_{CC}$  2.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate equivalent,  $C_L$  = 50pF (min) for  $C_L$  greater than 50pF, access time is derated by 0.15ns per pF.

- 2. Tested at initial design and after major design changes.

- 3.  $V_{CC} = 4.5V$  and 5.5V.

- 4. TAVQV = TELQV + TAVEL.

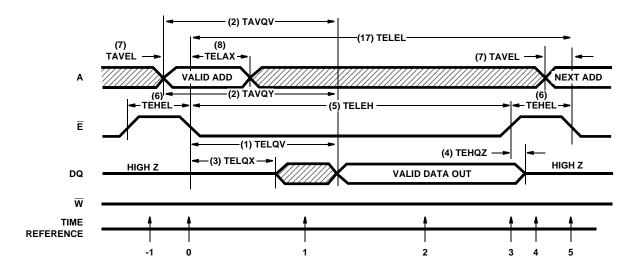

# **Timing Waveforms**

FIGURE 1. READ CYCLE

#### **TRUTH TABLE**

| TIME      | TIME INPUTS DATA I/O |   |   |    |                                           |

|-----------|----------------------|---|---|----|-------------------------------------------|

| REFERENCE | E                    | W | Α | DQ | FUNCTION                                  |

| -1        | Н                    | X | X | Z  | Memory Disabled                           |

| 0         | ¬ <u>\</u> _         | Н | V | Z  | Cycle Begins, Addresses are Latched       |

| 1         | L                    | Н | Х | Х  | Output Enabled                            |

| 2         | L                    | Н | Х | V  | Output Valid                              |

| 3         |                      | Н | Х | V  | Read Accomplished                         |

| 4         | Н                    | Х | Х | Z  | Prepare for Next Cycle (Same as -1)       |

| 5         | 7_                   | Н | V | Z  | Cycle Ends, Next Cycle Begins (Same as 0) |

The address information is latched in the on-chip registers on the falling edge of  $\overline{E}$  (T = 0). Minimum address set up and hold time requirements must be met. After the required hold time, the addresses may change state without affecting device operation. During time (T = 1) the output becomes

enabled, but data is not valid until during time (T = 2).  $\overline{W}$  must remain high throughout the read cycle. After the output data has been read,  $\overline{E}$  may return high (T = 3). This will disable the output buffer and all inputs, and ready the RAM for the next memory cycle (T = 4).

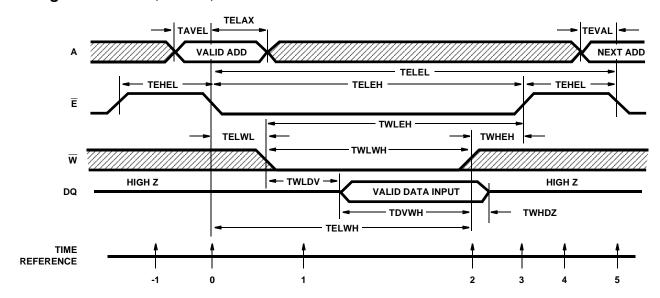

# Timing Waveforms (Continued)

FIGURE 2. WRITE CYCLE TRUTH TABLE

| TIME      |          |   | TIME     |   |                                           |  |

|-----------|----------|---|----------|---|-------------------------------------------|--|

| REFERENCE |          |   | FUNCTION |   |                                           |  |

| -1        | Н        | Х | X        | Z | Memory Disabled                           |  |

| 0         | <u> </u> | Х | V        | Z | Cycle Begins, Addresses are Latched       |  |

| 1         | L        | L | Х        | Z | Write Period Begins                       |  |

| 2         | L        |   | Х        | V | Data In is Written                        |  |

| 3         | 7        | Н | Х        | Z | Write Completed                           |  |

| 4         | Н        | Х | Х        | Z | Prepare for Next Cycle (Same as -1)       |  |

| 5         | 7        | Х | V        | Z | Cycle Ends, Next Cycle Begins (Same as 0) |  |

The write cycle is initiated by the falling edge of  $\overline{E}$  (T = 0), which latches the address information in the on-chip registers. There are two basic types of write cycles, which differ in the control of the common data-in/data-out bus.

Case 1:  $\overline{E}$  falls before  $\overline{W}$  falls

The output buffers may become enabled (reading) if  $\overline{E}$  falls before  $\overline{W}$  falls.  $\overline{W}$  is used to disable (three-state) the outputs so input data can be applied. TWLDV must be met to allow the  $\overline{W}$  signal time to disable the outputs before applying input data. Also, at the end of the cycle the outputs may become active if  $\overline{W}$  rises before  $\overline{E}$ . The RAM outputs and all inputs will three-state after  $\overline{E}$  rises (TEHQZ). In this type of write cycle TWLEL and TEHWH may be ignored.

Case 2:  $\overline{E}$  falls equal to or after  $\overline{W}$  falls, and  $\overline{E}$  rises before or equal to  $\overline{W}$  rising

This  $\overline{E}$  and  $\overline{W}$  control timing will guarantee that the data outputs will stay disabled throughout the cycle, thus, simplifying the data input timing. TWLEL and TEHWH must be met, but TWLDV becomes meaningless and can be ignored. In this cycle TDVWH and TWHDX become TDVEH and TEHDX. In other words, reference data setup and hold times to the  $\overline{E}$  rising edge.

|        | IF                                                                                                                                    | OBSERVE        | IGNORE         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| Case 1 | E falls before W                                                                                                                      | TWLDV          | TWLEL          |

| Case 2 | $\overline{\underline{E}}$ falls after $\overline{\overline{W}}$ and $\overline{\overline{E}}$ rises before $\overline{\overline{W}}$ | TWLEL<br>TEHWH | TWLDV<br>TWHDX |

$\underline{\text{If }}$  a series of consecutive write cycles are to be performed,  $\overline{\text{W}}$  may be held low until all desired locations have been written (an extension of Case 2).

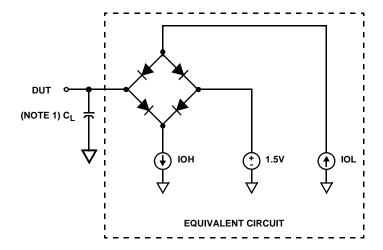

# Test Load Circuit

#### NOTE:

1. Test head capacitance.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may resul from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# Sales Office Headquarters

# NORTH AMERICA

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618

TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 **EUROPE**

Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland

TEL: +41 21 6140560 FAX: +41 21 6140579 **ASIA**

Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road

TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433