# **HMA510**

# 16 x 16-Bit CMOS Parallel Multiplier Accumulator

**April 1997**

#### Features

- 16 x 16-Bit Parallel Multiplication with Accumulation to a 35-Bit Result

- · High-Speed (45ns) Multiply Accumulate Time

- Low Power CMOS Operation

- I<sub>CCSB</sub> = 500μA Maximum

- I<sub>CCOP</sub> = 7.0mA Maximum at 1.0MHz

- HMA510 is Compatible with the CY7C510 and the IDT7210

- Supports Two's Complement or Unsigned Magnitude Operations

- TTL Compatible Inputs/Outputs

- · Three-State Outputs

# Ordering Information

| PART NUMBER | TEMP. RANGE<br>(°C) | PACKAGE    | PKG.<br>NO. |

|-------------|---------------------|------------|-------------|

| HMA510JC-45 | 0 to 70             | 68 Ld PLCC | N68.95      |

| HMA510JC-55 | 0 to 70             | 68 Ld PLCC | N68.95      |

| HMA510GC-55 | 0 to 70             | 68 Ld CPGA | G68.B       |

# Description

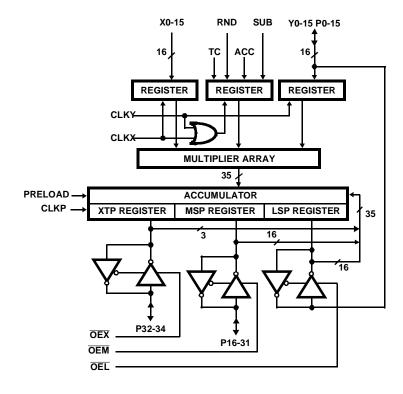

The HMA510 is a high speed, low power CMOS 16 x 16-bit parallel multiplier accumulator capable of operating at 45ns clocked multiply-accumulate cycles. The 16-bit X and Y operands may be specified as either two's complement or unsigned magnitude format. Additional inputs are provided for the accumulator functions which include: loading the accumulator with the current product, adding or subtracting the accumulator contents and the current product, and preloading the Accumulator Registers from the external inputs.

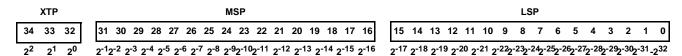

All inputs and outputs are registered. The registers are all positive edge triggered, and are latched on the rising edge of the associated clock signal. The 35-bit Accumulator Output Register is broken into three parts. The 16-bit least significant product (LSP), the 16-bit most significant product (MSP), and the 3-bit extended product (XTP) Registers. The XTP and MSP Registers have dedicated output ports, while the LSP Register shares the Y-inputs in a multiplexed fashion. The entire 35-bit Accumulator Output Register may be preloaded at any time through the use of the bidirectional output ports and the preloaded control.

# **Block Diagram**

#### **Pinouts 68 LEAD PLCC TOP VIEW** 9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61 60 🗖 Y2/P2 59 Y3/P3 58 🗖 Y4/P4 57 Y5/P5 56 Y6/P6 55 Y7/P7 54 🗖 GND 53 GND 52 Y8/P8 51 Y9/P9 50 TY10/P10 49 Y11/P11 48 Y12/P12 47 Y13/P13 46 Y14/P14 45 Y15/P15 44 P16 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 **68 LEAD CPGA TOP VIEW** N/C X15 RND ACC **CLKY PREL CLKP** P33 11 TC X14 **OEL** SUB CLKX **OEX** ОЕМ N/C X13 P34 P32 10 $v_{cc}$ P31 9 X11 X12 P30 8 Х9 X10 P28 P29 7 **X7** X8 P26 P27 Х6 P24 P25 6 X5 5 Х3 X4 P22 P23 **X1** Х2 P20 P21 Y0/P0 P18 3 X0 P19 Y10/ P10 Y12/ P12 Y14/ P14 Y3/P3 Y5/P5 Y7/P7 Y8/P8 P16 2 N/C Y1/P1 P17 Y11/ Y13/ Y15/ 1 Y2/P2 Y4/P4 Y6/P6 GND Y9/P9 N/C P11 P13 P15 Α В С D Ε F G J Κ L

# **HMA510**

# Pin Descriptions

| NAME              | PLCC PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>   | 17-20              |      | The +5V power supply pins. $0.1\mu F$ capacitors between the $V_{CC}$ and GND pins are recommended.                                                                                                                                                                                                                                                                                       |

| GND               | 53, 54             |      | The device ground.                                                                                                                                                                                                                                                                                                                                                                        |

| X0-X15            | 1-10, 63-68        | I    | X-Input Data. These 16 data inputs provide the multiplicand which may be in two's corplement or unsigned magnitude format.                                                                                                                                                                                                                                                                |

| Y0-Y15/<br>P0-P15 | 45-52, 55-62       | I/O  | Y-Input/LSP Output Data. This 16-bit port is used to provide the multiplier which may be in two's complement or unsigned magnitude format. It may also be used for output of the Least Significant Product (P0-P15) or for preloading the LSP Register.                                                                                                                                   |

| P16-P3            | 29-44              | I/O  | MSP Output Data. This 16-bit port is used to provide the Most Significant Product Output (P16-P31). It may also be used to preload the MSP Register.                                                                                                                                                                                                                                      |

| P32-P34           | 26-28              | I/O  | XTP Output Data. This 3-bit port is used to provide the Extended Product Output (P3 P34). It may also be used to preload the XTP Register.                                                                                                                                                                                                                                                |

| TC                | 21                 | I    | Two's Complement Control. Input data is interpreted as two's complement when this control is HIGH. A LOW indicates the data is to be interpreted as unsigned magnitude format. This control is latched on the rising edge of CLKX or CLKY.                                                                                                                                                |

| ACC               | 14                 | I    | Accumulate Control. When this control is HIGH, the Accumulator Output Register contents are added to or subtracted from the current product, and the result is stored back into the accumulator Output Register.  When LOW, the product is loaded into the accumulator Output Register overwriting the current contents. This control is also latched on the rising edge of CLKX or CLKY. |

| SUB               | 13                 | I    | Subtract Control. When both SUB and ACC are HIGH, the Accumulator Register co tents are subtracted from the current product. When ACC is HIGH and SUB is LOW the Accumulator Register contents and the current product are summed. The SUB co trol input is latched on the rising edge of CLKX or CLKY.                                                                                   |

| RND               | 12                 | I    | Round Control. When this control is HIGH, a one is added to the most significant bit the LSP. When LOW, the product is unchanged.                                                                                                                                                                                                                                                         |

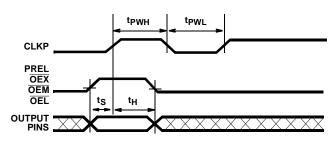

| PREL              | 23                 | I    | Preload Control. When this control is HIGH, the three bidirectional ports may be use to preload the Accumulator Registers. The three-state controls (OEX, OEM, OEL) mube HIGH, and the data will be preloaded on the rising edge of CLKP. When this contribution is LOW, the Accumulator Registers function in a normal manner.                                                           |

| ŌEL               | 11                 | I    | Y-Input/LSP Output Port Three-State Control. When $\overline{\text{OEL}}$ is HIGH, the output drivers are in the high impedance state. This state is required for Y-data input or preloading the LSP Register. When $\overline{\text{OEL}}$ is LOW, the port is enabled for LSP output.                                                                                                   |

| OEM               | 24                 | I    | MSP Output Port Three-State Control. A LOW on this control line enables the port for output. When $\overline{\text{OEM}}$ is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the MSP Register.                                                                                                                                         |

| OEX               | 22                 | I    | XTP Output Port Three-State Control. A LOW on this control line enables the port for output. When $\overline{\text{OEX}}$ is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the XTP Register.                                                                                                                                         |

| CLKX              | 15                 | I    | X-Register Clock. The rising edge of this clock latches the X-Data Input Register alor with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                                                                              |

| CLKY              | 16                 | I    | Y-Register Clock. The rising edge of this clock latches the Y-Data Input Register alor with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                                                                              |

| CLKP              | 25                 | I    | Product Register Clock. The rising edge of CLKP latches the LSP, MSP and XTP Resisters. If the preload control is active, the data on the I/O ports is loaded into these resisters. If preload is not active, the accumulated product is loaded into the registers.                                                                                                                       |

# Functional Description

The HMA510 is a high speed 16 x 16-bit multiplier accumulator (MAC). It consists of a 16-bit parallel multiplier follower by a 35-bit accumulator. All inputs and outputs are registered and are latched on the rising edge of the associated clock signal. The HMA510 is divided into four sections: the input section, the multiplier array, the accumulator and the output/preload section.

The input section has two 16-bit Operand Input Registers for the X and Y operands which are latched on the rising edge of CLKX and CLKY respectively. A four bit Control Register (TC, RND, ACC, SUB) is also included and is latched from either of the input clock signals.

The 16 x 16 multiplier array produces the 32-bit product of the input operands. Two's complement or unsigned magnitude operation can be selected by the use of the TC control. The 32-bit result may also be rounded through the use of the RND control. In this case, a '1' is added to the MSB of the LSP (bit P15). The 32-bit product is zero-filled or sign-extended as appropriate and passed as a 35-bit number to the accumulator section.

The accumulator functions are controlled by the ACC, SUB and PREL control inputs. Four functions may be selected: the accumulator may be loaded with the current product; the product may be added to the accumulator contents; the accumulator contents may be subtracted from the current product; or the accumulator may be loaded from the bidirectional ports. The Accumulator Registers are updated at the rising edge of the CLKP signal.

The output/preload section contains the Accumulator/Output Register and the bidirectional ports. This section is controlled by the signals PREL,  $\overline{\text{OEX}}$ ,  $\overline{\text{OEM}}$  and  $\overline{\text{OEL}}$ . When PREL is high, the output buffers are in a high impedance state. When one of the controls  $\overline{\text{OEX}}$ ,  $\overline{\text{OEM}}$  or  $\overline{\text{OEL}}$  are also high, data present at the outputs will be preloaded into the associated register on the rising edge of CLKP. When PREL is low, the signals  $\overline{\text{OEX}}$ ,  $\overline{\text{OEM}}$  and  $\overline{\text{OEL}}$  are enable controls for their respective three-state output ports.

**TABLE 1. PRELOAD FUNCTION TABLE**

|      |     |     |     | OUTP | UT REGIS | STERS |

|------|-----|-----|-----|------|----------|-------|

| PREL | OEX | OEM | OEL | XTP  | MSP      | LSP   |

| 0    | 0   | 0   | 0   | Q    | Q        | Q     |

| 0    | 0   | 0   | 1   | Q    | Q        | Z     |

| 0    | 0   | 1   | 0   | Q    | Z        | Q     |

| 0    | 0   | 1   | 1   | Q    | Z        | Z     |

| 0    | 1   | 0   | 0   | Z    | Q        | Q     |

| 0    | 1   | 0   | 1   | Z    | Q        | Z     |

| 0    | 1   | 1   | 0   | Z    | Z        | Q     |

| 0    | 1   | 1   | 1   | Z    | Z        | Z     |

| 1    | 0   | 0   | 0   | Z    | Z        | Z     |

| 1    | 0   | 0   | 1   | Z    | Z        | PL    |

| 1    | 0   | 1   | 0   | Z    | PL       | Z     |

| 1    | 0   | 1   | 1   | Z    | PL       | PL    |

| 1    | 1   | 0   | 0   | PL   | Z        | Z     |

| 1    | 1   | 0   | 1   | PL   | Z        | PL    |

| 1    | 1   | 1   | 0   | PL   | PL       | Z     |

| 1    | 1   | 1   | 1   | PL   | PL       | PL    |

- Z = Output Buffers at High Impedance (Disabled).

- Q = Output Buffers at LOW Impedance. Contents of Output Register Available Through Output Ports.

- PL = Output disabled. Preload data supplied to the output pins will be loaded into the register at the rising edge of CLKP.

TABLE 2. ACCUMULATOR FUNCTION TABLE

| PREL | ACC | SUB | Р  | OPERATION |

|------|-----|-----|----|-----------|

| L    | L   | Х   | Q  | Load      |

| L    | Н   | L   | Q  | Add       |

| L    | Н   | Н   | Q  | Subtract  |

| Н    | Х   | Х   | PL | Preload   |

## Input Formats

| 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 2-20 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14 2-15 2-0 2-1 2-2 2-3 2-4 | 1 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14 2-15 20 2-1 2-2 2-3 2-4                                                         |                                                                                                                                                                                         |

| (SIGN) (SIGN)                                                                                                                                   | 4 2 <sup>-5</sup> 2 <sup>-6</sup> 2 <sup>-7</sup> 2 <sup>-8</sup> 2 <sup>-9</sup> 2 <sup>-10</sup> 2 <sup>-11</sup> 2 <sup>-12</sup> 2 <sup>-13</sup> 2 <sup>-14</sup> 2 <sup>-15</sup> |

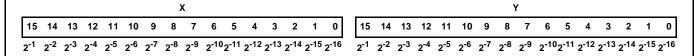

#### FIGURE 1. FRACTIONAL TWO'S COMPLEMENT INPUT

|                          | X  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |   |                    |    |                  |                  | ,                | <b>′</b>         |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

|--------------------------|----|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---|--------------------|----|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 15                       | 14 | 13               | 12               | 11               | 10               | 9               | 8               | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               | 1 | 5                  | 14 | 13               | 12               | 11               | 10               | 9               | 8               | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

| 2 <sup>-15</sup><br>(SIG | _  | 2 <sup>-13</sup> | 2 <sup>-12</sup> | 2 <sup>-11</sup> | 2 <sup>-10</sup> | 2 <sup>-9</sup> | 2 <sup>-8</sup> | 2 <sup>-7</sup> | 2 <sup>-6</sup> | 2 <sup>-5</sup> | 2 <sup>-4</sup> | 2 <sup>-3</sup> | 2 <sup>-2</sup> | 2 <sup>-1</sup> | -2 <sup>0</sup> | _ | 15 <u>2</u><br>IGN | -  | 2 <sup>-13</sup> | 2 <sup>-12</sup> | 2 <sup>-11</sup> | 2 <sup>-10</sup> | 2 <sup>-9</sup> | 2 <sup>-8</sup> | 2 <sup>-7</sup> | 2 <sup>-6</sup> | 2 <sup>-5</sup> | 2 <sup>-4</sup> | 2 <sup>-3</sup> | 2 <sup>-2</sup> | 2 <sup>-1</sup> | -2 <sup>0</sup> |

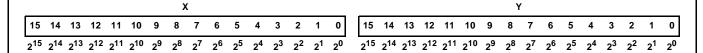

#### FIGURE 2. INTEGER TWO'S COMPLEMENT INPUT

#### FIGURE 3. UNSIGNED FRACTIONAL INPUT

FIGURE 4. UNSIGNED INTEGER INPUT

# **Output Formats**

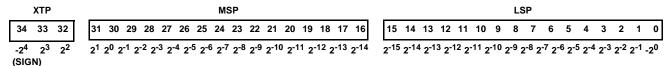

#### FIGURE 5. TWO'S COMPLEMENT FRACTIONAL OUTPUT

| XTP                                                     | MSP                                                             | LSP                                                                                                                                                                                                                                                   |

|---------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34 33 32                                                | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16                 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                                                                                                 |

| -2 <sup>34</sup> 2 <sup>33</sup> 2 <sup>32</sup> (SIGN) | 231 230 229 228 227 226 225 224 223 222 221 220 219 218 217 216 | 2 <sup>15</sup> 2 <sup>14</sup> 2 <sup>13</sup> 2 <sup>12</sup> 2 <sup>11</sup> 2 <sup>10</sup> 2 <sup>9</sup> 2 <sup>8</sup> 2 <sup>7</sup> 2 <sup>6</sup> 2 <sup>5</sup> 2 <sup>4</sup> 2 <sup>3</sup> 2 <sup>2</sup> 2 <sup>1</sup> 2 <sup>0</sup> |

#### FIGURE 6. TWO'S COMPLEMENT INTEGER OUTPUT

FIGURE 7. UNSIGNED FRACTIONAL OUTPUT

# Output Formats

|   |                 | XTP             |                 |   |                 |                 |                 |                 |                 |                 |                 | M               | SP              |                 |                 |                 |                 |                 |                 |                 |                 |     |    |                             |     |    |                 | L              | SP             |    |     |                |    |                |                |    |                |

|---|-----------------|-----------------|-----------------|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|----|-----------------------------|-----|----|-----------------|----------------|----------------|----|-----|----------------|----|----------------|----------------|----|----------------|

| Ī | 34              | 33              | 32              |   | 31              | 30              | 29              | 28              | 27              | 26              | 25              | 24              | 23              | 22              | 21              | 20              | 19              | 18              | 17              | 16              | 15              | 14  | 13 | 12                          | 11  | 10 | 9               | 8              | 7              | 6  | ; ; | 5              | 4  | 3              | 2              | 1  | 0              |

| - | 2 <sup>34</sup> | 2 <sup>33</sup> | 2 <sup>32</sup> | • | 2 <sup>31</sup> | 2 <sup>30</sup> | 2 <sup>29</sup> | 2 <sup>28</sup> | 2 <sup>27</sup> | 2 <sup>26</sup> | 2 <sup>25</sup> | 2 <sup>24</sup> | 2 <sup>23</sup> | 2 <sup>22</sup> | 2 <sup>21</sup> | 2 <sup>20</sup> | 2 <sup>19</sup> | 2 <sup>18</sup> | 2 <sup>17</sup> | 2 <sup>16</sup> | 2 <sup>15</sup> | 214 | 21 | <sup>3</sup> 2 <sup>1</sup> | 2 2 | 11 | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 27 | 26  | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 2 <sup>0</sup> |

FIGURE 8. UNSIGNED INTEGER OUTPUT

#### **Absolute Maximum Ratings**

| Supply Voltage                       | +8.0V                       |

|--------------------------------------|-----------------------------|

| Input, Output or I/O Voltage Applied | GND -0.5V to $V_{CC}$ +0.5V |

| ESD Classification                   | Class 1                     |

## **Operating Conditions**

| Voltage Range     |             |

|-------------------|-------------|

| Temperature Range | 0°C to 70°C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> (oC/M) |

|----------------------------------------|-------------------------------------|------------------------|

| 68 Lead PLCC                           | 43.2                                | 15.1                   |

| 68 Lead PGA                            | 42.69                               | 10.0                   |

| Maximum Package Power Dissipation at 7 | 70 <sup>0</sup> C                   |                        |

| PLCC                                   |                                     | 1.7W                   |

| PGA                                    |                                     |                        |

| Maximum Storage Temperature Range      | 65                                  | 5°C to 150°C           |

| Maximum Junction Temperature           |                                     |                        |

| PLCC                                   |                                     |                        |

| PGA                                    |                                     |                        |

| Maximum Lead Temperature (Soldering, 1 | 10s)                                | 300°C                  |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

# DC Electrical Specifications $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{o}C$ to $70^{o}C$

| PARAMETER                      | SYMBOL          | TEST CONDITIONS                                                                    | MIN | MAX | UNITS |

|--------------------------------|-----------------|------------------------------------------------------------------------------------|-----|-----|-------|

| Logical One Input Voltage      | V <sub>IH</sub> | V <sub>CC</sub> = 5.25V                                                            | 2.0 | -   | V     |

| Logical Zero Input Voltage     | V <sub>IL</sub> | V <sub>CC</sub> = 4.75V                                                            | -   | 0.8 | V     |

| Output HIGH Voltage            | V <sub>OH</sub> | $I_{OH} = -400$ mA, $V_{CC} = 4.75$ V                                              | 2.6 | -   | V     |

| Output LOW Voltage             | V <sub>OL</sub> | I <sub>OL</sub> = +4.0mA, V <sub>CC</sub> = 4.75V                                  | -   | 0.4 | V     |

| Input Leakage Current          | lį              | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.25V$                                         | -10 | 10  | μΑ    |

| Output or I/O Leakage Current  | IO              | $V_{OUT} = V_{CC}$ or GND, $V_{CC} = 5.25V$                                        | -10 | 10  | μΑ    |

| Standby Power Supply Current   | ICCSB           | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V,<br>Outputs Open | -   | 500 | μΑ    |

| Operating Power Supply Current | ІССОР           | $f = 1.0MHz$ , $V_{IN} = V_{CC}$ or GND $V_{CC} = 5.25V$ (Note 2)                  | -   | 7.0 | mA    |

#### NOTE:

2. Operating Supply Current is proportional to frequency, typical rating is 5.0mA/MHz.

# **Capacitance** $T_A = 25^{\circ}C$ , Note 3

| PARAMETER          | SYMBOL           | TEST CONDITIONS                                  | MIN | MAX | UNITS |

|--------------------|------------------|--------------------------------------------------|-----|-----|-------|

| Input Capacitance  | C <sub>IN</sub>  | FREQ = 1MHz, V <sub>CC</sub> = Open all Measure- | -   | 10  | pF    |

| Output Capacitance | C <sub>OUT</sub> | ments are Referenced to Device Ground            | -   | 10  | pF    |

| I/O Capacitance    | C <sub>I/O</sub> |                                                  | -   | 15  | pF    |

#### NOTES:

${\it 3. }\ {\it Not tested, but characterized at initial design and at major process/design changes.}$

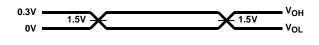

# AC Electrical Specifications $V_{CC}$ = 5.0V ±5%, $T_A$ = 0°C to 70°C

|                          |                 |                 | HMA5 | 10-45 | HMA5 | 10-55 |       |

|--------------------------|-----------------|-----------------|------|-------|------|-------|-------|

| PARAMETER                | SYMBOL          | TEST CONDITIONS | MIN  | MAX   | MIN  | MAX   | UNITS |

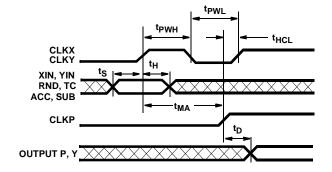

| Multiply Accumulate Time | T <sub>MA</sub> |                 | -    | 45    | -    | 55    | ns    |

# AC Electrical Specifications $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$ (Continued)

|                          |                  |                   | HMA510-45 |     | HMA510-55 |     |       |

|--------------------------|------------------|-------------------|-----------|-----|-----------|-----|-------|

| PARAMETER                | SYMBOL           | TEST CONDITIONS   | MIN       | MAX | MIN       | MAX | UNITS |

| Output Delay             | T <sub>D</sub>   |                   | -         | 25  | -         | 30  | ns    |

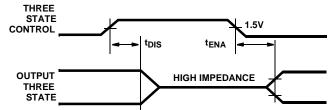

| Three-State Enable Time  | T <sub>ENA</sub> | Note 4            | -         | 25  | -         | 30  | ns    |

| Three-State Disable Time | T <sub>DIS</sub> | Note 4            | -         | 25  | -         | 30  | ns    |

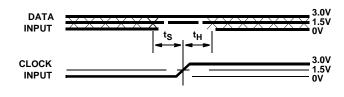

| Input Setup Time         | T <sub>S</sub>   |                   | 18        | -   | 20        | -   | ns    |

| Input Hold Time          | T <sub>H</sub>   |                   | 2         | -   | 2         | -   | ns    |

| Clock High Pulse Width   | T <sub>PWH</sub> |                   | 15        | -   | 20        | -   | ns    |

| Clock Low Pulse Width    | T <sub>PWL</sub> |                   | 15        | -   | 20        | -   | ns    |

| Output Rise Time         | t <sub>R</sub>   | From 0.8V to 2.0V | -         | 8   | -         | 8   | ns    |

| Output Fall Time         | t <sub>F</sub>   | From 2.0V to 0.8V | -         | 8   | -         | 8   | ns    |

#### NOTES:

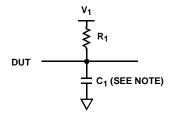

- 4. Transition is measured at  $\pm 200$ mV from steady state voltage with loading specified in AC Test Circuit;  $V_1 = 1.5$ V,  $R_1 = 500\Omega$  and  $C_L = 40$ pF.

- 5. For AC Test load, refer to AC Test Circuit with  $V_1$  = 2.4V,  $R_1$  = 500 $\Omega$  and  $C_L$  = 40pF.

# **AC Test Circuit**

# AC Testing Input, Output Waveforms

NOTE: Includes Stray and Jig Capacitance

NOTE: AC Testing: All Parameters tested as per test circuit. Input rise and fall times are driven at 1ns/V.

# **Timing Diagram**

FIGURE 9. SETUP AND HOLD TIME

FIGURE 10. THREE-STATE CONTROL

# Timing Diagram

FIGURE 11. HMA510 TIMING DIAGRAM

FIGURE 12. PRELOAD TIMING DIAGRAM

| All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.  Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

For information regarding Intersil Corporation and its products, see www.intersil.com

# Sales Office Headquarters

## NORTH AMERICA

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618

TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 **EUROPE** Intersil Europe Sarl

Ave. William Graisse, 3 1006 Lausanne Switzerland

TEL: +41 21 6140560 FAX: +41 21 6140579

#### **ASIA**

Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road TST, Kowloon Hong Kong

TEL: +852 2723 6339 FAX: +852 2730 1433