# 40MHz, 32-Channel Serial to Parallel Converter with Push-Pull Outputs

**Ordering Information**

|        | Package Options         |                          |                   |  |  |  |  |

|--------|-------------------------|--------------------------|-------------------|--|--|--|--|

| Device | 64 Pin Plastic Gullwing | 80-Lead Ceramic Gullwing | Die in Wafer Form |  |  |  |  |

| HV76   | HV7620PG                | HV7620DG                 | HV7620XW          |  |  |  |  |

#### **Features**

- □ Processed with HVCMOS® technology

- ☐ 5V CMOS logic and 12V supply rail

- ☐ Output voltage up to 200V

- Low power level shifting

- Source/sink current minimum 50mA

- □ 40MHz equivalent data rate

- Chip select

- □ Polarity function

- ☐ Forward and reverse shifting options (DIR pin)

- Latched outputs

### **General Description**

The HV76 is a low-voltage serial to high-voltage parallel converter with push-pull outputs. This device has been designed for use as a driver for color AC plasma displays.

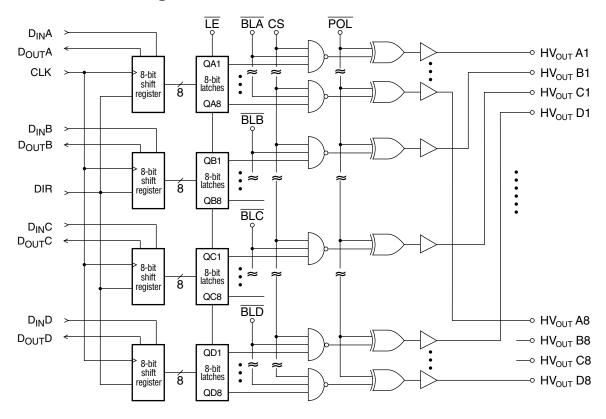

The device has 4 parallel 8-bit shift registers permitting data rate 4 times the speed of one. The data are clocked in simultaneously on all four data inputs with a single clock. Data are shifted in on a low to high transition of the clock. The latches and control logic perform the output enable function.

The DIR pin causes clockwise (CW) shifting of the data when connected to  $V_{\rm DD1}$ , and counterclockwise (CCW) shifting when connected to GND. Operation of the shift register is not affected by the  $\overline{\rm LE}$  (latch enable) input. Transfer of data from the shift registers to the latches occurs when the  $\overline{\rm LE}$  input is high. Data is stored in the latches when  $\overline{\rm LE}$  is low. The current source on the logic inputs provides active pull up when the input pins are open.

### **Absolute Maximum Ratings**

| Supply voltage <sup>1</sup> , V <sub>DD1</sub>  |                    | -0.5V to +15V                    |

|-------------------------------------------------|--------------------|----------------------------------|

| Supply voltage <sup>1</sup> , V <sub>DD2</sub>  |                    | -0.5V to +15V                    |

| Supply voltage <sup>1</sup> , V <sub>PP</sub>   |                    | -0.5V to +225V                   |

| Logic input levels <sup>1</sup>                 | -:                 | 2.0V to V <sub>DD1</sub> +2.0V   |

| Continuous total power dissipation <sup>2</sup> | Plastic<br>Ceramic | 1200mW<br>1900mW                 |

| Operating temperature range                     | Plastic<br>Ceramic | -40°C to +85°C<br>-55°C to 125°C |

| Storage temperature range                       |                    | -65°C to +150°C                  |

#### Notes:

- 1. All voltages are referenced to GND.

- For operation above 25°C ambient derate linearly to maximum operating temperature at 20mW/°C for plastic and at 19mW/°C for ceramic.

#### 02/96/022

# **Electrical Characteristics** (over recommended operating conditions unless noted) **DC Characteristics** ( $V_{DD1} = 5V$ , $V_{DD2} = 12V$ , $V_{PP} = 200V$ and $T_A = 25^{\circ}C$ )

| Symbol            | Parameters                                | Min  | Max | Units | Condition                                                  |

|-------------------|-------------------------------------------|------|-----|-------|------------------------------------------------------------|

| I <sub>DD1</sub>  | V <sub>DD1</sub> supply current           |      | 5   | mA    | f <sub>CLK</sub> =10MHz                                    |

| I <sub>DD2</sub>  | V <sub>DD2</sub> supply current           |      | 20  | mA    | $V_{DD2} = V_{DD2} \text{ max}$ $f_{CLK} = 10 \text{ MHz}$ |

| I <sub>PP</sub>   | High voltage supply current               |      | 2   | mA    | All output high or low                                     |

| I <sub>DD1Q</sub> | Quiescent V <sub>DD1</sub> supply current |      | 100 | μΑ    | All input = V <sub>DD1</sub>                               |

| I <sub>DD2Q</sub> | Quiescent V <sub>DD2</sub> supply current |      | 100 | μΑ    | All input = V <sub>DD1</sub>                               |

| V <sub>OH</sub>   | High-level output                         | 185  |     | V     | I <sub>O</sub> = -50mA                                     |

| $V_{OL}$          | Low-level output                          |      | 20  | V     | I <sub>0</sub> = 50mA                                      |

| I <sub>IH</sub>   | High-level logic input current            |      | 1.0 | μΑ    | $V_{IN} = V_{DD1}$                                         |

| I <sub>IL</sub>   | Low-level logic input current             |      | -10 | μΑ    | $V_{IN} = 0V$                                              |

| $V_{GG}$          | HVGND to LVGND voltage difference         | -1.0 | 1.0 | V     |                                                            |

### **AC Characteristics** (Logic signal inputs and data inputs have $t_r$ , $t_f \le 5$ ns. $V_{DD1} = 5V$ or 12V, $V_{DD2} = 12V$ , $V_{PP} = 200V$ )

| Symbol                              | Parameters                 | Min                            | Max | Units | Condition |                                    |

|-------------------------------------|----------------------------|--------------------------------|-----|-------|-----------|------------------------------------|

| f <sub>CLK</sub>                    | Clock frequency            | Clock frequency $V_{DD1} = 5V$ |     |       | MHz       | Per register C <sub>L</sub> = 15pF |

| CLK                                 | , ,                        | V <sub>DD1</sub> = 12V         |     | 5     | MHz       | Per register C <sub>L</sub> = 15pF |

| $t_{WL}, t_{WH}$                    | Clock width high or        | low                            | 40  |       | ns        |                                    |

| t <sub>su</sub>                     | Data set-up time           |                                | 20  |       | ns        |                                    |

| t <sub>H</sub>                      | Data hold time             |                                | 20  |       | ns        |                                    |

| t <sub>on</sub> , t <sub>off</sub>  | Time from LE to HV         | ,<br>OUT                       |     | 275   | ns        | C <sub>L</sub> = 15pF              |

| t <sub>wLE</sub>                    | Width of LE pulse          |                                | 25  |       | ns        |                                    |

| t <sub>DLE</sub>                    | Delay time clock to        | LE low to high                 | 50  |       | ns        |                                    |

| t <sub>SLE</sub>                    | LE setup time befor        | e clock rises                  | 20  |       | ns        |                                    |

| t <sub>DLF</sub> , t <sub>DLN</sub> | BL or CS low to hig        | h to HV <sub>оυт</sub>         |     | 250   | ns        |                                    |

| t <sub>cof</sub> , t <sub>con</sub> | Clock to HV <sub>OUT</sub> |                                | 275 | ns    |           |                                    |

| t <sub>DLH</sub>                    | Delay time clock to        | data low to high               |     | 100   | ns        | C <sub>L</sub> = 15pF              |

| t <sub>DHL</sub>                    | Delay time clock to        | data high to low               |     | 100   | ns        | C <sub>L</sub> = 15pF              |

## **Recommended Operating Conditions**

| Symbol                             | Parameters                                                  |                        | Min                    | Max                   | Unit |

|------------------------------------|-------------------------------------------------------------|------------------------|------------------------|-----------------------|------|

| V <sub>DD1</sub>                   | Logic supply voltage                                        |                        | 4.5                    | $V_{_{\mathrm{DD2}}}$ | V    |

| $V_{_{\mathrm{DD2}}}$              | 12V supply voltage                                          |                        | 10.8                   | 13.2                  | V    |

| V <sub>PP</sub>                    | High voltage supply voltage                                 |                        | 50                     | 200                   | V    |

| V <sub>IH</sub>                    | High-level input voltage                                    |                        | V <sub>DD1</sub> -0.5V | $V_{_{\mathrm{DD1}}}$ | V    |

| V <sub>IL</sub>                    | Low-level input voltage                                     |                        | 0                      | 0.5                   | V    |

| f <sub>clk</sub>                   | Clock frequency                                             | $V_{DD1} = 5V$         |                        | 10                    | MHz  |

|                                    |                                                             | V <sub>DD1</sub> = 12V |                        | 5                     | MHz  |

| T <sub>A</sub>                     | Operating free-air temperature                              | Plastic                | -40                    | +85                   | °C   |

|                                    |                                                             | Ceramic                | -55                    | +125                  | °C   |

| I <sub>OD</sub>                    | Allowable pulsed current through ouptut diodes <sup>1</sup> |                        |                        | 500                   | mA   |

| <br>GND(Vpp)                       | Allowable pulsed V <sub>PP</sub> or HVGND of                | current <sup>1</sup>   |                        | 16                    | Α    |

| V <sub>PP(SLEW)</sub> <sup>2</sup> | Slew rate of V <sub>PP</sub>                                |                        |                        | 340                   | V/µs |

#### Notes

<sup>1.</sup> The current pulse width = 500ns, duty cycle = 5%.

<sup>2.</sup>This device cannot be hot-switched for output frequency greater than 500Hz. For output frequency greater than 500Hz, V<sub>pp</sub> must be ramped.

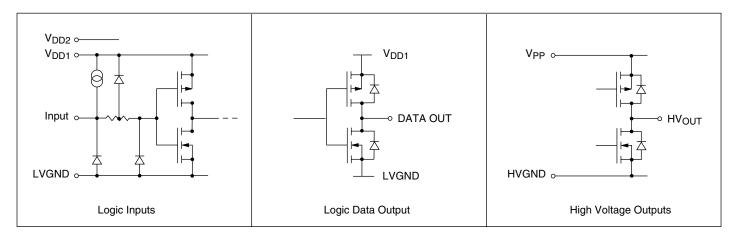

# **Input and Output Equivalent Circuits**

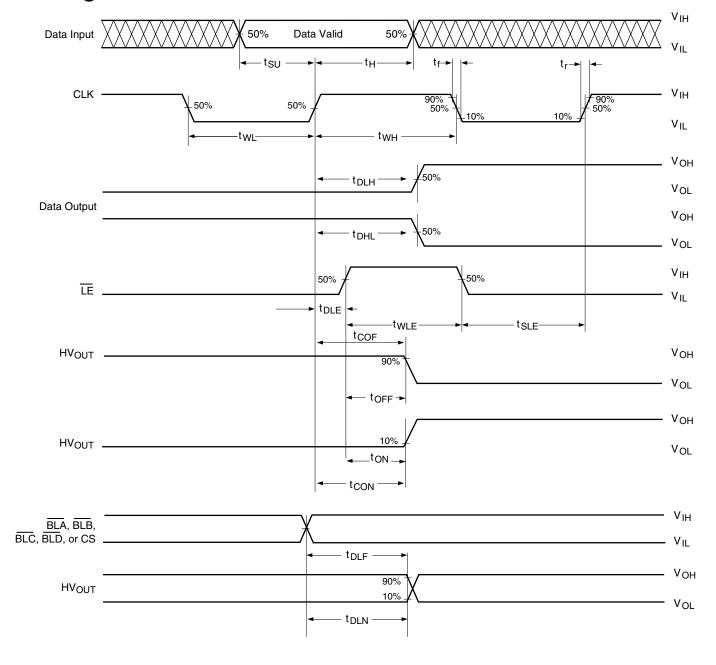

### **Switching Waveforms**

## **Functional Block Diagram**

### **Function Table**

|                  | Inputs            |                   |                   |                   |     |    |     |     |     | HV Outputs |     |    |     |                |                  |                  |                            |

|------------------|-------------------|-------------------|-------------------|-------------------|-----|----|-----|-----|-----|------------|-----|----|-----|----------------|------------------|------------------|----------------------------|

| Function         | D <sub>IN</sub> A | D <sub>IN</sub> B | D <sub>IN</sub> C | D <sub>IN</sub> D | CLK | LE | DIR | BLA | BLB | BLC        | BLD | cs | POL | Α              | В                | С                | D                          |

| All O/P High     | Х                 | Х                 | Х                 | Х                 | Х   | Х  | Х   | Х   | Х   | Х          | Х   | L  | L   | Н              | Н                | Н                | Н                          |

| All O/P Low      | Х                 | Х                 | Х                 | Х                 | Х   | Х  | Х   | Х   | Х   | Х          | Х   | L  | Н   | L              | L                | L                | L                          |

| "A" Outputs Low  | Х                 | Х                 | Х                 | Х                 | Х   | Х  | Х   | L   | Х   | Х          | Х   | Х  | Н   | L              | *                | *                | *                          |

| Normal Polarity  | Х                 | Х                 | Х                 | Х                 | Х   | Х  | Х   | Н   | Н   | Н          | Н   | Н  | Н   | No Inversion   |                  |                  |                            |

| Outputs Inverted | Х                 | Х                 | Х                 | Х                 | Х   | Х  | Х   | Н   | Н   | Н          | Н   | Н  | L   |                | Inver            | sion             |                            |

| Transparent Mode | Н                 | L                 | L                 | L                 | 1   | Н  | Х   | Н   | Н   | Н          | Н   | Н  | Н   | Н              | L                | L                | L                          |

| Data Stored      | Х                 | Х                 | Х                 | Х                 | Х   | L  | Х   | Н   | Н   | Н          | Н   | Н  | Н   |                | Stored           | Data             |                            |

| Shift CW         | Х                 | Х                 | Х                 | Х                 | 1   | Н  | Н   | Н   | Н   | Н          | Н   | Н  | Х   | A <sub>N</sub> | B <sub>N</sub>   | C <sub>N</sub>   | D <sub>N</sub>             |

|                  |                   |                   |                   |                   |     |    |     |     |     |            |     |    |     | $A_{N+1}$      | B→<br>N+1        | C→               | D→<br>N+1                  |

| Shift CCW        | Х                 | Х                 | Х                 | Х                 | 1   | Н  | L   | Н   | Н   | Н          | Н   | Н  | Х   | A <sub>N</sub> | B <sub>N</sub>   | C <sub>N</sub>   | D <sub>N</sub>             |

|                  |                   |                   |                   |                   |     |    |     |     |     |            |     |    |     | $A_{N-1}$      | B <sub>N-1</sub> | C <sub>N-1</sub> | $\overrightarrow{D_{N-1}}$ |

#### Notes

$H = High level, L = Low level, X = Irrelevant, \uparrow = Low to high transition.$

Power-up sequence:

GND (HV, LV)

$V_{DD2} \ V_{DD1}$

Logic Input Signals

$V_{PP}$

To power down reverse the sequence above.

The  $V_{PP}$  should not drop below  $V_{DD}$  or float during operation.

<sup>\* =</sup> Dependent on previous stage's state before the last  $\overrightarrow{CLK} \uparrow \text{ for last } \overrightarrow{LE} \text{ high.}$

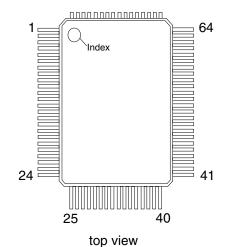

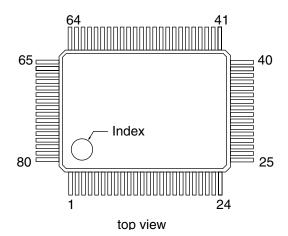

# **Pin Configurations**

| HV76 |                      |     |                      |

|------|----------------------|-----|----------------------|

| Pin  | Function             | Pin | <b>Function</b>      |

| 1    | HVGND                | 33  | CS                   |

| 2    | $V_{pp}$             | 34  | $D_{OUT}B$           |

| 3    | HV <sub>OUT</sub> D8 | 35  | D <sub>IN</sub> B    |

| 4    | HV <sub>OUT</sub> C8 | 36  | $D_{IN}A$            |

| 5    | HV <sub>OUT</sub> B8 | 37  | $D_{OUT}^{m}A$       |

| 6    | $HV_{OUT}A8$         | 38  | CLK                  |

| 7    | HV <sub>OUT</sub> D7 | 39  | BLA                  |

| 8    | HV <sub>OUT</sub> C7 | 40  | BLB                  |

| 9    | $HV_{OUT}B7$         | 41  | V <sub>DD1</sub>     |

| 10   | $HV_{OUT}A7$         | 42  | LVGND                |

| 11   | HV <sub>OUT</sub> D6 | 43  | N/C                  |

| 12   | HV <sub>OUT</sub> C6 | 44  | HVGND                |

| 13   | HV <sub>OUT</sub> B6 | 45  | HVGND                |

| 14   | HV <sub>OUT</sub> A6 | 46  | $V_{pp}$             |

| 15   | HV <sub>OUT</sub> D5 | 47  | $HV_{OUT}D4$         |

| 16   | HV <sub>OUT</sub> C5 | 48  | HV <sub>out</sub> C4 |

| 17   | HV <sub>OUT</sub> B5 | 49  | HV <sub>out</sub> B4 |

| 18   | HV <sub>out</sub> A5 | 50  | $HV_{OUT}A4$         |

| 19   | $V_{pp}$             | 51  | $HV_{OUT}D3$         |

| 20   | HVGND                | 52  | $HV_{OUT}C3$         |

| 21   | HVGND                | 53  | $HV_{OUT}B3$         |

| 22   | V <sub>DD2</sub>     | 54  | $HV_{OUT}A3$         |

| 23   | BLC                  | 55  | $HV_{OUT}D2$         |

| 24   | BLD                  | 56  | HV <sub>OUT</sub> C2 |

| 25   | LE                   | 57  | $HV_{OUT}B2$         |

| 26   | $D_{OUT}D$           | 58  | $HV_{OUT}A2$         |

| 27   | $D_{IN}D$            | 59  | $HV_{OUT}D1$         |

| 28   | $D_{IN}C$            | 60  | HV <sub>out</sub> C1 |

| 29   | D <sub>OUT</sub> C   | 61  | $HV_{OUT}B1$         |

| 30   | POL                  | 62  | $HV_{OUT}A1$         |

| 31   | LVGND                | 63  | $V_{PP}$             |

| 32   | DIR                  | 64  | HVGND                |

<sup>\*</sup>Pins 65 to 80 are N/C (ceramic only)

## Package Outline

3-sided Plastic 64-pin Gullwing Package

80-pin Ceramic Gullwing Package

Supertex inc.