# LA1175, 1175M

# FM Front End For Car Radio, Home Stereo Applications

#### **Functions**

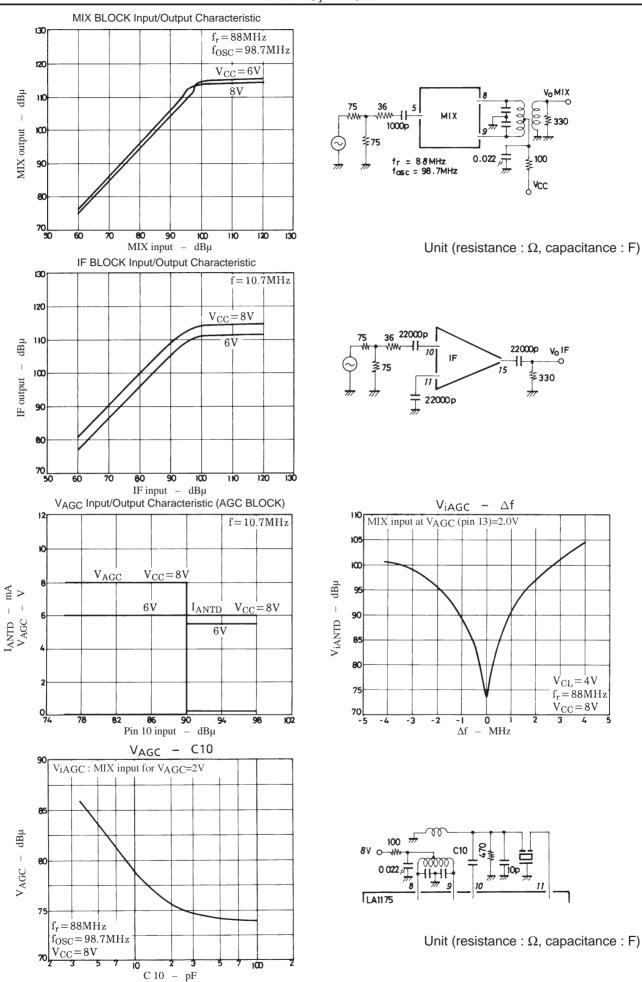

Double-balanced type MIX, PIN diode drive AGC output, MOS FET gate drive AGC output, keyed AGC, differential IF amplifier, buffer amplifier for oscillation, local oscillation.

#### **Features**

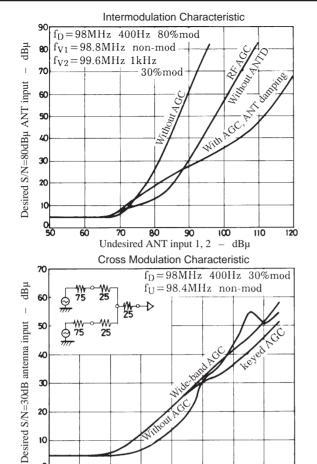

- By using the keyed AGC system, which is effective in improving the sensitivity suppression characteristic, in combination with the antenna damping AGC (PIN diode driver on chip) and MOS FET 2nd gate drive AGC, the intermodulation characteristic for a large undesired signal is greatly improved. It is also possible to use the keyed AGC system in combination with the antenna damping AGC or MOS FET 2nd gate drive AGC.

- The temperature characteristic and noise figure are improved. The same supply voltage makes it easy to use the LA1175, 1175M.

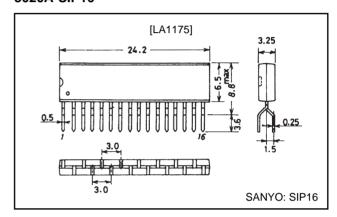

#### **Package Dimensions**

unit: mm

#### 3020A-SIP16

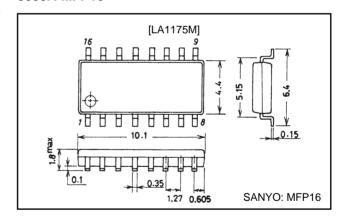

unit: mm

#### 3035A-MFP16

# Specifications

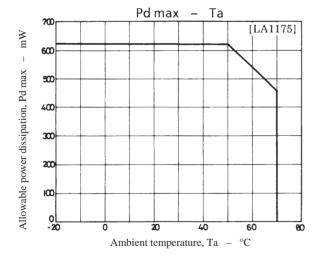

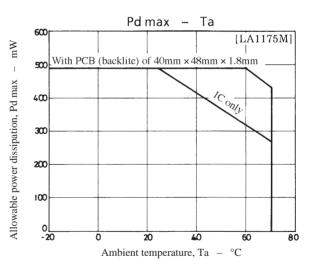

**Maximum Ratings** at Ta=25°C

| maximam raumgo at 1a-25 C   |                     |                           |             |      |  |  |  |  |

|-----------------------------|---------------------|---------------------------|-------------|------|--|--|--|--|

| Parameter                   | Symbol              | Conditions                | Ratings     | Unit |  |  |  |  |

| Maximum supply voltage      | V <sub>CC</sub> max | Pins 4, 14                | 9.5         | V    |  |  |  |  |

|                             |                     | Pins 8, 9                 | 15          | V    |  |  |  |  |

| Allowable power dissipation | Pd max              | LA1175 : Ta≤70°C          | 460         | mW   |  |  |  |  |

|                             |                     | LA1175M : Ta≤70°C         | 435         | mW   |  |  |  |  |

|                             |                     | Mounted on PCB (bakelite) |             |      |  |  |  |  |

|                             |                     | of 40mm×48mm×1.8mm²       |             |      |  |  |  |  |

| Operating temperature       | Topr                |                           | -20 to +70  | °C   |  |  |  |  |

| Storage temperature         | Tstg                |                           | -40 to +125 | °C   |  |  |  |  |

# **Operating Conditions** at Ta=25°C

| Parameter                  | Symbol             | Conditions      | Ratings | Unit |

|----------------------------|--------------------|-----------------|---------|------|

| Recommended supply voltage | V <sub>CC</sub>    | Pin 4, 8, 9, 14 | 8       | V    |

| Operating voltagerange     | V <sub>CC</sub> op |                 | 8 to 9  | V    |

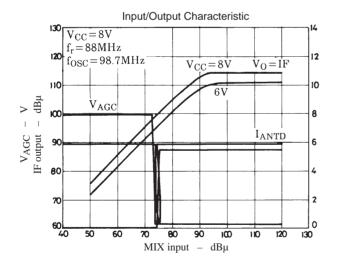

# **Electrical Characteristics** at Ta=25°C, V<sub>CC</sub>=8V, See specified Test Circuit.

| Parameter                                                | Symbol                | Conditions                                      | Ratings |      |      | Unit  |

|----------------------------------------------------------|-----------------------|-------------------------------------------------|---------|------|------|-------|

| r arameter                                               | Symbol                | Conditions                                      | min     | typ  | max  | Offic |

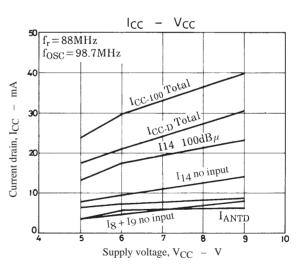

| Current drain                                            | ICC                   | Pins 4, 8, 9, 14 : no input                     | 23.0    | 28.0 | 33.0 | mA    |

| AGC high-level voltage                                   | V <sub>AGCH</sub>     | $V_{IN}$ =0dB $\mu$ , $V_{CL}$ =4 $V$           | 7.6     | 7.9  |      | V     |

| AGC low-level voltage                                    | V <sub>AGCL</sub>     | $V_{IN}$ =100dB $\mu$ , $V_{CL}$ =4 $V$         |         | 0.2  | 0.7  | V     |

| IF input resistance                                      | R <sub>IN</sub>       |                                                 | 260     | 330  | 400  | Ω     |

| AGC control input                                        | V <sub>CL</sub> 7     | V <sub>IN</sub> =100dBμ, V <sub>AGC</sub> =7V   |         | 0.25 | 0.5  | V     |

|                                                          | V <sub>CL</sub> 2     | V <sub>IN</sub> =100dBµ, V <sub>AGC</sub> =2V   | 1.1     | 1.6  | 2.1  | V     |

| Voltage gain                                             | A <sub>V</sub>        | LA1175 : V <sub>IN</sub> =75dBµ                 | 99      | 102  | 105  | dΒμ   |

|                                                          |                       | LA1175M : V <sub>IN</sub> =75dBµ                | 97      | 100  | 103  | dΒμ   |

| nput limiting voltage V <sub>INIim</sub> LA1175 : Refere |                       | LA1175 : Referenced to V <sub>IN</sub> =110dBµ  | 81      | 88   | 95   | dΒμ   |

|                                                          |                       | LA1175M : Referenced to V <sub>IN</sub> =110dBµ | 80      | 87   | 94   | dΒμ   |

| AGC input voltage                                        | V <sub>iAGC</sub>     | V <sub>AGC</sub> =2V                            | 67      | 74   | 81   | dΒμ   |

| Saturation output voltage                                | Vout                  | LA1175 : V <sub>IN</sub> =110dBμ                | 110     | 114  |      | dΒμ   |

|                                                          |                       | LA1175M : V <sub>IN</sub> =110dBμ               | 100     | 113  |      | dΒμ   |

| OSC BUFF output                                          | V <sub>OSC</sub> BUFF | 1kΩ load                                        | 105     | 109  |      | dΒμ   |

| ANT damping drive                                        | I <sub>ANT-D</sub>    | V <sub>IN</sub> =100dBµ                         | 4.5     | 6.0  | 8.0  | mA    |

| current                                                  |                       |                                                 |         |      |      |       |

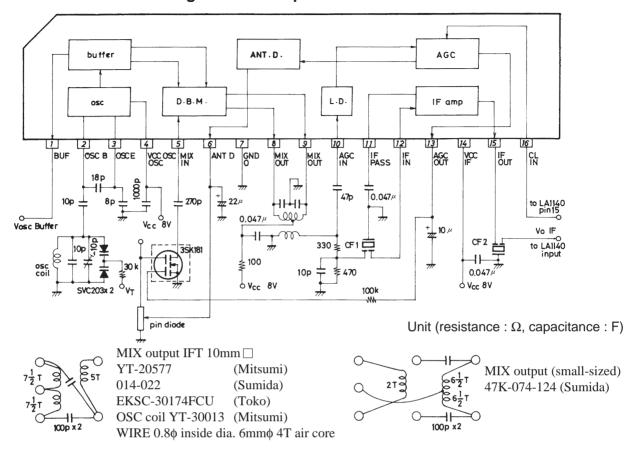

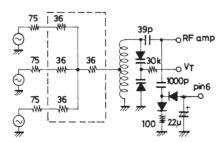

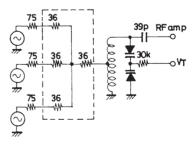

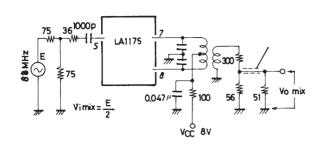

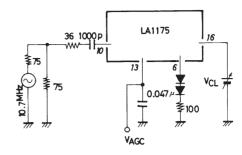

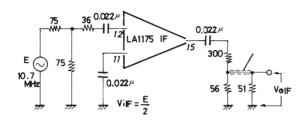

### **Equivalent Circuit Block Diagram and Peripheral Circuit: LA1175**

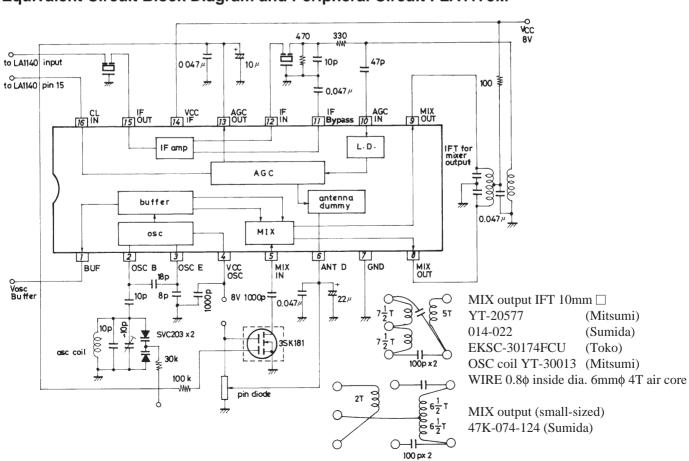

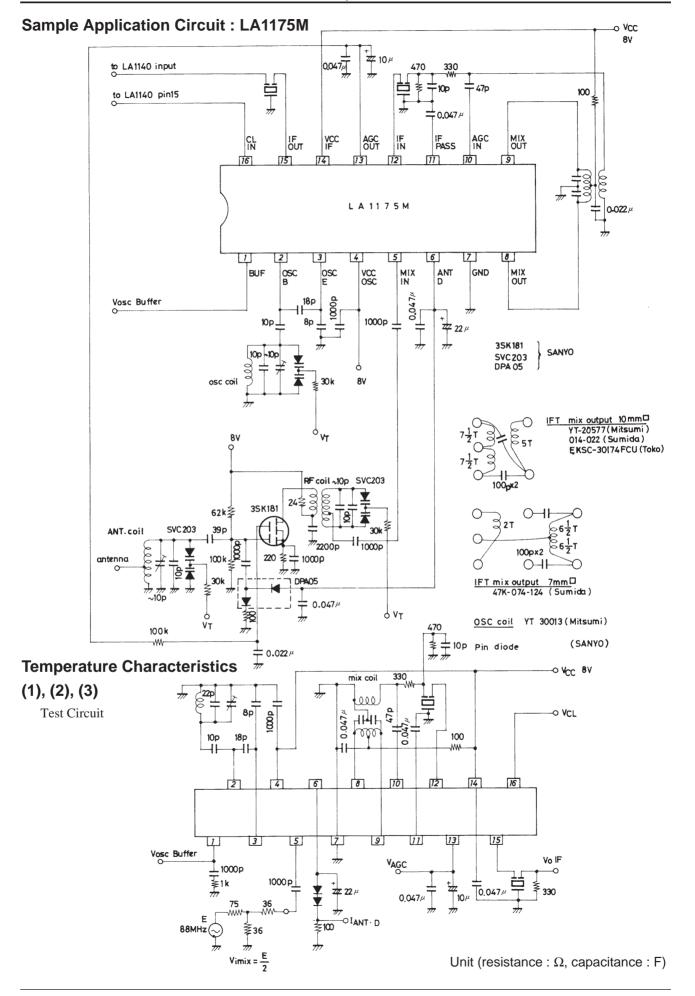

#### **Equivalent Circuit Block Diagram and Peripheral Circuit: LA1175M**

Unit (resistance :  $\Omega$ , capacitance : F)

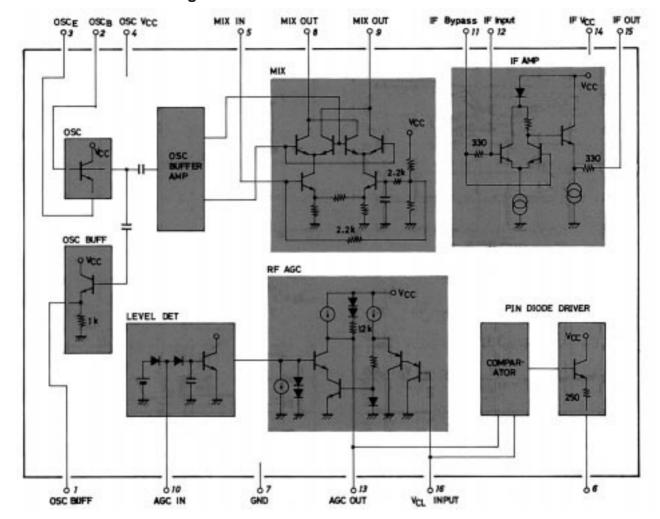

### **Internal Connection Diagram: LA1175**

Unit (resistance :  $\Omega$ , capacitance : F)

Unit (resistance :  $\Omega$ )

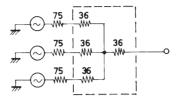

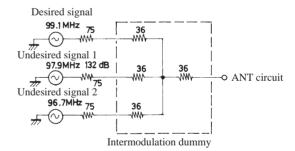

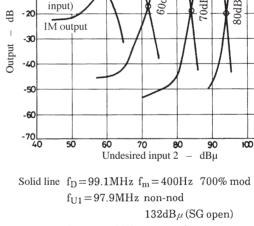

Improvement of IM characteristic in strong undesired input signal mode when ANT damping AGC is used (LA1174). Test conditions

120

f<sub>D</sub>: 99.1MHz, f<sub>m</sub>=400Hz 100% mod

$f_{U1}:97.9MHz$  non-mod SG open  $132dB\mu$

Undesired antenna input - dBµ

$f_{U2}:96.7MHz\ f_m=1kHz\ 100\%\ mod$

Unit (resistance :  $\Omega$ )

#### **Cross point**

The open input level of undesired signal 2 at which the IM output and desired signal output are at the same level.

IM output • Desired signal : Non-mod at each specified input

> : Non-mod at input 132dBu (SG open) • Undesired signal 1

• Undesired signal 2 : 100% mod with input variable

Desired signal output • Desired signal : 100% at each specified input

> • Undesired signal 1 : Non-mod at input 132dBµ (SG open)

: Non-mod with input variable • Undesired signal 2

|       | Desired input level                        | 50dBµ   | 60dBµ  | 70dBµ  | 80dBµ              |                  |

|-------|--------------------------------------------|---------|--------|--------|--------------------|------------------|

| point | With ANT damping<br>RF AGC and<br>ANTD AGC | 90.5dBμ | 109dBµ | 123dBµ | Test<br>impossible | Refer to Fig. A. |

| Cross | Without ANT<br>damping<br>RF AGC only      | 59.5dBμ | 72dBμ  | 89dBµ  | 98dBµ              | Refer to Fig. B. |

|       | Improvement                                | 31dB    | 37dB   | 34dB   |                    |                  |

Solid line  $f_D = 99.1MHz$   $f_m = 400Hz$  700% mod  $f_{U1} = 97.9MHz$  non-nod

132dBµ (SG open)

$f_{U2} = 96.7MHz$  non-mod Broken line f<sub>D</sub>=99.1MHz non-mod

$f_{U1} = 97.9MHz$  non-mod

$132 dB\mu$  (SG open)

f<sub>U2</sub>=96.7MHz 1kHz 100% mod

Desired

output

50dBu

(Desired

-10

$f_{U2} = 96.7MHz$  non-mod

Fig. B Intermodulation Characteristic (with ANT damping)

Broken line  $f_D = 99.1 MHz$  non-mod

$f_{U1} = 97.9MHz$  non-mod

$132 dB\mu$  (SG open)

$f_{112} = 96.7 \text{MHz}$  1kHz 100% mod

Intermodulation dummy

Intermodulation dummy

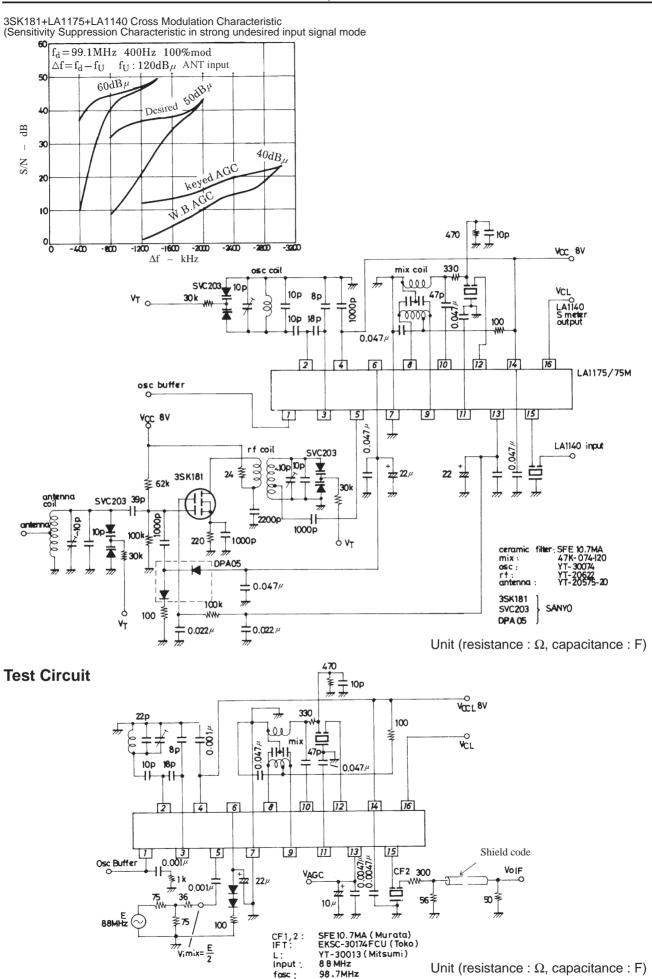

Unit (resistance :  $\Omega$ , capacitance F)

110

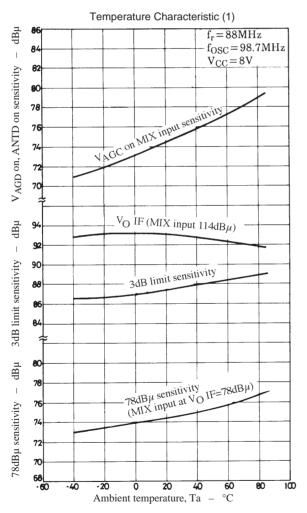

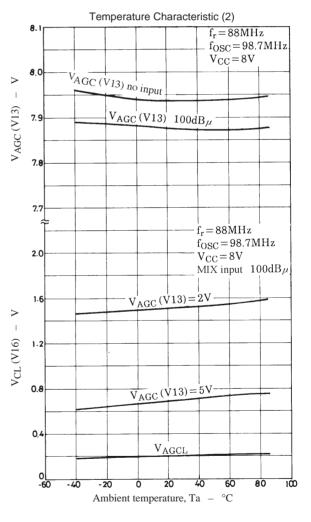

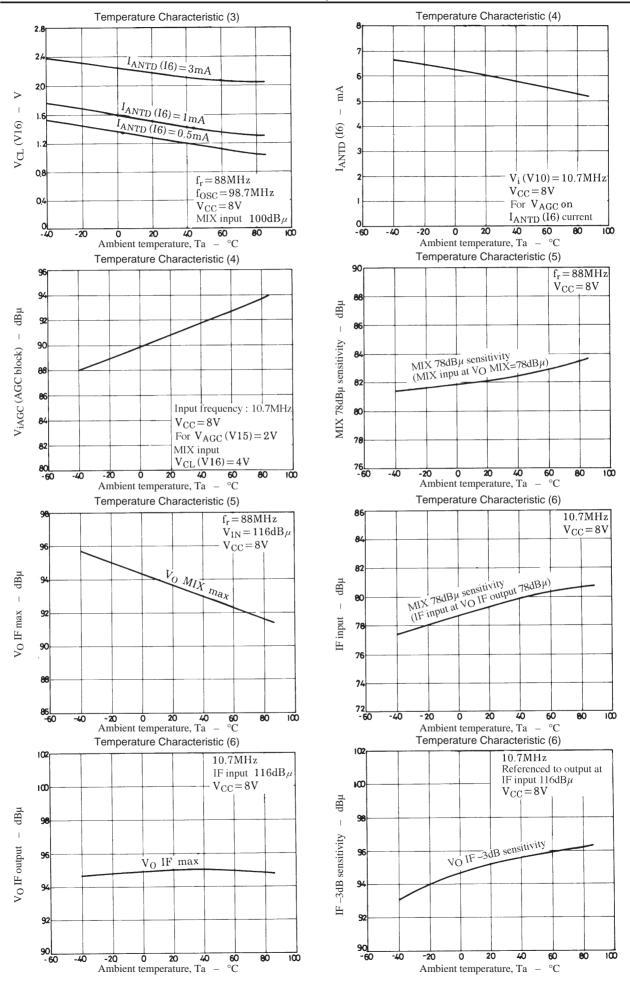

## **Temperature Characteristics (4)**

## **Temperature Characteristics (5)**

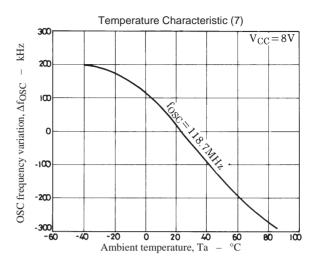

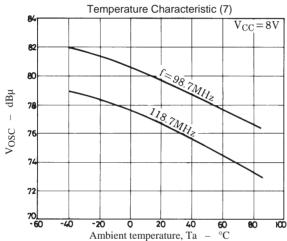

### **Temperature Characteristics (6)**

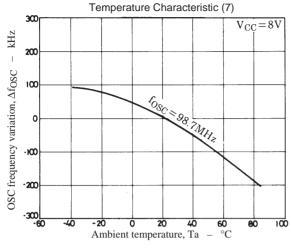

## **Temperature Characteristics (7)**

Unit (resistance :  $\Omega$ , capacitance : F)

## Description of AGC circuit in the LA1175, 1175M

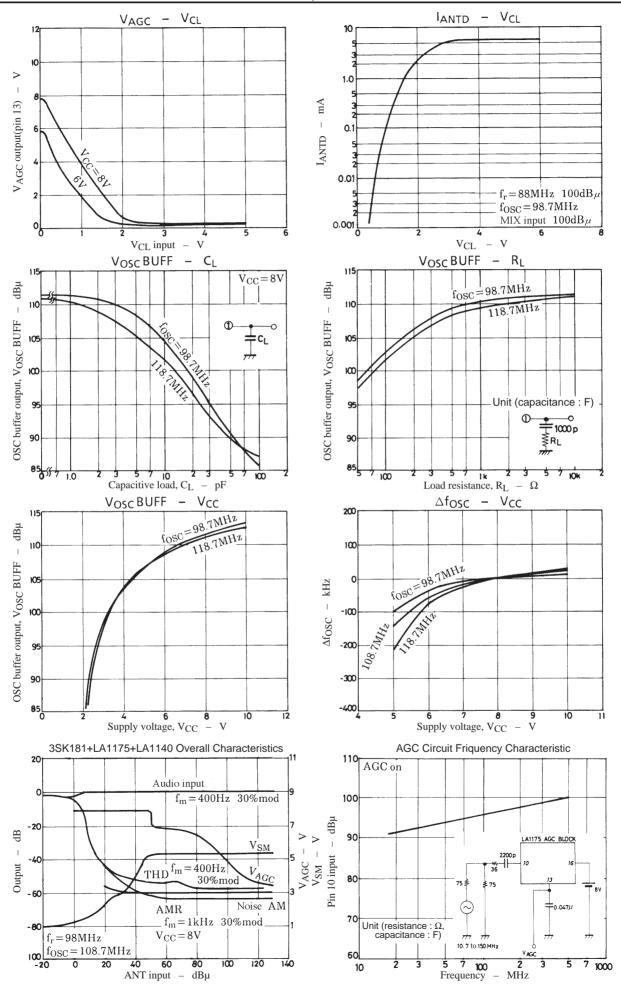

The LA1175, 1175M are designed so that AGC is operated in the order shown below.

ANT damping (PIN diode) → MOS FET 2nd gate voltage control (Attenuation)20dB (Attenuation)60dB

The following are the reasons why AGC is operated in this order.

- (1) When a signal of  $110dB\mu$  or greater is applied to the varactor in the ANT circuit, intermodulation may occur. In this case, if AGC is operated in the order of MOS FET 2nd gate control AGC  $\rightarrow$  ANT damping (PIN diode), the input to the varactor in the ANT circuit is not restricted unless a strong signal with AGC attenuation 60dB or greater is given. Therefore, AGC should be operated in the order shown above.

- (2) If the two AGC loops (AGC loop (ANT damping) and AGC loop (MOS FET 2nd gate control)) are operated simultaneously, the transient response of AGC loses stability. Therefore, the order shown below is impracticable.

MOS FET 2nd gate control  $\rightarrow$  ANT damping  $\rightarrow$  MOS FET 2nd gate control.

#### Relation between keyed AGC and two AGC loops

For the LA1170, keyed AGC provides AGC attenuation control (RF MOS FET 2nd gate). For the LA1175, 1175M, however, there are two AGC loops as shown above. Therefore, keyed AGC must be applied to both of the two AGC loops. The LA1175, 1175M contain the ANT damping circuit to improve intermodulation in a strong field, but the prevention of intermodulation in a strong field and the improvement of the sensitivity suppression characteristic by keyed AGC are mutually exclusive as mentioned below.

Conditions Desired signal Weak field

Undesired signals 1, 2 Strong field (Field strength in which the ANT circuit may cause

intermodulation to occur)

If keyed AGC is operated to cause AGC-OFF mode to be entered when a desired signal is received, the varactor in the ANT circuit may be distorted and intermodulation may occur, which means that it is meaningless for the LA1175, 1175M to contain the ANT damping circuit because it produces no effect. Therefore, the effect of the keyed AGC circuit in the LA1175, 1175M on the ANT damping circuit is made less than that in the LA1170 so that the abovementioned problem does not arise. However, if the LA1175, 1175M are used under the same conditions as for the LA1170 (no ANT damping, pin 6 open), keyed AGC is operated in the same manner as for the LA1170.

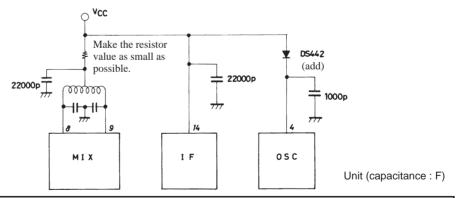

#### Application circuit used in a very strong field

Since the LA1175, 1175M are designed to be operated from single supply, the dynamic range of the MIX output becomes narrower as compared with the dual-supply type ( $V_{CC}$  MIX=12V, other=8V) heretofore in use. IF an adjacent interference channel signal is very strong, the intermodulation characteristic at  $\Delta f$ =400kHz is deteriorated, because the dynamic range of the MIX output exceeds the limit, which causes a distortion to occur.

The following three countermeasures are available.

- Q of the MIX coil is made higher to provide a higher selectivity.

(Must be balanced with the detection band of the wide-band AGC)

- 2. The LA1175, 1175M are operated from dual supplies (Most ideal).

- 3. The application circuit shown below is used.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property lose.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibilty for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 1997. Specifications and information herein are subject to change without notice.