**CMOS LSI**

SINGLE-CHIP 4-BIT MICROCOMPUTER (LOW-THRESHOLD INPUT, ON-CHIP FLT DRIVER)

The LC6514B is a microcomputer with FLT drivers. It is identical with the LC6510C in the internal architecture and instruction set. Since the normal/low-threshold level of input port A can be selected by option and the on-chip pull-down resistor can be bitwise connected to the FLT driver by option, the number of external parts used in the user equipment can be minimized, reducing the cost considerably.

(Note) The LC6514B heretofore in use has been improved by changing the value of the pull-down resistor to be contained in FLT drivers as shown below. When using the LC6514B, fully check that the new resistor value meets your application specifications.

|                                   | New r    | esistor va | alue  | 0     | old resiste | or value |             |

|-----------------------------------|----------|------------|-------|-------|-------------|----------|-------------|

|                                   | min      | typ        | max   | min   | typ         | max      |             |

| "L"-level output current IOL      | 0.190    | 0.362      | 0.760 | 0.108 | 0.304       | 0.543    | mΑ          |

| (Output pull-down resistance) (Rp | D) (200) | (105)      | (50)  | (350) | (125)       | (70)     | $(k\Omega)$ |

#### Features

- · Low power dissipation

- · ROM capacity: 4096 x 8 bits

- RAM capacity: 256 x 4 bits

- Subroutine stack: 8 levels (common with interrupt)

- · On-chip OSC circuit

- 800kHz typ. CR OSC:

- Ceramic OSC: 400kHz, 800kHz, 1000kHz

- External input: 1290kHz max.

- Power-down by 2 standby modes

- HALT mode: Power dissipation saving by program standby during normal operation

- HOLD mode: Power supply backup during power failure

- Input/output ports

- Input: 4 bits x 1 port

- 3 bits x 1 port

- Input/output: 4 bits x 2 ports Output: 4 bits x 4 ports

- 2 bits x 1 port

- Interrupt

- External interrupt:

- Internal timer interrupt: 1

- · On-chip 4-bit prescaler and 8-bit program timer

- Instruction cycle time: 3.1μs (at 1290kHz)

- · Supply voltage

- Normal operation: 4.0 to 6.0V

- Memory hold: 1.8 to 6.0V

- Instruction set common to the LC6502, LC6505 (BANK instruction added)

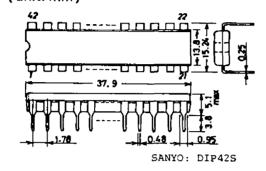

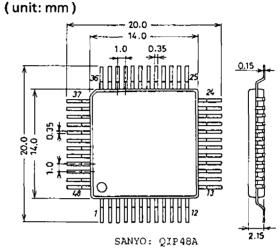

# Package: DIP42S (shrink) QIP48

# Package Dimensions 3025B-D42SIC (unit: mm)

# Package Dimensions 3052A-Q48AIC

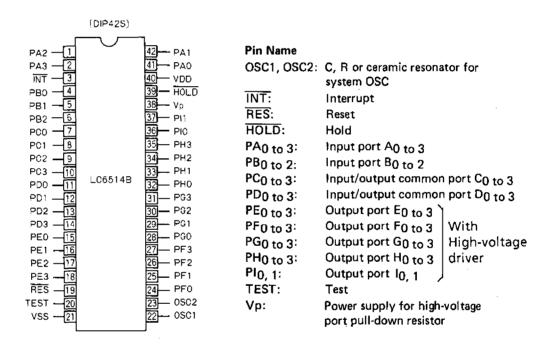

### Pin Assignment

### [QIP48]

When mounting the QIP package version on the board, do not dip it in solder.

NC pin: No connection

# LC6514B

| Pin Descrip          | otion            |                                                                                                                                                                                                                                                                                                     |

|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | Input/<br>Output | Function                                                                                                                                                                                                                                                                                            |

| INT                  | Input            | Interrupt request input pin.                                                                                                                                                                                                                                                                        |

| HOLD                 | Input            | HOLD mode request input pin (Differs from the LC6502/05 in function.)  Capable of being used as a general-purpose single-bit input port unless the standby mode is used.                                                                                                                            |

| RES                  | Input            | Reset input pin.                                                                                                                                                                                                                                                                                    |

| PA <sub>0 to</sub> 3 | Input            | Input port An to An (Normal voltage). Capable of 4-bit input and single-bit decision for branch. Used also for HALT mode release request input. Low threshold input for 4 bits selectable by option.                                                                                                |

| PB <sub>0 to 2</sub> | Input            | Input port B <sub>0 to</sub> B <sub>2</sub> (Normal voltage)  Capable of 3-bit input and single-bit decision for branch.                                                                                                                                                                            |

| PC <sub>0 to 3</sub> | Input/<br>output | Input/output common port C <sub>0</sub> to C <sub>3</sub> (Normal voltage).  Capable of 4-bit input and single-bit decision for branch during input.  Capable of 4-bit output and single-bit set/reset during output.                                                                               |

| PD <sub>0 to 3</sub> | Input/<br>output | Input/output common port D <sub>0</sub> to D <sub>3</sub> (Normal voltage).  Capable of 4-bit input and single-bit decision for branch during input.  Capable of 4-bit output and single-bit set/reset during output.                                                                               |

| PE <sub>O to</sub> 3 | Output           | Output port En to En (with high-voltage segment driver).  Capable of 4-bit output and single-bit set/reset.  Capable of 4-bit input of output latch contents and single-bit decision of output latch for branch.  Use/nonuse of pull-down resistor bitwise selectable by option.                    |

| PF <sub>0 to</sub> 3 | Output           | Output port Fg to Fg (with high-voltage segment driver). Capable of 4-bit output and single-bit set/reset. Capable of 4-bit input of output latch contents and single-bit decision of output latch for branch. Use/nonuse of pull-down resistor bitwise selectable by option.                       |

| PG <sub>D to</sub> 3 | Output           | Output port G <sub>0</sub> to G <sub>3</sub> (with high-voltage digit driver). Capable of 4-bit output and single-bit set/reset. Capable of 4-bit input of output latch contents and single-bit decision of output latch for branch. Use/nonuse of pull-down resistor bitwise selectable by option. |

| PH <sub>0 to</sub> 3 | Output           | Output port H <sub>D</sub> to H <sub>3</sub> (with high-voltage digit driver). Capable of 4-bit output and single-bit set/reset. Capable of 4-bit input of output latch contents and single-bit decision of output latch for branch. Use/nonuse of pull-down resistor bitwise selectable by option. |

| PI0, 1               | Output           | Output port I <sub>O</sub> , I <sub>1</sub> (with high-voltage digit driver). Capable of 2-bit output and single-bit set/reset. Capable of 2-bit input of output latch contents and single-bit decision of output latch for branch. Use/nonuse of pull-down resistor bitwise selectable by option.  |

| OSC1                 | Input            | Pin for supplying external clock.  If the internal clock mode is used, C, R or a ceramic resonator is connected to this pin and pin OSC2.                                                                                                                                                           |

| OSC2                 | Output           | Pin for externally connecting a resonance circuit for the internal clock mode.                                                                                                                                                                                                                      |

| V <sub>DD</sub>      | Input            | Power supply pin. Normally connected to +5V.                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>      | _                | Connected to 0V power supply.                                                                                                                                                                                                                                                                       |

| Vp                   | Input            | Power supply for high-voltage port pull-down resistor.                                                                                                                                                                                                                                              |

| TEST                 | Input            | LSI test pin. Normally connected to V <sub>SS</sub> (0V).                                                                                                                                                                                                                                           |

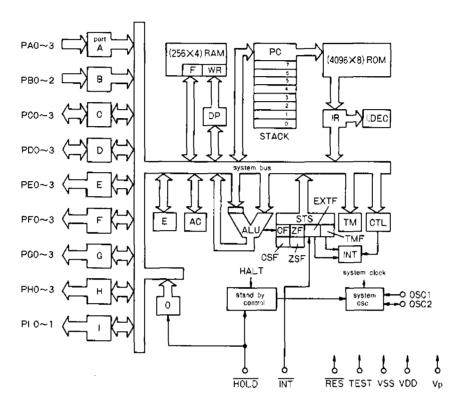

# System Block Diagram

| RAM: | Data memory               | ROM:              | Program memory                  |

|------|---------------------------|-------------------|---------------------------------|

| F:   | Flag                      | PC:               | Program counter                 |

| WR:  | Working register          | INT:              | Interrupt control               |

| AC:  | Accumulator               | IR:               | Instruction register            |

| ALU: | Arithmetic and logic unit | I.DEC:            | Instruction decoder             |

| DP:  | Data pointer              | CF, CSF:          | Carry flag                      |

| E:   | E register                |                   | Carry save flag                 |

| CTL: | Control register          | <b>ZF</b> , Z\$F: | Zero flag                       |

| OSC: | Oscillator                |                   | Zero save flag                  |

| TM:  | Timer                     | EXTF:             | External interrupt request flag |

| STS: | Status register           | TMF:              | Internal interrupt request flag |

|      |                           |                   |                                 |

# Absolute Maximum Ratings at Ta=25°C, VSS=0V (VDD=5V±20% unless otherwise specified)

|                        |            |                                        |                       | unit          |

|------------------------|------------|----------------------------------------|-----------------------|---------------|

| Maximum Supply Voltage | VDD max    |                                        | $-0.3 \sim +7.0$      | V             |

| Input Voltage          | VIN (1)    | Inputs other than Vp                   | $-0.3 \sim VDD + 0.3$ | ∨ (Note 1)    |

|                        | VIN (2)    | Vp                                     | VDD-45~VDD+0.3        | V             |

| Output Voltage         | Vout (1)   | Outputs other than ports E, F, G, H, I | $-0.3 \sim VDD + 0.3$ | V             |

|                        | Vout (2)   | Ports E, F, G, H, I                    | VDD-45~VDD+0.3        | V             |

| Peak Output Current    | lo (1)     | Each pin of ports C, D                 | $-2.0 \sim +2.0$      | mA            |

|                        | lo (2)     | Each pin of ports E, F                 | -10~0                 | mΑ            |

|                        | lo (3)     | Each pin of ports G, H, I              | $-15 \sim 0$          | mΑ            |

|                        | 10 (4)     | All pins of ports C to I               | $-90 \sim +16$        | mΑ            |

| Allowable Power        | Pd max (†) | DIP package, Ta=-30 to +70°C           | 600                   | mW            |

| Dissipation            | Pd max (2) | Flat package, Ta=-30 to +70°C          | 400                   | mW            |

| Operating Temperature  | Topr       |                                        | $-30 \sim +70$        | $\mathcal{C}$ |

| Storage Temperature    | Tstg       |                                        | $-55 \sim +125$       | $\mathcal{C}$ |

Note 1: For pin OSC1, up to oscillation amplitude generated when internally oscillated under the recommended oscillation conditions in Fig. 3 is allowable.

# Recommended Operating Conditions at Ta=-30 to +70°C, VSS=0V (VDD=4.0 to 6.0V unless otherwise specified)

|                                |                 |                                                             | min   | typ       | max   | unit |

|--------------------------------|-----------------|-------------------------------------------------------------|-------|-----------|-------|------|

| Operating Supply Voltage       | VDD             |                                                             | 4.0   | 5.0       | 6.0   | V    |

| Power-down Supply Voltage      | VDD(MR)         | HOLD=VIL(4), HOLD mode                                      | 1.8   |           | 6.0   | V    |

| "H"-Level Input Voltage        | V(H 11)         | Ports A to D, port A: "normal threshold                     | 0.7VD | D         | Vaa   | V    |

|                                |                 | input"                                                      |       |           |       |      |

|                                | VIH 2>          | V <sub>DD</sub> =4.5 to 5.5V, port A: "low threshold input" | 1.9   |           | Voo   | V    |

|                                | VIH 33          | INT, RES, HOLD, OSC1 pins                                   | 0.800 | D         | Voo   | V    |

| "L"-Level Input Voltage        | VIL (1)         | Ports A to D, port A: "normal threshold                     | Vss   | 0         | .3Voo | V    |

|                                |                 | input"                                                      |       |           |       |      |

|                                | VIL (2)         | V <sub>DD</sub> =4.5 to 5.5V, port A: "low threshold input" | Vss   |           | 0.5   | V    |

|                                | V(∟ 13)         | INT, RES, OSC1 pins                                         | Vss   | 0         | .2Vpp | V    |

|                                | VIL (4)         | V <sub>DD</sub> =1.8 to 6.0V, <del>HOLD</del> , TEST pins   | Vss   | 0         | .2VDD | V    |

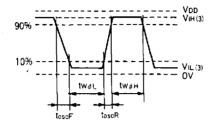

| Operating Clock Frequency      | fextosc         | At external clock input, See Fig. 1.                        | 222   |           | 1290  | KHZ  |

| "H"-Level Clock Pulse          | twøH            | 4                                                           | 0.3   |           |       | μ5   |

| Width                          |                 |                                                             |       |           |       |      |

| "L"-Level Clock Pulse          | twøL            | *                                                           | 0.3   |           |       | μS   |

| Width                          |                 |                                                             |       |           |       |      |

| Clock Input Rise               | toscR           | 4                                                           |       |           | 0.2   | μS   |

| Time                           |                 |                                                             |       |           |       |      |

| Clock Input Fall               | toscF ·         | 4                                                           |       |           | 0.2   | μS   |

| Time                           |                 |                                                             |       |           |       |      |

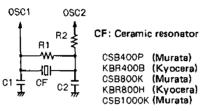

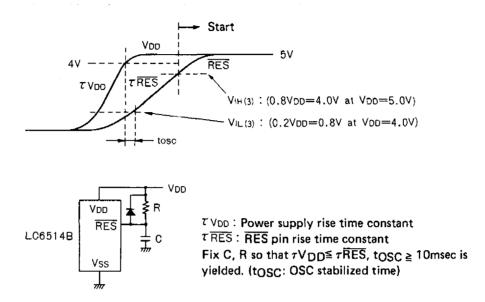

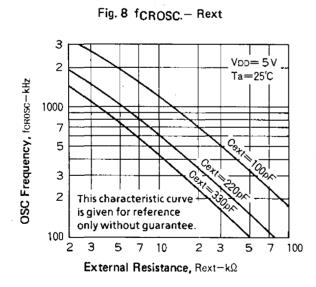

| External Capacitance for CR OS | <b>C</b> Cext   | See Fig. 8                                                  |       | 220±      |       | ρF   |

| External Resistance for CR OSC | Rext            | 7 See Fig. 0                                                |       | $6.8 \pm$ | 1 %   | kΩ   |

| External Circuit Constants     | R1, R2          | See Fig. 3                                                  |       |           |       |      |

| for Ceramic OSC                | C1, C2          |                                                             | _     |           |       |      |

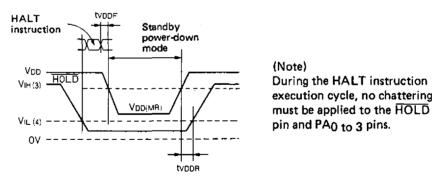

| Standby Timing                 | tyddr           | See Fig. 6, V <sub>DD</sub> =1.8 to 6.0V                    | 0     |           |       | μS   |

|                                | tyddf           | " "                                                         | 0     |           | . –   | μS   |

| Allowable Delay in             | t <sub>DL</sub> | See Figs. 9, 10.                                            |       |           | )·Tc  | μS   |

| Key Scan Circuit               | toH             | 4                                                           |       | (N-3      | )·Tc  | μS   |

Fig. 2 Recommended Oscillator for CR OSC

Fig. 1 OSC1 Pin Input Waveform

| Center<br>Frequency | CF                | C1(pF) | C2(pF) | R1(kΩ) | R2(kΩ) |

|---------------------|-------------------|--------|--------|--------|--------|

| 400kHz              | CSB400P (Murata)  | 470    | 470    | 1000   | 1.5    |

| 400112              | KBR400B(Kyocera)  | 470    | 470    | 1000   | 1.5    |

|                     | CSB800K (Murata)  | 220    | 220    | 1000   | 1.0    |

| 800kHz              | KBOBOOLUK         | 220    | 220    | 1000   | 1.0    |

|                     | KBR800H(Kyocera)  | 150    | 150    | 1000   | 1.5    |

| 1000kHz             | CSB1000K (Murata) | 100    | 100    | 1000   | 1.5    |

CSB1000K (Murata)

C1, C2: Tolerance ±10%

Fig. 3 Recommended Oscillator for Ceramic OSC

R1, R2: Tolerance ±5%

| Electrical Characteristics/Ta=- | -30 to +70°C,      | V <sub>DD</sub> =5V ±20%, V <sub>SS</sub> =0V      | min          | typ    | max     | unit                             |

|---------------------------------|--------------------|----------------------------------------------------|--------------|--------|---------|----------------------------------|

| "H"-Level Input Current         | lı⊢                | All input pins except Vp, VIN≂VDD                  |              |        | 1       | μА                               |

| "L"-Level Input Current         | lıı.,              | All input pins except Vp, VIN=VSS                  | <b>-</b> 1   |        |         | μА                               |

| "H"-Level Output Voltage        | VOH(1)             | Ports C, D: I <sub>OH</sub> =-1mA                  | 0.5~0        |        |         | V                                |

|                                 | VOH(2)             | Ports C, D: I <sub>OH</sub> =−100μA ∨ <sub>0</sub> | 0-0.5        |        |         | V                                |

|                                 | VOH(3)             | Ports E, F: IOH=-2mA                               | 0.1-0        |        |         | V                                |

|                                 | VOH(4)             | Ports E, F: I <sub>OH</sub> =-1mA,                 | 0-0.5        |        |         | V                                |

|                                 |                    | all ports IOH=-1mA                                 | ,            |        |         |                                  |

|                                 | VOH(5)             | Ports G, H, 1: I <sub>OH</sub> =-10mA Vo           | 00-1.8       |        |         | V                                |

|                                 | VOH(6)             | Ports G, H, I: IOH=-2mA                            | 0.1-0        |        |         | V                                |

|                                 | VOH(7)             | Ports G, H, I: IOH=-1mA,                           | 0.5          |        |         | V                                |

|                                 |                    | all ports IOH≃—1mA                                 |              |        |         |                                  |

| "L"-Level Output Voltage        | VOL(1)             | Ports C, D: IOL=1mA                                |              |        | 0.4     | V                                |

|                                 | VOL(2)             | Ports E, F, G, H, I: Vp=-35V, output Tr Ol         | FF,          | 1      | -33     | ٧                                |

|                                 |                    | output open, with pull-down resistor               |              |        |         |                                  |

| "L"-Level Output Current        | ior l              | Ports E, F, G, H, I: Vp=-35V,                      |              | 0.362  |         | $mA_{\scriptscriptstyle{\perp}}$ |

| (Output Pull-down resistor)     | (R <sub>PD</sub> ) | VOL=3V, VDD=5V, with pull-down resistor            | (200)        | (105)  | (50)    | (kΩ)                             |

| Output OFF Leak Current IOFF(1) |                    | Ports C, D: VOUT=VDD                               |              |        | 1.0     | $\mu A$                          |

|                                 | IOFF(2)            | Ports C, D: VOUT=VSS                               | <b>-1</b> .0 |        |         | μΑ                               |

|                                 | IOFF(3)            | Port E to I: VOUT=VDD, OD output                   |              |        | 30      | μА                               |

|                                 | IOFF(4)            | Port E to 1: VOUT=VDD-40V, OD output               | -30          |        |         | μА                               |

| Clock OSC Frequency             | fcFosc(1)          | Recommended conditions for ceramic OSC,            | 384          | 400    | 416     | KHZ                              |

| for Ceramic OSC                 |                    | at OSC circuit in Fig. 3 (Note 1)                  |              |        |         |                                  |

|                                 | fCFOSC(2)          | "                                                  | 768          | 800    | 832     | kHz                              |

|                                 | fcFosc(3)          | "                                                  | 960          | 1000   | 1040    | KHZ                              |

| Clock OSC Frequency             | fcrosc             | Cext=220pF, Rext=6.8k $\Omega$ ,                   | 600          | 800    | 1220    | kHz                              |

| for CR OSC                      |                    | at OSC circuit in Fig. 2                           |              |        |         |                                  |

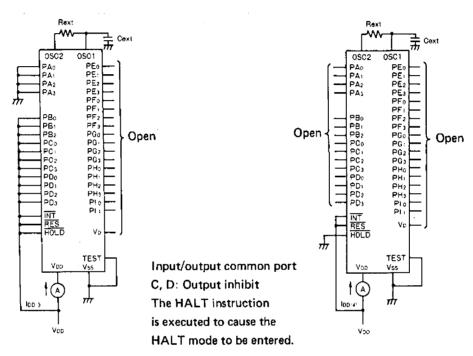

| Current Dissipation             | IDD(1)             | At CR OSC, Cext=220pF, Rext=6.8kΩ,                 |              | 1.0    | 2.0     | mΑ                               |

|                                 |                    | output pin open, input pin, VIN=VDD                |              |        |         |                                  |

|                                 | IDD(2)             | At ceramic OSC (800kHz), output pin open           | ,            | 1.0    | 2.0     | mΑ                               |

|                                 |                    | input pin, VIN=VDD                                 | -            |        |         |                                  |

|                                 | 100(3)             | HALT mode, V <sub>DD</sub> =4.0 to 6.0V,           |              |        | 10      | μΑ                               |

|                                 |                    | at test circuit in Fig. 4                          |              |        |         |                                  |

|                                 | IDD(4)             | HOLD mode, V <sub>DD</sub> =1.8 to 6.0 V,          |              |        | 10      | $\muA$                           |

|                                 |                    | at test circuit in Fig. 5                          |              |        |         |                                  |

| (Note 1) fCFOS                  | : Oscillatable     | ·                                                  | Conti        | nued c | on next | page.                            |

| Continued from preceding | g page. | • • • • • • • • • • • • • • • • • • • • | min | typ | max | unit |

|--------------------------|---------|-----------------------------------------|-----|-----|-----|------|

| Input Capacitance        | CIN     | f=1MHz                                  |     | 5   |     | ρF   |

| Output Capacitance       | Cout    | f=1MHz, output: high impedance          |     | 10  |     | ρF   |

| Input/Output Capacitance | Cio     | "                                       |     | 10  |     | ρF   |

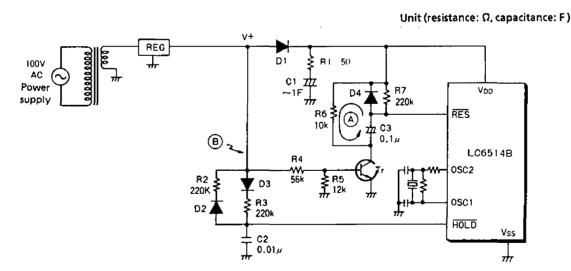

Fig. 4 IDD(3) Test Circuit

Fig. 5 IDD(4) Test Circuit

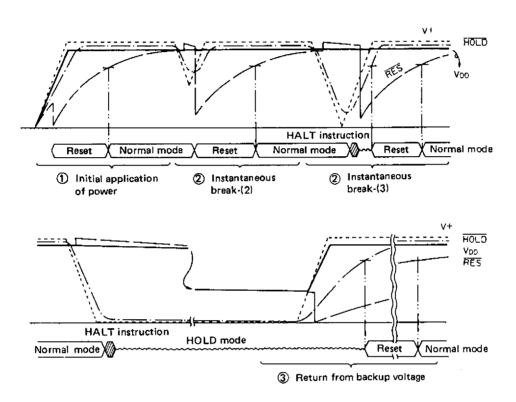

Fig. 6 Standby Mode Timing

Fig. 7 Initial Reset Timing

#### CR OSC characteristic of LC6514B

Fig. 8 shows the CR OSC characteristic of the LC6514B. For the variation range of CR OSC frequency of the LC6514B, the following is guaranteed at external constants of Cext=220pF, Rext=6.8kohm only. The outgoing inspection is performed under this condition only.

If any other constants than specified above are used, the range of Rext=5k to 50kohm, Cext=100p to 300pF must be observed. (See Fig. 8.)

Note 1. The OSC frequency at V<sub>DD</sub>=5V, Ta=25°C must be 800kHz or less.

Note 2. The OSC frequency at  $V_{DD}$ =4 to 6V, Ta= -30 to  $+70^{\circ}$ C must be within the operation clock frequency range (222kHz to 1290 kHz).

### Proper cares in using the IC

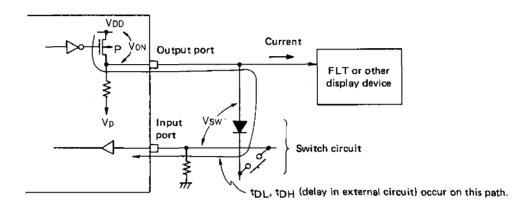

[Digit drive signal-used key scan]

When key-scanning with the FLT digit drive signal in Fig. 9 and inputting the return signal to port A, the following must be observed.

- (a) Estimate voltage drop (VoN) in the output transistor using the current flowing in an FLT used and the V-I characteristic of the output port of the LC6514B.

- (b) Estimate voltage drop (VSW) in the switch circuit.

- (c) Check to see that (VON + VSW) meets the VIH/VIL requirement of the input port.

Fig. 9 Sample Key Scan Application

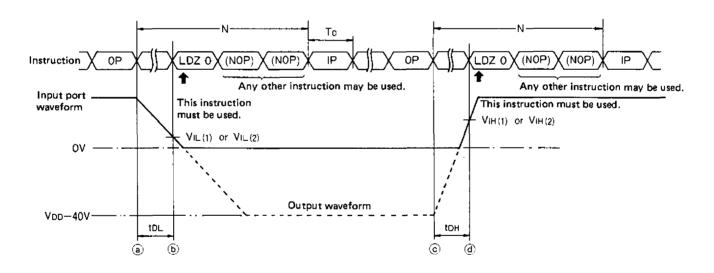

For the key scan application in Fig. 9, make the program considering the delay in the external circuit and the input delay shown below.

- N: Number of instruction cycles existing between instruction (OP, SPB, RPB) used to output data to output port and instruction (IP, BP, BNP) used to input data from input port.

(Number of instruction cycles to be programmed according to the length of tpl, tph)

- tDL, tDH: Delay in external circuit from output port to input port .

When the IP instruction is used to input the return signal as shown in Fig. 10, the input delay must be considered and three instructions are placed between the IP instruction and the crossing of input port waveform and  $V_{1L(1)}$  or  $V_{1L(2)}$ ,  $V_{1H(1)}$  or  $V_{1H(2)}$  respectively.

Some instructions must be placed additionally according to the length of delay (tpl, tph) in the external circuit after the digit drive signal is delivered with the execution of the OP instruction (a) and c).

#### <Notes for Standby Function Application>

#### [Proper cares in using standby function]

The LC6514B provides the standby function called HALT, HOLD mode to minimize the current dissipation when the program is in the wait state. The standby function is controlled by the HALT instruction, the HOLD pin, RES pin. A peripheral circuit and program must be so designed as to provide precise control of the standby function. In most applications where the standby function is performed, voltage regulation, instantaneous break of power, and external noise are not negligible. When designing an application circuit and program, whether or not to take some measures must be considered according to the extent to which these factors are allowed.

This section mainly describes power failure backup for which the standby function is mostly used. A sample application circuit where the standby function is performed precisely is shown below and notes for circuit design and program design are also given below. When using the standby function, the application circuit shown below must be used and the notes must be also fully observed. If any other method than shown in this section is applied, it is necessary to fully check the environmental conditions such as power failure and the actual operation of an application equipment.

#### [Sample application and notes]

When using the HOLD mode, an application circuit and program must be designed with the following in mind.

- (1) The supply voltage at the standby state must not be less than specified.

- (2) Input timing of each control signal (HOLD, RES, port A, INT, etc.) at the standby initiate/release state.

- (3) Release operation must not be overlapped at the time of execution of the HALT instruction.

A sample application where the standby function is used for power failure backup is shown below as a concrete method to observe these notes. A sample application circuit, its operation, and notes for program design are given below.

- 1. Sample application where the standby function is used for power failure backup

Power failure backup is an application where power failure of the main power source is detected by the HOLD pin, etc. to cause the HOLD mode to be entered so that the current dissipation is minimized and a backup capacitor is used to retain the contents of the internal registers even during power failure.

- 1-1. Sample application circuit (CF OSC)

Fig. 11 shows a CF OSC-applied circit where the standby function is used for power failure backup.

Fig. 11 Sample Application Circuit

#### 1-2. Operating waveform

The operating waveform in the sample application circuit in Fig. 11 is shown below. The mode is roughly divided as follows:

- 1 Initial application of power

- 2 Instantaneous break

- 3 Return from backup mode

- 1-3. Operation of sample application circuit

- ① At the time of initial application of power

A reset occurs and the execution of the program starts at address 000H of the program counter (PC).

- ② At the time of instantaneous break

- (1) At the time of very short instantaneous break

The execution of the program continues.

- (2) At the time of instantaneous break being a little longer than (1)

- (When the  $\overline{RES}$  input voltage meets  $V_{|L|}$  and  $\overline{HOLD}$  input voltage does not meet  $V_{|L|}$ )

A reset occurs during the execution of the program and the execution of the program starts at address 000H of the program counter (PC).

Since the HOLD request signal is not applied to the HOLD pin, the HOLD mode is not entered.

(3) At the time of long instantaneous break (When both of the RES input voltage and HOLD input voltage meet V<sub>1</sub>L)

The HOLD request signal is applied to the HOLD pin and the HOLD mode is entered.

- When V+ rises after instantaneous break, a reset occurs to release the HOLD mode and the execution of the program starts at address 000H of the program counter (PC).

- 3 At the time of return from backup voltage

A reset occurs and the execution of the program starts at address 000H of the program counter (PC).

- 1-4. Notes for circuit design

- ① How to fix C3, R6, C2, R2

Fix closed loop (A) discharge time constants C3, R6 and HOLD pin charge time constants C2, R2 so that closed loop (A) fully discharges before the HOLD input voltage gets lower than VIL at the time of instantaneous break and the RES input voltage is sure to get lower than VIL (a reset occurs) when V+ rises after instantaneous break where the HOLD input voltage gets lower than VIL.

- (2) How to fix C3, R7

- Fix RES pin charge time constants C3, R7 so that when power is applied initially or the HOLD mode is released the CF OSC oscillates normally and the RES input voltage exceeds VIH and the program starts running.

- 3 How to fix R4, R5

- Fix Tr bias constants R4, R5 so that when V+ rises after instantaneous break the RES input voltage gets lower than V<sub>1L</sub> (brought to "L" level) before the HOLD input voltage exceeds V<sub>1H</sub> (brought to "H" level).

- 4 How to fix C2, R3

- Fix  $\overline{HOLD}$  pin charge time constants C2, R3 so that when the HOLD mode is released from the backup mode the  $\overline{HOLD}$  input voltage does not exceed  $V_{IH}$  (not brought to "H" level) until the  $\overline{RES}$  input voltage gets lower than  $V_{IL}$  (brought to "L" level).

- Fix C3, R7 and C2, R3 so that the time interval from the moment the HOLD input voltage exceeds V<sub>IH</sub> until the RES input voltage exceeds V<sub>IH</sub> is longer than the CF OSC stabilizing time.

- (5) When the load is heavy or the polling interval is long

- Since C1 discharges largely, increase the capacity of C1 or separate (B) detection from V+ and use a power supply or signal that rises faster than V+.

#### 1-5. Notes for software design

When the HOLD request signal is detected, the HALT instruction is executed immediately. A concrete example is shown below.

- 1) An interrupt is inhibited before polling the HOLD request pin (HOLD pin).

- Polling of the HOLD pin and the HALT instruction are programmed consecutively.

## [Concrete example]

RCTL 3 ; EXTEN, TMEN + 0 (External, timer interrupt inhibit)

BPO AAA ; Polling of the HOLD pin (If "H" level, a branch occurs to AAA.)

HALT ; The HOLD mode is entered.

AAA:

#### Application development tools

Evaluation chip (LC6597), simulation chip (LC65PG97) and the dedicated equipment called "application development tools" are available to facilitate application development of the LC6514B.

#### SDS-410 system

This is a combination of floppy disk-provided CPU, CRT, and printer. This system enables application development programs of microcomputers to be prepared (edited, assembled) very speedily and efficiently in assembly language. By connecting the EVA-410 to the CPU, programs can be debugged and assembled data can be written into the EPROM (using EPROM WRITER function contained in the EVA-410).

#### EVA-410

This is an evaluation kit having EPROM WRITER function, function of parallel/serial data communication with external equipment (SDS-410, etc.). This kit enables application development programs to be corrected or debugged on the machine language level.

#### • EVA-TB3B

This is a board which is connected with the EVA-410 to develop programs dedicated to the LC6514B.

#### ● EVA-97-14B

Simulation chip (LC65PG97) is identical with the LC6510C in the I/O port breakdown voltage and pin assignment. Since the LC6514B has high-voltage output ports and differs partially in the pin assignment, conversion board "EVA-97-14B" with high-voltage drivers is used to evaluate the LC6514B.

(Note) The threshold level of input port A of the LC6514B can be selected to be normal/low level by option. However, since port A of the EVA-TB3B, EVA-97-14B is of normal threshold input type, they cannot be used to evaluate the low threshold input version of the LC6514B.

# LC6514B

#### **APPENDIX** LC6510 Series Instruction Set (by Function)

( ), ( ]: Contents

Transfer and direction

Addition

Subtraction

AND

V: OR

Exclusive OR M: Memory

M(DP): Memory addressed by DP

P(DPL): Input/output port addressed by DPL

PC: Program counter

STACK: Stack register

TM: Timer

TMF: Timer (internal) interrupt request flag

At, Ha, La: Working register

ZF: Zero flag Symbols

AC:

ACt:

CF:

CTL:

DP:

E: Accumulator

Accumulator bit t

Carry flag

Control register

Data pointer

E register E: E register

EXTF: External interrupt request flag

Fn: Flag bit n

|                         | En:      | Flag bit n                                              |          | ZF:         |   | 26   | ero flag                                                                   |                                                                                                                                                                                                 |                |                                                                                        |

|-------------------------|----------|---------------------------------------------------------|----------|-------------|---|------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------|

| Instruction             |          | Mnemonic                                                | Instruc  | tion code   | ē | Ē    | Function                                                                   | Description                                                                                                                                                                                     | Status<br>flag | Remarks                                                                                |

| Justin                  |          | Milemonic                                               | D7D6D5D4 | D3 D2 D1 D0 | Ą | Cycl | Function                                                                   | Description                                                                                                                                                                                     | aftected       | Nemarks                                                                                |

| ş                       | CLA      | Clear AC                                                | 1100     | 0000        | 1 | 1    | AC ← O .                                                                   | The AC contents are cleared.                                                                                                                                                                    | ZF             | <b>*</b> 1                                                                             |

| ctio                    | CLC      | Clear CF                                                | 1110     | 0001        | 1 | 1    | CF ←0                                                                      | The CF is reset.                                                                                                                                                                                | CF             |                                                                                        |

| nster                   | STC      | Set CF                                                  | 1111     | 0001        | 1 | ī    | CF -1                                                                      | The CF is set.                                                                                                                                                                                  | CF             |                                                                                        |

| inoi                    | CMA      | Complement AC                                           | 1110     | 1011        | 1 | 1    | AC ←(AC)                                                                   | The AC contents are complemented (zero bits become 1, one bits become 0).                                                                                                                       | ZF             | [                                                                                      |

| pulat                   | INÇ      | Increment AC                                            | 0000     | 1 1 1 0     | , | 1    | AC ←(AC) +1                                                                | The AC contents are incremented +1.                                                                                                                                                             | ZF CF          |                                                                                        |

| manip                   | DE ¢     | Decrement AC                                            | 0000     | 1 1 1 1     | 1 | 1    | AC ←(AC) -1                                                                | The AC contents are decremented -1.                                                                                                                                                             | ZF CF          |                                                                                        |

| ulator m                | RAL      | Rotate AC left<br>through CF                            | 0000     | 0 0 0 1     | , | ,    | AC0 -(CF), ACn+1-<br>(ACn), CF-(AC3)                                       | The AC contents are shifted left through the CF.                                                                                                                                                | ZF CF          |                                                                                        |

| Ę                       | TAÉ      | Transfer AC to E                                        | 0000     | 0011        | , | ī    | E ←(AC)                                                                    | The AC contents are transferred to the E.                                                                                                                                                       |                |                                                                                        |

| Ą                       | XAE      | Exchange AC with E                                      | 0000     | 1 1 0 1     | ī | 1    | (AC) <b>=</b> (E)                                                          | The AC contents and the E contents are exchanged.                                                                                                                                               |                |                                                                                        |

| č                       | INM      | Increment M                                             | 0010     | 1110        | , | ļ,   | $M(DP) \leftarrow (M(DP)) + 1$                                             | The M(OP) contents are incremented +1.                                                                                                                                                          | ZF CF          |                                                                                        |

| latic                   | DE M     | Decrement M                                             | 0010     | 1 1 1 1     | 1 | 1    | M(DP) - [M(DP)] -1                                                         | The M(DP) contents are decremented =1.                                                                                                                                                          | ZF CF          |                                                                                        |

| manipu<br>ions          | SMB bit  | Set M data bit                                          | 0000     | 1 0 8 180   |   | ,    | M(DP, B <sub>1</sub> B <sub>0</sub> ) +1                                   | A single bit of the M(DPI specified by B1B0 is set.                                                                                                                                             | 2 - 0          |                                                                                        |

| Memory                  | AMB bit  | Reset M data bit                                        | 0010     | 1 C B 1 B 0 | 1 | 1    | M(DP, B₁8₀) ←0                                                             | A single bit of the M(OP) specified by B1B0 is set.                                                                                                                                             | ZF             |                                                                                        |

|                         | AD       | Add M to AC                                             | 0110     | 0000        | 1 | 1    | AC +(AC) + (M(DP))                                                         | The AC contents and the M(DP) contents are binary-added and the result is placed in the AC.                                                                                                     | ZF CF          |                                                                                        |

|                         | ADC      | Add M to AC with CF                                     | 0010     | 0000        | 1 | 1    | AC ←(AC) + (M(DP))<br>+(CF)                                                | The AC, CF, M(DP) contents are binary added and the result is placed in the AC.                                                                                                                 | ZF CF          |                                                                                        |

|                         | DAA      | Decimal adjust AC in addition                           | 1110     | 0110        | , | ,    | AC -( AC) + 6                                                              | 6 is added to the AC contents.                                                                                                                                                                  | ZF             |                                                                                        |

| 20                      | DAS      | Decimal adjust AC in subtraction                        | 1110     | 1010        | 1 | ,    | AC -(ACI+10                                                                | 10 is added to the AC contents.                                                                                                                                                                 | ZF             |                                                                                        |

| tructions               | EXL      | Exclusive or M to AC                                    | 1 1 1 1  | 0101        | 1 | 1    | AC -(AC) ¥ (M(DP))                                                         | The AC contents and the M(DP) contents are exclusive-ORed and the result is placed in the AC.                                                                                                   | ZF             |                                                                                        |

| ison insi               | AND      | And M to AC                                             | 1110     | 0 1 1 1     | , | 1    | AC -(AC) A (M(DP))                                                         | The AC contents and the M(DP) contents are ANDed and the result is placed in the AC.                                                                                                            | ZF             |                                                                                        |

| сошрег                  | OR       | Or M to AC                                              | 1110     | 0101        | ١ | 1    | AC -(AC)V (M(DP))                                                          | The AC contents and the M(DP) contents are ORed and the result is placed in the AC.                                                                                                             | ZF             |                                                                                        |

| Operation               | СМ       | Compare AC with M                                       | 1111     | 1011        | 1 | 1    | (M(DP))+(AC)+1                                                             | The AC contents and the M(DP) contents are compared and the CF and ZF are set/reset.    Comparison result   CF   ZF     (M(DP)   > (AC  0 0 0     (M(DP)   = (AC  1 1     (M(DP)   < (AC  1 0 0 | ZF CF          |                                                                                        |

|                         | C) dala  | Compare AC with immediate data                          | 0010     | 1 1 0 0     | 2 | 2    | 13121110 +(AC)+1                                                           | The AC contents and immediate data [3]2110 are compared and the ZF and CF are set/reset.                                                                                                        | ZF CF          |                                                                                        |

|                         | CL) data | Compare DPc with immediate data                         | 0010     | 1 1 0 0     | 2 | 2    | (DPL) ¥13121110                                                            | The DPL contents and immediate data 1312(1)() are compared.                                                                                                                                     | ZF             |                                                                                        |

|                         | LI data  | Load AC with<br>immediate data                          | 1 1 0 0  | 13121,10    | ۰ | ,    | AC -13121110                                                               | Immediate data 13(2)(1)(0) is loaded in the AC.                                                                                                                                                 | 2F             | *1                                                                                     |

|                         | s        | Store AC to M                                           | 0000     | 0010        | ١ | ١    | M(DP) ←(AC)                                                                | The AC contents are stored in the M(DP),                                                                                                                                                        |                |                                                                                        |

| 1                       | L        | Load AC from M                                          | 0010     | 0001        | 1 | 1    | AC ← (M(DP))                                                               | The MIDP) contents are loaded in the AC.                                                                                                                                                        | ZF             |                                                                                        |

| tions                   | XM data  | Exchange AC with M. then modify DPH with immediate data | 1010     | O M2M1M0    | ١ | 2    | (AC) \$ (M(DP))<br>DP <sub>H</sub> ← (DP <sub>H</sub> ) ¥<br>0 M 2 M 1 M 0 | The AC contents and the M(DP) contents are exchanged. Then, the DPH contents are modified with the contents of (DPH) VOM2M1MD.                                                                  | ZF             | The ZF is set/<br>reset according<br>to the result of<br>IDPHIVOM2<br>M1M0.            |

| Load/store instructions | x        | Exchange AC with M                                      | 1010     | 0000        | 1 | 2    | (AC) = (M(DP))                                                             | The AC contents and the M(DP) contents are exchanged.                                                                                                                                           | ZF             | The ZF is set/<br>reset according<br>to the DPH<br>contents at the<br>time of instruc- |

| Load/st                 | ΧI       | Exchange AC with M. then increment DPL                  | 1 1 1 1  | 1110        | ١ | 2    | (AC) = (M(DP))<br>DPL - (DPL) + 1                                          | The AC contents and the M(DP) contents are exchanged. Then, the DPL contents are incremented +1.                                                                                                | ZF             | The ZF is set/<br>reset according<br>to the result of<br>(DPL + 1).                    |

|                         | X D      | Exchange AC with Mithen decrement DPL                   | 1 1 1 1  | 1 1 1 1     | 1 | 2    | (AC) \$ (M(DPI)<br>DPL +(DPL)-1                                            | The AC contents and the M(DP) contents are exchanged. Then, the DPL contents are decremented -1.                                                                                                | ZF             | The ZF is set/<br>reset according<br>to the result of<br>IDPL - 1).                    |

|                         | ATBL     | Read table data from program ROM                        | 0110     | 0011        | ' | 2    | AC.E←ROM<br>(PCh.E. AC)                                                    | The contents of ROM addressed by the PC whose low-order 8 bits are replaced with the E and AC contents are loaded in the AC and E.                                                              |                |                                                                                        |

# LC6514B

| E                                   |                                 |                                               | lotteret                                                               | ion code                                                    |       | Γ.     | [                                                              |                                                                                                                                                                    | Status                       |                                                                                                                                                                                                                          |

|-------------------------------------|---------------------------------|-----------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------|-------|--------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nstruction                          |                                 | Mnemonic                                      |                                                                        |                                                             | Bytes | Cycles | Function                                                       | Description                                                                                                                                                        | flag                         | Remarks                                                                                                                                                                                                                  |

| <u> </u>                            | LDZ data                        | Load DPH with Zero and                        | D <sub>7</sub> D <sub>8</sub> D <sub>5</sub> D <sub>4</sub>            | D <sub>3</sub> D <sub>7</sub> D <sub>1</sub> D <sub>0</sub> | 1     | 1      | DPH ←0                                                         | The DPH and OPL are loaded with 0 and immediate data [3][2]: [10 respectively.                                                                                     | affected                     |                                                                                                                                                                                                                          |

| nipulation instructions             |                                 | DPL with immediate data respectively          |                                                                        |                                                             |       | L      | DP ( 13   2   1   0                                            |                                                                                                                                                                    |                              |                                                                                                                                                                                                                          |

| lation in                           | LHI data                        | Load DPH with immediate data                  | 0100                                                                   | 13 12 11 10                                                 | 1     | 1      | DPH - 13 12 11 10                                              | The DPH is loaded with immediate data i3121110.                                                                                                                    |                              |                                                                                                                                                                                                                          |

| ij.                                 | IND                             | Increment DPL                                 | 1 1 1 0                                                                | 1 1 1 0                                                     | ١     | 1      | DPL ← (DPL) + 1                                                | The DPL contents are incremented +1.                                                                                                                               | ZF                           |                                                                                                                                                                                                                          |

| Ē                                   | DED                             | Decrement DPL                                 | 1 1 1 0                                                                | 1 1 1 1                                                     | ١     | ;      | DP <sub>L</sub> ← ( DP <sub>L</sub> ) — 1                      | The DPL contents are decremented -1.                                                                                                                               | ZF ·                         |                                                                                                                                                                                                                          |

| pointe                              | TAL                             | Transfer AC to DPL                            | 3 1 1 1                                                                | 0 1 1 1                                                     | 1     | 1      | DP L - (AC)                                                    | The AC contents are transferred to the DPL.                                                                                                                        |                              |                                                                                                                                                                                                                          |

|                                     | TLA                             | Transfer DPL to AC                            | 1 1 1 0                                                                | 1 0 0 1                                                     | 1     | 1      | AC -(DPL)                                                      | The DPL contents are transferred to the AC.                                                                                                                        | ZF                           |                                                                                                                                                                                                                          |

| Oata                                | XAH                             | Exchange AC with DPH                          | 0010                                                                   | 0011                                                        | ١     | 1      | (AC) \$ (DPH)                                                  | The AC contents and the DPH contents are exchanged.                                                                                                                |                              |                                                                                                                                                                                                                          |

| putation<br>instructions            | XA1<br>XAO<br>XAI<br>XA2<br>XA3 | Exchange AC with<br>working register At       | 1 1 1 0                                                                | 0 0 0 0<br>0 1 0 0<br>1 0 0<br>1 1 0 0                      | 1 1 1 | 1 1 1  | (AC) = (AO)<br>(AC) = (A1)<br>(AC) = (A2)<br>(AC) = (A3)       | The AC contents and the contents of working register AO, A1, A2, or A3 specified by t110 are exchanged.                                                            |                              |                                                                                                                                                                                                                          |

| gister man                          | XHa<br>XH0<br>XH1               | Exchange DPH with working register. Ha        | 1 1 1 1                                                                | 1 0 0 0<br>1 1 0 0                                          | 1     | 1      | (DPH) ≒(H0)<br>(DPH) ≒(H1)                                     | The DPH contents and the contents of working register HD or H1 specified by a are exchanged.                                                                       |                              |                                                                                                                                                                                                                          |

| Working register manipulation instr | XLa<br>XLO<br>XLI               | Exchange DPL with working register. La        | 1 1 1 1                                                                | 0000                                                        | 1     | 1      | (DPに与(LO)<br>(DPに)与(L1)                                        | The DPL contents and the contents of working register LO or L1 specified by a are exchanged,                                                                       |                              |                                                                                                                                                                                                                          |

| ions                                | SFB Hag                         | Set flag bit                                  | 0 1 0 1                                                                | 83 B2 B1 B0                                                 | 1     | 1      | Fn ←1                                                          | A flag specified by B3B2B1B0 is set.                                                                                                                               |                              |                                                                                                                                                                                                                          |

| Flag manipulation instructions      | RFB flag                        | Reset flag bit                                | 0001                                                                   | B3 B2 B1 B0                                                 | 1     | 1      | Fn ←0                                                          | A flag specified by 83828180 is reset.                                                                                                                             | ZF                           | The flags are divided into 4 groups of FD to F3. F4 to F7. F8 to F11. F12 to F15. The ZF is set/ reset according to the 4 bits including a single bit specified by immediate data Bababababababababababababababababababa |

|                                     | JMP addr                        | Jump in the current<br>bank                   | O 1 1 0<br>P <sub>7</sub> P <sub>6</sub> P <sub>5</sub> P <sub>4</sub> | 1 P10P9 P8<br>P3P2P1P0                                      | 2     | 2      | PC ←PC11( Or PC11)<br>P10P9 P8 P7 P6 P5<br>P4 P3 P2 P1 P0      | A jump to an address specified by the PC[1] for PC[1] and immediate data P10 to P0 occurs.                                                                         |                              | If the BANK and JMP in-<br>structions are executed con-<br>secutively.<br>PC11 →PC11                                                                                                                                     |

| ions                                | JPEA                            | Jump in the current page modified by E and AC | 1 1 1 1                                                                | 1010                                                        | 1     | 1      | PC7~0 ←(E.AC)                                                  | A jump to an address specified by the contents of the PC whose low-order B bits are replaced with the E and AC contents occurs.                                    |                              |                                                                                                                                                                                                                          |

| ine instructions                    | CZP addr                        | Call subroutine in the zero page              | 1011                                                                   | P3 P2 P1 P0                                                 | 1     | 1      | STACK ← (PC)+1<br>PC+1~6, PC+~0 ←0<br>PC5~2 ←P3 P2 P+P0        | A subroutine in page 0 of bank 0 is called.                                                                                                                        |                              |                                                                                                                                                                                                                          |

| Jump/subroutine                     | CAL addi                        | Call subroutine in the zero bank              | 1 0 1 0<br>P7 P5 P5 P4                                                 | 1 PxxP9P8<br>P3P2P1P0                                       | 2     | 2      | STACK ←(PC) +2<br>PC+1~0 ← OP10P9P8P7<br>P8P5P4P3P2P+P0        | A subtoutine in bank 0 is called,                                                                                                                                  |                              |                                                                                                                                                                                                                          |

| ٦                                   | RT                              | Return from subroutine                        | 0110                                                                   | 0 0 1 0                                                     | 1     | 1      | PC - (STACK)                                                   | A return from a subroutine occurs,                                                                                                                                 |                              |                                                                                                                                                                                                                          |

|                                     | RTI                             | Return from interrupt routine                 | 0 0 1 0                                                                | 0010                                                        | 1     | ,      | PC - (STACK) CF ZF - CSF. ZSF                                  | A return from an interrupt servicing routine occurs.                                                                                                               | ZF CF                        |                                                                                                                                                                                                                          |

| L                                   | BANK                            | Change bank                                   | 1 1 1 1                                                                | 1 1 0 1                                                     | 1     | ,      | PC 11 ← (PC11)                                                 | The bank is changed.                                                                                                                                               | Effective immeditude JMP ins | re only when used ately before the truction.                                                                                                                                                                             |

|                                     | BAt addr                        | Branch on AC bit                              | O 1 1 1<br>P7P6P5P4                                                    | O O 111 o<br>P3 P2 P1 Po                                    |       | 2      | PC7~0 - P7 P6P5 P4<br>P3 P2P1P0<br>if AC1 = 1                  | If a single bit of the AC specified by immediate data 1110 is 1, a branch to an address specified by immediate data P7 to P0 within the current page occurs.       |                              | Mnemonic is<br>BA0 to BA3<br>according to<br>the value of t.                                                                                                                                                             |

|                                     | BNA1 addr                       | Branch on no AC bit                           | O O I I<br>P7P6P5P4                                                    | 0 0 tito<br>P3 P2 P1 P0                                     | 2     | 2      | PC7~0 - P7 P6P5P4<br>P3P2P1P0<br>if AC1 = 0                    | If a single bit of the AC specified by immediate data 1100 is 0 a branch to an address specified by immediate data P7 to P0 within the current page occurs.        |                              | Mnemonic is<br>BNAO to<br>BNA3 second-<br>ing to the value<br>of t.                                                                                                                                                      |

|                                     | BMt addr                        | Branch on M bit                               | O 1 1 1<br>P:P6P5P4                                                    | O 1 t 1 t o<br>P3 P2 P1 Po                                  | 2     | 2      | PC 7~0 - P7 P6 P5 P4<br>P3 P2 P1 P0<br>If [M(DP. 1 1 t a)] = 1 | If a single bit of the MIDPI specified by immediate data (110 is 1, a branch to an address specified by immediate data P7 to P0 within the current page occurs.    |                              | Mnemonic is<br>BM0 to 6M3<br>according to<br>the value of t,                                                                                                                                                             |

| nch instruction                     | BNM: addr                       | Branch on no M bit                            | O O 1 1<br>P7P5P5P4                                                    | 0 1 t 1 t o<br>P3 P2 P1 Po                                  |       | 2      | PC7~0 - P7 P6 P5 P4<br>P3 P2 P1 P0<br>If (M(OP.t 1t 01) = 0    | If a single bit of the M(OP) specified by immediate data 1110 is 0, a branch to an address specified by immediate data P7 to P0 within the current page occurs.    |                              | Mnemonic is<br>BNM0 to<br>BNM3 accord-<br>ing to the value<br>of t.                                                                                                                                                      |

| Bran                                | BPt addr                        | Branch on Port bit                            | O 1 1 1<br>P7 P6 P5 P4                                                 | ) Otito<br>P3P2P1P0                                         |       | 2      | PC7~0 + P7 P6 P6 P4<br>P3 P2 P1 P0<br>II (P(DP4 tito))=1       | If a single bit of port P(DPLI specified by immediate data 1) (0 is 1, a branch to an address specified by immediate data P7 to P0 within the current page occurs. |                              | Mnemonic is<br>BP0 to BP3<br>according to<br>the value of t                                                                                                                                                              |

|                                     | BNP1 addr                       | Branch on no Port bit                         | O O 1 1<br>P7 P6 P5 P4                                                 | 1 Otito<br>P3 P2 P1 P0                                      |       | 2      | PC7~0 - P7P6P5P4<br>P3P2P3P0<br>If (P(DPL, t it o))=0          | If a single bit of port PIDPL1 specified by immediate data tit() is 0, a branch to an address specified by immediate data P7 to P0 within the current page occurs. |                              | Mnamonic is<br>BNPO to BNP3<br>according to<br>the value of t.                                                                                                                                                           |

|                                     | BTM addr                        | Branch on timer                               | 0 1 1 1<br>PrP6P5P4                                                    | 1 1 0 0<br>P3P7P1P0                                         | 2     | 2      | PC7~0 ← P7P6P5P4<br>P3P2P1P0<br>if TMF=1<br>then TMF ←0        | If the TMF is 1, a branch to an address specified by immediate data P7 to P0 within the current page occurs. The TMF is reset.                                     | TMF                          |                                                                                                                                                                                                                          |

| Instruction         |           | Mnemonic                         | Instruct               | on code                    | ig. | Sel | Function                                                            | Description                                                                                                                                                          | Status   | Remarks                                                                                    |

|---------------------|-----------|----------------------------------|------------------------|----------------------------|-----|-----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------|