# Electronic Volume Control System for Audio Equipment

#### Functions

(F)2169A

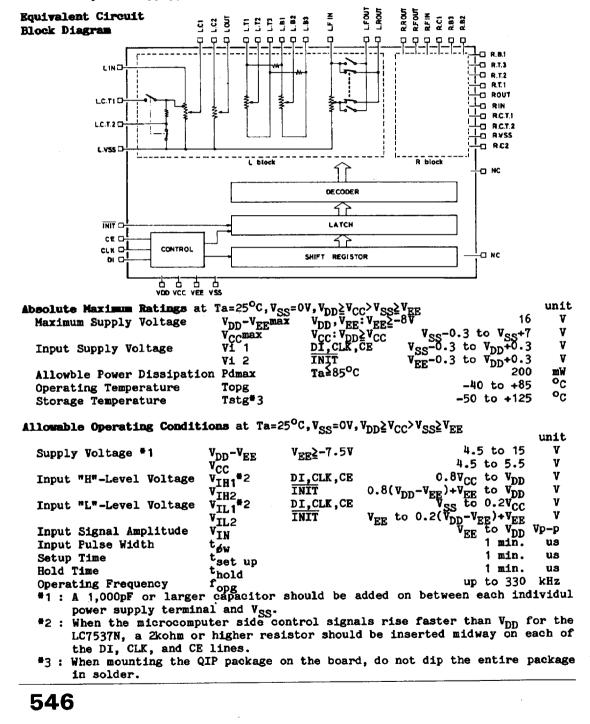

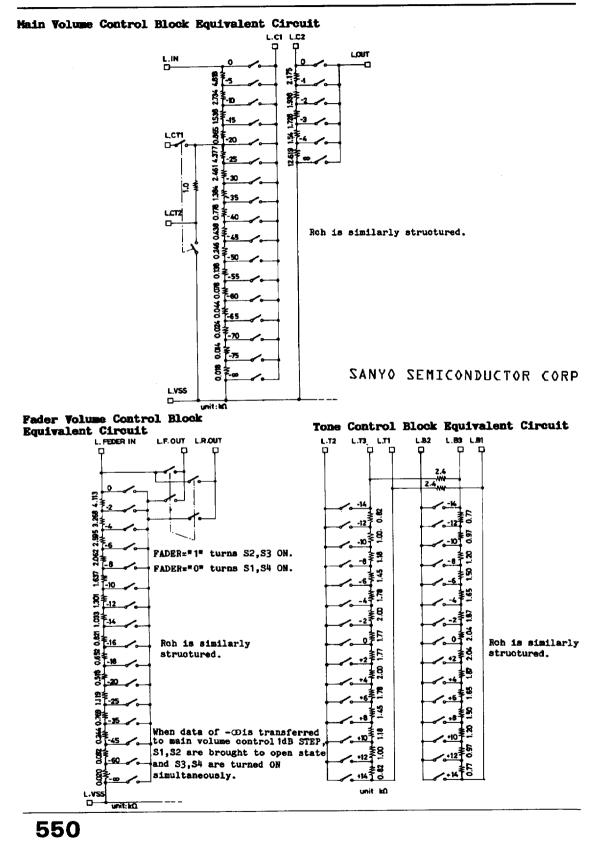

The LC7537N is an electronic control LSI capable of electronically controlling the volume, balance, loudness, fader, bass, and treble functions individually with fewer externally connected component parts.

#### Features

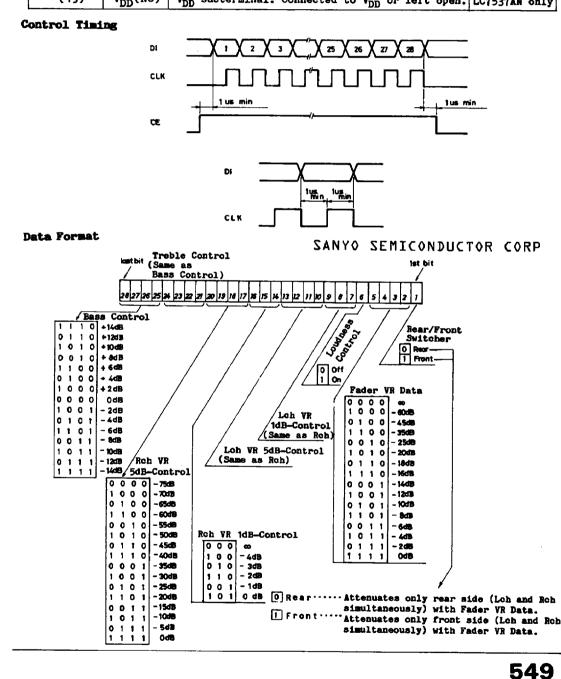

- . Enables controlling the below-listed functions with 3-line serial data, including CE, DI, and CLK. Also, due to OV to 5V swing of the serial data input voltage, permits the use of a general purpose microcomputer.

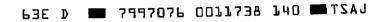

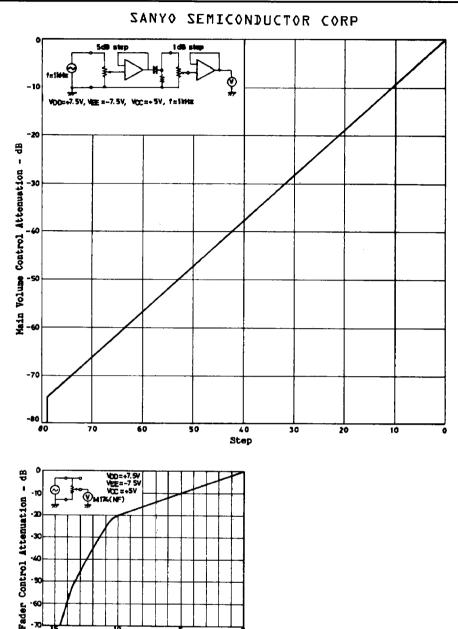

- (1) Volume : Separately controls the Lch and Rch volume levels across 81 positions over the 0dB to -79dB (in 1dB steps) range and  $-\infty$ , and consequently also serves balance control purposes.

- (2) Loudness : By virtue of a center tap provided at the -20dB position of the volume controlling ladder resistors, permits loudness to be controlled with externally connected CR components.

- (3) Fader : By varying only the rear or front output level across 16 positions, provides fader functions (in 2dB steps over the 0dB to -20dB range, and 5dB steps over the -20dB to -45dB range, and at -∞, for a total of 16 positions). Continued on next page.

This Material Copyrighted By Its Respective Manufacturer

## 63E D 🖿 7997076 DO11734 5T5 🖿 TSAJ

### LC7537N,7537AN

Continued from preceding page.

SANYO SEMICONDUCTOR CORP

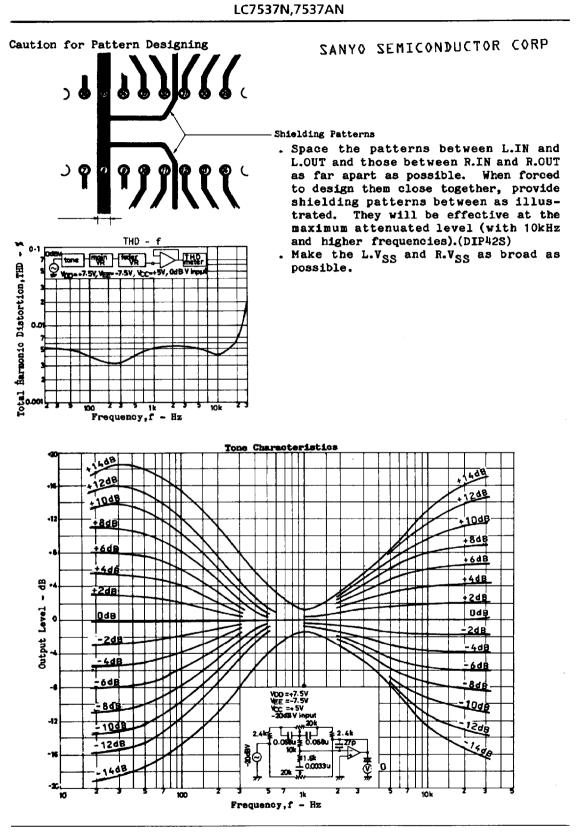

- (4) Bass/Treble: With CR components externally connected, forms an NF type tone control circuit (Baxandall type) to exercise control across 15 positions over both the bass and treble functions in 2dB steps.

- . By virtue of its CMOS structure, the LSI operates under a broad power supply voltage range from +4.5V to +15V, permitting the use of either a single or a dual ± power supply, whichever is preferred.

638 D 🖿 7997076 0011735 431 🖿 5AJ

| <b>.</b>                      |                   |                                                                                                       | min  | typ   | max  | uni |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|------|-------|------|-----|

| Total Harmonic                | THD(1)            | V <sub>IN</sub> =1V,f=1kHz,all flat overall                                                           |      | 0.005 | 0.01 | ,   |

| Distortion                    | THD(2)            | V <sub>IN</sub> =1V,f=20kHz,all flat overall                                                          |      | 0.006 | 0.02 | 1   |

| Crosstalk                     | CT                | V <sub>IN</sub> =1V,f=1kHz,all flat,Rg=1kohm                                                          | 60   | 95    |      | d]  |

| Maximum Attenuation<br>Output | Vomin(1)          | V <sub>IN</sub> =1V,f=1kHz,MAIN,VR= $\infty$ ,<br>FADER VR= $\infty$                                  | 80   | 90    |      | d   |

|                               | Vomin(2)          | )V <sub>IN</sub> =1V,f=1kHz,MAIN VR= $\infty$ ,                                                       | 70   | 80    |      | d)  |

|                               |                   | $V_{DD}^{10}=8V, FADER VR=\infty, V_{EE}=V_{SS}=0V,$<br>C between $V_{SS}$ and GND of L/R=100         |      |       |      |     |

|                               |                   | C between V <sub>SS</sub> and GND of L/R=100                                                          | )OuF |       |      |     |

| VR Resistance                 | RVOL(1)           | 5dB-step                                                                                              | 12   | 20    | 28   | koh |

| Value                         | RVOL(2)           | 1dB-step                                                                                              | 12   | 20    | 28   | koh |

|                               | RBASS             |                                                                                                       | 12   | 20    | 28   | koh |

|                               | RTREBLE           |                                                                                                       | 12   | 20    | 28   | koh |

|                               | RFADER            |                                                                                                       | 12   | 20    | 28   | koh |

| Output Noise<br>Voltage       | V <sub>N(1)</sub> | All flat overall(I <sub>HFA</sub> )<br>Rg=1kohm                                                       |      | 2     | 10   | น   |

|                               | V <sub>N(2)</sub> | OdB position (I <sub>HFA</sub> )<br>Rg=1kohm,V <sub>DD</sub> =8V,V <sub>EE</sub> =V <sub>SS</sub> =0V |      | 2     | 10   | u   |

| Current Dissipation           | IDD               | $v_{DD} - v_{EE} = 15V$<br>$v_{CC} = 5V$                                                              |      |       | 1    | D.  |

|                               | ICC               | V5V                                                                                                   |      |       | 1    | m   |

## LC7537N,7537AN

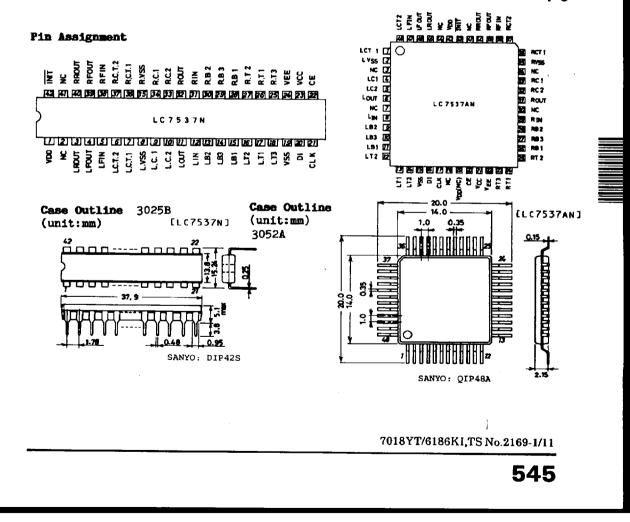

Pin Description ( ):LC7537AN

SANYO SEMICONDUCTOR CORP

| Pin No. | Symbol | Description of Functions                                      | Remarks         |

|---------|--------|---------------------------------------------------------------|-----------------|

| 12(8)   | L.IN   | Main Volume Control Block 5dB-Step                            |                 |

|         |        | Attenuator Input Terminals. These pins                        |                 |

| 31(29)  | R.IN   | should be driven at a low impedance.                          |                 |

| 9(4)    | L.C1   | Main Volume Control Block 5dB-Step                            |                 |

| 34(33)  | R.C1   | Attenuator Output Terminals, Having been                      |                 |

|         |        | designed to be open, the step positions                       | VR Resistance : |

|         |        | will develop errors if at low acceptor                        | 20kohma         |

|         |        | impedances, so that as high load impedan-                     |                 |

|         |        | ces as possible should be provided.                           |                 |

| 10(5)   | L.C2   | Main Volume Control Block 1dB-Step                            |                 |

|         | i i    | Attenuator Input Terminals. These pins                        |                 |

| 33(32)  | R.C2   | should be driven at a low impedance.                          |                 |

| 11(6)   | L.OUT  | Main Volume Control Block 1dB-Step                            |                 |

|         |        | Attenuator Output Terminals. Due to the                       |                 |

|         |        | step positions designed to be open, load                      | VR Resistance : |

|         |        | impedances as high as possible should be                      | 20kohms         |

| 32(31)  | R.OUT  | provided to them, similar to those for                        |                 |

| 5(47)   | L.FIN  | the lot and lot                                               |                 |

| 2(41)   | LIFIN  | Fader Functions Employing Mode Input                          |                 |

| 38(38)  | R.FIN  | Terminals. These pins should be driven<br>at a low impedance. |                 |

| 4(46)   | L.FOUT | Fader Block Output Terminals. These pins                      |                 |

|         |        | permit the front and rear sides to be                         |                 |

|         |        | faded out independently of each other.                        |                 |

| 3(45)   | L.ROUT | Attenuations exercised on Lch will be the                     |                 |

|         |        | same as on Rch. Due to the step posi-                         | VR Resistance : |

|         |        | tions designed to be open, acceptor                           | 20kohma         |

| 39(39)  | R.FOUT | impedances as high as possible should be                      |                 |

| 40(40)  | R.ROUT | provided to them.                                             |                 |

| 40(40)  | R.ROUT |                                                               |                 |

Continued on next page.

547

This Material Copyrighted By Its Respective Manufacturer

.

# 63E D 🔳 7997076 0011736 378 🔳 TSAJ

## LC7537N,7537AN

| in No.          | Symbol            | Description of Functions                                                                                                | Remarks                               |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 5(11)           | L.B1              | Bass Tone Control Block Terminals. A                                                                                    |                                       |

| 6(9)            | L.B2              | total of 15 positions have been provided                                                                                |                                       |

| 4(10)           | L.B3              | in 2dB steps.                                                                                                           | VR Resistance :                       |

| 28(26)          | R.B1              |                                                                                                                         | 20kohms                               |

| 27(28)          | R.B2              |                                                                                                                         |                                       |

| 29(27)          | R.B3              |                                                                                                                         |                                       |

| 17(13)          | L.T1              | Treble Tone Control Block Terminals. A                                                                                  |                                       |

| 16(12)          | L.T2              | total of 15 positions have been provided                                                                                | VR Resistance :                       |

| 18(14)          | L.T3              | in 2dB steps. The VR resistance value is                                                                                | 20kohms                               |

| 26(24)          | R.T1              | 20kohm.                                                                                                                 | Louding                               |

| 27(25)          | R.T2              |                                                                                                                         |                                       |

| 25(23)          | R.T3              |                                                                                                                         |                                       |

|                 | LCT1              | Loudness Dedicated Terminals. A high-                                                                                   |                                       |

| 7(1)            | LCT2              | frequency-range correcting C should be                                                                                  |                                       |

| 6(48)           | RCT 1             | put between CT1 and IN, and low-frequen-                                                                                |                                       |

| 36(36)          | RCT2              | cy-range-correcting C between CT2 and                                                                                   |                                       |

| 37( <b>37</b> ) | I NOIZ            | L.V <sub>SS</sub> (R.V <sub>SS</sub> ).                                                                                 |                                       |

|                 | ···               | Main Volume Control Block Fader Control                                                                                 |                                       |

|                 |                   | Common Terminals. The impedance of pat-                                                                                 |                                       |

|                 | 1                 | tern connected to these pins should be as                                                                               | IN                                    |

| 9(2)            |                   | low as possible. Since L.V <sub>SS</sub> , R.V <sub>SS</sub> , and                                                      | وي المحاطبا                           |

| 8(2)            | L.V <sub>SS</sub> | $V_{SS}$ have not been connected inside the                                                                             | VDD                                   |

|                 |                   | LSI, they should be connected together on                                                                               |                                       |

|                 | 1                 | the outside in conformance with their                                                                                   |                                       |

|                 |                   | individual specifications.                                                                                              |                                       |

| 35(35)          | R.V <sub>SS</sub> | Particular attenuation should be paid to                                                                                |                                       |

|                 |                   | the capacitance assigned to the capaci-                                                                                 | ↓ <u>↓</u> <del>▼</del> ♥             |

|                 |                   | the capacitance assigned to the capacit-                                                                                |                                       |

|                 |                   | tors put between L.V <sub>SS</sub> (R.V <sub>SS</sub> ) and V <sub>SS</sub> , which will emerge as a residual resistive |                                       |

|                 |                   | component when control is turned down for                                                                               |                                       |

| •               |                   |                                                                                                                         |                                       |

|                 |                   | maximum attenuation.<br>Intra-IC Latch Resetting Terminal                                                               |                                       |

| 42(42)          | INIT              | Intra-It Laten Resetting ferminal                                                                                       |                                       |

|                 |                   | INIT Assure an "H" level here.                                                                                          |                                       |

|                 |                   |                                                                                                                         |                                       |

|                 |                   |                                                                                                                         | ≰ Ц                                   |

|                 |                   | Gratural external data at the internal                                                                                  |                                       |

|                 |                   | Control-setting data at the internal                                                                                    | ───────────────────────────────────── |

|                 |                   | latch will be indeterminate when power                                                                                  | ' YEE                                 |

|                 |                   | has just been switched on, so that by                                                                                   |                                       |

|                 |                   | engaging the "L" level of this pin at                                                                                   |                                       |

|                 |                   | power-on, the fader control may be set at                                                                               |                                       |

|                 |                   | its - co position and muting behavior                                                                                   |                                       |

|                 |                   | is engaged (Note: V <sub>DD</sub> -V <sub>EE</sub> Level).                                                              |                                       |

| 22(20)          | CE                | Chip Enable Terminal. When this pin is                                                                                  | 9 VCC                                 |

| • •             |                   | made "H" $\rightarrow$ "L", data is written in the                                                                      | CE N                                  |

|                 |                   | internal latch, activating the various                                                                                  | CE E                                  |

|                 |                   | analog switches. When the "H" level is                                                                                  | VSS                                   |

|                 |                   | then restored, transfer of the data will                                                                                | ,                                     |

|                 |                   | be enabled.                                                                                                             |                                       |

| 20(16)          | DI                | Input Terminals for Serial Data and Clock                                                                               | o VCC                                 |

|                 |                   | that serve control purposes.                                                                                            | Dior                                  |

|                 | _                 |                                                                                                                         | <u>c₽</u> k []}                       |

| 21(17)          | CLK               |                                                                                                                         | ↓ vss                                 |

|                 |                   |                                                                                                                         |                                       |

|                 |                   |                                                                                                                         | l                                     |

|                 |                   |                                                                                                                         |                                       |

548

# LAZT 🖿 405 7671100 J707867 🛤 🛛 364

| Pin No.                              | Symbol                                                                   | Description of Functions                                                                                                  | Remarks |

|--------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|

| 1(43)<br>23(21)<br>19(15)<br>24(22)  | V <sub>DD</sub><br>V <sub>CC</sub><br>V <sub>SS</sub><br>V <sub>SS</sub> | These pins are connected to the relevant power supplies. Exercise caution against $V_{CC}$ rising earlier than $V_{DD}$ . | -<br>-  |

| 2(3,7)<br>41(18,<br>30,34,<br>41,44) | NC NC                                                                    | No Connect Pins. Absolutely nothing should be connected here.                                                             |         |

LC7537N,7537AN

This Material Copyrighted By Its Respective Manufacturer

LC7537N,7537AN

This Material Copyrighted By Its Respective Manufacturer

551

63E D 🛲 7997076 0033740 879 📰 TSAJ

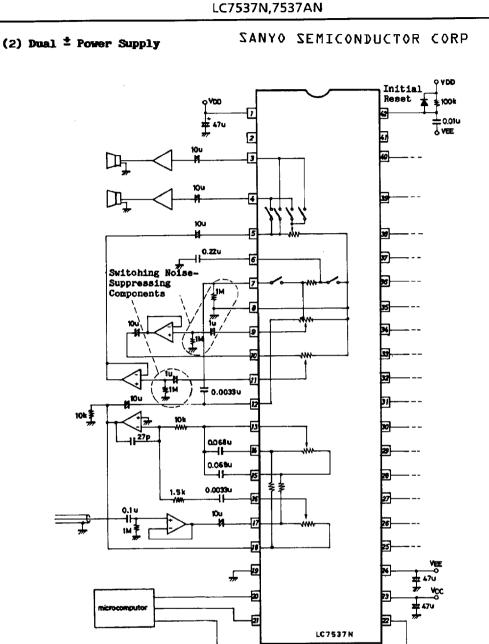

Note: Bipolar electrolytic capacitors should preferably be employed where no polarity has been indicated.

# 552

### SANYO SEMICONDUCTOR CORP

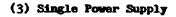

Note: Bipolar electrolytic capacitors should preferably be employed where no polarity has been indicated.

553

This Material Copyrighted By Its Respective Manufacturer

LC7537N,7537AN

555

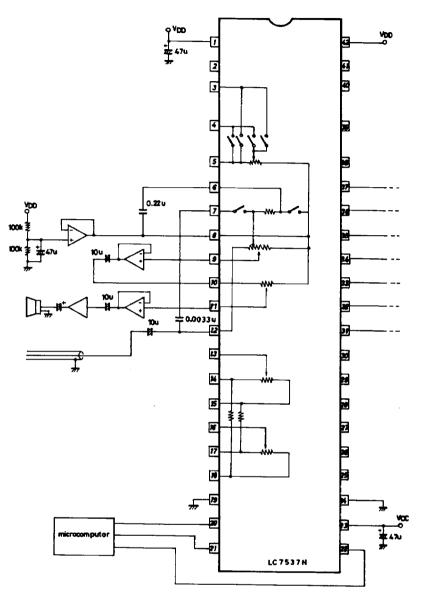

10 Step