# LM1281

LM1281 85 MHz RGB Video Amplifier System with On Screen Display (OSD)

Literature Number: SNOS755

April 1999

National Semiconductor

## LM1281 85 MHz RGB Video Amplifier System with On Screen Display (OSD)

#### **General Description**

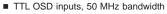

The LM1281 is a full feature video amplifier with OSD inputs, all within a 28-pin package. This part is intended for use in monitors with resolutions up to 1024 x 768. The video section of the LM1281 features three matched video amplifiers with blanking. All of the video amplifier adjustments feature high input impedance 0V to 4V DC controls, providing easy interfacing to bus controlled alignment systems. The OSD section features three TTL inputs and a DC contrast control. The switching between the OSD and video section is controlled by a single TTL input. Although the OSD signals are TTL inputs, these signals are internally processed to match the OSD logic low level to the video black level. When adjusting the drive controls for color balance of the video signal, the color balance of the OSD display will track these color adjustments. The LM1281 also features an internal spot killer circuit to protect the CRT when the monitor is turned off. For applications without OSD insertion please refer to the LM1205 or LM1208 data sheets.

#### **Features**

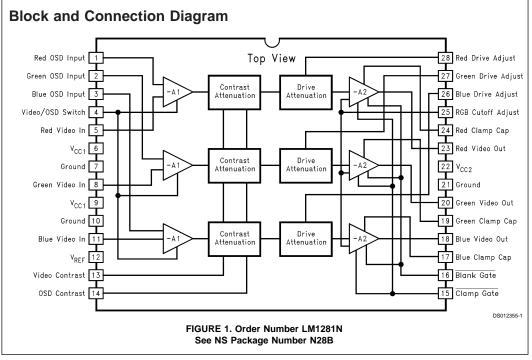

Three wideband video amplifiers 85 MHz @ -3 dB (4 V<sub>PP</sub> output)

- On chip blanking, outputs under 0.1 V when blanked

- High speed Video/OSD switch

- Independent drive control for each channel for color

- balance

0V to 4V, high impedance DC contrast control with over 40 dB range

- OV to 4V, high impedance DC drive control (0 dB to -12 dB range)

- OV to 4V, high impedance DC OSD contrast control with over 40 dB range

- Capable of 7 V<sub>PP</sub> output swing (slight reduction in bandwidth)

- Output stage directly drives most hybrid or discrete CRT drivers

#### Applications

High resolution RGB CRT monitors requiring OSD capability

© 1999 National Semiconductor Corporation DS012355

#### Absolute Maximum Ratings (Note 1)

•

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage<br>Pins 6, 9, and 22                                                                        | 15V                           |

|------------------------------------------------------------------------------------------------------------|-------------------------------|

| Peak Video Output Source Current<br>(Any One Amp) Pins 18, 20, and 23                                      | 28 mA                         |

| Voltage at Any Input Pin (V <sub>IN</sub> )                                                                | $V_{CC} \geq V_{IN} \geq GND$ |

| Power Dissipation (P <sub>D</sub> )<br>(Above 25°C Derate based on<br>θ <sub>IA</sub> and T <sub>J</sub> ) | 2 5W                          |

| OJA and TJ)                                                                                                | 2.000                         |

| Thermal Resistance $(\theta_{JA})$       | 50°C/W          |

|------------------------------------------|-----------------|

| Junction Temperature (T <sub>J</sub> )   | 150°C           |

| ESD Susceptibility (Note 4)              | 2 kV            |

| Storage Temperature                      | –65°C to +150°C |

| Lead Temperature<br>(Soldering, 10 sec.) | 265°C           |

### Operating Rating (Note 2)

| Temperature Range:                | –20°C to +70°C               |

|-----------------------------------|------------------------------|

| Supply Voltage (V <sub>CC</sub> ) | $11.4V \le V_{CC} \le 12.6V$ |

#### **DC Electrical Characteristics**

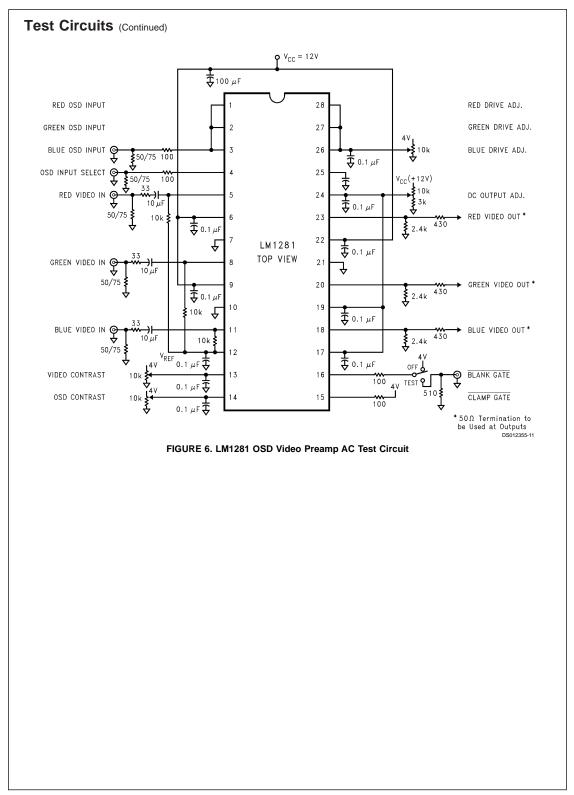

See DC Test Circuit (*Figure 5*),  $T_A = 25^{\circ}C$ ;  $V_{CC1} = V_{CC2} = 12V$ ;  $V_{13} = 4V$ ;  $V_{14} = 4V$ ;  $V_{16} = 4V$ ;  $V_{drive} = 4V$ ;  $V_4 = 0V$ ;  $V_{15} = 0V$ ;  $V_{25} = 1V$  unless otherwise stated

| Symbol                               | Parameter                                  | Conditions                                     | Typical<br>(Note 5) | Limit<br>(Note 6) | Units      |

|--------------------------------------|--------------------------------------------|------------------------------------------------|---------------------|-------------------|------------|

| Is                                   | Supply Current                             | $V_{CC1} + V_{CC2}, R_L = \infty$ (Note 7)     | 95                  | 120               | mA (max)   |

| R <sub>IN</sub>                      | Video Input Resistance                     | Any One Amplifier                              | 100                 |                   | kΩ         |

| V <sub>15I</sub>                     | Clamp Gate Low Input Voltage               | Clamp Comparators On                           | 1.2                 | 0.8               | V (max)    |

| V <sub>15h</sub>                     | Clamp Gate High Input Voltage              | Clamp Comparators Off                          | 1.6                 | 2.0               | V (min)    |

| I <sub>151</sub>                     | Clamp Gate Low Input Current               | V <sub>15</sub> = 0V                           | -1.5                | -5.0              | µA (max)   |

| I <sub>15h</sub>                     | Clamp Gate High Input Current              | V <sub>15</sub> = 12V                          | 0.01                | 1.0               | µA (max)   |

| V <sub>16I</sub>                     | Blank Gate Low Input Voltage               | Blank Gate On                                  | 1.2                 | 0.8               | V (max)    |

| V <sub>16h</sub>                     | Blank Gate High Input Voltage              | Blank Gate Off                                 | 1.6                 | 2.0               | V (min)    |

| I <sub>161</sub>                     | Blank Gate Low Input Current               | V <sub>16</sub> = 0V                           | -8                  | -11               | µA (max)   |

| I <sub>16h</sub>                     | Blank Gate High Input Current              | V <sub>16</sub> = 12V                          | 0.01                | 1.0               | µA (max)   |

| V <sub>12</sub>                      | Reference Voltage                          |                                                | 2.0                 |                   | V          |

| I <sub>vid-clamp</sub>               | Video Input Cap Charge Current             | Clamp Comparators On                           | ±750                | ±450              | μA (min)   |

| I <sub>vid-bias</sub>                | Video Input Cap Bias Discharge<br>Current  | Clamp Comparators Off                          | ±750                |                   | nA         |

| I <sub>out-clamp</sub>               | Output Clamp Cap Charge Current            | Clamp Comparators On                           | ±750                | ±450              | μA (min)   |

| l <sub>out-bias</sub>                | Output Clamp Cap Bias Discharge<br>Current | Clamp Comparators Off                          | 750                 |                   | nA         |

| V <sub>OL</sub>                      | Video Output Low Voltage                   | V <sub>25</sub> = 0V                           | 50                  | 100               | mV (max)   |

| V <sub>он</sub>                      | Video Output High Voltage                  | V <sub>25</sub> = 10V                          | 7.5                 | 7                 | V (min)    |

| V <sub>O(1V)</sub>                   | Video Black Level Output Voltage           | V <sub>25</sub> = 1V                           | 1.2                 |                   | V (Note 8) |

| $\Delta V_{O(1V)}$                   | Video ∆Black Level Output<br>Voltage       | Between Any Two Amplifiers,<br>$V_{25} = 1V$   | ±20                 | ±250              | mV (max)   |

| V <sub>OL</sub> (blanked)            | Video Output Blanked Voltage               | Blank Gate On                                  | 100                 | 500               | mV (max)   |

| I <sub>13,14, 26, 27, or</sub><br>28 | Contrast/Drive Control Input<br>Current    | $V_{contrast} = V_{Drive} = 0V \text{ to } 4V$ | -125                | -500              | nA (max)   |

| I <sub>25</sub>                      | Cut-Off Control Input Current              | V <sub>25</sub> = 0V to 4V                     | -1.0                | 1.5               | µA (max)   |

| V <sub>spot</sub>                    | Spot Killer Voltage                        | V <sub>CC</sub> Adjusted to Activate           | 10.6                | 11.2              | V          |

| Symbol                      | Parameter                                | Conditions                                                   | Typical<br>(Note 5) | Limit<br>(Note 6) | Units     |

|-----------------------------|------------------------------------------|--------------------------------------------------------------|---------------------|-------------------|-----------|

| A <sub>V max</sub>          | Video Amplifier Gain                     | V <sub>13</sub> = 4V, V <sub>IN</sub> = 400 mV <sub>PP</sub> | 10.0                | 7.0               | V/V (min) |

|                             |                                          | V <sub>drive</sub> = 4V                                      | 20.0                | 16.9              | dB (min)  |

| ΔA <sub>V 2V</sub>          | Contrast Attenuation @ 2V                | Ref: $A_V$ max, $V_{13}$ = 2V                                | -6                  |                   | dB        |

| ΔA <sub>V 0.25V</sub>       | Contrast Attenuation @ 0.25V             | Ref: $A_V$ max, $V_{13}$ = 0.25V                             | -40                 |                   | dB        |

| $\Delta Drive_{2V}$         | Drive Attenuation @ 2V                   | Ref: $A_V$ max, $V_{drive}$ = 2V                             | -4.5                |                   | dB        |

| ∆Drive <sub>0.25V</sub>     | Drive Attenuation @ 0.25V                | Ref: $A_V$ max, $V_{drive}$ = 0.25V                          | -11                 |                   | dB        |

| A <sub>V match</sub>        | Absolute Gain Match @ A <sub>v</sub> max | V <sub>13</sub> = 4V, V <sub>drive</sub> = 4V (Note<br>9)    | ±0.3                |                   | dB        |

| A <sub>V track</sub>        | Gain Change between Amplifiers           | V <sub>13</sub> = 4V to 2V (Notes 9, 10)                     | ±0.2                |                   | dB        |

| THD                         | Video Amplifier Distortion               | $V_{O} = 1 V_{PP}, f = 10 \text{ kHz}$                       | 1                   |                   | %         |

|                             |                                          | $V_{13} = 4V, V_{drive} = 3V,$<br>$V_{O} = 4 V_{PP}$         | 85                  |                   | MHz       |

| t <sub>r</sub> (Video)      | Video Output Rise Time (Note 11)         | $V_{O} = 4 V_{PP}$                                           | 3.5                 |                   | ns        |

| t <sub>f</sub> (Video)      | Video Output Fall Time (Note 11)         | $V_{O} = 4 V_{PP}$                                           | 4.5                 |                   | ns        |

| V <sub>sep</sub> 10 kHz     | Video Amplifier 10 kHz Isolation         | V <sub>13</sub> = 4V (Note 13)                               | -70                 |                   | dB        |

| V <sub>sep</sub> 10 MHz     | Video Amplifier 10 MHz Isolation         | V <sub>13</sub> = 4V (Notes 11, 13)                          | -50                 |                   | dB        |

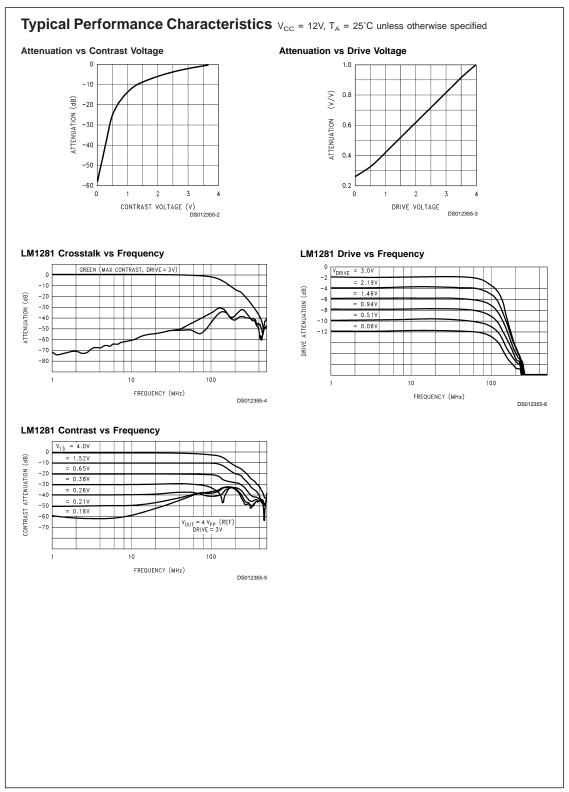

| t <sub>r</sub> (Blank)      | Blank Output Rise Time (Note 11)         | Blank Output = 1 V <sub>PP</sub>                             | 8                   |                   | ns        |

| t <sub>f</sub> (Blank)      | Blank Output Fall Time (Note 11)         | Blank Output = 1 V <sub>PP</sub>                             | 14                  |                   | ns        |

| t <sub>r-prop</sub> (Blank) | End of Blanking Propagation Delay        | Blank Output = 1 V <sub>PP</sub>                             | 23                  |                   | ns        |

| t <sub>f-prop</sub> (Blank) | Start of Blanking Propagation Delay      | Blank Output = 1 V <sub>PP</sub>                             | 20                  |                   | ns        |

| T <sub>pw</sub> (Clamp)     | Back Porch Clamp Pulse Width             | (Note 14)                                                    |                     | 200               | ns (min)  |

Г

| Symbol                      | Parameter                                                        | Conditions                                            | Typical<br>(Note 5) | Limit<br>(Note 6) | Units           |

|-----------------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------|-------------------|-----------------|

| V <sub>OSDI</sub>           | OSD Input Low Input Voltage                                      |                                                       | 1.2                 | 0.4               | V (max          |

| V <sub>OSDh</sub>           | OSD Input High Input Voltage                                     |                                                       | 1.6                 | 2.0               | V (min          |

| V <sub>4I</sub>             | OSD Select Low Input Voltage                                     | Video Inputs are Selected                             | 1.2                 | 0.8               | V (max          |

| V <sub>4h</sub>             | OSD Select High Input Voltage                                    | OSD Inputs are Selected                               | 1.6                 | 2.0               | V (min          |

| I <sub>41</sub>             | OSD Select Low Input Current                                     | $V_4 = 0V$                                            | -3.0                | -5.0              | μA (ma          |

| l <sub>4h</sub>             | OSD Select High Input Current                                    | V <sub>4</sub> = 12V                                  | 0.01                | 2.0               | μA (mi          |

| $\Delta V_{O-OSD(1V)}$      | OSD ∆Black Level Output Voltage,<br>Difference from Video Output | V <sub>25</sub> = 1V                                  | ±85                 | ±175              | mV (ma          |

| V <sub>OSD-out</sub>        | OSD Output Voltage V <sub>PP</sub>                               | V <sub>14</sub> = 4V, V <sub>Drive</sub> = 2V         | 4.5                 |                   | V <sub>PP</sub> |

| ΔV <sub>OSD-out</sub>       | OSD Output V <sub>PP</sub> Attenuation                           | V <sub>14</sub> = 2V, V <sub>Drive</sub> = 2V         | 50                  | 30                | % (mir          |

| ∆V <sub>OSD-out match</sub> | Output Match between Channels                                    | V <sub>14</sub> = 4V, V <sub>Drive</sub> = 2V         | ±2.0                |                   | %               |

| V <sub>OSD-out track</sub>  | Output Variation between Channels                                | $V_{14} = 4V$ to 2V, $V_{Drive} = 2V$                 | ±3.5                |                   | %               |

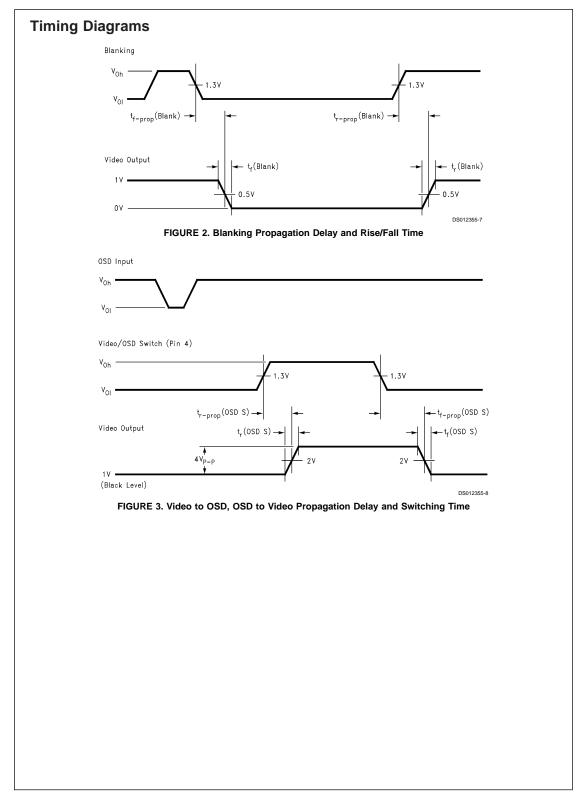

| t <sub>r</sub> (OSD S)      | Video to OSD Switch Time (Note 11)                               | $V_1 = V_2 = V_3 = 4V$ (Note 16)                      | 4                   |                   | ns              |

| t <sub>f</sub> (OSD S)      | OSD to Video Switch Time (Note 11)                               | $V_1 = V_2 = V_3 = 4V$ (Note 16)                      | 11                  |                   | ns              |

| t <sub>r-prop</sub> (OSD S) | Video to OSD Propagation Delay                                   | $V_1 = V_2 = V_3 = V_{13} = V_{14} = 4V$              | 11                  |                   | ns              |

| f-prop (OSD S)              | OSD to Video Propagation Delay                                   | $V_1 = V_2 = V_3 = V_{13} = V_{14} = 4V$              | 12                  |                   | ns              |

| r (OSD)                     | OSD Rise Time at V <sub>O</sub> (Note 11)                        | V <sub>14</sub> = 4V; V <sub>25</sub> = 1V            | 4                   |                   | ns              |

| f (OSD)                     | OSD Fall Time at V <sub>O</sub> (Note 11)                        | V <sub>14</sub> = 4V; V <sub>25</sub> = 1V            | 10                  |                   | ns              |

| r-prop (OSD)                | Starting OSD Propagation Delay                                   | V <sub>14</sub> = 4V; V <sub>25</sub> = 1V            | 6.5                 |                   | ns              |

| f-prop (OSD)                | Ending OSD Propagation Delay                                     | V <sub>14</sub> = 4V; V <sub>25</sub> = 1V            | 9                   |                   | ns              |

| V <sub>feed</sub> 10 kHz    | Video Feedthrough into OSD                                       | $V_{14} = 4V; V_{25} = 1V;$<br>$V_1 = V_2 = V_3 = 0V$ | -70                 |                   | dB              |

| / <sub>feed</sub> 10 MHz    | Video Feedthrough into OSD                                       | $V_{14} = 4V; V_{25} = 1V;$<br>$V_1 = V_2 = V_3 = 0V$ | -60                 |                   | dB              |

Note 3: V<sub>CC</sub>supply pins 6, 9, and 22 must be externally wired together to prevent internal damage during V<sub>CC</sub> power on/off cycles.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Typical specifications are specified at +25°C and represent the most likely parametric norm.

Note 6: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 7: The supply current specified is the quiescent current for  $V_{CC1}$  and  $V_{CC2}$  with  $R_L = \infty$ , see Figure 5's test circuit. The supply current for  $V_{CC2}$  (pin 22) also depends on the output load. With video output at 1V DC, the additional current through  $V_{CC2}$  is 8 mA for Figure 5's test circuit.

Note 8: Output voltage is dependent on load resistor. Test circuit uses RL = 390 $\Omega$ .

Note 9: Measure gain difference between any two amplifiers. V\_{IN} = 400 mV\_{PP}.

Note 10:  $\Delta A_V$  track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three attenuators. It is the difference in gain change between any two amplifiers with the contrast voltage (V<sub>13</sub>) at either 4V or 2V measured relative to an  $A_V$  max condition,  $V_{13} = 4V$ . For example, at  $A_V$  max the three amplifiers' gains might be 17.1 dB, 16.9 dB, and 16.8 dB and change to 11.2 dB, 10.9 dB and 10.7 dB respectively for  $V_{13} = 2V$ . This yields the measured typical ±0.1 dB channel tracking.

Note 11: When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit board without socket is recommended. Video amplifier 10 MHz isolation test also requires this printed circuit board. The reason for a double sided full ground plane PCB is that large measurement variations occur in single sided PCBs.

Note 12: Adjust input frequency from 10 MHz (A<sub>V</sub> max reference level) to the -3 dB corner frequency (f<sub>-3 dB</sub>).

Note 13: Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at f<sub>IN</sub> = 10 MHz for V<sub>sep 10 MHz</sub>.

Note 14: A minimum pulse width of 200 ns is guaranteed for a horizontal line of 15 kHz. This limit is guaranteed by design. If a lower line rate is used a longer clamp pulse may be required.

Note 15: During the AC test the 4V DC level is the center voltage of the AC output signal. For example, if the output is 4 V<sub>PP</sub> the signal will swing between 2V DC and 6V DC.

Note 16: When  $V_1 = V_2 = V_3 = 0V$  and the video input is 0.7V, then  $t_r$  (OSD) = 11 ns and  $t_f$ (OSD) = 4 ns. The Video Output waveform will be inverted from the one shown in *Figure 3*. Thus  $t_r$  (OSD) is actually a fall time and  $t_f$  (OSD) is actually a rise time in this condition.

.

| Pin No.                    | Pin Name                                                                  | Schematic                                               | Description                                                                                                                                                                                                                      |

|----------------------------|---------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3                | Red OSD Input<br>Green OSD Input<br>Blue OSD Input                        | OSD OF Sk                                               | These inputs accept standard TTL inputs. Eac<br>color is either fully on (logic high) or fully off<br>(logic low). Connect unused pins to ground<br>with a 47k resistor.                                                         |

| 4                          | Video/OSD Switch                                                          | Video/OSD<br>Switch                                     | This input accepts a standard TTL input.<br>H = OSD<br>L = Video<br>Connect to ground with a 47k resistor when<br>not using OSD.                                                                                                 |

| 5<br>8<br>11               | Red Video In<br>Green Video In<br>Blue Video In                           | Video<br>Input<br>Used to Clamp<br>Input DC Black Level | Video inputs. These inputs <b>must</b> be AC<br>Coupled with a minimum of a 1 $\mu$ F cap, 10 $\mu$ F<br>is preferred. DC restoration is done at these<br>inputs. A series resistor of about 33 $\Omega$ should<br>also be used. |

| 6<br>9                     | V <sub>CC1</sub>                                                          | · · ·                                                   | Power supply pins (excluding output stage)                                                                                                                                                                                       |

| 7<br>10<br>21              | Ground                                                                    |                                                         | Ground pins. All grounds are internally<br>connected and must also be connected on the<br>PCB.                                                                                                                                   |

| 12                         | V <sub>REF</sub>                                                          |                                                         | Pin used for additional filter capacitor to internal reference. The voltage at this pin is 2.0V.                                                                                                                                 |

| 13<br>14<br>26<br>27<br>28 | Video Contrast<br>OSD Constrast<br>Blue Drive<br>Green Drive<br>Red Drive | 5.3V 50 µA                                              | Contrast control pins:<br>4V — no attenuation<br>0V — over 60 dB attenuation<br>Drive control pins:<br>4V — no attenuation<br>0V — 12 dB attenuation                                                                             |

| 15<br>16                   | Clamp Gate<br>Blank Gate                                                  | Clamp/Blank                                             | Both pins accept TTL inputs and are active<br>low. The clamp gate provides DC restoration<br>the video signal. The blank gate forces the<br>video outputs to below 200 mV.                                                       |

| 17<br>19<br>24             | Blue Clamp Cap<br>Green Clamp Cap<br>Red Clamp Cap                        | V<br>VCC1<br>Clamp<br>Cap                               | The external clamp cap is charged and discharged to the correction voltage needed for DC restoration. 0.1 µF is the recommended value.                                                                                           |

www.national.com

10

| Pin No.        | Pin Name                                           | Schematic                                          | Description                                                                                                                               |

|----------------|----------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 18<br>20<br>23 | Blue Video Out<br>Green Video Out<br>Red Video Out | V <sub>CC2</sub><br>50Ω<br>Video<br>Output<br>5 mA | Video output. For proper black level the output must drive $390\Omega$ impedance.                                                         |

| 22             | V <sub>CC2</sub>                                   |                                                    | Power supply pin for the output stage. There are no internal connections to $V_{CC1}$                                                     |

| 25             | RGB Cutoff Adjust                                  | Cutoff Cutoff                                      | Sets the black level of the video outputs to all<br>three channels. Range is 0V to 4V. Minimum<br>black level is limited to about 300 mV. |

#### **Functional Description**

Figure 1 on the front page shows the block diagram of the LM1281 along with the pinout of the IC. Each channel receives both a video signal and an OSD signal at its input amplifier (-A1). The Video/OSD Switch signal also goes to the input amplifiers, controlling whether the video or the OSD signal passes through the LM1281. Both the OSD inputs and the Video/OSD Switch accept standard TTL signals. If video is selected then a TTL low is applied to pin 4, for OSD a TTL high needs to be applied. When the OSD feature is not used, then pin 4 needs to be connected to ground via a 47k resistor. Although the OSD input signal is a TTL signal, the input amplifier processes this signal to match the video levels. A TTL high signal will be at the video white level and a TTL low signal will typically be within 100 mV of the video black level. Note that by using the LM1281 the monitor designer connects the OSD input signals directly to the IC with NO signal processing.

DC restoration is performed on the video inputs to the LM1281. Remember video inputs are always AC coupled to the video pre-amp. There is no DC standard for the video input, therefore AC coupling the video inputs is necessary for proper operation of the monitor. A minimum capacitance of 1  $\mu$ F is recommended at the video input pins. The preferred value is 10  $\mu$ F. Part of the signal processing of the TTL OSD inputs is matching the black level of the OSD signal (TTL low) to the black level of the video signal. With AC coupling of the video inputs, DC restoration must be done at the input to perform the black level matching.

The next stage in the LM1281 is the Contrast Attenuation. Both the video and OSD contrast controls go to this stage. For easy interfacing to 5V DACs all control inputs, including these two controls, use a 0V to 4V range. Both contrast controls give no attenuation at 4V and full attenuation (over -50 dB) at 0V. The video and OSD contrast adjustments are completely independent of each other, allowing the user to set the desired contrast of the OSD window without affecting the video portion of the display. There is only one output from this section, any adjustments on the signal path beyond the contrast stage affects both the video signal and the OSD signal.

Following the Contrast Attenuation block is the Drive Attenuation. By having the Drive Attenuation past the contrast stage, any adjustment made on the video signal will **equally** affect the OSD signal. This configuration simplifies the white level adjustment. When the white level of the video is adjusted then the OSD white level is automatically set. The only OSD adjustment necessary when using the LM1281 is the OSD contrast. Note that when performing the white level adjustments the video portion of the display must be used, because there are minor variations between the OSD levels and the video levels.

The output stage is the -A2 amplifier. This stage is similar to the LM1205 output stage, where the video output can be blanked to a level below the video black level. A blacker than black output during blanking provides the capability to blank at the cathodes of the CRT. This eliminates the need for using high voltage transistors at G1 of the CRT to perform the blanking function. When the outputs are blanked the LM1281 can still DC restore the video output signal by using the Clamp Gate. There is an internal feedback stage that does the DC restoration. In order to maintain the correct video levels based on this feedback loop, the video output of the LM1281 must be terminated with a  $390\Omega$  impedance. The required correction voltage for DC restoration is stored on the clamp cap. A value of 0.1  $\mu F$  is recommended for the clamp cap. If the cap value is too small then there will be a tilt (shift) in the DC level of the video output during the horizontal scan. If the cap value is too large, then the DC restoration circuit may not be able to maintain the proper DC level of the video signal. Since DC restoration is also done at the video inputs, larger clamp cap values will be less of a problem with the LM1281 than with most other video preamps. The reference level for the DC restoration circuit is set at the RGB Cutoff Adjust pin (pin 25). Most monitor applications AC

#### Functional Description (Continued)

couple the preamp output to the cathode drivers. Therefore only one cutoff adjustment is provided, this is used primarily to optimize the operation of the cathode drivers.

Note that the Blank and Clamp Gates are active low. These pins are normally controlled by standard TTL signals. For video applications the Clamp Gate must be used. There are designs where the blank function may not be required. When the Blank Gate is not used, it must be tied high by a pullup resistor. A resistor value of 47k is acceptable, going to either 4V or 12V.

Gain of -A2 is controlled by the Drive Adjust pins. These are also 0V to 4V control voltages. 4V results in no attenuation at -A2, and 0V results in a -12 dB attenuation. The 12 dB adjustment range should provide more than enough adjustment for setting the white level. Note that a 12 dB range gives a 4 to 1 range in the output levels between the three channels.

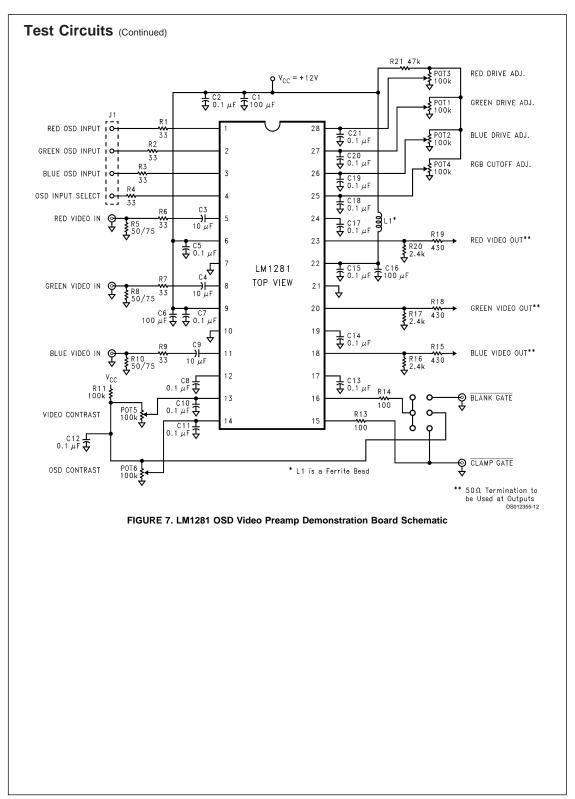

#### Applications of the LM1281

A schematic for a demonstration board is shown in Figure 7. This board was used for the characterization of the LM1281. Note that a 33  $\!\Omega$  resistor is in series with all inputs to the IC that receive external signals. These resistors are recommended to protect the IC from any sudden voltage surges that may result during the power up and power down modes, or when connecting the monitor to other equipment. The monitor designer should include these resistors in his design. If additional protection against ESD at the video inputs is necessary, then adding clamp diodes on the IC side of the  $33\Omega$  resistor is recommended; one to  $V_{\text{CC1}}$  and one to ground. Normally a designer may want to increase the value of the 33 $\Omega$  resistor at pins 5, 8, and 11 for additional ESD protection at the video inputs. Remember that the input capacitor to the video inputs is also part of the DC restoration circuit. This circuit is depending on a maximum circuit resistance of about 110 $\Omega$ . The 33 $\Omega$  resistors should not be increased in value. The internal ESD protection and the external clamp diodes, one to +12V and the other to ground, will provide excellent ESD protection.

Interfacing to the OSD inputs is quite easy since the signal processing necessary to match the OSD signals to the video levels is done internally by the LM1281. However, proper design techniques must be followed in assuring that a good TTL signal is received at the LM1281. Ground bounce in the TTL signal can cause improper switching times, possibly with multiple switching. Such affects will result in degradation in the quality of the displayed OSD window. The final TTL stage needs to be located near the LM1281 to assure clean TTL signals. Propagation delay is another source capable of degrading the OSD display. The optimum condition is to have all OSD signals originate from one register, keeping the variation in the propagation delays under 5 ns. If the OSD feature is not used, or the lines may be disconnected for some testing operations, then the Video/OSD Switch pin (pin 4) must have a pull down resistor to ground to insure operation in the video mode. Using a 47k pull down resistor will keep this pin low, and provide enough resistance to where the pin can still be driven directly by a TTL signal. Pins 1 through 3 should also be terminated the same way, eliminating the potential to switch logic levels just from the noise at the open pins.

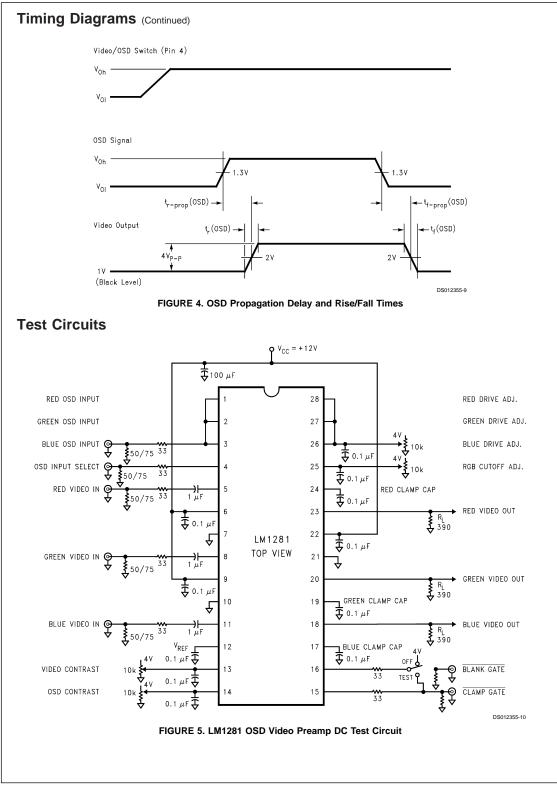

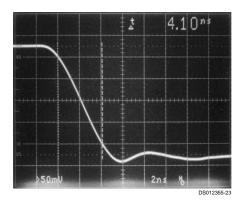

*Figure 2* through *Figure 4* show the timing diagrams for the LM1281. When measuring propagation delays all TTL signals are measured at the time they cross 1.3V. The video

output is set to 4  $V_{\rm PP}.$  Propagation delay is measured when the output is half way in its transition (changed by 2V). Rise and fall times of the video output are measured between the 10% and 90% points of the transitions.

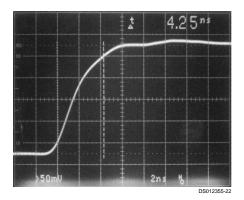

Board layout is always critical in a high frequency application such as using the LM1281. A poor layout can result in ringing of the video waveform after sudden transitions, or the part could actually oscillate. A good ground plane and proper routing of the +12V are important steps to a good PCB layout. The LM1281 can operate on a single sided board with a good layout. A ground plane is recommended and it is best to isolate the output stage grounds from the rest of the circuit. Also the two grounds should be connected together only at one point, ideally where the ground cable is connected to the board ground. Yes, all grounds are connected internally, but trace resistance can still allow for ground bounce, giving enough feedback for oscillations. The output stage power supply pin, pin 22, does not have an internal connection to the other power supply pins. This pin must be connected to the +12V supply, preferably with high frequency isolation. This is easily done with a ferrite bead between pin 22 and the +12V supply. Figures Figure 8 and Figure 9 show the waveform obtained with the LM1281 using the single sided demo board designed for this part.

FIGURE 8. LM1281 Rise Time

FIGURE 9. LM1281 Fall Time

#### References

Zahid Rahim, "Guide to CRT Video Design," Application Note 861, National Semiconductor Corp., Jan. 1993

Ott, Henry W. Noise Reduction Techniques in Electronic systems , John Wiley & Sons, New York, 1976

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated