### LM604A/LM604 4 Channel Mux-Amp

### **General Description**

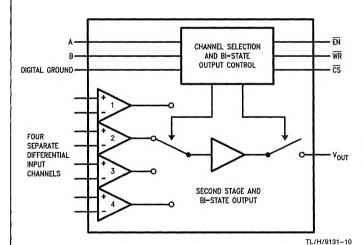

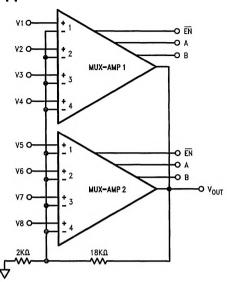

The LM604 Mux-Amp is an op-amp with four selectable differential inputs, combining the functions of a multiplexer with an op-amp. The LM604 can select, buffer, and amplify one of four different input signals, providing a complete system for multiplexing analog signals. It also has the unique Bi-State output which allows two or more Mux-Amps to be connected together at their outputs to increase the number of multiplexed channels. Channel selection and the Bi-State output are controlled by internal logic that interfaces directly to a microprocessor. Besides these unique features, the LM604 has excellent AC and DC op-amp specifications and is internally compensated.

Applications include signal multiplexing and linear circuits that are controlled by digital signals (i.e., programmable gain blocks, filters, and other op-amp circuits).

#### **Features**

- Multiplexes four differential input channels to a single op-amp

- Easy to interface to microprocessor, or operates "stand alone"

- Bi-State output: Operates in two states, Active and Disabled. When disabled, it becomes a high impedance.

- Wide operating voltage range single supply

4V to 32V ±2V to ±16V

split supply

Wide input common mode range

V- to V+-1V

■ Fast channel to channel switching time

5 μs

■ Output will drive a 600Ω load

### **Block Diagram**

#### **Channel Selection**

| Α | В | WR | CS | Channel   |

|---|---|----|----|-----------|

| 0 | 0 | 0  | 0  | 1         |

| 0 | 1 | 0  | 0  | 2         |

| 1 | 0 | 0  | 0  | 3         |

| 1 | 1 | 0  | 0  | 4         |

| X | Х | X  | 1  | Unchanged |

| Х | Χ | 1  | X  | Unchanged |

#### **Bi-State Output Control**

| l | EN | WR | CS | Output State     |

|---|----|----|----|------------------|

| ĺ | 0  | 0  | 0  | Enabled          |

|   | 1  | 0  | 0  | Disabled, High Z |

| 1 | Х  | X  | 1  | Unchanged        |

|   | Х  | 1  | Х  | Unchanged        |

| • |    |    |    |                  |

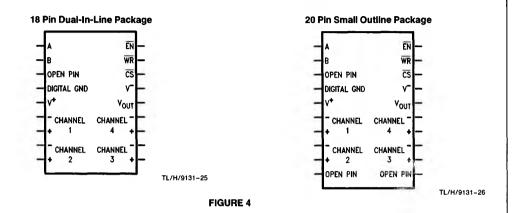

Order Number LM604AMJ, LM604IJ, LM604IN, LM604ACN, LM604CN, LM604ACM, or LM604CM See NS Package Number J18A, N18A or M20B

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 36V or ±18V

Differential Input Voltage ± Supply Voltage

Input Voltage Range ± Supply Voltage

Output Short Circuit to Gnd Continuous (Note 1)

ESD Tolerance (C<sub>7AP</sub> = 120 pF,

$R_{ZAP} = 1500\Omega$ ) 2,000V Lead Temperature (Soldering, 5 sec.) 300°C Storage Temperature Range  $-65^{\circ}$ C to 150°C Operating Ambient Temperature Range

J Pkg. M Pkg. N Pkg.

Power Dissipation (Note 2) 1,600 mW 1,500 mW 1,900 mW  $T_{JMAX}$  150°C 150°C 150°C  $\theta_{JA}$  (Typical, 75°C/W 83°C/W 65°C/W

Board Mounted)

### DC Electrical Characteristics V<sub>SUPPLY</sub> = ±15V (Note 3)

|                                            |                             |                         |                | LM6                                           | D4AM                        | LMC                         | 6041                        | LM604AC<br>LM604C           |                             |                          |  |

|--------------------------------------------|-----------------------------|-------------------------|----------------|-----------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------|--|

| Parameter                                  | Conditi                     | ions                    | Typical        | Tested<br>Limit<br>(Note 4)                   | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Units<br>(Limit          |  |

| Input Offset Voltage<br>(V <sub>OS</sub> ) | $R_S = 10 \mathrm{k}\Omega$ | LM604<br>LM604A         | 1.0<br>0.5     | 1.0<br><b>3.0</b>                             |                             | 3.0                         | 5.0                         | 3.0<br>1.0                  | 5.0<br>3.0                  | mV<br>(Max)              |  |

| V <sub>OS</sub> Temperature<br>Drift       |                             |                         | 5.5            |                                               |                             |                             |                             |                             |                             | μV/°C                    |  |

| Input Offset Current (IOS)                 |                             |                         | 2              | 10<br><b>12</b>                               |                             | 10                          | 12                          | 10                          | 12                          | nA<br>(Max)              |  |

| I <sub>OS</sub> Temperature<br>Drift       |                             |                         | 10             |                                               |                             |                             |                             |                             |                             | pA/°C                    |  |

| Input Bias Current (I <sub>B</sub> )       |                             | LM604<br>LM604A         | 50<br>30       | 50<br><b>60</b>                               |                             | 80                          | 100                         | 80<br>50                    | 100<br>60                   | nA<br>(Max)              |  |

| I <sub>B</sub> Temperature<br>Drift        |                             |                         | 55             |                                               |                             |                             |                             |                             |                             | pA/°C                    |  |

| Input Common<br>Mode Voltage<br>Range      |                             | Upper Limit Lower Limit | 14.0<br>-15.0  | 13.5<br><b>13.0</b><br>-15.0<br>- <b>15.0</b> |                             | 13.5<br>- 15.0              | 13.0<br>- 15.0              | 13.5<br>15.0                | 13.0<br>- 15.0              | V<br>(Min)<br>V<br>(Max) |  |

| Input Resistance                           |                             |                         | 1.0            |                                               |                             |                             |                             |                             |                             | Meg s                    |  |

| Output Voltage<br>Swing                    | $R_L = 10  k\Omega$         | Upper Limit             | 13.4<br>- 14.2 | 13.0<br><b>12.5</b><br>-13.8                  |                             | 13.0<br>- 13.8              | 12.5<br>- 13.3              | 13.0<br>- 13.8              | 12.5<br>- 13.3              | V<br>(Min)<br>V          |  |

|                                            | $R_L = 600\Omega$           | Upper Limit             | 12.7           | - <b>13.3</b><br>12.3<br><b>10.0</b>          |                             | 12.3                        | 10.0                        | 12.3                        | 10.0                        | (Max)<br>V<br>(Min)      |  |

|                                            |                             | Lower Limit             | -12.6          | -12.2<br>-11.7                                | }                           | -12.2                       | -11.7                       | -12.2                       | 1 1.7                       | V<br>(Max)               |  |

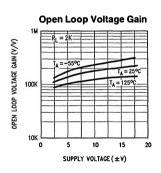

| Large Signal<br>Voltage Gain               | $V_{OUT} = \pm 10V$         | _                       | 200            | 50<br><b>25</b>                               |                             | 50                          | 25                          | 50                          | 25                          | V/m\<br>(Min)            |  |

|                                            |                             | $R_L = 600\Omega$       | 200            | 50<br><b>25</b>                               |                             | 50                          | 25                          | 50                          | 25                          |                          |  |

| Common Mode<br>Rejection Ratio             | $V_{CM} = -15.0V$           | to 13.5V                | 100            | 80<br><b>70</b>                               |                             | 80                          | 70                          | 80                          | 70                          | dB<br>(Min)              |  |

# DC Electrical Characteristics $V_{SUPPLY} = \pm 15V$ (Note 3)

| Parameter                       |                                                                  |         | LM604AM             |                             | LM604I                      |                             | LM604AC<br>LM604C           |                             |                  |  |

|---------------------------------|------------------------------------------------------------------|---------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------------------|--|

|                                 | Conditions                                                       | Typical | Limit               | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Units<br>(Limit) |  |

| Power Supply<br>Rejection Ratio | $V_{SUPPLY} = \pm 5.0V \text{ to } \pm 16.0V$                    | 100     | 80<br><b>70</b>     |                             | 80                          | 70                          | 80                          | 70                          | dB<br>(Min)      |  |

| Output Short Circuit<br>Current |                                                                  | ±35     | ±50<br>± <b>60</b>  |                             | ±50                         | ±60                         | ±50                         | ±60                         | mA<br>(Max)      |  |

| Output Leakage<br>Current       | $V_{OUT} = -13.5V \text{ to } 13.0V$<br>Bi-State Output Disabled | 4.0     | 10.0<br><b>20.0</b> |                             | 10.0                        | 20.0                        | 10.0                        | 20.0                        | μΑ<br>(Max)      |  |

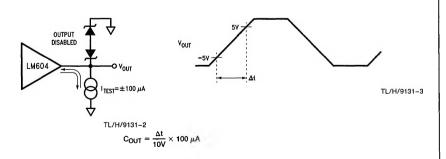

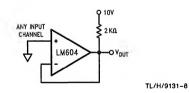

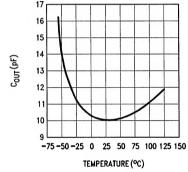

| Output Capacitance              | Bi-State Output Disabled<br>See <i>Figure 1</i>                  | 10      |                     |                             |                             |                             |                             |                             | pF               |  |

| Supply Current                  |                                                                  | 7.0     | 9.0<br><b>10.0</b>  |                             | 9.0                         | 10.0                        | 9.0                         | 10.0                        | mA<br>(Max)      |  |

### AC Electrical Characteristics V<sub>SUPPLY</sub> = ±15V (Note 3)

|                                             |                                                                          |                  | LM604AM    |                             | 04AM  | LM6041                      |                             | LM604AC<br>LM604C           |                | Units         |

|---------------------------------------------|--------------------------------------------------------------------------|------------------|------------|-----------------------------|-------|-----------------------------|-----------------------------|-----------------------------|----------------|---------------|

| Parameter                                   | Condition                                                                | s                | Typicai    | Tested<br>Limit<br>(Note 4) | Limit | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Limit          | (Limit)       |

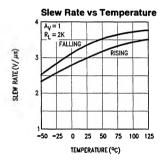

| Slew Rate                                   | $A_V = 1$ , $R_L = 2 k\Omega$                                            |                  | 3.0        | 2.0<br><b>1.5</b>           |       | 2.0                         | 1.5                         | 2.0                         | 1.5            | V/μs<br>(Min) |

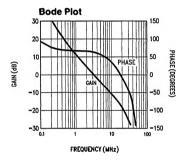

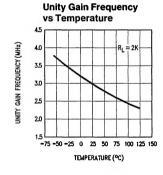

| Gain Bandwidth<br>Product                   | f = 100 kHz                                                              |                  | 7.0        | 6.0<br><b>3.0</b>           |       | 6.0                         | 3.0                         | 6.0                         | 3.0            | MHz<br>(Min)  |

| Unity Gain<br>Frequency                     |                                                                          |                  | 3.0        |                             | 2.5   |                             | 2.5                         |                             | 2.5            | MHz<br>(Min)  |

| Phase Margin                                | $R_L = 2 k\Omega, C_L = 200 \mu$                                         | oF               | 50         |                             |       |                             |                             |                             |                | Degrees       |

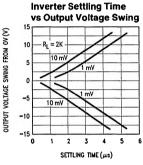

| Settling Time to 0.1% of Final Value        | $A_V = -1$ , $V_{OUT} = -5$<br>$R_L = 2 k\Omega$                         | .0V to 5.0V      | 4.0        |                             |       |                             |                             |                             |                | μs            |

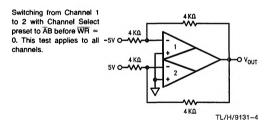

| Channel Switching<br>Time                   | See <i>Figure 2</i>                                                      | tsw1             | 4.0<br>5.0 | 5.5<br><b>6.5</b>           | 6.5   | 5.5                         | <b>6.5</b><br>6.5           | 5.5                         | <b>6.5</b> 6.5 | μs<br>(Max)   |

|                                             | $R_S = 10 \text{ k}\Omega, f = 10 \text{ kH}$<br>$V_{IN} = 10.0 V_{p-p}$ | lz               | 100        |                             |       |                             |                             | _                           |                | dB            |

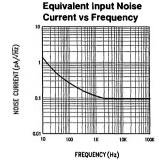

| Input Noise Voltage                         | $R_S = 100 \Omega$ , $f = 1 \text{ kHz}$                                 | 2                | 20         |                             |       |                             |                             |                             |                | nV/√Hz        |

| Input Noise Current                         | f = 1 kHz                                                                |                  | 0.3        |                             |       |                             |                             |                             |                | pA/√Hz        |

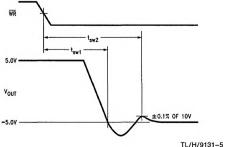

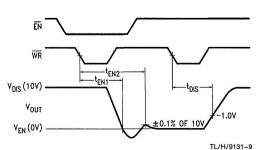

| Mux-Amp Enable<br>Time                      | See <i>Figure 3</i>                                                      | t <sub>EN1</sub> | 3.0        | 4.0<br><b>5.0</b>           |       | 4.0                         | 5.0                         | 4.0                         | 5.0            | μs<br>(Max)   |

|                                             |                                                                          | t <sub>EN2</sub> | 4.0        |                             | 5.5   | <u> </u>                    | 5.5                         |                             | 5.5            |               |

| Mux-Amp Disable<br>Time (t <sub>DIS</sub> ) | See <i>Figure 3</i>                                                      |                  | 1.0        | 2.0<br><b>3.0</b>           |       | 2.0                         | 3.0                         | 2.0                         | 3.0            | μs<br>(Max)   |

# DC Electrical Characteristics V<sub>SUPPLY</sub> = 5V (Note 3)

|                                       | Conditions                                               |                                      |            | LM60                                   | 04AM                               | LMC                         | 6041                               | LM604AC<br>LM604C           |                                    | Units                    |

|---------------------------------------|----------------------------------------------------------|--------------------------------------|------------|----------------------------------------|------------------------------------|-----------------------------|------------------------------------|-----------------------------|------------------------------------|--------------------------|

| Parameter                             |                                                          |                                      | Typical    | Tested<br>Limit<br>(Note 4)            | Design<br>Limit<br>(Note 5)        | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5)        | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5)        | (Limit)                  |

| Input Offset Voltage                  | $R_S = 10 \text{ k}\Omega$<br>$V_{OUT} = 2.0V$           | LM604<br>LM604A                      | 1.0<br>0.5 | 1.0<br><b>3.0</b>                      |                                    | 3.0                         | 5.0                                | 3.0<br>1.0                  | 5.0<br>3.0                         | mV<br>(Max)              |

| Input Offset Current                  | V <sub>OUT</sub> = 2.0V                                  |                                      | 3.0        | 10<br><b>18</b>                        |                                    | 10                          | 18                                 | 10                          | 18                                 | nA<br>(Max)              |

| Input Bias Current                    | V <sub>OUT</sub> = 2.0V                                  | LM604<br>LM604A                      | 70<br>50   | 80<br>110                              |                                    | 130                         | 150                                | 130<br>80                   | 150<br>110                         | nA<br>(Max)              |

| Input Common<br>Mode<br>Voltage Range | V <sub>OUT</sub> = 2.0V                                  | Upper Limit                          | 4.0<br>0   | 3.5<br><b>3.0</b><br>0                 |                                    | 3.5<br>0                    | 3.0<br>0                           | 3.5<br>0                    | 3.0<br>0                           | V<br>(Min)               |

| Output Voltage<br>Swing               | $R_L = 10 \text{ k}\Omega$                               | Upper Limit                          | 3.5<br>0.5 | 3.2<br><b>3.0</b><br>0.7<br><b>0.8</b> | -                                  | 3.2<br>0.7                  | 3.0<br>0.8                         | 3.2<br>0.7                  | 3.0<br>0.8                         | V<br>(Min)<br>V<br>(Max) |

|                                       | $R_L = 600\Omega$                                        | Upper Limit                          | 3.3<br>0.4 | 3.0<br><b>2.8</b><br>0.6<br><b>0.7</b> |                                    | 3.0<br>0.6                  | 2.8<br>0.7                         | 3.0<br>0.6                  | 2.8<br>0.7                         | (Min)<br>V<br>(Max)      |

| Large Signal<br>Voltage<br>Gain       | V <sub>OUT</sub> = 0.8V<br>to 2.8V                       | $R_L = 2 k\Omega$<br>$R_L 600\Omega$ | 200<br>200 |                                        | 50<br><b>25</b><br>50<br><b>25</b> |                             | 50<br><b>25</b><br>50<br><b>25</b> |                             | 50<br><b>25</b><br>50<br><b>25</b> | V/mV<br>(Min)            |

| Common Mode<br>Rejection Ratio        | V <sub>CM</sub> = 0V to 3.5V<br>V <sub>OUT</sub> = 2.0V  |                                      | 100        | 80<br><b>70</b>                        |                                    | 80                          | 70                                 | 80                          | 70                                 | dB<br>(Min)              |

| Power Supply<br>Rejection Ratio       | V <sup>+</sup> = 4.0V to 5.0V<br>V <sub>OUT</sub> = 2.0V |                                      | 100        | 80<br><b>70</b>                        |                                    | 80                          | 70                                 | 80                          | 70                                 | dB<br>(Min)              |

FIGURE 1. Output Capacitance Test

### **Digital Input Electrical Characteristics** V<sub>SUPPLY</sub> = ±15V (Note 6)

| Parameter                                |                     |         | LM604AM                     |                             | LM604I                      |                             | LM604AC<br>LM604C           |                             | Units       |

|------------------------------------------|---------------------|---------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------|

|                                          | Conditions          | Typical | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | (Limit)     |

| VINHS                                    |                     |         | 1.8<br><b>2.0</b>           |                             | 1.8                         | 2.0                         | 1.8                         | 2.0                         | V<br>(Min)  |

| V <sub>INLO</sub>                        |                     |         | 1.0<br><b>0.8</b>           |                             | 1.0                         | 0.8                         | 1.0                         | 0.8                         | V<br>(Max)  |

| linhi                                    |                     |         | 5.0<br><b>10.0</b>          |                             | 5.0                         | 10.0                        | 5.0                         | 10.0                        | μA<br>(Max) |

| INLO                                     |                     |         | 5.0<br><b>10.0</b>          |                             | 5.0                         | 10.0                        | 5.0                         | 10.0                        | μA<br>(Max) |

| Minimum Pulse<br>Width for WR & CS       |                     |         |                             | 100                         |                             | 100                         |                             | 100                         | ns<br>(Min) |

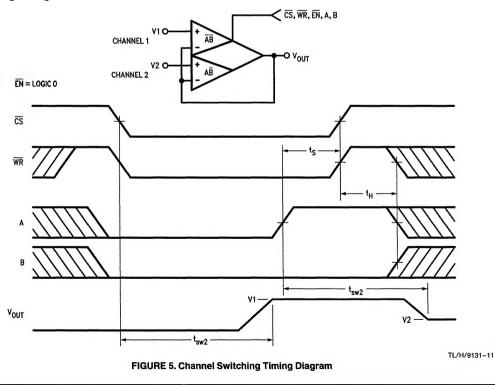

| Minimum Set-Up<br>Time (t <sub>S</sub> ) | See Figures 3 and 5 |         |                             | 100                         |                             | 100                         |                             | 100                         | ns<br>(Min) |

| Minimum Hold<br>Time (t <sub>H</sub> )   | See Figures 3 and 5 |         |                             | 50                          |                             | 50                          |                             | 50                          | ns<br>(Min) |

| Input Capacitance                        |                     | 5       |                             |                             |                             |                             |                             |                             | pF          |

Note 1: Applies to both single and split supply operation. Continuous short circuit operation can result in exceeding the maximum allowed junction temperature.

Note 2: When operating at T<sub>A</sub> > 25°C, the maximum power dissipation must be derated based on  $\theta_{\rm JA}$ .

Note 3: Unless specified otherwise, all limits are guaranteed for  $T_A = T_J = 25^{\circ}\text{C}$ ,  $V_{CM} = 0\text{V}$ ,  $V_{OUT} = 0\text{V}$ , and  $R_L > 1\text{Meg}\Omega$ . Boldface limits apply at  $0^{\circ}\text{C} \le T_J \le 70^{\circ}\text{C}$  for LM604AC and LM604C,  $-40^{\circ}\text{C} \le T_J \le 85^{\circ}\text{C}$  for LM604I, and  $-55^{\circ}\text{C} \le T_J 125^{\circ}\text{C}$  for LM604AM.

Note 4: Guaranteed and 100% production tested.

Note 5: Guaranteed but not 100% production tested. These numbers are not used to calculate outgoing quality levels.

Note 6: Unless specified otherwise, all units are guaranteed at T<sub>A</sub> = T<sub>J</sub> = 25°C. Boldface limits apply at the junction temperature extremes specified in note 3. Input voltage levels are with respect to digital ground (pin 4) which must be at least 4.0V below V<sup>+</sup>.

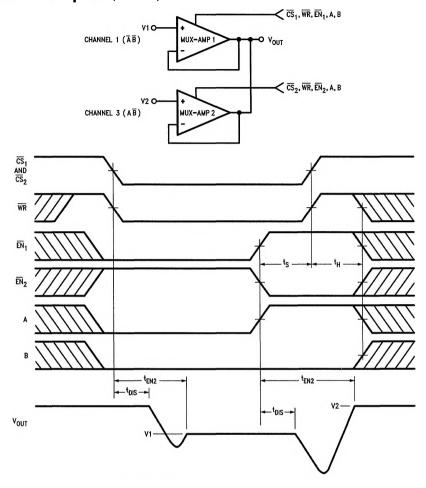

FIGURE 2. Channel Switching Time Test

FIGURE 3. Bi-State Output Enable and Disable Time Test

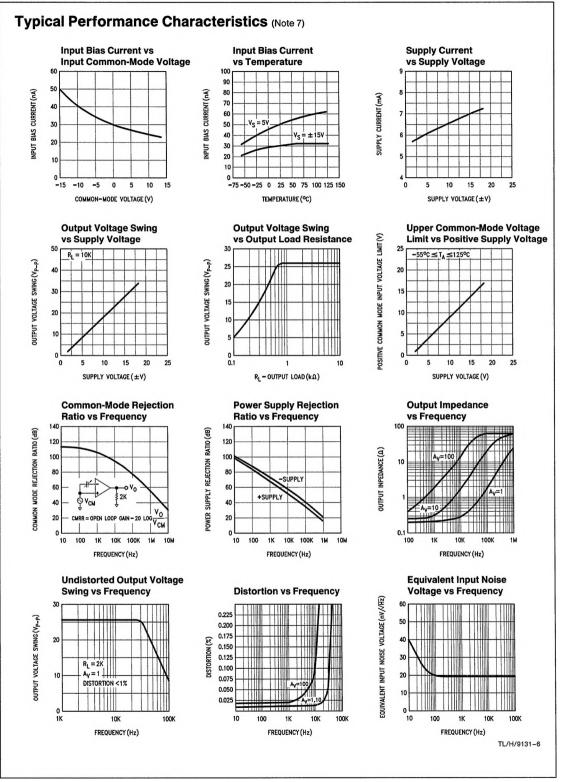

### **Typical Performance Characteristics** (Note 7)

TL/H/9131-7

Note 7: Unless specified otherwise,  $T_A = T_J = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = 0V$ ,  $V_{OUT} = 0V$ , and  $R_L > 1$  Meg.

### **Connection Diagrams**

### **Timing Diagrams**

#### **Functional Description**

#### INPUT CHANNEL SELECTION

The LM604 contains four differential input channels that are selected one at a time. An input is selected by writing its binary code to pins A and B when  $\overline{CS}$  and  $\overline{WR}$  are a logic 0, see block diagram. The LM604 always has one of its inputs selected. In order to isolate all four channels from the output, the Bi-State output can be disabled.

Figure 5 illustrates how the LM604 switches from one channel to another. The switching begins on the falling edge of  $\overline{WR}$  if A and B are valid before  $\overline{WR}$  is a logic 0, or when A and B become valid while  $\overline{WR}$  is a logic 0. In either case, the channel switching time ( $t_{SW2}$ ) remains the same. If a channel is to remain selected, its binary code must be valid during the rising edge of  $\overline{WR}$  as specified by  $t_S$  and  $t_H$ .

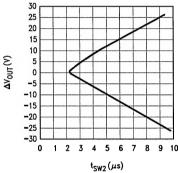

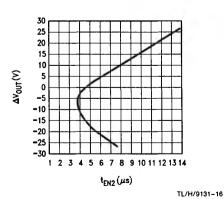

Channel switching time is specified by  $t_{SW1}$  and  $t_{SW2}$  as shown in Figure 2.  $t_{SW1}$  is the time it takes the output to first reach its new value, and  $t_{SW2}$  is the time it takes the output to settle to within 0.1% of its new value. Clearly,  $t_{SW2}$  is a more useful parameter for specifying switching time, but it is difficult to test on a production basis. Therefore,  $t_{SW1}$  is tested and this allows  $t_{SW2}$  to be guaranteed. Channel switching time will vary as a function of how far the output swings to reach its new value. This is shown in Figure 6 where  $t_{SW2}$  is plotted as a function of output voltage swing  $(\Delta V_{OIIT})$ .

TL/H/9131-12

$\Delta V_{OUT} = V_{OUT} \text{ (Selected Channel)} - V_{OUT} \text{ (Previous Channel)}$  FIGURE 6.  $t_{SW2}$  vs  $\Delta V_{OUT}$

#### **BI-STATE OUTPUT**

The Bi-State output can be either enabled (on) or disabled (off). When disabled, the output becomes a high impedance load that can be driven by another output stage. This allows several Mux-Amps to be connected together at their outputs by having only one output enabled at one time. Thus, several Mux-Amps can be in parallel to the same output to increase the number of multiplexed channels. The Bi-State output is controlled by  $\overline{EN}$  when  $\overline{CS}$  and  $\overline{WR}$  are a logic 0, see block diagram.

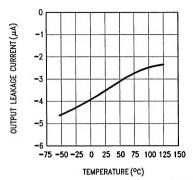

When the output is disabled and driven by another output, it behaves like a small capacitive load with a few microamps of leakage current. The data sheet specifies this with the parameters "Output Capacitance" and "Output Leakage Current". Both parameters vary with temperature, as shown in *Figure 7*.

TL/H/9131-13

TL/H/9131-14

#### FIGURE 7. ILEAKAGE and COUT vs Temperature

Figure  $\vartheta$  illustrates switching between two Mux-Amps that are connected in parallel to the same output. Switching begins on the falling edge of  $\overline{WR}$  if the  $\overline{EN}$  signals are correctly set before  $\overline{WR}$  is a logic 0, or when the  $\overline{EN}$  signals become valid while  $\overline{WR}$  is a logic 0. The Bi-State output takes less time to become disabled than it does to become enabled, and this insures the outputs are switched in a "break before make" method. If an in output is to remain enabled or disabled after  $\overline{WR}$  becomes a logic 1,  $\overline{EN}$  must be valid during the rising edge of  $\overline{WR}$  as specified by  $t_S$  and  $t_H$ . Note that when a Mux-Amp has its output enabled, the binary code for the selected input channel must also be written.

Bi-State output enable time ( $t_{EN1}$  and  $t_{EN2}$ ) and disable time ( $t_{DIS}$ ) are defined in *Figure 3*.  $t_{EN1}$  is the time it takes the output to first reach its enabled value ( $V_{EN}$ ), and  $t_{EN2}$  is the time it takes the output to settle to within 0.1% of  $V_{EN}$ . As with channel switching time,  $t_{EN1}$  is a tested parameter that allows  $t_{EN2}$  to be guaranteed.  $t_{DIS}$  is the time it takes the output to become a high impedance. Output enable time will vary according to how far the output swings from  $V_{DIS}$  to  $V_{EN}$ , and this is plotted in *Figure 9*.

### Functional Description (Continued)

FIGURE 8. Timing Diagram for Switching Bi-State Outputs

$\Delta V_{OUT} = V_{EN} - V_{DIS}$ FIGURE 9.  $t_{EN2}$  vs  $\Delta V_{OUT}$

#### DIGITAL CONTROL

As mentioned in the previous sections, the input channels and Bi-State output are controlled by logic levels on pins A, B, and  $\overline{\mathbb{E}}\mathbb{N}$ . There are two ways to apply logic levels to these pins. 1) Hardwire  $\overline{\mathbb{W}}\mathbb{N}$  and  $\overline{\mathbb{C}}\mathbb{N}$  directly to digital ground so that the LM604 operates in a "stand alone" mode. This allows input logic levels to directly control the LM604. 2) Write digital signals to A, B, and  $\overline{\mathbb{E}}\mathbb{N}$  as shown in the timing diagrams of Figures 5 and 8. This method is used when the LM604 interfaces to a microprocessor. Note that  $\overline{\mathbb{C}}\mathbb{N}$  and  $\overline{\mathbb{C}}\mathbb{N}$  and  $\overline{\mathbb{C}}\mathbb{N}$  and  $\overline{\mathbb{C}}\mathbb{N}$  and bold times are not required for  $\overline{\mathbb{C}}\mathbb{N}$ . Also, notice that  $\overline{\mathbb{C}}\mathbb{N}$  must remain a logic 1 during the hold time period.

Input logic levels are referenced to a 1.4V threshold voltage, making the LM604 compatible with TTL and CMOS logic. This threshold voltage is referenced to digital ground. The voltage level of digital ground can be as low as V<sup>-</sup> (pin 15) and as high as 4V below V<sup>+</sup> (pin 5).

#### **Application Hints**

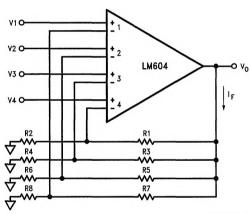

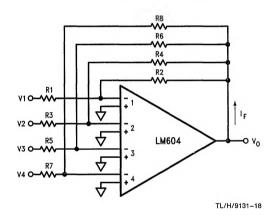

#### **USING MULTIPLE FEEDBACK LOOPS**

Each input channel of the LM604 is used as a single opamp with its own feedback loop. Two examples of this are circuits with multiple inverting gain channels and non-inverting gain channels (*Figure 10*). These circuits have multiple feedback loops connected to the same output with one feedback loop connected to a selected channel and the others connected to "off" channels. The feedback loop of the selected channel determines the gain of these circuits. The off channel feedback loops affect these circuits in two ways. 1) They create an additional load at the output. 2) Feedback loops for inverting gain channels provide feedthrough paths from the inputs of the off channels to the output.

In Figure 10, the loading affect of multiple feedback loops is given in terms of current flowing through the feedback loops ( $I_F$ ). In circuits with non-inverting gain channels,  $I_F$  is a function of  $V_{OUT}$  and the resistance of the feedback loops. In circuits with inverting gain channels,  $I_F$  is different for each channel selected because it is also a function of the off channel input voltages. This additional loading must be accounted for when designing Mux-Amp circuits. Otherwise, the output load resistance will be less than anticipated.

TL/H/9131-19

| Channel                                                     | V <sub>o</sub>                   |

|-------------------------------------------------------------|----------------------------------|

| 1                                                           | V1 (1 + R7 R8)                   |

| 2                                                           | $V2\left(1+\frac{R5}{R6}\right)$ |

| 3                                                           | V3 (1 + R3 R4)                   |

| 4                                                           | $V4\left(1+\frac{R1}{R2}\right)$ |

| $I_F = V_0 \left( \frac{1}{R1 + R2} + \frac{1}{R3} \right)$ | 1 + R4 + 1 R5 + R6 + 1 R7 + R8   |

Multiple Non-Inverting Gain Channels

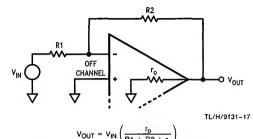

Figure 11 illustrates feedthrough in an off inverting gain channel. Feedthrough occurs because the feedback resistors and the Mux-Amp output impedance ( $r_0$ ) form a voltage divider. This divider allows a portion of the off channel's input signal to appear at the output. The amount of signal that feeds through depends on the ratio of output impedance to feedback loop resistance. Output impedance varies according to Mux-Amp gain (gain of the selected channel) and the frequency of the feedthrough signal. This variation must be considered when calculating feedthrough, and it is plotted in the "Typical Device Characteristics" section.

FIGURE 11. Inverting Gain Channel Feedthrough

| Channel | V <sub>o</sub>                   | l <sub>F</sub>                                                                                    |

|---------|----------------------------------|---------------------------------------------------------------------------------------------------|

| 1       | $-V1\left(\frac{R2}{R1}\right)$  | $\frac{V_0}{R2} + \frac{V_0 - V2}{R3 + R4} + \frac{V_0 - V3}{R5 + R6} + \frac{V_0 - V4}{R7 + R8}$ |

| 2       | $-v_2\left(\frac{R4}{R3}\right)$ | $\frac{V_0}{R4} + \frac{V_0 - V1}{R1 + R2} + \frac{V_0 - V3}{R5 + R6} + \frac{V_0 - V4}{R7 + R8}$ |

| 3       | -v3 ( <del>R6</del> )            | $\frac{V_0}{R6} + \frac{V_0 - V1}{R1 + R2} + \frac{V_0 - V2}{R3 + R4} + \frac{V_0 - V4}{R7 + R8}$ |

| 4       | $-V4\left(\frac{R8}{R7}\right)$  | $\frac{V_0}{R8} + \frac{V_0 - V1}{R1 + R2} + \frac{V_0 - V2}{R3 + R4} + \frac{V_0 - V3}{R5 + R6}$ |

Multiple Inverting Gain Channels

FIGURE 10. Circuits Using Multiple Inverting and Non-Inverting Gain Channels

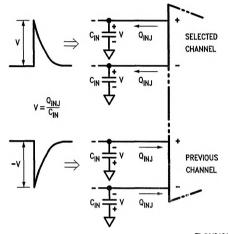

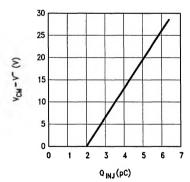

# Application Hints (Continued) INPUT CHARGE INJECTION

When the Mux-Amp switches channels, charge is injected from the inputs of the selected and previous channels, see Figure 12. This causes a positive error voltage at the input of the selected channel and a negative voltage at the previous channel. The amplitude of this error voltage equals  $Q_{\rm INJ}/C_{\rm IN}$ , where  $C_{\rm IN}$  is the total capacitance at the input and  $Q_{\rm INJ}$  is the charge injected. As plotted in Figure 13,  $Q_{\rm INJ}$  increases proportionally with the difference in voltage between a channel's input common mode voltage and the negative supply. The RC time constant of  $C_{\rm IN}$  times resistance seen from the input will determine how long the error voltage remains at the input.

TL/H/9131-20

FIGURE 12. Error Voltage From Input Charge Injection

TL/H/9131-21

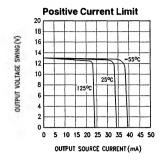

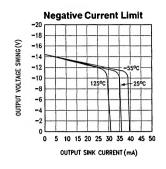

#### MAXIMUM OUTPUT LOAD CONDITIONS

The Mux-Amp is guaranteed to drive a  $600\Omega$  load as specified over its entire operating range. Reducing the load resistance below this value may cause the output to current

limit. It may also cause the junction temperature limit to be exceeded when operating the part near its maximum ambient temperature.

The Mux-Amp is unconditionally stable with as much as 500 pF connected from the output to ground. If the output is required to drive a larger capacitive load, the Mux-Amp may need to operate with at least a gain of 10. Otherwise, it may become unstable when sinking current.

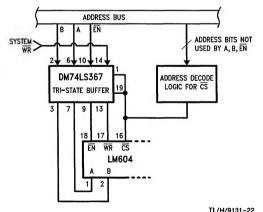

#### **DIGITAL FEEDTHROUGH**

When interfacing the Mux-Amp to a microprocessor, pins A, B, EN, and WR are connected to an address bus where high frequency digital signals are present. The fast edges of these signals can propagate into the Mux-Amp's analog signal path, causing fast transients to appear at the output. To avoid this problem, the following precautions should be taken.

- Analog and digital ground must be kept separate. They

can only be connected together back at the power supply or

supply bus.

- 2) Bypass capacitors should have low inductance to prevent noise spikes on the voltage supply pins. A ceramic disc capacitor of 0.1  $\mu F$  is usually sufficient.

- 3) All lead lengths should be kept short to prevent them from picking up digital signals.

By using these rules, digital signals can be attenuated at the input channels by typically 100 dB.

Lab measurements have shown a minimum digital feed-through signal of 2 mV occurs at the output even when the best layout precautions are taken. This is fine for many applications, but to completely eliminate digital feedthrough, any signals coming directly from the bus must be sent to the Mux-Amp via a Tri-State buffer, see *Figure 14*. This isolates the Mux-Amp's digital pins from the address bus to prevent pin to pin feedthrough. CS can be used to enable the Tri-State buffers when signals are sent to the Mux-Amp from the address bus.

FIGURE 14. Isolating Mux-Amp from Address

Bus by Using a Tri-State Buffer

### **Typical Applications**

| Mux-Amp<br>1 |   |    | N | iux-Ai | Input |    |  |

|--------------|---|----|---|--------|-------|----|--|

| Α            | В | EN | Α | В      | EN    | ,  |  |

| 0            | 0 | 0  | Х | Х      | 1     | V1 |  |

| 0            | 1 | 0  | X | X      | 1     | V2 |  |

| 1            | 0 | 0  | X | X      | 1     | V3 |  |

| 1            | 1 | 0  | X | X      | 1     | V4 |  |

| Х            | X | 1  | 0 | 0      | 0     | V5 |  |

| X            | X | 1  | 0 | 1      | 0     | V6 |  |

| X            | X | 1  | 1 | 0      | 0     | V7 |  |

| X            | X | 1  | 1 | 1      | 0     | V8 |  |

|              |   |    |   |        |       |    |  |

TL/H/9131-23

Eight Channel Multiplexer and Amplifier with a Gain of 10

110 ΚΩ 1% 54.9 KΩ 1% 1.5 nF 4.32 KΩ 1% 110 KΩ 1% 54.9 KΩ 1% VINO 1.5 nF 1 KΩ 1%€ LM604 110 KΩ 1% 54.9 KΩ 1% MUX-AMP 1.5 nF 54.9 KΩ 1% Center Frequency Channel 237Ω 1% \$ 1.5 nF 5 kHz +10Ω 1% 3 4 10 khz 15 kHz 20 kHz TL/H/9131-24

Programmable Bandpass Filter: Each channel has a 2 kHz bandwidth and a gain of 1 at the center frequency