# Dual 700MHz, 200mA Operational Amplifier

### **FEATURES**

- 700MHz Gain Bandwidth

- ±200mA Minimum I<sub>OUT</sub>

- Low Distortion: -72dBc at 1MHz,  $4V_{P-P}$ ,  $25\Omega$ ,  $A_V = 2$

- Stable in  $A_V \ge 10$ , Simple Compensation for  $A_V < 10$

- $\pm 4.3$ V Minimum Output Swing,  $V_S = \pm 6$ V,  $R_L = 25\Omega$

- 7mA Supply Current per Amplifier

- 200V/µs Slew Rate

- Stable with 1000pF Load

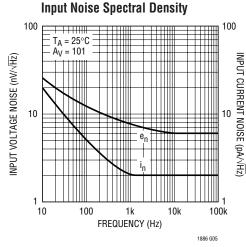

- 6nV/√Hz Input Noise Voltage

- 2pA/√Hz Input Noise Current

- 4mV Maximum Input Offset Voltage

- 4µA Maximum Input Bias Current

- 400nA Maximum Input Offset Current

- $\pm 4.5$ V Minimum Input CMR,  $V_S = \pm 6$ V

- Specified at ±6V, ±2.5V

## **APPLICATIONS**

- DSL Modems

- xDSL PCI Cards

- USB Modems

- Line Drivers

### DESCRIPTION

The LT®1886 is a 200mA minimum output current dual op amp with outstanding distortion performance. The amplifiers are gain-of-ten stable, but can be easily compensated for lower gains. The LT1886 features balanced, high impedance inputs with  $4\mu A$  maximum input bias current, and 4mV maximum input offset voltage. Single supply applications are easy to implement and have lower total noise than current feedback amplifier implementations.

The output drives a  $25\Omega$  load to  $\pm 4.3V$  with  $\pm 6V$  supplies. On  $\pm 2.5V$  supplies the output swings  $\pm 1.5V$  with a  $100\Omega$  load. The amplifier is stable with a 1000pF capacitive load which makes it useful in buffer and cable driver applications.

The LT1886 is manufactured on Linear Technology's advanced low voltage complementary bipolar process and is available in a thermally enhanced SO-8 package.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

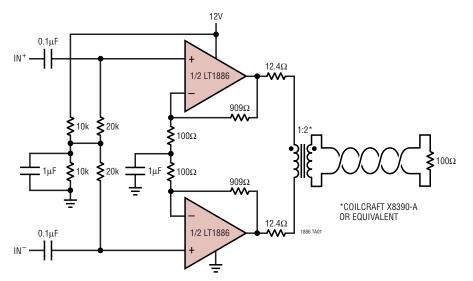

## TYPICAL APPLICATION

Single 12V Supply ADSL Modem Line Driver

### **ABSOLUTE MAXIMUM RATINGS**

###

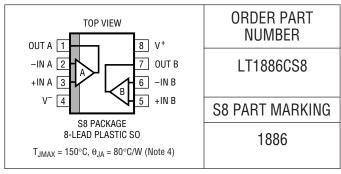

## PACKAGE/ORDER INFORMATION

Consult factory for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 6V$ , $V_{CM} = 0V$ , pulse power tested unless otherwise noted. (Note 9)

| SYMBOL           | PARAMETER                                                           | CONDITIONS                               |   | MIN          | TYP         | MAX        | UNITS        |

|------------------|---------------------------------------------------------------------|------------------------------------------|---|--------------|-------------|------------|--------------|

| V <sub>OS</sub>  | Input Offset Voltage                                                | (Note 5)                                 |   |              | 1           | 4          | mV           |

|                  | 1 10% 11/11 5 %                                                     | (N. 1. 2)                                | • |              |             | 5          | mV           |

|                  | Input Offset Voltage Drift                                          | (Note 8)                                 | • |              | 3           | 17         | μV/°C        |

| $I_{0S}$         | Input Offset Current                                                |                                          |   |              | 150         | 400<br>600 | nA           |

|                  | Innut Dies Ouwent                                                   |                                          | • |              | 1.5         |            | nA           |

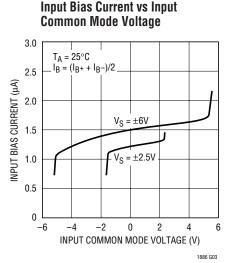

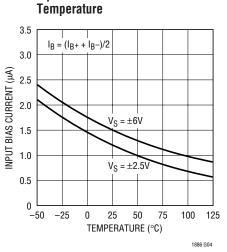

| I <sub>B</sub>   | Input Bias Current                                                  |                                          |   |              | 1.5         | 4<br>6     | μA<br>μA     |

| e <sub>n</sub>   | Input Noise Voltage                                                 | f = 10kHz                                |   |              | 6           |            | nV/√Hz       |

| i <sub>n</sub>   | Input Noise Current                                                 | f = 10kHz                                |   |              | 2           |            | pA/√Hz       |

| R <sub>IN</sub>  | Input Resistance                                                    | V <sub>CM</sub> = ±4.5V<br>Differential  |   | 5            | 10<br>35    |            | MΩ<br>kΩ     |

| C <sub>IN</sub>  | Input Capacitance                                                   |                                          |   |              | 2           |            | pF           |

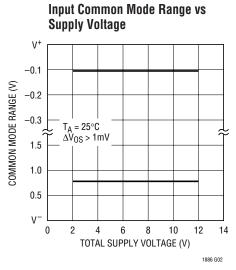

|                  | Input Voltage Range (Positive) Input Voltage Range (Negative)       |                                          | • | 4.5          | 5.9<br>-5.2 | -4.5       | V            |

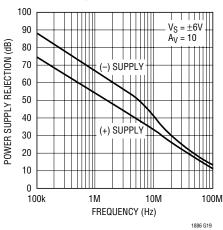

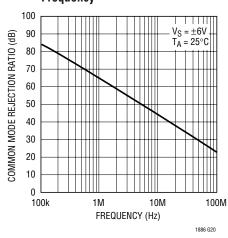

| CMRR             | Common Mode Rejection Ratio                                         | V <sub>CM</sub> = ±4.5V                  | • | 77           | 98          |            | dB           |

|                  | Minimum Supply Voltage                                              | Guaranteed by PSRR                       | • |              |             | ±2         | V            |

| PSRR             | Power Supply Rejection Ratio                                        | $V_S = \pm 2V \text{ to } \pm 6.5V$      | • | 80<br>78     | 86          |            | dB<br>dB     |

| A <sub>VOL</sub> | Large-Signal Voltage Gain                                           | $V_{OUT} = \pm 4V$ , $R_L = 100\Omega$   | • | 5.0<br>4.5   | 12          |            | V/mV<br>V/mV |

|                  |                                                                     | $V_{OUT} = \pm 4V$ , $R_L = 25\Omega$    | • | 4.5<br>4.0   | 12          |            | V/mV<br>V/mV |

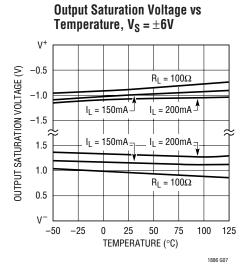

| V <sub>OUT</sub> | Output Swing                                                        | $R_L = 100\Omega$ , 10mV Overdrive       | • | 4.85<br>4.70 | 5           |            | ±V<br>±V     |

|                  |                                                                     | $R_L = 25\Omega$ , 10mV Overdrive        | • | 4.30<br>4.10 | 4.6         |            | ±V<br>±V     |

|                  |                                                                     | I <sub>OUT</sub> = 200mA, 10mV Overdrive | • | 4.30<br>4.10 | 4.5         |            | ±V<br>±V     |

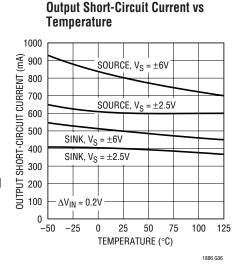

| I <sub>SC</sub>  | Short-Circuit Current (Sourcing)<br>Short-Circuit Current (Sinking) | (Note 3)                                 |   |              | 800<br>500  |            | mA<br>mA     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 6V$ , $V_{CM} = 0V$ , pulse power tested unless otherwise noted. (Note 9)

| SYMBOL           | PARAMETER                  | CONDITIONS                                                                |   | MIN | TYP     | MAX  | UNITS |

|------------------|----------------------------|---------------------------------------------------------------------------|---|-----|---------|------|-------|

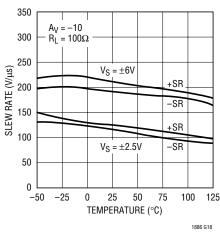

| SR               | Slew Rate                  | $A_V = -10 \text{ (Note 6)}$                                              |   | 133 | 200     |      | V/µs  |

|                  |                            |                                                                           | • | 110 |         |      | V/µs  |

|                  | Full Power Bandwidth       | 4V Peak (Note 7)                                                          |   |     | 8       |      | MHz   |

| GBW              | Gain Bandwidth             | f = 1MHz                                                                  |   |     | 700     |      | MHz   |

| $t_r$ , $t_f$    | Rise Time, Fall Time       | $A_V = 10$ , 10% to 90% of 0.1V, $R_L = 100\Omega$                        |   |     | 4       |      | ns    |

|                  | Overshoot                  | $A_V = 10, 0.1V, R_L = 100\Omega$                                         |   |     | 1       |      | %     |

|                  | Propagation Delay          | $A_V = 10, 50\% V_{IN} \text{ to } 50\% V_{OUT}, 0.1 V, R_L = 100 \Omega$ |   |     | 2.5     |      | ns    |

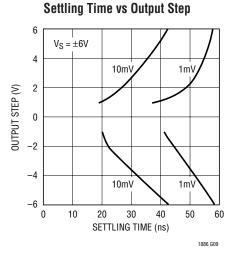

| t <sub>S</sub>   | Settling Time              | 6V Step, 0.1%                                                             |   |     | 50      |      | ns    |

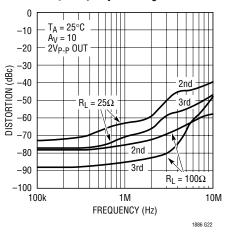

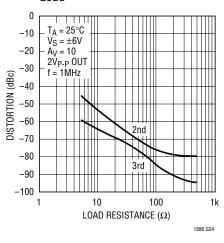

|                  | Harmonic Distortion        | HD2, $A_V = 10$ , $2V_{P-P}$ , $f = 1MHz$ , $R_L = 100\Omega/25\Omega$    |   |     | -75/-63 |      | dBc   |

|                  |                            | HD3, $A_V = 10$ , $2V_{P-P}$ , $f = 1MHz$ , $R_L = 100Ω/25Ω$              |   |     | -85/-71 |      | dBc   |

| IMD              | Intermodulation Distortion | $A_V$ = 10, f = 0.9MHz, 1MHz, 14dBm, $R_L$ = 100 $\Omega$ /25 $\Omega$    |   |     | -81/-80 |      | dBc   |

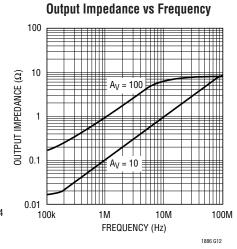

| R <sub>OUT</sub> | Output Resistance          | A <sub>V</sub> = 10, f = 1MHz                                             |   |     | 0.1     |      | Ω     |

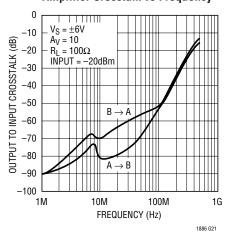

|                  | Channel Separation         | $V_{OUT} = \pm 4V$ , $R_L = 25\Omega$                                     |   | 82  | 92      |      | dB    |

|                  |                            |                                                                           | • | 80  |         |      | dB    |

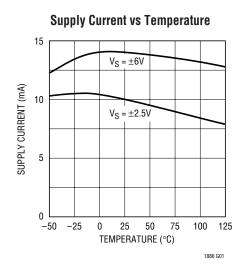

| Is               | Supply Current             | Per Amplifier                                                             |   |     | 7       | 8.25 | mA    |

|                  |                            |                                                                           | • |     |         | 8.50 | mA    |

The ullet denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_S = \pm 2.5 V$ ,  $V_{CM} = 0 V$ , pulse power tested unless otherwise noted. (Note 9)

| SYMBOL           | PARAMETER                                                     | CONDITIONS                               |   | MIN          | TYP         | MAX        | UNITS        |

|------------------|---------------------------------------------------------------|------------------------------------------|---|--------------|-------------|------------|--------------|

| V <sub>OS</sub>  | Input Offset Voltage                                          | (Note 5)                                 | • |              | 1.5         | 5<br>6     | mV<br>mV     |

|                  | Input Offset Voltage Drift                                    | (Note 8)                                 | • |              | 5           | 17         | μV/°C        |

| I <sub>OS</sub>  | Input Offset Current                                          |                                          | • |              | 100         | 350<br>550 | nA<br>nA     |

| I <sub>B</sub>   | Input Bias Current                                            |                                          | • |              | 1.2         | 3.5<br>5.5 | μA<br>μA     |

| e <sub>n</sub>   | Input Noise Voltage                                           | f = 10kHz                                |   |              | 6           |            | nV/√Hz       |

| i <sub>n</sub>   | Input Noise Current                                           | f = 10kHz                                |   |              | 2           |            | pA/√Hz       |

| R <sub>IN</sub>  | Input Resistance                                              | V <sub>CM</sub> = ±1V<br>Differential    |   | 10           | 20<br>50    |            | MΩ<br>kΩ     |

| C <sub>IN</sub>  | Input Capacitance                                             |                                          |   |              | 2           |            | pF           |

|                  | Input Voltage Range (Positive) Input Voltage Range (Negative) |                                          | • | 1            | 2.4<br>-1.7 | -1         | V            |

| CMRR             | Common Mode Rejection Ratio                                   | V <sub>CM</sub> = ±1V                    | • | 75           | 91          |            | dB           |

| A <sub>VOL</sub> | Large-Signal Voltage Gain                                     | $V_{OUT} = \pm 1V$ , $R_L = 100\Omega$   | • | 5.0<br>4.5   | 10          |            | V/mV<br>V/mV |

|                  |                                                               | $V_{OUT} = \pm 1V$ , $R_L = 25\Omega$    | • | 4.5<br>4.0   | 10          |            | V/mV<br>V/mV |

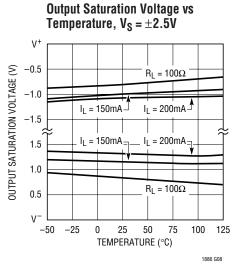

| V <sub>OUT</sub> | Output Swing                                                  | $R_L = 100\Omega$ , 10mV Overdrive       | • | 1.50<br>1.40 | 1.65        |            | ±V<br>±V     |

|                  |                                                               | $R_L = 25\Omega$ , 10mV Overdrive        | • | 1.35<br>1.25 | 1.50        |            | ±V<br>±V     |

|                  |                                                               | I <sub>OUT</sub> = 200mA, 10mV Overdrive | • | 0.87<br>0.80 | 1           |            | ±V<br>±V     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 2.5V$ , $V_{CM} = 0V$ , pulse power tested unless otherwise noted. (Note 9)

| SYMBOL                          | PARAMETER                                                           | CONDITIONS                                                                                                                                         |   | MIN      | TYP                | MAX          | UNITS        |

|---------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|--------------------|--------------|--------------|

| I <sub>SC</sub>                 | Short-Circuit Current (Sourcing)<br>Short-Circuit Current (Sinking) | (Note 3)                                                                                                                                           |   |          | 600<br>400         |              | mA<br>mA     |

| SR                              | Slew Rate                                                           | $A_V = -10$ (Note 6)                                                                                                                               | • | 66<br>60 | 100                |              | V/µs<br>V/µs |

|                                 | Full Power Bandwidth                                                | 1V Peak (Note 7)                                                                                                                                   |   |          | 16                 |              | MHz          |

| GBW                             | Gain Bandwidth                                                      | f = 1MHz                                                                                                                                           |   |          | 530                |              | MHz          |

| t <sub>r</sub> , t <sub>f</sub> | Rise Time, Fall Time                                                | $A_V = 10$ , 10% to 90% of 0.1V, $R_L = 100\Omega$                                                                                                 |   |          | 7                  |              | ns           |

|                                 | Overshoot                                                           | $A_V = 10, 0.1V, R_L = 100\Omega$                                                                                                                  |   |          | 5                  |              | %            |

|                                 | Propagation Delay                                                   | $A_V = 10, 50\% \ V_{IN} \ to \ 50\% \ V_{OUT}, \ 0.1 V, \ R_L = 100 \Omega$                                                                       |   |          | 5                  |              | ns           |

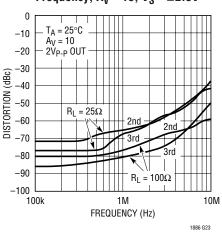

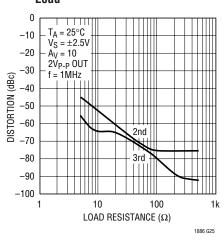

|                                 | Harmonic Distortion                                                 | HD2, $A_V$ = 10, $2V_{P-P}$ , $f$ = 1MHz, $R_L$ = 100 $\Omega/25\Omega$<br>HD3, $A_V$ = 10, $2V_{P-P}$ , $f$ = 1MHz, $R_L$ = 100 $\Omega/25\Omega$ |   |          | -75/-64<br>-80/-66 |              | dBc<br>dBc   |

| IMD                             | Intermodulation Distortion                                          | $A_V = 10$ , $f = 0.9$ MHz, 1MHz, 5dBm, $R_L = 100\Omega/25\Omega$                                                                                 |   |          | -77/-85            |              | dBc          |

| R <sub>OUT</sub>                | Output Resistance                                                   | A <sub>V</sub> = 10, f = 1MHz                                                                                                                      |   |          | 0.2                |              | Ω            |

|                                 | Channel Separation                                                  | $V_{OUT} = \pm 1V$ , $R_L = 25\Omega$                                                                                                              | • | 82<br>80 | 92                 |              | dB<br>dB     |

| I <sub>S</sub>                  | Supply Current                                                      | Per Amplifier                                                                                                                                      | • |          | 5                  | 5.75<br>6.25 | mA<br>mA     |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The inputs are protected by back-to-back diodes. If the differential input voltage exceeds 0.7V, the input current should be limited to less than 10mA.

**Note 3:** A heat sink may be required to keep the junction temperature below absolute maximum.

**Note 4:** Thermal resistance varies depending upon the amount of PC board metal attached to the device.  $\theta_{JA}$  is specified for a 2500mm<sup>2</sup> test board covered with 2 oz copper on both sides.

Note 5: Input offset voltage is exclusive of warm-up drift.

**Note 6:** Slew rate is measured between  $\pm 2V$  on a  $\pm 4V$  output with  $\pm 6V$  supplies, and between  $\pm 1V$  on a  $\pm 1.5V$  output with  $\pm 2.5V$  supplies.

**Note 7:** Full power bandwidth is calculated from the slew rate:  $FPBW = SR/2\pi V_P$ .

Note 8: This parameter is not 100% tested.

**Note 9:** The LT1886C is guaranteed to meet specified performance from 0°C to 70°C. The LT1886C is designed, characterized and expected to meet specified performance from –40°C to 85°C but is not tested or QA sampled at these temperatures. For guaranteed I-grade parts, consult the factory.

**Note 10:** The LT1886C is guaranteed functional over the operating temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

# TYPICAL PERFORMANCE CHARACTERISTICS

LINEAR TECHNOLOGY

**Input Bias Current vs**

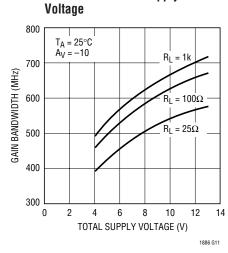

Gain Bandwidth vs Supply

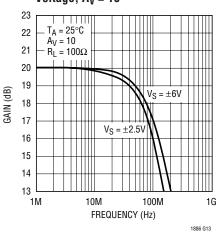

# Frequency Response vs Supply Voltage, $A_V = 10$

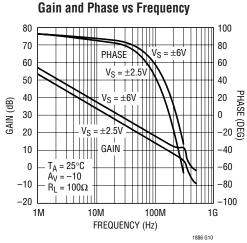

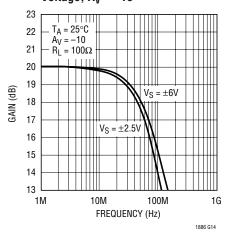

# Frequency Response vs Supply Voltage, $A_V = -10$

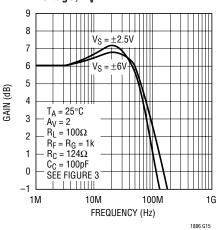

Frequency Response vs Supply Voltage,  $A_V = 2$

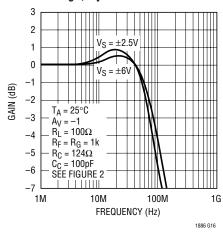

# Frequency Response vs Supply Voltage, $A_V = -1$

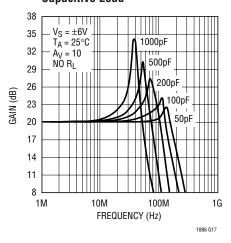

#### Frequency Response vs Capacitive Load

Slew Rate vs Temperature

#### Power Supply Rejection vs Frequency

#### Common Mode Rejection Ratio vs Frequency

#### **Amplifier Crosstalk vs Frequency**

#### Harmonic Distortion vs Frequency, $A_V = 10$ , $V_S = \pm 6V$

#### Harmonic Distortion vs Frequency, $A_V = 10$ , $V_S = \pm 2.5V$

# Harmonic Distortion vs Resistive Load

# Harmonic Distortion vs Resistive Load

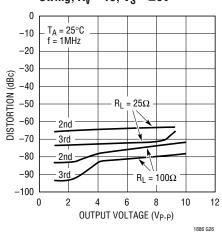

Harmonic Distortion vs Output Swing,  $A_V = 10$ ,  $V_S = \pm 6V$

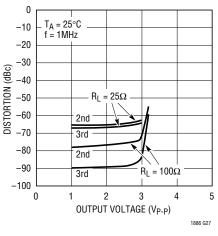

Harmonic Distortion vs Output Swing,  $A_V = 10$ ,  $V_S = \pm 2.5 V$

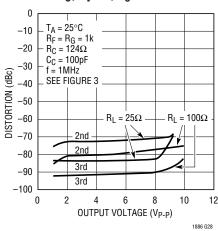

# Harmonic Distortion vs Output Swing, $A_V = 2$ , $V_S = \pm 6V$

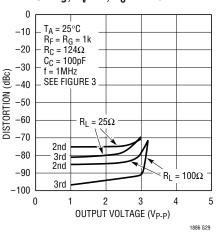

Harmonic Distortion vs Output Swing,  $A_V = 2$ ,  $V_S = \pm 2.5V$

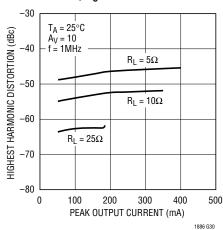

Harmonic Distortion vs Output Current,  $V_S = \pm 6V$

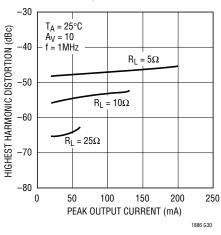

Harmonic Distortion vs Output Current,  $V_S = \pm 2.5V$

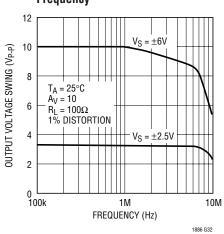

Undistorted Output Swing vs Frequency

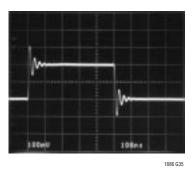

Small-Signal Transient,  $A_V = 10$

Small-Signal Transient,  $A_V = -10$

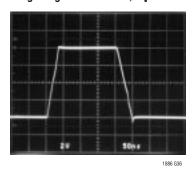

Small-Signal Transient,  $A_V=10$ ,  $C_L=1000 pF$

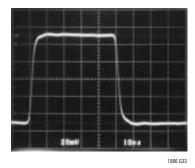

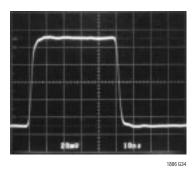

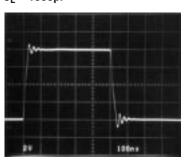

Large-Signal Transient,  $A_V = 10$

Large-Signal Transient,  $A_V = -10$

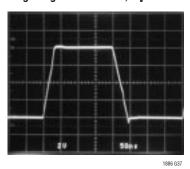

Large-Signal Transient,  $A_V = 10$ ,  $C_L = 1000 pF$

1886 G38

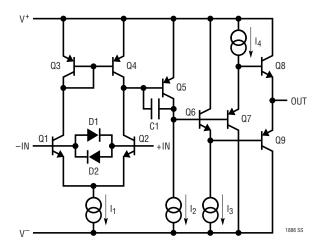

### **Input Considerations**

The inputs of the LT1886 are an NPN differential pair protected by back-to-back diodes (see the Simplified Schematic). There are no series protection resistors onboard which would degrade the input voltage noise. If the inputs can have a voltage difference of more than 0.7V, the input current should be limited to less than 10mA with external resistance (usually the feedback resistor or source resistor). Each input also has two ESD clamp diodes—one to each supply. If an input drive exceeds the supply, limit the current with an external resistor to less than 10mA.

The LT1886 design is a true operational amplifier with high impedance inputs and low input bias currents. The input offset current is a factor of ten lower than the input bias current. To minimize offsets due to input bias currents, match the equivalent DC resistance seen by both inputs. The low input noise current can significantly reduce total noise compared to a current feedback amplifier, especially for higher source resistances.

### **Layout and Passive Components**

With a gain bandwidth product of 700MHz the LT1886 requires attention to detail in order to extract maximum performance. Use a ground plane, short lead lengths and a combination of RF-quality supply bypass capacitors (i.e., 470pF and 0.1 $\mu$ F). As the primary applications have high drive current, use low ESR supply bypass capacitors (1 $\mu$ F to 10 $\mu$ F). For best distortion performance with high drive current a capacitor with the shortest possible trace lengths should be placed between Pins 4 and 8. The optimum location for this capacitor is on the back side of the PC board. The DSL driver demo board (DC304) for this part uses a Taiyo Yuden 10 $\mu$ F ceramic (TMK432BJ106MM).

The parallel combination of the feedback resistor and gain setting resistor on the inverting input can combine with the input capacitance to form a pole which can cause frequency peaking. In general, use feedback resistors of  $1k\Omega$  or less.

#### Thermal Issues

The LT1886 enhanced  $\theta_{JA}$  SO-8 package has the V<sup>-</sup> pin fused to the lead frame. This thermal connection increases

the efficiency of the PC board as a heat sink. The PCB material can be very effective at transmitting heat between the pad area attached to the V<sup>-</sup> pin and a ground or power plane layer. Copper board stiffeners and plated throughholes can also be used to spread the heat generated by the device. Table 1 lists the thermal resistance for several different board sizes and copper areas. All measurements were taken in still air on 3/32" FR-4 board with 2oz copper. This data can be used as a rough guideline in estimating thermal resistance. The thermal resistance for each application will be affected by thermal interactions with other components as well as board size and shape.

Table 1. Fused 8-Lead SO Package

| COPPER                | AREA (2oz)              | TOTAL       |         |

|-----------------------|-------------------------|-------------|---------|

| TOPSIDE               | BACKSIDE                | COPPER AREA | θЈА     |

| 2500 sq. mm           | 2500 sq. mm 5000 sq. mm |             | 80°C/W  |

| 1000 sq. mm           | 2500 sq. mm             | 3500 sq. mm | 92°C/W  |

| 600 sq. mm            | 2500 sq. mm             | 3100 sq. mm | 96°C/W  |

| 180 sq. mm            | 2500 sq. mm             | 2680 sq. mm | 98°C/W  |

| 180 sq. mm            | 1000 sq. mm             | 1180 sq. mm | 112°C/W |

| 180 sq. mm 600 sq. mm |                         | 780 sq. mm  | 116°C/W |

| 180 sq. mm            | 300 sq. mm              | 480 sq. mm  | 118°C/W |

| 180 sq. mm            | 100 sq. mm              | 280 sq. mm  | 120°C/W |

| 180 sq. mm 0 sq. mm   |                         | 180 sq. mm  | 122°C/W |

### **Calculating Junction Temperature**

The junction temperature can be calculated from the equation:

$$T_J = (P_D)(\theta_{JA}) + T_A$$

T<sub>J</sub> = Junction Temperature

T<sub>A</sub> = Ambient Temperature

P<sub>D</sub> = Device Dissipation

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

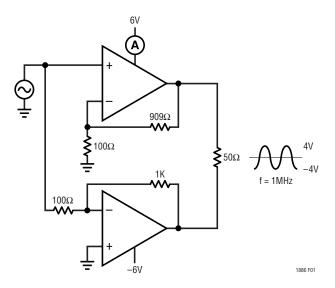

As an example, calculate the junction temperature for the circuit in Figure 1 assuming an 85°C ambient temperature.

The device dissipation can be found by measuring the supply currents, calculating the total dissipation and then subtracting the dissipation in the load.

Figure 1. Thermal Calculation Example

The dissipation for the amplifiers is:

$$P_D = (63.5 \text{mA})(12 \text{V}) - (4 \text{V}/\sqrt{2})^2/(50) = 0.6 \text{W}$$

The total package power dissipation is 0.6W. When a 2500 sq. mm PC board with 2oz copper on top and bottom is used, the thermal resistance is  $80^{\circ}$ C/W. The junction temperature  $T_{\text{J}}$  is:

$$T_{J} = (0.6W)(80^{\circ}C/W) + 85^{\circ}C = 133^{\circ}C$$

The maximum junction temperature for the LT1886 is 150°C so the heat sinking capability of the board is adequate for the application.

If the copper area on the PC board is reduced to 180 sq. mm the thermal resistance increases to 122°C/W and the junction temperature becomes:

$$T_J = (0.6W)(122^{\circ}C/W) + 85^{\circ}C = 158^{\circ}C$$

which is above the maximum junction temperature indicating that the heat sinking capability of the board is inadequate and should be increased.

### **Capacitive Loading**

The LT1886 is stable with a 1000pF capacitive load. The photo of the small-signal response with 1000pF load in a gain of 10 shows 50% overshoot. The photo of the large-signal response with a 1000pF load shows that the output slew rate is not limited by the short-circuit current. The

Typical Performance Curve of Frequency Response vs Capacitive Load shows the peaking for various capacitive loads.

This stability is useful in the case of directly driving a coaxial cable or twisted pair that is inadvertently unterminated. For best pulse fidelity, however, a termination resistor of value equal to the characteristic impedance of the cable or twisted pair (i.e.,  $50\Omega/75\Omega/100\Omega/135\Omega$ ) should be placed in series with the output. The other end of the cable or twisted pair should be terminated with the same value resistor to ground.

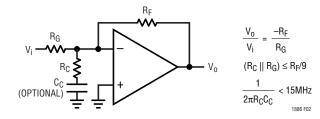

### **Compensation**

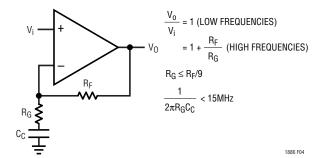

The LT1886 is stable in a gain 10 or higher for any supply and resistive load. It is easily compensated for lower gains with a single resistor or a resistor plus a capacitor. Figure 2 shows that for inverting gains, a resistor from the inverting node to AC ground guarantees stability if the parallel combination of  $R_{C}$  and  $R_{G}$  is less than or equal to  $R_{F}/9$ . For lowest distortion and DC output offset, a series capacitor,  $C_{C}$ , can be used to reduce the noise gain at lower frequencies. The break frequency produced by  $R_{C}$  and  $C_{C}$  should be less than 15MHz to minimize peaking. The Typical Curve of Frequency Response vs Supply Voltage,  $A_{V} = -1$  shows less than 1dB of peaking for a break frequency of 12.8MHz.

Figure 2. Compensation for Inverting Gains

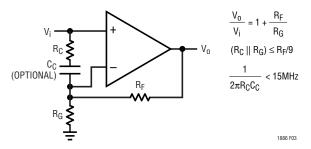

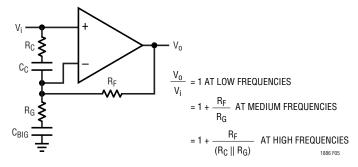

Figure 3 shows compensation in the noninverting configuration. The  $R_C$ ,  $C_C$  network acts similarly to the inverting case. The input impedance is not reduced because the network is bootstrapped. This network can also be placed between the inverting input and an AC ground.

Another compensation scheme for noninverting circuits is shown in Figure 4. The circuit is unity gain at low frequency and a gain of  $1 + R_F/R_G$  at high frequency. The DC output offset is reduced by a factor of ten. The techniques of

Figures 3 and 4 can be combined as shown in Figure 5. The gain is unity at low frequencies,  $1 + R_F/R_G$  at mid-band and for stability, a gain of 10 or greater at high frequencies.

Figure 3. Compensation for Noninverting Gains

Figure 4. Alternate Noninverting Compensation

Figure 5. Combination Compensation

### **Output Loading**

The LT1886 output stage is very wide bandwidth and able to source and sink large currents. Reactive loading, even isolated with a back-termination resistor, can cause ringing at frequencies of hundreds of MHz. For this reason, any design should be evaluated over a wide range of output conditions. To reduce the effects of reactive loading, an optional snubber network consisting of a series RC across the load can provide a resistive load at high frequency. Another option is to filter the drive to the load. If a back-

termination resistor is used, a capacitor to ground at the load can eliminate ringing.

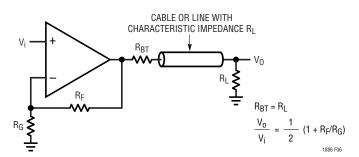

#### **Line Driving Back-Termination**

The standard method of cable or line back-termination is shown in Figure 6. The cable/line is terminated in its characteristic impedance ( $50\Omega$ ,  $75\Omega$ ,  $100\Omega$ ,  $135\Omega$ , etc.). A back-termination resistor also equal to to the chararacteristic impedance should be used for maximum pulse fidelity of outgoing signals, and to terminate the line for incoming signals in a full-duplex application. There are three main drawbacks to this approach. First, the power dissipated in the load and back-termination resistors is equal so half of the power delivered by the amplifier is wasted in the termination resistor. Second, the signal is halved so the gain of the amplifer must be doubled to have the same overall gain to the load. The increase in gain increases noise and decreases bandwidth (which can also increase distortion). Third, the output swing of the amplifier is doubled which can limit the power it can deliver to the load for a given power supply voltage.

Figure 6. Standard Cable/Line Back-Termination

An alternate method of back-termination is shown in Figure 7. Positive feedback increases the effective back-termination resistance so  $R_{BT}$  can be reduced by a factor of n. To analyze this circuit, first ground the input. As  $R_{BT} = R_L/n$ , and assuming  $R_{P2} >> R_L$  we require that:

$V_a = V_0 (1 - 1/n)$  to increase the effective value of  $R_{BT}$  by n.

$$V_D = V_O (1 - 1/n)/(1 + R_F/R_G)$$

$$V_0 = V_p (1 + R_{P2}/R_{P1})$$

Eliminating Vp, we get the following:

$$(1 + R_{P2}/R_{P1}) = (1 + R_F/R_G)/(1 - 1/n)$$

For example, reducing  $R_{BT}$  by a factor of n = 4, and with an amplifer gain of  $(1 + R_F/R_G) = 10$  requires that  $R_{P2}/R_{P1} = 12.3$ .

Note that the overall gain is increased:

$$\frac{V_0}{V_i} = \frac{R_{P2} / (R_{P2} + R_{P1})}{\left[ \left( 1 + 1/n \right) / \left( 1 + R_F / R_G \right) \right] - \left[ R_{P1} / \left( R_{P2} + R_{P1} \right) \right]}$$

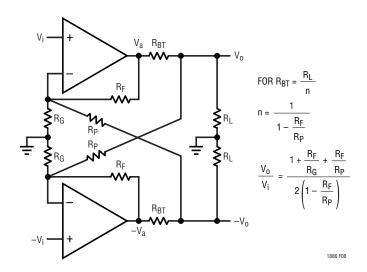

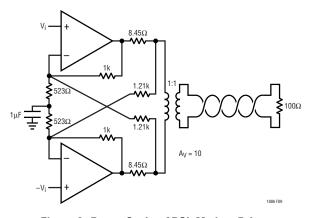

A simpler method of using positive feedback to reduce the back-termination is shown in Figure 8. In this case, the drivers are driven differentially and provide complementary outputs. Grounding the inputs, we see there is inverting gain of  $-R_F/R_P$  from  $-V_0$  to  $V_a$

$$V_a = V_0 (R_F/R_P)$$

and assuming R<sub>P</sub> >> R<sub>L</sub>, we require

$$V_a = V_0 (1 - 1/n)$$

solving

$$R_F/R_P = 1 - 1/n$$

So to reduce the back-termination by a factor of 3 choose  $R_F/R_P = 2/3$ . Note that the overall gain is increased to:

$$V_0/V_i = (1 + R_F/R_G + R_F/R_P)/[2(1 - R_F/R_P)]$$

### **ADSL Driver Requirements**

The LT1886 is an ideal choice for ADSL upstream (CPE) modems. The key advantages are: ±200mA output drive

$V_{i} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_{i} \\ R_{i} \\ R_{i} \\ R_{i} \end{bmatrix} = \begin{bmatrix} R_$

Figure 7. Back-Termination Using Positive Feedback

with only 1.7V worst-case total supply voltage headroom, high bandwidth, which helps achieve low distortion, low quiescent supply current of 7mA per amplifier and a space-saving, thermally enhanced SO-8 package.

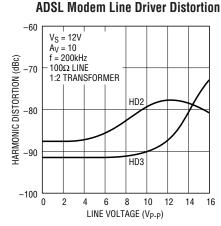

An ADSL remote terminal driver must deliver an average power of 13dBm (20mW) into a  $100\Omega$  line. This corresponds to  $1.41V_{RMS}$  into the line. The DMT-ADSL peak-to-average ratio of 5.33 implies voltage peaks of 7.53V into the line. Using a differential drive configuration and transformer coupling with standard back-termination, a transformer ratio of 1:2 is well suited. This is shown on the front page of this data sheet along with the distortion performance vs line voltage at 200kHz, which is beyond ADSL requirements. Note that the distortion is better than -73dBc for all swings up to  $16V_{P-P}$  into the line. The gain of this circuit from the differential inputs to the line voltage is 10. Lower gains are easy to implement using the compensation techniques of Figure 5. Table 2 shows the drive requirements for this standard circuit.

The above design is an excellent choice for desktop applications and draws typically 550mW of power. For portable applications, power savings can be achieved by reducing the back-termination resistor using positive feedback as shown in Figure 9. The overall gain of this circuit is also 10, but the power consumption has been reduced to 350mW, a savings of 36% over the previous design. Note that the reduction of the back-termination resistor has allowed use of a 1:1 transformer ratio.

Figure 8. Back-Termination Using Differential Positive Feedback

Table 2. ADSL Upstream Driver Designs

|                                 | STANDARD              | LOW POWER            |

|---------------------------------|-----------------------|----------------------|

| Line Impedance                  | 100Ω                  | 100Ω                 |

| Line Power                      | 13dBm                 | 13dBm                |

| Peak-to-Average Ratio           | 5.33                  | 5.33                 |

| Transformer Turns Ratio         | 2                     | 1                    |

| Reflected Impedance             | 25Ω                   | 100Ω                 |

| Back-Termination Resistors      | 12.5Ω                 | 8.35Ω                |

| Transformer Insertion Loss      | 1dB                   | 0.5dB                |

| Average Amplifier Swing         | 0.79V <sub>RMS</sub>  | 0.87V <sub>RMS</sub> |

| Average Amplifier Current       | 31.7mA <sub>RMS</sub> | 15mA <sub>RMS</sub>  |

| Peak Amplifier Swing            | 4.21V Peak            | 4.65V Peak           |

| Peak Amplifier Current          | 169mA Peak            | 80mA Peak            |

| Total Average Power Consumption | 550mW                 | 350mW                |

| Supply Voltage                  | Single 12V            | Single 12V           |

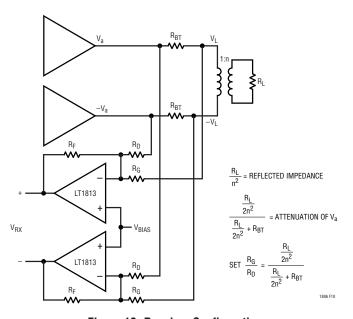

Table 2 compares the two approaches. It may seem that the low power design is a clear choice, but there are further system issues to consider. In addition to driving the line, the amplifiers provide back-termination for signals that are received simultaneously from the line. In order to reject the drive signal, a receiver circuit is used such as shown in Figure 10. Taking advantage of the differential nature of the signals, the receiver can subtract out the drive signal and amplify the received signal. This method works well for standard back-termination. If the back-termination resistors are reduced by positive feedback, a portion of the received signal also appears at the amplifier outputs. The result is that the received signal is attenuated

Figure 9. Power Saving ADSL Modem Driver

by the same amount as the reduction in the back-termination resistor. Taking into account the different transformer turns ratios, the received signal of the low power design will be one third of the standard design received signal. The reduced signal has system implications for the sensitivity of the receiver. The power reduction may, or may not, be an acceptable system tradeoff for a given design.

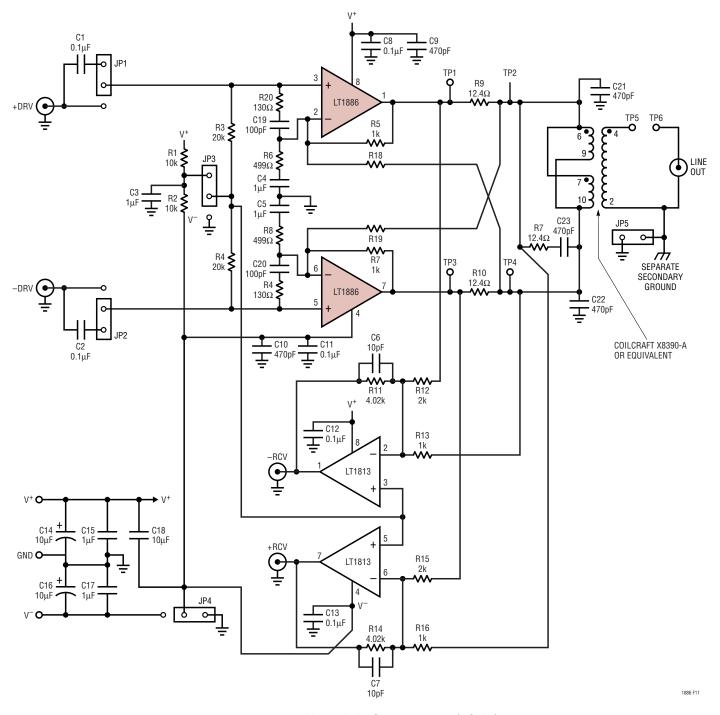

### **Demo Board**

Demo board DC304 has been created to provide a versatile platform for a line driver/receiver design. (Figure 11 shows a complete schematic.) The board is set up for either single or dual supply designs with Jumpers 1–4. The LT1886 is set up for differential, noninverting gain of 3. Each amp is configured as in Figure 5 for maximum flexibility. The amplifiers drive a 1:2 transformer through back-termination resistors that can be reduced with optional positive feedback. The secondary of the transformer can be isolated from the primary with Jumper 5.

A differential receiver is included using the LT1813, a dual 100MHz,  $750V/\mu s$  operational amplifier. The receiver gain from the transformer secondary is 2, and the drive signals are rejected by approximately a factor of 14dB. Other optional components include filter capacitors and an RC snubber network at the transformer primary.

Figure 10. Receiver Configuration

Figure 11. LT1886, LT1813 DSL Demo Board (DC304)

# SIMPLIFIED SCHEMATIC

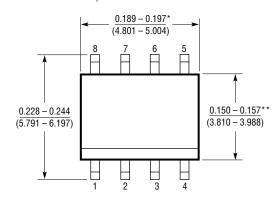

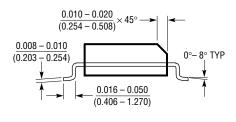

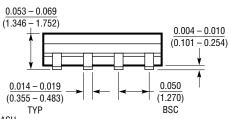

# PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

\*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

\*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

S08 1298

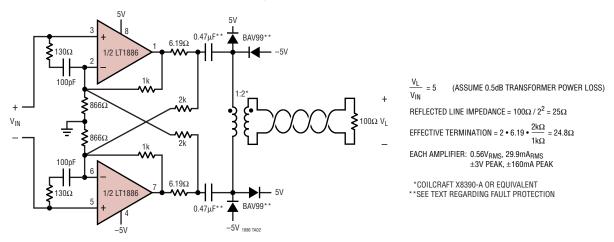

# TYPICAL APPLICATION

#### **Considerations for Fault Protection**

The basic line driver design presents a direct DC path between the outputs of the two amplifiers. An imbalance in the DC biasing potentials at the noninverting inputs through either a fault condition or during turn-on of the system can create a DC voltage differential between the two amplifier outputs. This condition can force a considerable amount of current, 500mA or more, to flow as it is limited only by the small valued back-termination resistors and the DC resistance of the transformer primary. This high current can possibly cause the power supply voltage source to drop significantly impacting overall system performance. If left unchecked, the high DC current can heat the LT1886 to destruction.

Using DC blocking capacitors to AC couple the signal to the transformer eliminates the possibility for DC current to flow under any conditions. These capacitors should be sized large enough to not impair the frequency response characteristics required for the data transmission.

Another important fault related concern has to do with very fast high voltage transients appearing on the telephone line (lightning strikes for example). TransZorbs<sup>™</sup>, varistors and other transient protection devices are often used to absorb the transient energy, but in doing so also create fast voltage transitions themselves that can be coupled through the transformer to the outputs of the line driver. Several hundred volt transient signals can appear at the primary windings of the transformer with current into the driver outputs limited only by the back termination resistors. While the LT1886 has clamps to the supply rails at the output pins, they may not be large enough to handle the significant transient energy. External clamping diodes, such as BAV99s, at each end of the transformer primary help to shunt this destructive transient energy away from the amplifier outputs.

TransZorb is a registered trademark of General Instruments, GSI

### Split Supply ±5V ADSL CPE Line Driver

# RELATED PARTS

| PART NUMBER                                         | DESCRIPTION                                     | COMMENTS                                                             |  |  |

|-----------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|--|--|

| LT1207 Dual 250mA, 60MHz Current Feedback Amplifier |                                                 | Shutdown/Current Set Function                                        |  |  |

| LT1361 Dual 50MHz, 800V/µs Op Amp                   |                                                 | $\pm 15$ V Operation, 1mV V <sub>OS</sub> , 1 $\mu$ A I <sub>B</sub> |  |  |

| LT1396                                              | Dual 400MHz, 800V/µs Current Feedback Amplifier | 4.6mA Supply Current Set, 80mA I <sub>OUT</sub>                      |  |  |

| LT1497                                              | Dual 125mA, 50MHz Current Feedback Amplifier    | 900V/μs Slew Rate                                                    |  |  |

| LT1795                                              | Dual 500mA, 50MHz Current Feedback Amplifier    | Shutdown/Current Set Function, ADSL CO Driver                        |  |  |

| LT1813                                              | Dual 100MHz, 750V/μs, 8nV/√Hz Op Amp            | Low Noise, Low Power Differential Receiver                           |  |  |