# *OXUF922 DATA SHEET*

### **FEATURES**

- 1394B Phy Interface and Link

- Backward compatible with 1394A

- 800Mb/s Support

- SBP2 Bus Mastering

- USB2.0 Phy and Link Layer

- Backward Compatible with USB1.1

- 480Mb/s Support

- Bulk Transfer USB Slave receiver

- 100MHz IDE interface

- Full support for AT A6 Drives

- LBA support for large drives

- Full Master and Slave support

- Supports Data Rates up to 80MBytes/s

- Simple DMA master scheme

- ORB accelerator

- Groups orbs and provides high speed response for hard coded commands

- High-Performance, Low Power ARM7TDMI Processor

- 50MHz Clock Rate

- 32Bit

- 8KByte Closely Coupled RAM

- 12Mb/s Async UART

- Extended 128Byte Buffer

- Local Bus Support

- Generic bus support for external peripherals

- 8 GPIO pins

- Programmable IO

- 6KByte Cache for USB or 1394 data

- 0.18µm advanced CMOS process

- 160 LQFP or 176 VFBGA

- I/O Supply Voltage 3.3V +/- 0.3V

- Core Supply Voltage 1.8V +/- 0.15V

### **DESCRIPTION**

The OXUF922 is a combined USB2.0 and 1394B bridge to any IDE device or DMA based SRAM architecture. Optimised for performance the OXUF922 has a flexible ARM7 embedded processor, which can be programmed for next generation Computer Peripheral and Consumer Applications.

- 1394B and USB2.0 PC and Apple Storage Devices for HDD, DVD, CD, CF and Tape or Dual LUN Combinations of the above.

- Consumer Appliance (STB, PVR) Storage solutions for HDD and DVD.

- Digital Camera Companions

- Digital Camcorder Storage Devices

- Advanced Compressed Audio Players (MP3)

- Printers and Scanners

- 1394B Raid Array with UART Back-channel monitor support.

The embedded ARM7TDMI processor enables a new set of innovative products to be supported through custom firmware development. Program code can be programmed 'In-System' through the 1394 port simplifying manufacture. The 1394 Link supports A, B or Beta Phys and is fully backward compatible with earlier 1394 standards. The Link interface supports data rates up to S800 (800Mb/s) and has a rich complement of 1394 second layer functionality.

The OXUF922 fully supports 1394 Peer-To-Peer operation enabling PC-less communication over the 1394 Bus for file copying or manipulation. In addition the OXUF922 is backward compatible with the Oxford FW900 and FW911 enabling a limited Peer-To-Peer operation by SBP2 mastering the 1394 bus.

The OXUF922 has an ORB data accelerator which, without processor intervention, significantly increases the performance of the bridge device when transferring many small files.

.

Oxford Semiconductor Ltd. 25 Milton Park, Abingdon, Oxon, OX14 4SH, UK Tel: +44 (0)1235 824900 Ó Oxford Semiconductor 2002 . Template: DS\_C018A . DATA SHEET. CONFIDENTIAL.

# **CONTENTS**

| 1                   | OXUF922 DESCRIPTION                                  |    |

|---------------------|------------------------------------------------------|----|

| 1.1<br>2            | BLOCK DIAGRAMPIN INFORMATION                         |    |

|                     |                                                      |    |

| 3                   | PIN DESCRIPTIONS                                     |    |

| 3.1                 | USB PIN CONFIGURATION REQUIREMENT                    |    |

| 3.2                 | POWER ON / RESET SEQUENCE                            |    |

| 3.2.1<br><b>3.3</b> | LOCKUP HAZARDFUNCTIONAL MODES                        |    |

| 3.4                 | EXTERNAL DEVICES REQUIRED                            |    |

|                     | MEMORY ORGANISATION                                  |    |

| 4<br>4.1            | MEMORY ORGANISATION                                  |    |

| 4.1<br>4.2          | REGISTER SET AND BASE ADDRESSES OF HARDW ARE DEVICES |    |

|                     | CPU FUNCTIONS                                        |    |

| 5                   |                                                      |    |

| 5.1                 | CLOCK BLOCK                                          |    |

| 5.1.1               |                                                      |    |

| 5.1.2<br>5.1.3      |                                                      |    |

| 5.1.4               |                                                      |    |

| 5.1.5               |                                                      |    |

| 5.1.3<br>5.2        | STATIC RAM CONTROLLER                                |    |

| 5.2.1               |                                                      |    |

| 5.2.2               |                                                      |    |

| 5.2.3               |                                                      |    |

| 5.2.4               | GENERAL ADDRESS DECODING                             | 23 |

| 5.2.5               | ADDITIONAL FUNCTIONS                                 | 23 |

| 5.3                 | RPS BLOCK                                            |    |

| 5.3.1               |                                                      |    |

| 5.4                 | ARM RPS REGISTER SET SUMMARY                         |    |

| 5.5                 | INTERRUPT OPERATION                                  |    |

| 5.5.1               |                                                      |    |

| 5.6                 | WATCHDOG TIMER                                       |    |

| 5.6.1               |                                                      |    |

| 5.6.2<br><b>5.7</b> | WDT PERIOD                                           |    |

| 5.7.1               |                                                      |    |

| 5.7.1               |                                                      |    |

| 5.7.Z               | GPIO BLOCK                                           |    |

| 5.8.1               |                                                      |    |

| 5.8.2               |                                                      |    |

| 5.8.3               |                                                      | 29 |

| 5.8.4               |                                                      |    |

| 5.8.5               |                                                      | 30 |

| 5.8.6               | GPIO PIN MULTIPLEXING                                | 30 |

| 5.9                 | RESET CONTROL                                        | 31 |

| 5.9.1               |                                                      |    |

| 5.9.2               | BLOCK RESET MAPPING - LOCATION 0A000340              | 31 |

| 6                   | UART                                                 | 32 |

| 7                   | INTERFACE & PERIPHERAL FUNCTIONS                     | 34 |

|                     | - · · · · · · · · · · · · · · · · · · ·              |    |

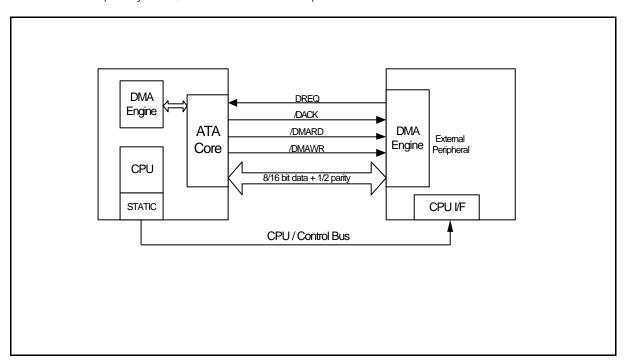

| 7.1          | DMA ENGINE                                                 | 34 |

|--------------|------------------------------------------------------------|----|

| 7.1<br>7.2   | ATA BLOCK                                                  |    |

| 7.3          | ATA BYPASS                                                 |    |

| 7.3.1        | PIN MAPPING                                                |    |

| 7.3.2        | OPERATION                                                  |    |

| 7.3.3        | BYPASS CONFIGURATION                                       |    |

| 7.3.4        | BYPASS CONTROL / STATUS                                    |    |

| 7.3.5        | CONFIGURATION PARAMETERS                                   |    |

| 7.3.6        | TIMING PARAMETERS                                          |    |

| 7.3.7        | BYPASS LIMITATIONS                                         |    |

| 7.3.8        | BYPASS MODE IN A STREAMING IMPLEMENTATION                  |    |

| 7.4          | LINK-CORE                                                  |    |

| 7.4.1        | REGISTER SET                                               |    |

| 7.5          | FIFO MANAGER.                                              | 47 |

| 7.5.1        | DATA PLANE                                                 |    |

| 7.5.2        | CONTEXT RAM                                                | 47 |

| 7.5.3        | AHB SLAVE UNITS AND APBINTERFACE                           |    |

| 7.5.4        | REGISTER SET                                               |    |

| 7.6          | ORB CO-PROCESSOR.                                          |    |

| 7.7          | QUEUE SELECTOR                                             |    |

| 7.8          | ASYNC ENGINE                                               | 51 |

| 7.9          | USB2 CORE                                                  | 52 |

| 7.10         | SERIAL CONTROLLER                                          | 53 |

| 7.10.1       | SERIAL ADDRESS AND CONTROL REGISTER - LOCATION 0X0AA00000  | 53 |

| 7.10.2       | SERIAL READ DATA REGISTER - LOCATION 0X0AA00004            | 54 |

| 7.10.3       | SERIAL SOFTWARE CONTROL OUT REGISTER - LOCATION 0X0AA00008 | 54 |

| 7.10.4       | SERIAL CONTROL SOFTWARE IN REGISTER - LOCATION 0X0AA0000C  | 54 |

| 7.11         | SERIAL AUDIO                                               | 55 |

| 7.11.1       | REGISTER SET                                               | 56 |

| 7.11.2       | FEATURE LIST                                               | 57 |

| 7.11.3       | LIMITATIONS                                                | 57 |

| о г          | ODOF FLACILV 1.1                                           | EO |

|              | ORCE FLASH V 1.1                                           |    |

| 9 C          | DPERATING CONDITIONS                                       | 60 |

| 10           | DC ELECTRICAL CHARACTERISTICS                              | 61 |

|              |                                                            |    |

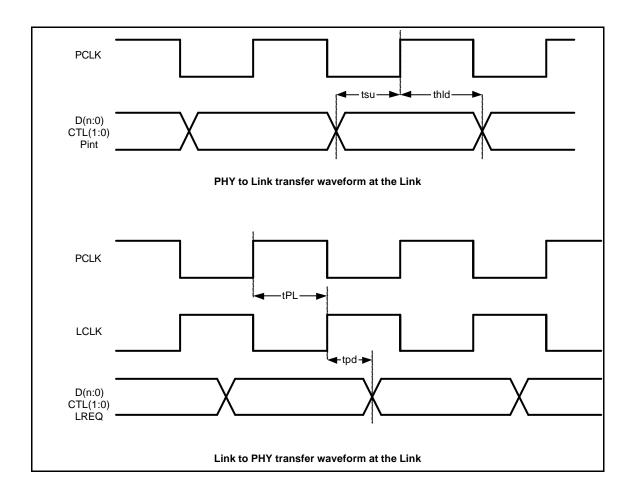

| 11           | PHY-LINK INTERFACE TIMING DIAGRAMS                         |    |

| 11.1         | A MODE                                                     |    |

| 11.2         | B MODE                                                     | 63 |

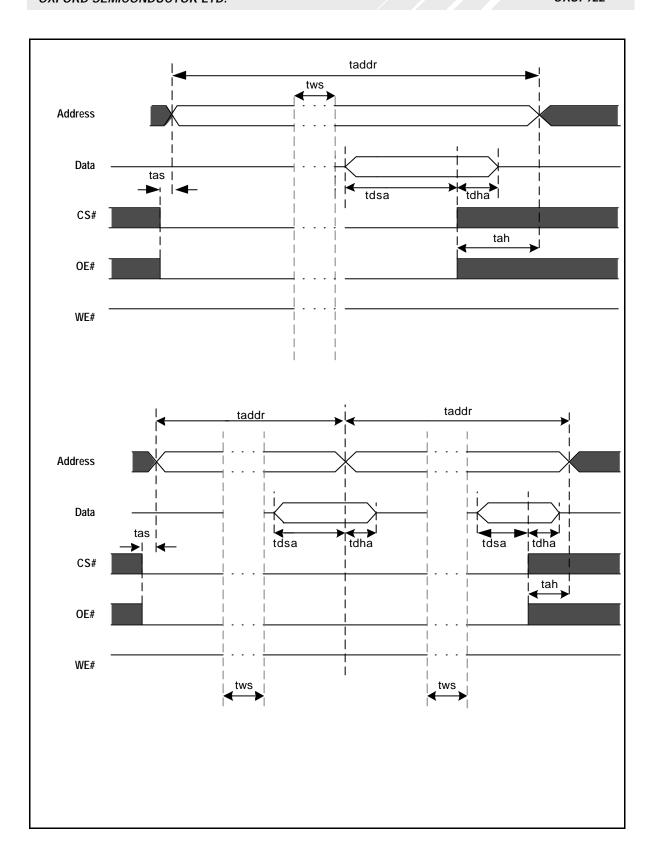

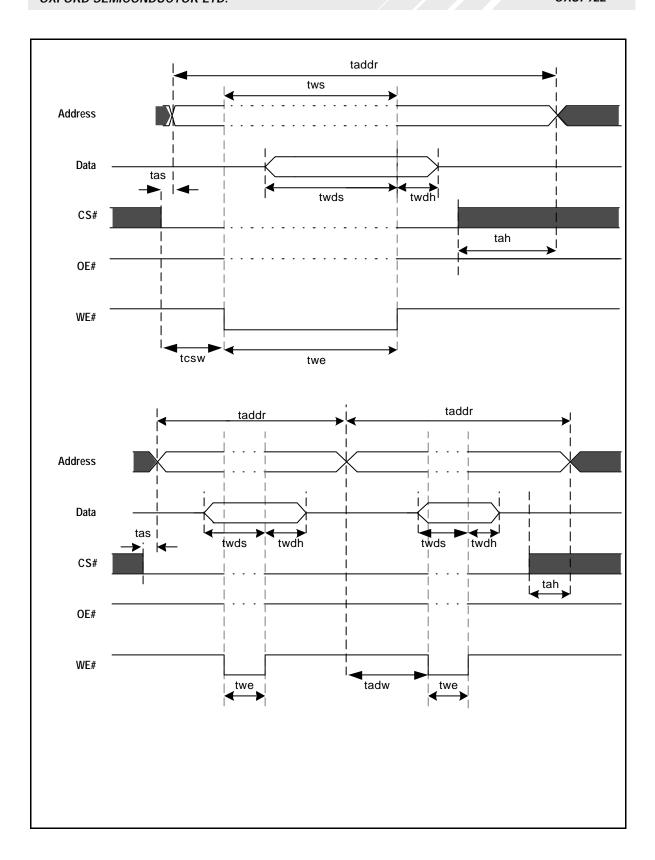

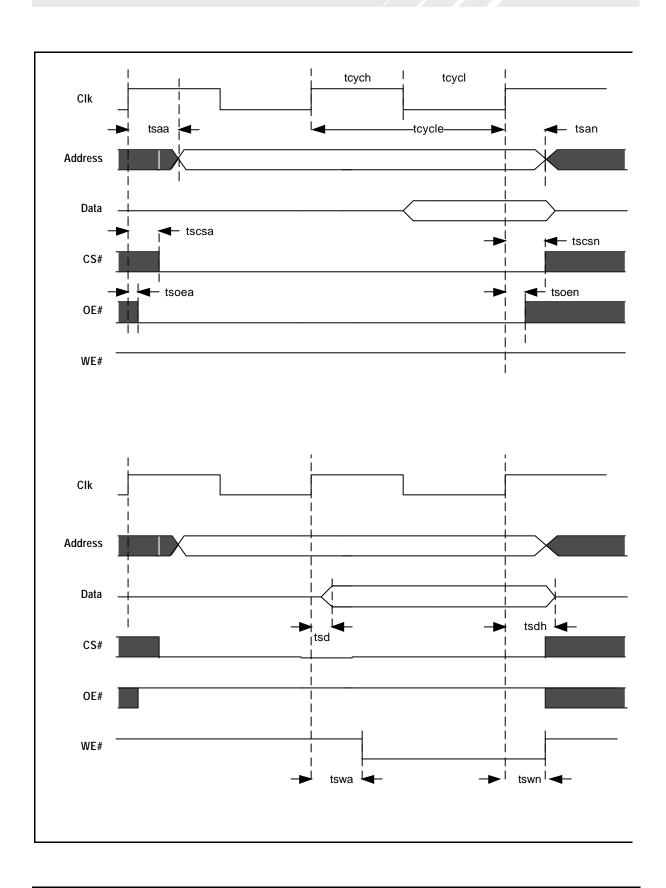

| 12           | EXTERNAL BUS TIMING DIAGRAMS                               | 64 |

| 13           | POWER CONSUMPTION                                          | 68 |

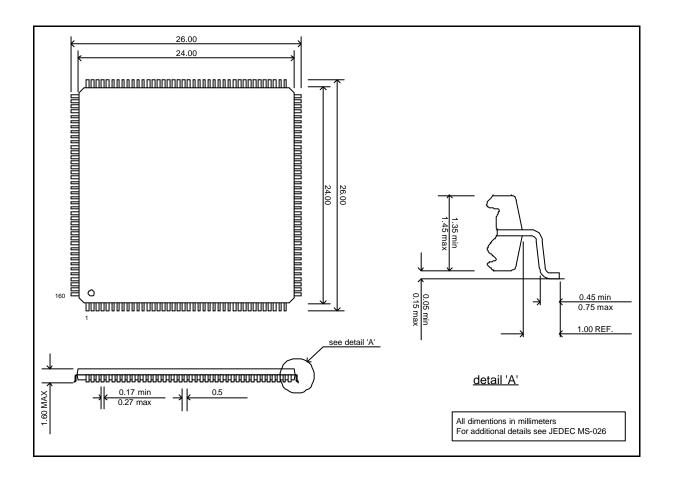

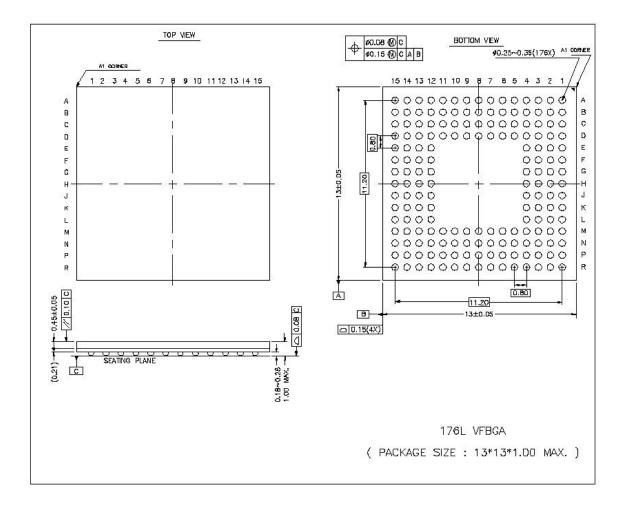

| 14           | PACKAGE INFORMATION                                        | 60 |

| 14.1         | 160 LQFP PACKAGE                                           |    |

| 14.1<br>14.2 | 176 BGA PACKAGE                                            |    |

|              |                                                            |    |

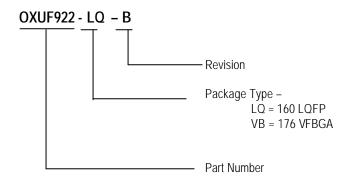

| 15           | ORDERING INFORMATION                                       | 71 |

# **REVISION HISTORY**

| REV  | DATE     | REASON FOR CHANGE / SUMMARY OF CHANGE                                                                         |

|------|----------|---------------------------------------------------------------------------------------------------------------|

| 0.4  | 15/4/02  | Output pin drive strengths added. Package drawing clarified                                                   |

| 0.5  | 29/4/02  | active polarity of pin 41 (FFLASH) changed                                                                    |

| 0.6  | 23/7/02  | added reset / PLL en info                                                                                     |

| 0.7  | 29/7/02  | Added VFBGA info. 1394 Phy Link timings updated. Revision updated                                             |

| 0.8  | 19/9/02  | Added clarification to PLL_TEST and PLL_EN pins. Front page updated                                           |

| 0.9  | 6/11/02  | Added block descriptions and register details                                                                 |

| 0.10 | 11/11/02 | General formatting changes, addition of CPU related functions and registers                                   |

| 0.11 | 18/11/02 | Added Static Interface details and timing                                                                     |

|      |          | Added ATA bypass details                                                                                      |

| 0.12 | 19/11/02 | Final review. Missing references fixed. GPIO tables fixed                                                     |

| 1.0  | 20/11/02 | First Release                                                                                                 |

| 1.1  | 06/12/02 | Add more detail into sections 7.4 Link-Core, 7.5 FIFO Manager., 7.10 Serial Controller and 7.11 Serial Audio. |

# 1 OXUF922 DESCRIPTION

#### Description

The OXUF922 is a combined USB2.0 and 1394 bridge to IDE device. The 1394 Link supports A or B PHYs and is fully backward compatible with earlier 1394 standards. The OXUF922 also includes an on-chip USB2.0 PHY allowing up to 480Mb/s data transfer.

The 1394 Link interface supports data rates up to S800 (800Mb/s) and has a rich complement of 1394 second layer functionality. The OXUF922 fully supports 1394 Peer-To-Peer operation enabling PC-less communication over the 1394 Bus for file copying or manipulation. The chip has an ORB data accelerator which, without processor intervention, significantly increases the performance of the bridge device when transferring many small files, and frees the processor for other tasks.

The OXUF922 integrates an ARM7TDMI operating at 50 MHz with a closely coupled zero wait state 2Kx32 SRAM provided for local program, stack or data storage. The closely coupled ram supports byte, word and quadlet access. The embedded ARM7TDMI processor enables a new set of innovative products to be supported through custom firmware development. Program code can be programmed 'In-System' through the 1394 port simplifying manufacture.

By combining the ARM7TDMI processor core with on-chip SRAM and a wide range of perpheral functions including timers, serial communication controllers and Oxford Semiconductor extensive knowledge of 1394 and USB applications the OXUF922 provides a highly flexible and costeffective solution to many compute-intensive applications requiring connectivity and storage on top of normal micro-controller features.

### **Development Support**

The OXUF922 is be supported by an open source 'C' compiler (GCC) coupled with a free UNIX environment (Cygwin) to enable the compiling and debugging of the software. Free Uploader software allows quick and easy method of uploading software to the device in-circuit.

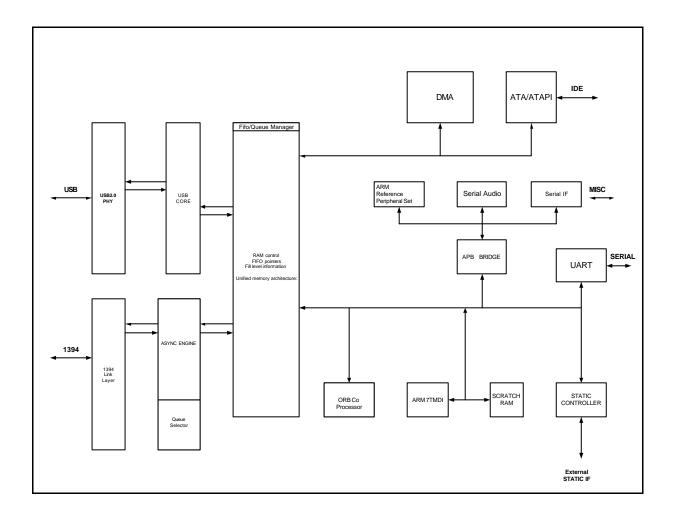

# 1.1 Block Diagram

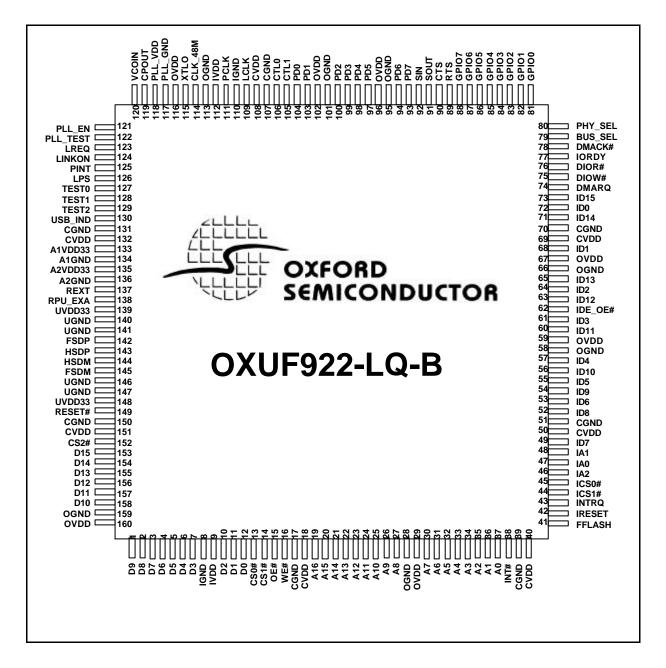

## 2 PIN INFORMATION

Figure 1 - LQFP Pin Information

|   | 1                 | 2                | 3               | 4                | 5              | 6      | 7        | 8            | 9            | 10      | 11              | 12            | 13             | 14               | 15              |

|---|-------------------|------------------|-----------------|------------------|----------------|--------|----------|--------------|--------------|---------|-----------------|---------------|----------------|------------------|-----------------|

|   |                   |                  |                 |                  |                |        |          |              |              |         |                 |               |                |                  |                 |

| Α | GND:              | STATIC_<br>D11   | STATIC_<br>D13  | STATIC_<br>Z_CS2 | Z_RESE<br>T    | FSDM   |          | UGND:        | REXT         | A1GND:  | GND:            | TESTPIN<br>1  | PINT           | LREQ             | CPOUT           |

| В | STATIC_<br>D7     | VDD:             | STATIC_<br>D10  | STATIC_<br>D12   | STATIC_<br>D14 | GND:   | UGND:    |              | UGND:        | A2GND:  | VDD:            | TESTPIN<br>0  | LINK_O<br>N    |                  | VDD:            |

| С | STATIC_<br>D6     | STATIC_<br>D8    |                 |                  | STATIC_<br>D15 | UVDD:  | HSDM     | HSDP         | UVDD:        | A2VDD:  | USB_IN<br>D     | LPS           | EN             | VCOIN            | XTLO            |

| D | STATIC_<br>D4     | STATIC_<br>D5    | STATIC_<br>D9   |                  | VDD:           | UGND:  |          | FSDP         | RPU_EN<br>A  | A1VDD:  | TESTPIN<br>2    | PLLTES<br>T   |                | GNDP:            | VDD:            |

| E | VDD:              | STATIC_<br>D2    | GND:            | STATIC_<br>D3    |                |        |          |              |              |         |                 | GND:          | CLK_48<br>M    | VDDP:            | LCLK            |

| F | STATIC_<br>Z_CS0  | STATIC_<br>Z_CS1 | STATIC_<br>D0   | STATIC_<br>D1    |                | 0976   |          |              |              |         |                 | VDD:          | IGND:          | PHY_CL<br>K_1394 | CTL0            |

| G | GND:              | VDD:             | STATIC_<br>Z_WE | STATIC_<br>Z_OE  | ŽI<br>Li       |        | <u>-</u> | YEO          | 9 D          |         |                 | PD0           | CTL1           | GND:             | PD1             |

| Н | STATIC_<br>A14    | STATIC_<br>A15   | STATIC_<br>A16  | STATIC_<br>A13   |                | OXFORD |          |              |              |         |                 | PD3           | GND:           | VDD:             | PD2             |

| J | STATIC_<br>A11    | STATIC_<br>A9    | STATIC_<br>A10  | STATIC_<br>A12   |                |        |          |              |              |         |                 | GND:          | VDD:           | PD4              | PD5             |

| K | GND:              | STATIC_<br>A7    | VDD:            | STATIC_<br>A8    | C              | Xί     | JFS      | 922          | ? <b>-</b> V | B-E     | 3               | Z_CTS         | SIN            | PD7              | PD6             |

| L | STATIC_<br>A6     | STATIC_<br>A2    | STATIC_<br>A4   | STATIC_<br>A5    |                |        |          |              |              |         |                 | GPIO_1        | GPIO_6         | Z_RTS            | SOUT            |

| M | STATIC_<br>A3     | STATIC_<br>Z_INT |                 | GND:             |                | GND:   | IDE_D5   | VDD:         | IDE_D12      | VDD:    | IDE_D0          |               | GPIO_2         | GPIO_5           | GPIO_7          |

| N | STATIC_<br>A1     | VDD:             |                 | IDE_Z_C<br>S1    | IDE_A0         | IDE_D8 | IDE_D10  | IDE_D11      | IDE_D2       | VDD:    | IDE_Z_D<br>MACK |               |                | GPIO_0           | GPIO_4          |

| Р | STATIC_<br>A0     |                  | IDE_RES<br>ET   | IDE_A2           | IDE_D7         | IDE_D9 | GND:     | IDE_Z_O<br>E | GND:         | IDE_D14 | IDE_DM<br>ARQ   | IDE_IOR<br>DY | BUS_SE<br>L    |                  | GPIO_3          |

| R | Z_FORC<br>E_FLASH | IDE_INT<br>RQ    | IDE_Z_C<br>S0   | IDE_A1           | VDD:           | IDE_D6 | IDE_D4   | IDE_D3       | IDE_D13      | IDE_D1  | GND:            | IDE_D15       | IDE_Z_D<br>IOW | IDE_Z_D<br>IOR   | A_B_PH<br>Y_SEL |

Figure 2 – VFBGA Pin Information (Top view)

# 3 PIN DESCRIPTIONS

| LQFP Pin             | VFBGA         | #  | Type <sup>1</sup> | Name            | Description                                               |

|----------------------|---------------|----|-------------------|-----------------|-----------------------------------------------------------|

| 1394 LINK            |               |    | J1                |                 |                                                           |

| 93,94,97-100,103,104 | K14,K15,J15,  | 8  | B_4               | PD[7:0]         | Phy-Link Data Bus                                         |

|                      | J14,H12,H15   |    | _                 |                 |                                                           |

|                      | G15,G12       |    |                   |                 |                                                           |

| 105,106              | G13,F15       | 2  | B_4               | CTL[1:0]        | Phy-Link Control Bus                                      |

| 111                  | F14           | 1  | Ī                 | PCLK            | 49.152 (A)/ 98.304 (B) MHz clock sourced by PHY           |

| 123                  | A14           | 1  | 0_4               | LREQ            | Link Request                                              |

| 124                  | B13           | 1  | IU                | LINKON          | Requests link to power up when in a low power             |

|                      |               |    |                   |                 | mode                                                      |

| 126                  | C12           | 1  | 0_4               | LPS             | Indicates to phy that link is powered and ready           |

| 109                  | E15           | 1  | 0_4               | LCLK            | B Only – PCLK returned to PHY                             |

| 125                  | A13           | 1  | Ī                 | PINT            | B Only – PHY Interrupt                                    |

| STATIC IF            | 1             |    |                   | 1               | · · · · · · · · · · · · · · · · ·                         |

| 153-158,1,2          | C5,B5,A3,B4,  | 8  | B_8               | D[15:8]         | Static IF external upper data bus when TEST[2:0] =        |

| 100 100/1/2          | A2,B3,D3,C2   | Ĭ  | 5_0               | <i>D</i> [10.0] | 000 or 010                                                |

| 153-157              | C5,B5,A3,B4,  | 0  | B_8               | TDI,TDO, TMS,   | JTAG Bus when TEST[2:0] =001                              |

| 100 107              | A2            | U  | D_0               | TCK, TRST       | 317/G Bu3 WHOH TE31[2.0] =001                             |

| 158,1,2              | B3,D3,C2      | 0  | 0_8               | A[19:17]        | Extended Static IF external address bus when              |

| 100,172              | 00,00,02      | Ŭ  | 0_0               | 71[7.17]        | TEST[2:0] =001                                            |

| 156-158,1,2          | B4,A2,B3,D3,  | 0  | 0_8               | A[21:17]        | Extended Static IF external address bus when              |

| 130 130,1,2          | C2            | U  | 0_0               | / ([21.17]      | TEST[2:0] =101                                            |

| 3-7,10-12            | B1,C1,D2,D1,  | 8  | T_B_8             | D[7:0]          | Static IF external lower data bus                         |

| 0 1/10 12            | E4,E2,F4,F3   | Ĭ  | 1_5_0             | 5[7.0]          | Station Shornario wor data bas                            |

| 19-27,30-37          | H3,H2,H1,H4,  | 17 | T_O_8             | A[16:0]         | Static IF external address bus                            |

| 17 27 700 07         | J4,J1,J3,J2,K | ., |                   | 7.[10.0]        | Station Stational address 245                             |

|                      | 4,K2,L1,L4,L3 |    |                   |                 |                                                           |

|                      | ,M1,L2,N1,P1  |    |                   |                 |                                                           |

| 152,14,13            | A4,F2,F1      | 3  | T_O_8             | CS#[2:0]        | Static IF external chip selects. CSO# is always used      |

|                      |               |    |                   |                 | for Flash.                                                |

| 15                   | G4            | 1  | T_O_8             | OE#             | External output enable. Active when reading data          |

|                      |               |    |                   |                 | from external devices including Flash                     |

| 16                   | G3            | 1  | T_O_8             | WE#             | Write Enable. Active when writing to external             |

|                      |               |    |                   |                 | devices                                                   |

| 38                   | M2            | 1  | T_B_8             | INT#            | External CPU interrupt – Defined as input by default      |

| 38                   | M2            | 0  | T_B_8             | CLK_50          | 50MHz clock output – pin function controlled by           |

|                      |               |    |                   |                 | firmware                                                  |

| 79                   | P13           | 1  |                   | BUS_SEL         | High for 8 bit external Flash device, low for 16 bit      |

|                      |               |    |                   | _               | external Flash device                                     |

| USB                  | •             |    |                   |                 |                                                           |

| 143                  | C8            | 1  | USB_B             | HSDP            | High Speed Data+ Connect to USB D+ line                   |

| 144                  | C7            | 1  | USB_B             | HSDM            | High Speed Data - Connect to USB D- line                  |

| 137                  | A9            | 1  | USB_O             | REXT            | 200 uA fixed reference bias current pin. Connect to       |

|                      |               |    | _                 |                 | ground via the external resister Rext 12.5K $\Omega$ ± 1% |

| 142                  | D8            | 1  | USB_B             | FSDP            | Full Speed Data + Connect to USB D+ line via              |

|                      |               | ]  | 555_5             |                 | external resister (39 $\Omega$ ±2 %)                      |

| 145                  | A6            | 1  | USB_B             | FSDM            | Full Speed Data - Connect to USB D- line via              |

| 170                  | 1,10          | '  | 000_0             | I SDIVI         | external resister (39 $\Omega$ ±2 %)                      |

|                      | I             | 1  |                   | 1               | CATOLINAL LOSISTOL (3/24 TV /0)                           |

| 138                      | D9           | 1  | USB_O        | RPU_ENA   | In FS mode and HS chirp mode, this pin is set to H                                     |

|--------------------------|--------------|----|--------------|-----------|----------------------------------------------------------------------------------------|

| 130                      | D 9          | '  | 030_0        | KFU_LINA  | to supply Vdd to external resister Rup (1.5K $\Omega$ ±5                               |

|                          |              |    |              |           | %). In HS operation, it is tri-stated.                                                 |

| IDE                      |              |    |              |           | 15), in the operation, the distinction                                                 |

| 73,71,65,63,60,56,54,52, | R12,P10,R9,  | 16 | T_B_4        | ID[15:0]  | IDE data bus                                                                           |

| 49,53,55,57,61,64,68,72  | M9,N8,N7,P6, |    |              |           |                                                                                        |

|                          | N6,P5,R6,M7, |    |              |           |                                                                                        |

|                          | R7,R8,N9,R1  |    |              |           |                                                                                        |

|                          | 0,M11        |    |              |           |                                                                                        |

| 46,48,47                 | P4,R4,N5     | 3  | T_O_4        | IA[2:0]   | IDE address bus                                                                        |

| 44,45                    | N4,R3        | 2  | T_O_4        | ICS#[1:0] | IDE chip select. Selects IDE drive 0 or 1                                              |

| 62                       | P8           | 1  | T_O_8        | IDE_OE#   | IDE output enable. Only used when external buffering is required to drive IDE data bus |

| 42                       | P3           | 1  | T_O_4        | IRESET    | IDE interface reset                                                                    |

| 74                       | P11          | 1  | 1_U_4<br>T I | DMARQ     | IDE IIIlerrace resei                                                                   |

| 75                       | R13          | 1  | T_O_4        | DIOW#     | IDE interface write strobe                                                             |

| 76                       | R14          | 1  | T_O_4        | DIOW#     | IDE interface write strobe                                                             |

| 77                       | P12          | 1  | 1_U_4<br>T I | IORDY     | IDE IIIGHAGE LEAN SHONE                                                                |

| 78                       | N11          | 1  | T_O_4        | DMACK#    |                                                                                        |

| 43                       | R2           | 1  | T I          | INTRQ     |                                                                                        |

| UART                     | 11/2         |    | <u> </u>     | INTING    |                                                                                        |

| 91                       | L15          | 1  | O 4          | SOUT      | Transmitter serial data output.                                                        |

| 89                       | L14          | 1  | 0_4          | RTS#      | Active-low Request To-Send output.                                                     |

| 92                       | K13          | 1  |              | SIN       | Receiver serial data input.                                                            |

| 90                       | K12          | 1  | i            | CTS#      | Active-low Clear-To-Send input.                                                        |

| PLL + OSC                |              |    |              | 1         |                                                                                        |

| 114                      | E13          | 1  | П            | XTLI      | OSC input from 48 MHz crystal (or crystal oscillator)                                  |

| 115                      | C15          | 1  | 0            | XTLO      | OSC output                                                                             |

| 122                      | D12          | 1  |              | PLL_TEST  | Test Enable (tie low for normal operation)                                             |

| 121                      | C13          | 1  |              | PLL_EN    | VCO Enable (tie high for normal operation)                                             |

| 120                      | C14          | 1  |              | VCOIN     | Loop filter in                                                                         |

| 119                      | A15          | 1  | 0            | CPOUT     | Loop filter out                                                                        |

| MISC                     |              |    |              |           |                                                                                        |

| 88                       | M15          | 1  | T_B_4        | GPIO 7    | General purpose IO / DTR# / Serial Audio driver word                                   |

| 87                       | L13          | 1  | T_B_4        | GPIO 6    | General purpose IO / DSR# / Serial Audio driver                                        |

| 07                       |              |    | 1_D_4        | 01100     | data                                                                                   |

| 86                       | M14          | 1  | T_B_4        | GPIO 5    | General purpose IO / DCD# / Serial Audio driver clk                                    |

| 85                       | N15          | 1  | T_B_4        | GPIO 4    | General purpose IO / RI                                                                |

| 84                       | P15          | 1  | T_B_4        | GPIO 3    | General purpose IO                                                                     |

| 83                       | M13          | 1  | T_B_4        | GPIO 2    | General purpose IO / STATIC WE2# (upper byte                                           |

|                          | 140          |    | T. C         | 0010.1    | write enable)                                                                          |

| 82                       | L12          | 1  | T_B_4        | GPIO 1    | General purpose IO / Serial Data                                                       |

| 81                       | N14          | 1  | T_B_4        | GPIO 0    | General purpose IO / Serial Clk                                                        |

| 129-127                  | D11,A12,B12  | 3  | l I          | TEST[2:0] | Test pins to select functional modes. See section 3.3 Functional Modes                 |

| 149                      | A5           | 1  | l            | RESET#    | Active low reset                                                                       |

| 41                       | R1           | 1  |              | FFLASH    | While low the device is configured in force_flash mode.                                |

| 80                       | R15          | 1  | I            | PHY_SEL   | Selects A or B Link PHY                                                                |

| 130                      | C11          | 1  | İ            | USB_IND   | High to indicate USB                                                                   |

|                          |              |    | •            |           | J                                                                                      |

|                          |              |    |              |           |                                                                                        |

|                          |              |    |              |           |                                                                                        |

|                          | 1            |    |              | •         | •                                                                                      |

| Power and ground <sup>2</sup>     |                                         |   |      |             |                   |

|-----------------------------------|-----------------------------------------|---|------|-------------|-------------------|

| 18,40,50,69,108,132,151           | G2,N2,R5,N1<br>0,F12,B11,D5             | 7 | CVDD | digital VDD | 1.8V Core voltage |

| 17,39,51,70,107,131,150           | G1,M4,M6,R1<br>1,G14,A11,B6             | 7 | CGND | digital GND |                   |

| 9,29,59,67,96,102,112,1<br>16,160 | E1,K3,M8,M1<br>0,J13,H14,D1<br>5,B15,B2 | 9 | VDD  | digital VDD | 3.3V IO voltage   |

| 8,28,58,66,95,101,110,1<br>13,159 | E3,K1,P7,P9,<br>J12,H13,F13,<br>E12,A1  | 9 | GND  | digital GND |                   |

| 133,135,139,148                   | D10,C10,C9,<br>C6                       | 4 | UVDD | USB VDD     | 3.3V IO voltage   |

| 134,136,140,141,146,14<br>7       | A10,B10,A8,B<br>9,B7,D6                 | 6 | UGND | USB GND     |                   |

| 118                               | E14                                     | 1 | PVDD | PLL VDD     | 1.8V PLL voltage  |

| 117                               | D14                                     | 1 | PGND | PLL GND     |                   |

Table 1 - Pin Description

# Note 1: Type key – (w\_) x (y)(\_z) – All IO are CMOS levels

| Τ   | 5V tolerant          |

|-----|----------------------|

|     | 3.3V                 |

|     |                      |

| Χ   | Direction            |

| - 1 | input                |

| 0   | output               |

| В   | Bi-directional       |

|     |                      |

| у   | Pull-up/down         |

| UD  | pull-up<br>pull-down |

| D   | pull-down            |

|     | none                 |

|     |                      |

|     |                      |

| 4<br>8 | 4 m<br>8 m | A drive<br>A drive                                   |

|--------|------------|------------------------------------------------------|

|        |            | Dedicated USB output<br>Dedicated USB bi-directional |

| CVE    | )D         | 1.8V Digital Core Power                              |

Output drive capability

CGND Core Ground

VDD 3.3V IO Digital Power

GND IO Ground

PVDD 1.8V Digital Core Power

PGND PLL Ground

UVDD 3.3V Analogue Power

UGND Analogue Ground

# Note 2: Power and ground

Tolerance

Separate supplies are recommended for the digital and analogue power supplies.

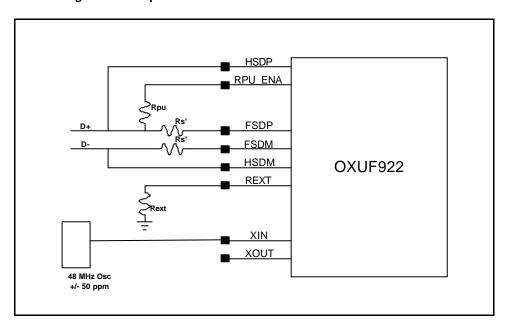

# 3.1 USB Pin Configuration Requirement

(Note: see Table 1 - Pin Description for resistor values)

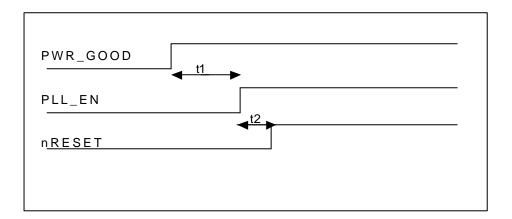

# 3.2 Power on / reset sequence

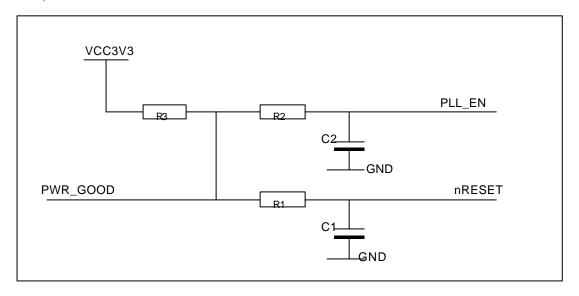

The OXUF922 Requires reset timing as follows:

- t1: The oscillator needs time to stabilise before the OXUF922's PLL is enabled (by pulling high PLL\_EN). t1 is the time required from power being stable (within limits) for the oscillator to stabilize.

- t2: >2mS. This is the minimum delay required for the PLL to lock. The PLL must be locked prior to taking the OXUF922 out of reset.

The OXUF922 PLL Enable and Reset inputs have Schmitt type inputs to allow the use of RC delay elements as shown in the example below.

In calculating values for R1, R2, R3, C1 and C2, 'PWR\_GOOD' is assumed to be an open drain output from the local power conditioning circuitry and that it can sink at least 1mA with an output low voltage of 0.3v thereby setting R3 at 3K3 (as nearest convenient value).

For this example let the requirement for T1 be 40mS (the actual requirement will depend on the oscillator used which is application dependant.)

The lowest value of input high voltage for the OXUF922 Schmitt inputs is 0.9 Volts (Min Vil + Min Hysteresis = 0.5 + 0.4 V).

Using R = T / (C \* In[(Vaim - Vstart)/(Vaim - Vth)])

Calculate value for R2 given C2 = 1uF

Set C = 1uF

T = 50mS

Vaim = 3.3 V (Supply voltage)

Vstart = 0.3 V (PWR\_GOOD Output Low) Vth = 0.9 V (Input high voltage)

Gives R = 224K therefore let R2 = 220K as nearest standard value.

When tolerances, thresholds and supply range are accounted for, C = +20%, R = +5%, Vaim = 3.0, Vth = 2.3 T becomes 374 ms

Now calculate values for R1 given C1 = 1uF.

Set C = 1uF - 20%

T = 52mS

Vaim = 3.3 V (Supply voltage)

Vstart = 0.3 V (PWR\_GOOD Output Low) Vth = 0.9 V (Input high voltage)

Gives R = 291.3K therefore let R1 = 330K to use standard values and account for 5% tolerance

The 3K3 pull-up will extend these times slightly but is insignificant compared to capacitor tolerance.

R1 = 69K ohms C1 = 330nF makes  $t2 \sim 4.5$ mS.

C1 is determined from the minimum Vih threshold of 0.9V, a starting Vil of 0.3v. By making R1 large enough not to load the output say 69K. This leads to a value of 240nF. This has been rounded up to 330nF as the nearest standard value and provides some margin.

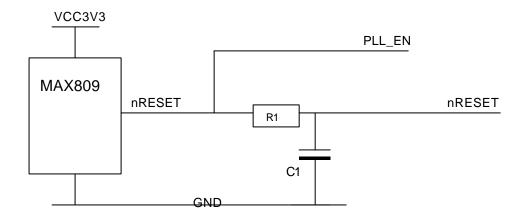

The MAX809 provides a reset low pulse of 140mS, easily accommodating the requirements for t1.

#### Why use the MAX809?

A reset controller is defined for this circuit because not using one requires knowledge of the end user systems power supply characteristics, specifically the supply rise time.

### 3.2.1 Lockup Hazard

If an OXUF922 /PHY combination is powered up attached to a 1394 bus, there is a potential hazard where the OXUF922 misses the node ID from the PHY and hence fails to operate correctly. This is only an issue when trying to access the flash port when no firmware is loaded. When firmware is loaded one of the first things it does is cause a bus reset which sorts everything out.

Avoidance action: Ensure the OXUF922 comes out of reset before the PHY.

#### 3.3 Functional Modes

| Test Mode <sup>1</sup> | Description                                                                    |

|------------------------|--------------------------------------------------------------------------------|

| 000                    | Normal mode – 8 or 16 bit data bus, 128Kbyte address range                     |

| 001                    | JTAG bond out on upper data bus, 8 bit data bus only, 1Mbyte address range     |

| 010                    | 1394 Only, no USB clock source required                                        |

| 011                    | Reserved                                                                       |

| 100                    | Reserved                                                                       |

| 101                    | Extended address on upper data bus, 8 bit data bus only, 4 MByte address range |

| 110                    | Reserved                                                                       |

| 111                    | Reserved                                                                       |

#### Notes

1. Test Mode = TEST [2:0] pins

#### 3.4 External Devices Required

8/16-bit Flash

48 MHz  $\pm\,50$  ppm crystal oscillator for USB (and system clock). 1394 PHY (A or B) and corresponding crystal.

# 4 MEMORY ORGANISATION

# 4.1 Memory Organisation

| Block                    | CPU Base Address | Decode Size (Bytes) |

|--------------------------|------------------|---------------------|

| External Chip Selects    | 0x00000000       | 4 x 4M              |

| Repeat of above          | 0x01000000       | 4 x 4M              |

| Repeat of above          | 0x02000000       | 4 x 4M              |

| Repeat of above          | 0x03000000       | 4 x 4M              |

| Unused                   | 0x04000000       |                     |

| Unused                   | 0x05000000       |                     |

| FIFO Manager             | 0x06000000       | n/a                 |

| UART                     | 0x07000000       |                     |

| Unused                   | 0x08000000       |                     |

| Unused                   | 0x09000000       |                     |

| Logic Registers          | 0x0A00000        | n/a                 |

| Logic Registers (Repeat) | 0x0B000000       | n/a                 |

| Unused                   | 0x0C000000       |                     |

| Unused                   | 0x0D000000       |                     |

| Static If                | 0x0E000000       | n/a                 |

| Unused                   | 0x0F000000       |                     |

| SCRATCH RAM Base address | 0x80002000       | 8K                  |

# 4.2 Register Set and Base Addresses of Hardware Devices

| Block                                  | Base Address (31:16)                                 | Location                              |  |  |  |  |  |  |

|----------------------------------------|------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| Chip Select 0 address (External Flash) | 0x0000                                               | See section 5.2 Static RAM Controller |  |  |  |  |  |  |

| Chip Select 1                          | 0x0040                                               | See section 5.2 Static RAM Controller |  |  |  |  |  |  |

| Chip Select 2                          | 0x0080                                               | See section 5.2 Static RAM Controller |  |  |  |  |  |  |

| not used                               | 0x00C0                                               |                                       |  |  |  |  |  |  |

| UART                                   | 0x0700                                               | See section 6 UART                    |  |  |  |  |  |  |

| RPS                                    | 0x0A00                                               | See section 5.3 RPS Block             |  |  |  |  |  |  |

| Link                                   | 0x0A10                                               | See section 7.4 Link-Core             |  |  |  |  |  |  |

| Async Engine                           | 0x0A20                                               | See section 7.8 Async Engine          |  |  |  |  |  |  |

| Queue Selector                         | 0x0A28                                               | See section 7.7 Queue Selector        |  |  |  |  |  |  |

| USB                                    | 0x0A30                                               | See section 7.9 USB2 core             |  |  |  |  |  |  |

| FIFOMAN                                | 0x0A40                                               | See section 7.5 FIFO Manager.         |  |  |  |  |  |  |

| not used                               | 0x0A50                                               |                                       |  |  |  |  |  |  |

| DMA                                    | 0x0A60                                               | See section 7.1 DMA Engine            |  |  |  |  |  |  |

| ATA                                    | 0x0A70                                               | See section 7.2 ATA Block             |  |  |  |  |  |  |

| OCP                                    | 0x0A80                                               | See section 7.6 ORB Co-Processor.     |  |  |  |  |  |  |

| not used                               | 0x0A90                                               |                                       |  |  |  |  |  |  |

| serial control                         | 0x0AA0                                               | See section 7.10 Serial Controller    |  |  |  |  |  |  |

| clock control                          | 0x0AB0                                               | See section 5.1 Clock Block           |  |  |  |  |  |  |

| Serial Audio                           | 0x0AC0                                               | See section 7.11 Serial Audio         |  |  |  |  |  |  |

| not used                               | 0x0AD0 - 0AF0                                        |                                       |  |  |  |  |  |  |

| Static Registers                       | 0x0E00                                               | See section 5.2 Static RAM Controller |  |  |  |  |  |  |

|                                        |                                                      |                                       |  |  |  |  |  |  |

| No                                     | Note : register set repeats, only bits 27:24 decoded |                                       |  |  |  |  |  |  |

# 5 CPU Functions

### 5.1 Clock Block

The clock block contains all the clock generation and gating logic required. There are four registers to allow the control of the serial clock, the clock to the USB PHY for suspend and power saving control and the stop and start controls for the clocks to the majority of the logic. In addition to stopping clocks it is also possible to slow all the logic clocks, except the USB PHY clock to half speed. This is done via bit 30 of the start / stop registers.

The table below details which clocks run at what speed, which are controllable and their state after reset.

The normal application of the device would have the 48 MHz source being used as the system clock and USB clock, and a separate crystal being used for the 1394 PHY. There is an additional mode where the 1394 clock can be used to replace the 48 MHz, but this then precludes the use of USB. See section 3.3 Functional Modes for details on pin assignment for this.

| Block                      | Frequency (MHz) | Clock Stop | Reset Value |

|----------------------------|-----------------|------------|-------------|

| Fifoman – CPU bus          | 50              | Yes        | Stopped     |

| Fifoman – DMA bus          | 100             | Yes        | Stopped     |

| OCP – AHB master           | 50              | Yes        | Stopped     |

| OCP – function             | 100             | Yes        | Stopped     |

| Static                     | 50              | Yes        | Running     |

| Serial                     | 50              | Yes        | Stopped     |

| UART – AHB                 | 50              | Yes        | Stopped     |

| UART – sys_clk             | 50              | Yes        | Stopped     |

| Link / Async / Queue Sel   | 100             | Yes        | Running     |

| USB                        | 100             | Yes        | Running     |

| DMA / ATA / DMA AHB subsys | 100             | Yes        | Stopped     |

| Serial Audio               | 100             | Yes        | Stopped     |

# 5.1.1 Clock Control Registers

Clock control registers can be found starting at location 0AB00000

| Register           | Offset | Reset value | Description                            |

|--------------------|--------|-------------|----------------------------------------|

| Serial Clk Control | 0      | 0x020       | Divider value to generate serial clock |

| UTMI CIk Control   | 4      | 0x01        | UTMI PHY clock enable (1=enabled)      |

| Clock Stop         | 8      | 0x01DC      | Write to stop various clocks           |

| Clock Start        | С      | 0x01DC      | Write to start various clocks          |

# 5.1.2 Serial Clk Register

Set one bit to select serial dk frequency when using serial if controller

| Bit  | Serial frequency (MHz) | Reset read value |

|------|------------------------|------------------|

| 0    | 100 / 8                | 0                |

| 1    | 100 / 16               | 0                |

| 2    | 100 / 32               | 0                |

| 3    | 100 / 64               | 0                |

| 4    | 100 / 128              | 0                |

| 5    | 100 / 256              | 1                |

| 6    | 100 / 512              | 0                |

| 7    | 100 / 1024             | 0                |

| 31-8 | reserved               | 0                |

# 5.1.3 UTMI Clk Register

Writing to this register will enable / disable the UTMI PHY's clock. This can be used in conjunction with the suspend indication in the USB core to put the USB PHY into power save mode.

| Bit  | UTMI Clk enable               | Reset read value |

|------|-------------------------------|------------------|

| 0    | 1 to enable clk, 0 to disable | 1                |

| 31-1 | reserved                      | 0                |

#### 5.1.4 Clock Stop Register

Write 1 to stop the clocks (bits 0 to 9)

Write 1 to slow clocks below to half rate (bit 30)

| Clock Stop bit | Clock(s)                  | Reset read value         |

|----------------|---------------------------|--------------------------|

| 0              | Link system clock         | 0 = started, 1 = stopped |

|                | Async clock               |                          |

|                | Queue sel clock           |                          |

| 1              | USB system clock          | 0                        |

| 2              | FM system clock           | 1                        |

|                | FM AHB CPU clock          |                          |

| 3              | OCP system clock          | 1                        |

|                | OCP AHB CPU clock         |                          |

| 4              | DMA system clock          | 1                        |

|                | ATA system clock          |                          |

| 5              | Static system clock       | 0                        |

| 6              | Serial system clock       | 1                        |

| 7              | Serial Audio system clock | 1                        |

| 8              | UART system clock         | 1                        |

|                | UART AHB clock            |                          |

| 29:9           | Not defined               | 0                        |

| 30             | Slow clock select         | 0 = normal, 1= slow      |

| 31             | Reserved                  | 0                        |

5.1.5 Clock Start Register

Write 1 to start the clocks (bits 0 to 9)

Write 1 to bit 30 to return clocks below to full rate

| Clock Start bit | Clock(s)                  | Reset / read value       |

|-----------------|---------------------------|--------------------------|

| 0               | Link system clock         | 0 = started, 1 = stopped |

|                 | Async clock               |                          |

|                 | Queue sel clock           |                          |

| 1               | USB system clock          | 0                        |

| 2               | FM system clock           | 1                        |

|                 | FM AHB CPU clock          |                          |

| 3               | OCP system clock          | 1                        |

|                 | OCP AHB CPU clock         |                          |

| 4               | DMA system clock          | 1                        |

|                 | ATA system clock          |                          |

| 5               | Static system clock       | 0                        |

| 6               | Serial system clock       | 1                        |

| 7               | Serial Audio system clock | 1                        |

| 8               | UART system clock         | 1                        |

|                 | UART AHB clock            |                          |

| 29:9            | Not defined               | 0                        |

| 30              | Slow clock select         | 0 = normal, 1= slow      |

| 31              | reserved                  | 0                        |

### 5.2 Static RAM Controller

The controller supports up to three chip select banks with independent timing control. This allows the external connection of flash and peripherals to the OXUF922, so the chip can take on the responsibility of application host.

- Three separate chip select banks (CS0, CS1 & CS2).

- 8bit or 16bit memory support (pin select for cs0 boot, register select for cs1 & cs2)

- Bank size up to 4MBytes (A21:0) when the chip is in 8 bit mode

- Bank size up to 1MBytes (A19:0) when the chip is in 8 bit mode with JTAG debug

- Bank size up to 128KBytes(A16:1) when the chip is in 16 bit mode

- Programmable burst fetch.

- Supports external 245 buffer ICs for glue-less data bus expansion.

- Configurable pin for an interrupt input from a static peripheral or 50 MHz output for use by a synchronous peripheral on the static bus.

- Second write enable pin can be selected to be used for an upper byte write enable for 16 bit SRAM on the static bus.

The way each chip select bank is accessed and controlled is via its own register. The register for each bank (address space) controls the following:-

- Whether it is an 8 bit or 16 bit bus. Note that when in 8 bit mode the bank size is 4Mbytes, when in 16 bit mode it is 128Kbytes.

- A delay of up to 3 clocks can be added to /WE strobing low after /CS strobes low in a write cycle.

- The number of clocks into a write cycle that /WE goes high can be controlled.

- The number of clocks /CS is low in a write cycle (from 1 up to 64).

- The number of clocks /CS is low in a read cycle (from 1 up to 64).

- /OE can be delayed by 1 Clk after /CS strobes low in a read cycle.

Note: Setting the test pins may constrain the data width of connected memory devices, regardless of the register settings.

### 5.2.1 Register Set

All addresses are stated as an offset from the static ram controller register set base address, 0x0E000000.

| Address offset from | R/W | Reset Value | Register                           |

|---------------------|-----|-------------|------------------------------------|

| STATIC_REG_BASE     |     |             |                                    |

| 0x00                | R   | 0x0000001   | Version ID register                |

| 0x04                | R/W | 0xXFFFFFF   | Static Bank 0 register (Boot Bank) |

| 0x08                | R/W | 0x0FFFFFF   | Static Bank 1 register             |

| 0x0C                | R/W | 0x0FFFFFF   | Static Bank 2 register             |

| 0x10                |     |             | Not used                           |

Note X values in Boot bank reset. See below.

## 5.2.2 Static Bank registers 0 to 3

| Bits  | Dir | Name              | Reset  | Function                                                             |

|-------|-----|-------------------|--------|----------------------------------------------------------------------|

| 31:30 | R/W | Width             | 00*    | External memory width "00" 8bit, "01" 16bit, "10" 32bit              |

| 29    | R/W | Read Burst Enable | 0      | Enable read bursts speeds access by not raising /CS between accesses |

| 28    | R/W | Buffer Present    | 0      | External 245 buffer required for this bank                           |

| 27:26 |     | write_start       | 11     | The number of clocks into the write cycle that the /WE strobes fall. |

| 25:24 | R/W | turn_cycle        | 11     | Turn around time in CPU clocks. /CS high time.                       |

| 23:22 |     | Reserved          | 11     |                                                                      |

| 21:16 | R/W | write_pulse       | 111111 | The number of clocks into the write cycle that the /WE strobes rise. |

| 15:14 |     | Reserved          | 11     |                                                                      |

| 13:8  |     | write_cycle       | 111111 | /CS is low for write_cycle+1 for a write access                      |

| 7     | R/W | Delay ÓE          | 1      | Specifies whether OE should be delayed 1 clock from CS               |

| 6     |     | Reserved          | 1      |                                                                      |

| 5:0   | R/W | read_cycle        | 111111 | /CS is low for read_cycle+1 for a read access.                       |

The reset value is such that the memory works in the slowest possible mode.

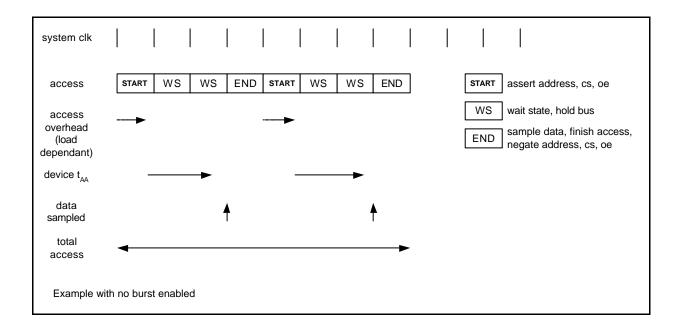

Section 12 External Bus Timing Diagrams gives examples of various configurations.

# 5.2.3 Example Bus Timing with Wait States

Assuming an 8-bit Flash device on CS(0), the following diagram and tables gives example values to set in the bank registers depending on the access time of the device ( $t_{AA}$ ).

<sup>\*</sup>The Width configuration for the boot block is set by pin 79 **BUS\_SEL**, so that the boot block can be accessed correctly from reset. This should be set in conjunction with the test pins.

|                         |                            |                        | Total Access Time (ns) |         |                    |       |  |

|-------------------------|----------------------------|------------------------|------------------------|---------|--------------------|-------|--|

|                         | Max t <sub>AA</sub> (ns) 3 |                        | 32bit Read (ARM)       |         | 16bit Read (Thumb) |       |  |

| Read_cycle <sup>1</sup> | 15pF load <sup>2</sup>     | 25pF load <sup>2</sup> | No Burst <sup>4</sup>  | Burst 5 | No Burst           | Burst |  |

| 0                       | 4.6                        | 3.6                    | 167                    | 104     | 83                 | 63    |  |

| 1                       | 25.4                       | 24.4                   | 250                    | 188     | 125                | 104   |  |

| 2                       | 46.3                       | 45.3                   | 333                    | 271     | 167                | 146   |  |

| 3                       | 67.1                       | 66.1                   | 417                    | 354     | 208                | 188   |  |

| 4                       | 87.9                       | 86.9                   | 500                    | 438     | 250                | 229   |  |

#### 49.152 MHz system clock (1394 only)

|                         |                                       |                        | Total Access Time (ns) |                    |                    |       |

|-------------------------|---------------------------------------|------------------------|------------------------|--------------------|--------------------|-------|

|                         | Max t <sub>AA</sub> (ns) <sup>3</sup> |                        | 32bit Read (ARM)       |                    | 16bit Read (Thumb) |       |

| Read_cycle <sup>1</sup> | 15pF load <sup>2</sup>                | 25pF load <sup>2</sup> | No Burst 4             | Burst <sup>5</sup> | No Burst           | Burst |

| 0                       | 4.1                                   | 3.1                    | 163                    | 102                | 81                 | 61    |

| 1                       | 24.4                                  | 23.4                   | 244                    | 183                | 122                | 102   |

| 2                       | 44.8                                  | 43.8                   | 326                    | 264                | 163                | 142   |

| 3                       | 65.1                                  | 64.1                   | 407                    | 346                | 203                | 183   |

| 4                       | 85.5                                  | 84.5                   | 488                    | 427                | 244                | 224   |

#### Notes

- 1. read\_cycle as defined by bits (5:0) in bank register

- 2. Load seen by address, cs (chip select) and oe (output enable). Affects access overhead. (16.25ns for 15pF, 17.25ns for 25pF)

- 3. Max t<sub>M</sub> is calculated from ((1 + read\_cycle) \* system clk period) access overhead.

- 4. Total access time = (1 + read\_cycle + 1) \* system clk period \* number of required memory accesses

- 5. Total access time = ((1 + read\_cycle) \* system clk period \* number of required memory accesses) + 1 \* system clk period

### 5.2.4 General Address Decoding

The following address decodes are used by this block. Note the processor must have the boot code at address 0x00000000.

|   | ARM address offset from STATIC_BASE | Block                          | Function       |

|---|-------------------------------------|--------------------------------|----------------|

|   | 0x0000000                           | External FLASH chip select (0) | External Flash |

| 1 | 0x00400000                          | External chip select (1)       | SRAM           |

| 1 | 0x00800000                          | External chip select (2)       | LED Bank       |

### 5.2.5 Additional Functions

To provide a means to directly interface to an external device running synchronously to the OXUF922, there is the facility to output the CPU dock. This is controlled from the GPIO data register detailed below. Timing diagrams showing the timing relationship is shown in section 12 External Bus Timing Diagrams.

Additionally when interfacing to a 16bit SRAM a second write enable maybe required for byte write accesses. This function is also provided through the GPIO register below.

GPIO data register - location 0x0A0003C0 - note this will also control the direction change of the pin.

| GPIO data bit | Write                                                                 | Read                 | Reset value |

|---------------|-----------------------------------------------------------------------|----------------------|-------------|

| 17            | Set to 1 to mux static_wen(1) onto GPIO(2) pin for 16 bit SRAM writes | Register write value | 0           |

| 18            | Set to 1 to output static_clk (50 MHz) on pin 38 (static_int)         | Register write value | 0           |

#### 5.3 RPS Block

The ARM Reference Peripheral Set RPS provides a basic set of standard APB peripherals. The reference peripheral set (or RPS) is intended to provide useful common functionality that is required in many embedded systems. This block implements counter timer, interrupt controller and address map controller. These peripherals are fully defined in ARM's RPS specification. In addition to these, this RPS includes the following extra system peripherals:

- A watchdog timer for providing a system reset should software hang, or if no software is present

- A GPIO controller to provide flexible digital IO

- A Block reset controller which allows individual design sub-blocks to be reset independently of one another under software control

### 5.3.1 Block descriptions

Brief description of the blocks is given below with more detailed descriptions following

#### *Interrupt Controller (see section 5.4)*

The interrupt controller provides a means by which the processors enable, disable, set and clear the various interrupts in the system. The actual interrupts seen by the processor are routed from this block. This block is also fully specified in the ARM RPS specification.

### Watchdog Timer (see section 5.6)

This block provides a counter which is continually counting (incrementing every CPU clock cycle). The count is reset every time its register is read (returning the count immediately prior to the read), and a timeout output goes active if the terminal count is ever reached. This timeout may be used to reset the system processor. This provides a useful facility for software crash protection.

In addition, the watchdog has two timeout modes, Fast (default) and slow. In fast timeout mode, the terminal count is 16,384 clock cycles (327uS with a 50MHz clock). In slow timeout mode (which may be entered by writing a special value to the watchdog register), the timeout is a longer programmable period. (This is defined in more detail in the register block description).

The watchdog switch on timeout output is a programmable output (reset to ACTIVE) for interfacing to a "Force Flash" controller. The intended use is to cause a transition to force flash mode if a watchdog timeout occurs while this bit is set.

#### Programmable Counters (see section 5.7)

These are programmable 16-bit down counting interval (re-loading) or timeout (one-shot) counters used for generating timed interrupts to the processor. These timers are fully specified in the ARM RPS specification.

### GPIO (see section 5.8)

This block provides user I/O. GPIOs can be programmed as inputs or outputs. Additionally, inputs can be set to cause an interrupt upon a transition. Each GPIO has its own direction control (output enable), so open drain outputs can be emulated easily by setting the output value to zero, and writing the inverse of the data to the OE bit instead of the output.

### Block Reset Controller (see section 5.9)

This block simply defines a writable register which generates several reset outputs which can be routed to the various sub-blocks in the system, in order to provide more flexible resetting. All reset outputs are activated by the global system reset input, or by setting the appropriate bit in the reset control register. In this case the bit is self-clearing, and the reset is activated for 4 CPU clock cycles.

# 5.4 ARM RPS Register Set Summary

| BASE         | READ                     | WRITE              |  |  |

|--------------|--------------------------|--------------------|--|--|

| IRQ Interrup | ot Control               |                    |  |  |

| 0x0000       | Masked IRQ Source Status | none               |  |  |

| 0x0004       | Raw IRQ Source Status    | none               |  |  |

| 0x0008       | IRQ Enable Mask          | IRQ Enable bits    |  |  |

| 0x000C       | none                     | IRQ Disable bits   |  |  |

| 0x0010       | none                     | Software Interrupt |  |  |

|              |                          |                    |  |  |

| FIQ Interrup |                          | 1                  |  |  |

| 0x0104       | Masked FIQ Source Status | none               |  |  |

| 0x0108       | Raw FIQ Source Status    | none               |  |  |

| 0x010C       | FIQ Enable Mask          | FIQ Enable bits    |  |  |

| 0x0110       | none                     | FIQ Disable bits   |  |  |

|              |                          |                    |  |  |

| Timer One    |                          |                    |  |  |

| 0x0200       |                          | 1 Load             |  |  |

| 0x0204       | Timer 1 Current Count    | none               |  |  |

| 0x0208       |                          | Control            |  |  |

| 0x020C       | none                     | Timer 1 Clear      |  |  |

| 0x0210       | none                     | none               |  |  |

| Timer Two    |                          |                    |  |  |

| 0x0220       | Timor                    | 2 Load             |  |  |

| 0x0220       | Timer 2 Current Count    | none               |  |  |

| 0x0224       |                          | 2 Control          |  |  |

| 0x022C       | none                     | Timer 2 Clear      |  |  |

| 0x0230       | none                     | none               |  |  |

| 0,10200      | 770170                   | 776170             |  |  |

| Reset & Re   | map                      |                    |  |  |

| 0x0300       | none                     | Pause              |  |  |

| 0x0304       | Identification           | none               |  |  |

| 0x0308       | none                     | Clear Reset Map    |  |  |

|              | D + 0++                  | D + O+ + O +       |  |  |

Note: Reset & Remap registers are NOT implemented in the OXUF922.

0x030C

0x0310

Reset Status

none

Data Sheet Rev 1.1 Page 25

Reset Status Set

Reset Status Clear

# 5.5 Interrupt Operation

The interrupt controller provides a means by which the processor can enable, disable, set and clear the various interrupts in the system. The actual interrupts seen by the processor are routed from this block. This block is fully specified in the ARM RPS specification.

# 5.5.1 Interrupt Bit Mapping

The interrupt registers can be found starting at location 0A000000. The table below shows the OXUF922 interrupt 32-bit assignment for the Interrupt Controller.

| Interrupt bit | Write / Read       | Reset value |

|---------------|--------------------|-------------|

| 0             | FIQ – SERIAL AUDIO | 0           |

| 1             | Software Irq (SWI) | 0           |

| 2             | Reserved           | 0           |

| 3             | Reserved           | 0           |

| 4             | Timer 0            | 0           |

| 5             | Timer 1            | 0           |

| 6             | ATA                | 0           |

| 7             | DMA                | 0           |

| 8             | Link               | 0           |

| 9             | UART               | 0           |

| 10            | Async              | 0           |

| 11            | FIFOMAN            | 0           |

| 12            | Reserved           | 0           |

| 13            | OCP                | 0           |

| 14            | USBCORE            | 0           |

| 15            | Static             | 0           |

| 31            | GPIO interrupt     | 0           |

| 16:30         | Reserved           | 0           |

### 5.6 Watchdog Timer

This block provides a counter which is continually counting (incrementing every CPU clock cycle). The count is reset every time its register is read (returning the count immediately prior to the read) under normal operation the watchdog timer must be cleared at a regular interval. If this is not done a timeout output goes active if the terminal count is ever reached. This timeout may be used to reset the system processor. This provides a useful facility for software crash protection providing a system reset should software hang.

In addition, the watchdog has two timeout modes, Fast (default) and slow. In fast timeout mode, the terminal count is 16,384 clock cycles (327uS with a 50MHz clock). In slow timeout mode (which may be entered by writing a special value to the watchdog register), the timeout is a longer programmable period. (This is defined in more detail in the register block description below).

The watchdog switch on timeout output is a programmable output (reset to ACTIVE) for interfacing to a "Force Flash" controller. The intended use is to cause a transition to force flash mode if a watchdog timeout occurs while this bit is set.

### 5.6.1 Watchdog timer - location 0x0A000380

| Offset<br>0x0380 | Watchdog Control Register 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| RD               | Number of APB clock cycles sincle last read (or reset)                                                          |

| WR1              | 0 0 0 1 0 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 1 1 0 0 0 1 5                                                         |

| WR2              | 0 0 1 0 0 0 0 0 1 1 0 1 0 Timeout 0 1 0 1 1 1 1 1 0 0 0 1 0 0 1                                                 |

Reading the watchdog returns the number of CPU clock cycles since the last time it was read (or reset) and then resets the count. The count is also reset when a timeout occurs, or the ARM reset input signal is asserted. Writing to this register with values from 0x1068AFC5 to 0x1068AFC7 allows the F and S bits to be set (according to the bottom two bits of the value written).

Switch on timeout bit (S) is intended for use in conjunction with an external "Force flash" controller, allowing it to enter force flash mode upon a watchdog timeout when this bit is set. This bit is set by default.

Fast Timeout bit (F) is used to cause watchdog timeout after just 16,384 clock cycles. This is the default state, hence software should clear this bit and the S bit as soon as possible after booting (By writing **0x1068AFC4**)

#### 5.6.2 WDT PERIOD

Writing this register with 0x20D15F89 OR'ed with (timeout << 16) allows setting of the long timeout value (F = '0'). The timeouts defined are given in the following table:

| F Bit | Timeout Clocks to timeout Period – 50 |              | Period – 50MHz clock |

|-------|---------------------------------------|--------------|----------------------|

| 1     | Х                                     | 16 x 1024    | 327 us               |

| 0     | 0                                     | 4096 x 1024  | 84 ms                |

| 0     | 1 (default)                           | 8192 x 1024  | 168 ms               |

| 0     | 2                                     | 16384 x 1024 | 336 ms               |

| 0     | 3                                     | 32768 x 1024 | 671 ms               |

| 0     | 4                                     | 65536 x 1024 | 1.34 s               |

| 0     | 5-7                                   | Reserved     | Undefined            |

The watchdog may be completely **disabled** by writing the value **0x20D15F88**. It should be noted that once the watchdog has been disabled the counter is stopped. Writing with the timeout value specified above will re-enable the watchdog.

#### 5.7 Counter Timers

#### 5.7.1 Overview

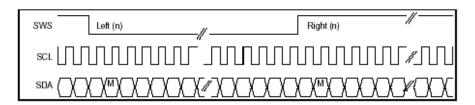

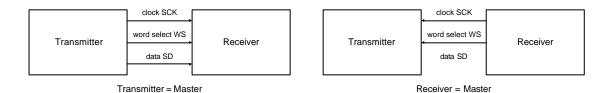

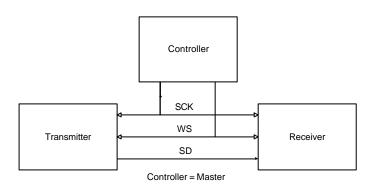

The OXUF922 has two timer modules which can be either a programmable 16-bit down counting interval (re-loading) or a timeout (one-shot) counter used for generating timed interrupts to the processor. Each channel can be independently programmed to perform a wide range of functions, including frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse-width modulation.