# 8-BIT PARALLEL-OUT SERIAL | \$54164 SHIFT REGISTERS

N74164

\$54164-A,F,W • N74164-A,F

DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

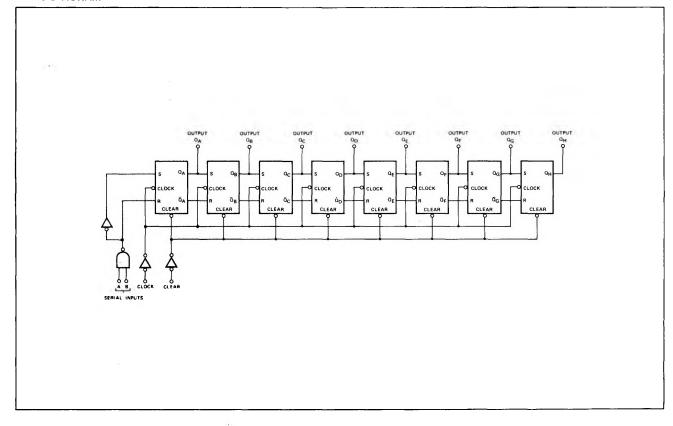

These 8-bit shift registers feature gated serial inputs and an asynchronous clear. The gated serial inputs (A and B) permit complete control over incoming data as a low at either (or both) input(s) inhibits entry of the new data and resets the first flip-flop to the low level at the next clock pulse. A high-level input enables the other input which will then determine the state of the first flip-flop. Data at the serial inputs may be changed while the clock is high, but only information meeting the setup requirements will be entered. Clocking occurs on the low-to-high-level transition of the clock input.

All inputs are diode-clamped to minimize transmission-line effects, and are buffered to represent only one Series 54/74 load which simplifies system design. Power dissipation is typically 21 milliwatts per bit. Maximum input clock frequency is typically 36 megahertz.

The S54164 is characterized for operation over the full military temperature range of -55°C to 125°C; the N74164 is characterized for operation from 0°C to 70°C.

#### TRUTH TABLE

| SERIA | LINP            | JTS A AND           |

|-------|-----------------|---------------------|

| INP   | UTS             | OUTPUT              |

| A1    | ۲t <sub>n</sub> | ATt <sub>n</sub> +1 |

| Α     | В               | QA                  |

| H     | Н               | Н                   |

| L     | Н               | L                   |

| н     | L               | L                   |

| L     | L               | L                   |

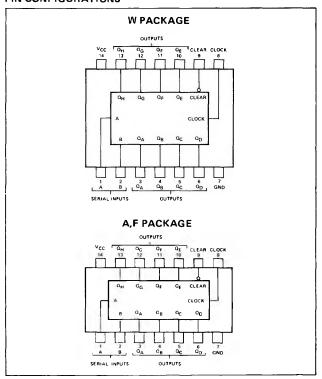

#### PIN CONFIGURATIONS

# LOGIC DIAGRAM

# SIGNETICS DIGITAL 54/74 TTL SERIES - S54164 ● N74164

#### RECOMMENDED OPERATING CONDITIONS

|                                                          | S54164 |     | N74164 |      |     |      |      |

|----------------------------------------------------------|--------|-----|--------|------|-----|------|------|

|                                                          | MIN    | NOM | MAX    | MIN  | NOM | MAX  | UNIT |

| Supply Voltage V <sub>CC</sub>                           | 4.5    | 5   | 5.5    | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out from each Output, N: High logic level |        |     | 10     |      |     | 10   |      |

| Low logic level                                          |        |     | 5      |      |     | 5    |      |

| Input Clock Frequency, fclock                            | 0      |     | 25     | 0    |     | 25   | MHz  |

| Width of Clock or Clear Input Pulse, tw                  | 20     |     | ,      | 20   |     |      | ns   |

| Data Setup Time, t <sub>setup</sub>                      | 15     |     |        | 15   |     |      | ns   |

| Data Hold Time, thold                                    | 0      |     |        | 0    |     |      | กร   |

| Operating Free-Air Temperature, TA                       | -55    | 25  | 125    | 0    | 25  | 70   | °c   |

# ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                 | DADAMETED                              | TEST COMPLETIONS *                                |                                                   | S54164 |                  | N74164 |     |          | 140117 |      |

|-----------------|----------------------------------------|---------------------------------------------------|---------------------------------------------------|--------|------------------|--------|-----|----------|--------|------|

| PARAMETER       |                                        | TEST CONDITIONS*                                  |                                                   | MIN    | TYP**            | MAX    | MIN | TYP*     | * мах  | UNIT |

| VIH             | High-level input voltage               |                                                   |                                                   | 2      |                  |        | 2   |          |        | V    |

| VIL             | Low-level input voltage                |                                                   |                                                   | 1      |                  | 8.0    |     |          | 0.8    | V    |

| v <sub>i</sub>  | Input clamp voltage                    | V <sub>CC</sub> = MAX,                            | I <sub>I</sub> = -12mA                            |        |                  | -1.5   |     |          | ~1.5   | V    |

| v <sub>OH</sub> | High-level output voltage              | $V_{CC} = MIN,$ $V_{IL} = 0.8V,$                  | V <sub>IH</sub> = 2V,<br>I <sub>OH</sub> = -400μA | 2.4    |                  |        | 2.4 |          |        | V    |

| VOL             | Low-level output voltage               | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8V, | V <sub>IH.</sub> = 2V,<br>I <sub>OL</sub> = 8mA   |        |                  | 0.4    |     |          | 0.4    | V    |

| 11              | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                            | V <sub>1</sub> = 5.5V                             |        |                  | 1      |     |          | 1      | mA   |

| Ήн              | High-level input current               | V <sub>CC</sub> = MAX,                            | $V_1 = 2.4V$                                      | ļ      |                  | 40     |     |          | 40     | μΑ   |

| IL              | Low-level input current                | V <sub>CC</sub> = MAX,                            | V <sub>1</sub> = 0.4V                             | ŀ      |                  | -1.6   |     |          | -1.6   | mA   |

| os              | Short-circuit output current †         | V <sub>CC</sub> = MAX                             | ·                                                 | -10    |                  | -27.5  | -9  |          | -27.5  | mA   |

| 'cc             | Supply current                         | V <sub>CC</sub> = MAX,<br>See Note                | $V_{1(clock)} = 0.4V$<br>$V_{1(clock)} = 2.4V$    | }      | 3 <b>0</b><br>37 | 54     |     | 30<br>37 | 54     | mA   |

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_{A}$ = 25°C, N = 5

| PARAMETER             |                                  | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|-----------------------|----------------------------------|-----------------------|-----|-----|-----|------|

| f <sub>max</sub>      | Maximum input count frequency    | C <sub>1</sub> = 15pF | 25  | 36  |     | МН   |

| IIIdx                 | Propagation delay time, high-to- | C <sub>L</sub> = 15pF | l   | 24  | 36  | l    |

| tPHL low-level Q or   | low-level Q outputs from clear   |                       |     |     |     | ſr   |

| , , , L               | input                            | C <sub>1</sub> = 50pF |     | 28  | 42  |      |

|                       | Propagation delay time, low-to-  | C <sub>1</sub> = 15pF | 8   | 17  | 27  | 1    |

| <sup>t</sup> PLH      | high-level Q outputs from clock  |                       |     |     |     | r    |

| ren                   | input                            | $C_1 = 50pF$          | 10  | 20  | 30  |      |

| Propagation del       | Propagation delay time, high-to- | C <sub>1</sub> = 15pF | 10  | 21  | 32  | 1    |

| tPHL low-level (input | low-level Q outputs from clock   |                       | f   |     |     | · -  |

|                       | ·                                | C <sub>L</sub> = 50pF | 10  | 25  | 37  | ļ    |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

<sup>\*\*</sup> All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C. † Not more than two outputs should be shorted at a time.

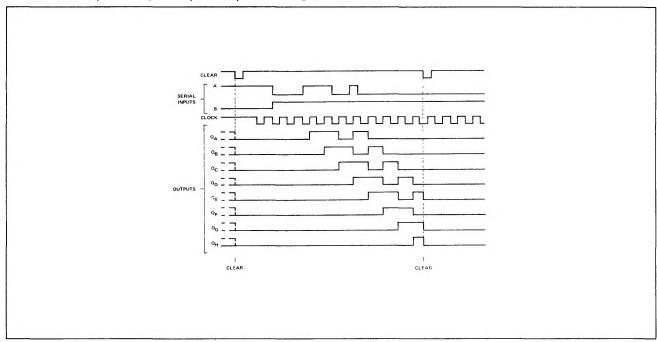

# TYPICAL CLEAR, INHIBIT, SHIFT, CLEAR, AND INHIBIT SEQUENCES

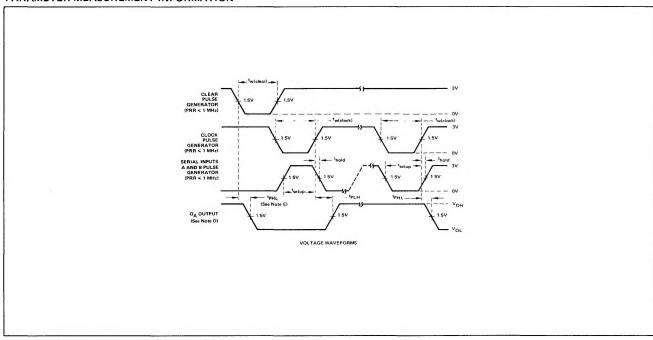

### PARAMETER MEASUREMENT INFORMATION

NOTES:

- A. The pulse generators have the following characteristics:  $t_f \le 10$ ns,  $t_f \le 10$ ns, duty cycle  $\le 50\%$ ,  $Z_{out} \approx 50\Omega$ .

- B. C<sub>L</sub> includes probe and jig capacitance.

C. All diodes are 1N3064.

D. Q<sub>A</sub> output is illustrated. Relationship of serial input A and B data to other Q outputs is illustrated in the typical shift sequence.

- E. Outputs are set to the high level prior to the measurement of  $t_{\mbox{\footnotesize{PHL}}}$  from the clear input.