J-K FLIP-FLOP | \$5470 S5470-A,F,W • N7470-A,F

# DIGITAL 54/74 TTL SERIES

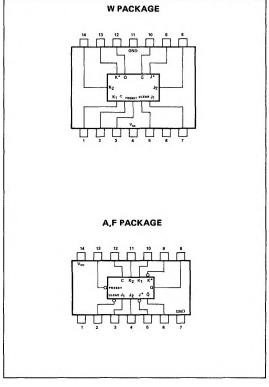

PIN CONFIGURATIONS

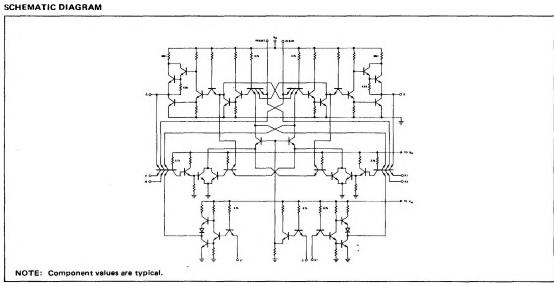

### DESCRIPTION

The S5470/N7470 is a monolithic, edge-triggered J-K flip-flop featuring gated inputs, direct clear and preset inputs, and complementary  ${\bf Q}$  and  $\overline{{\bf Q}}$  outputs. Input information is transferred to the outputs on the positive edge of the clock pulse.

Direct-coupled clock triggering occurs at a specific voltage level of the clock pulse; and after the clock input threshold voltage has been passed, the gated inputs are locked out.

The S5470/N7470 flip-flop is ideally suited for medium- and high-speed applications, and can be used for a significant saving in system power dissipation and package count where input gating is required.

## TRUTH TABLE

| Jn | Kn | $Q_{n+1}$                   | PRESET | CLEAR | Q |

|----|----|-----------------------------|--------|-------|---|

| 0  | 0  | Q <sub>n</sub>              | 0      | 0     | t |

| 1  | 0  | 1                           | 1      | 0     | 0 |

| 0  | 1  | 0                           | 0      | 1     | 1 |

| 1  | 1  | $\overline{\mathbf{Q}}_{n}$ | 1      | 1     | Q |

n is time prior to clock

n+1 is time following clock

f Both outputs in 0 state

### POSITIVE LOGIC

Low input to preset sets Q to logical 1

Low input to clear sets Q to logical 0

Preset or clear function can occur only when clock input is low.

## RECOMMENDED OPERATING CONDITIONS

|                                                                        | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S5470 Circuits                        | 4.5  | 5   | 5.5  | V    |

| N7470 Circuits                                                         | 4.75 | 5   | 5.25 | V    |

| Operating Free-Air Temperature Range, T <sub>A</sub> : S5470 Circuits  | -55  | 25  | 125  | °C   |

| N7470 Circuits                                                         | l    | 25  | 70   | °C   |

| Jormalized Fanout from each Output, N                                  |      |     | 10   |      |

| Clock Pulse Transition Time to Logical 1 Level, t <sub>1</sub> (clock) | 5    |     | 150  | ns   |

| Vidth of Clock Pulse, t., (-1, -1,)                                    | 20   |     |      | ns   |

| width of Preset Pulse, taleanne                                        | 25   |     |      | ns   |

| Vidth of Clear Pulse, tp(clear)                                        | 25   |     |      | ns   |

## ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                    | PARAMETER                                                               | 7                                                | EST CONDITIONS*                                  |                | MIN        | TYP** | MAX        | UNIT     |

|--------------------|-------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------|------------|-------|------------|----------|

| V <sub>in(1)</sub> | Input voltage required<br>to ensure logical 1 at<br>any input terminal  | V <sub>CC</sub> = MIN                            |                                                  |                | 2          |       |            | ٧        |

| V <sub>in(0)</sub> | Input voltage required to ensure logical 0 at any input terminal        | V <sub>CC</sub> = MIN                            |                                                  |                |            |       | 8.0        | V        |

| $V_{out(1)}$       | Logical 1 output voltage                                                | V <sub>CC</sub> = MIN,                           | I <sub>load</sub> = -400µA                       |                | 2.4        | 3.5   |            | v        |

| $V_{out(0)}$       | Logical 0 output voltage                                                | V <sub>CC</sub> = MIN,                           | Isink = 16mA                                     |                |            | 0.22  | 0.4        | \ \      |

| <sup>1</sup> in(0) | Logical O level input<br>current at J1, J2, J*,<br>K1, K2, K*, or clock | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |       | -1.6       | mA       |

| lin(0)             | Logical O level input<br>current at preset or<br>clear                  | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |       | -3.2       | m/       |

| lin(1)             | Logical 1 level input<br>current at J1, J2, J*,<br>K1, K2, K*, or clock | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |       | 40<br>1    | μA<br>mA |

| lin(1)             | Logical 1 level input<br>current at preset or clear                     | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |       | 80<br>1    | μA<br>mA |

| los                | Short circuit output current <sup>†</sup>                               | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0                              | S5470<br>N7470 | -20<br>-18 |       | -75<br>-75 | m#       |

| I <sub>CC</sub>    | Supply current                                                          | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 5V                             |                | 1          | 13    | 26         | mA       |

# SWITCHING CHARACTERISTICS, V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C, N = 10

|                    | PARAMETER                                                                      | 1                      | TEST CONDITIONS       | MIN | TYP | MAX | דומט |

|--------------------|--------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| fclock             | Maximum clock frequency                                                        | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 15  | 35  |     | MHz  |

| t <sub>setup</sub> | Minimum Input Setup time                                                       | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 10  | 20  | ns   |

| <sup>t</sup> hold  | Minimum input hold time                                                        | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 0   | 5   | ns   |

| <sup>t</sup> pd1   | Propagation delay time<br>to logical 1 level from<br>clear or preset to output | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     |     | 50  | ns   |

| <sup>t</sup> pd0   | Propagation delay time<br>to logical 0 level from<br>clear or preset to output | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 1   |     | 50  | ns   |

| <sup>t</sup> pd1   | Propagation delay time<br>to logical 1 level from<br>clock to output           | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 10  | 27  | 50  | ns   |

| <sup>t</sup> pd0   | Propagation delay time<br>to logical 0 level from<br>clock to output           | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 10  | 18  | 50  | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\* All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

† Not more than one output should be shorted at a time.