# DUAL 4-INPUT POSITIVE NAND GATE | \$54H20

N74H20

S54H20-A,F,W • N74H20-A,F

# DIGITAL 54/74 TTL SERIES

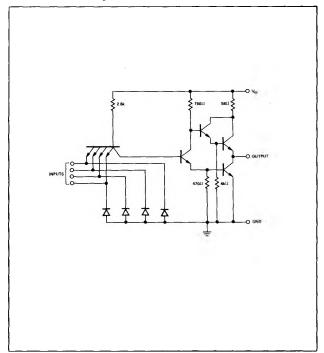

#### SCHEMATIC (each gate)

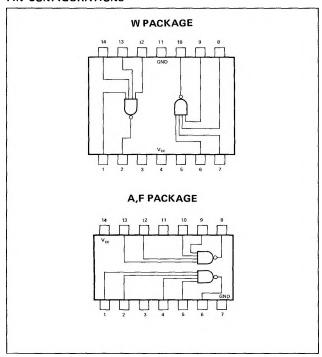

#### PIN CONFIGURATIONS

## **RECOMMENDED OPERATING CONDITIONS**

|                                                                        | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S54H20 Circuits                       | 4.5  | 5   | 5.5  | V    |

| N74H20 Circuits                                                        | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out from each Output, N                                 | 1    |     | 10   |      |

| Operating Free-Air Temperature Range, T <sub>A</sub> : S54H20 Circuits | -55  | 25  | 125  | °c   |

| N74H20 Circuits                                                        | 0    | 25  | 70   | °c   |

|                     | PARAMETER                                                                                   |                                                    | TEST CONDITIONS*                                 |        | TYP** | MAX     | UNIT     |

|---------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|--------|-------|---------|----------|

| V <sub>in(1)</sub>  | Logical 1 input voltage required at all input terminals to ensure logical 0 level at output | V <sub>CC</sub> = MIN                              |                                                  | 2      |       |         | V        |

| V <sub>in(0)</sub>  | Logical 0 input voltage required of any input terminal to ensure logical 1 level at output  | V <sub>CC</sub> = MIN,                             |                                                  | l<br>I |       | 0.8     | \ \ \    |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                                    | $V_{CC} = MIN,$ $I_{load} = -500\mu A$             | V <sub>in</sub> = 0.8V,                          | 2.4    |       |         | V        |

| V <sub>out(0)</sub> | Logical 0 output voltage                                                                    | V <sub>CC</sub> = MIN,<br>I <sub>sink</sub> = 20mA | V <sub>in</sub> = 2V,                            |        |       | 0.4     | \ \      |

| <sup>1</sup> in(0)  | Logical 0 level input current (each input)                                                  | V <sub>CC</sub> = MAX,                             | $V_{in} = 0.4V$                                  |        |       | -2      | mA       |

| <sup>1</sup> in(1)  | Logical 1 level input current (each input)                                                  | $V_{CC} = MAX,$<br>$V_{CC} = MAX,$                 | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |        |       | 50<br>1 | μA<br>mA |

| ¹os                 | Short circuit output current <sup>†</sup>                                                   | V <sub>CC</sub> = MAX,                             |                                                  | -40    |       | -100    | mA       |

| I <sub>CC(0)</sub>  | Logical 0 level supply current                                                              | V <sub>CC</sub> = MAX,                             | V <sub>in</sub> = 4.5V                           |        | 13    | 20      | mA       |

| <sup>1</sup> CC(1)  | Logical 1 level supply current                                                              | V <sub>CC</sub> = MAX,                             | V <sub>in</sub> = 0                              |        | 5     | 8.4     | mA       |

### SIGNETICS DIGITAL 54/74 TTL SERIES - S54H20 • N74H20

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

|                  | PARAMETER                                    | Т                      | EST CONDITIONS        | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| tpd0             | Propagation delay time<br>to logical O level | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω |     | 7   | 10  | ns   |

| <sup>t</sup> pd1 | Propagation delay time to logical 1 level    | CL = 25pF,             | R <sub>L</sub> = 280Ω |     | 6   | 10  | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\*\* All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

† Not more than one output should be shorted at a time and duration of short circuit test should not exceed 1 second.