# DUAL D-TYPE EDGE TRIGGERED S54H74 FLIP-FLOP

N74H74

S54H74-A,F,W • N74H74-A,F

DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

These monolithic, high-speed, dual, edge-triggered flip-flops utilize TTL circuitry to perform D-type flip-flop logic. Each flip-flop has individual clear and preset inputs, and also complementary Q and  $\overline{Q}$ outputs.

Information at input D is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D-input signal has no effect.

These circuits are fully compatible for use with most TTL or DTL circuits. Input clamping diodes are provided to minimize transmission line effects and thereby simplify systems design. A full fan-out to 10 normalized Series 54H/74H loads is available from each of the outputs in the low-level condition. In the high-level state, a fan-out of 20 is available to facilitate tying unused inputs to used inputs. Maximum clock frequency is 35 megahertz, with a typical power dissipation of 75 milliwatts per flip-flop.

#### TRUTH TABLE

### LOGIC

| (Each Flip-Flop) |                  |             |  |  |  |  |

|------------------|------------------|-------------|--|--|--|--|

| <sup>t</sup> n   | t <sub>n+1</sub> |             |  |  |  |  |

| Input<br>D       | Output<br>Q      | Output<br>Q |  |  |  |  |

| L                | L                | Н           |  |  |  |  |

| н                | н                | L           |  |  |  |  |

#### NOTES:

- 1.  $t_n = bit time before$ clock pulse

- 2.  $t_{n+1} = bit time af$ ter clock pulse

# H = High Level, L = Low Level

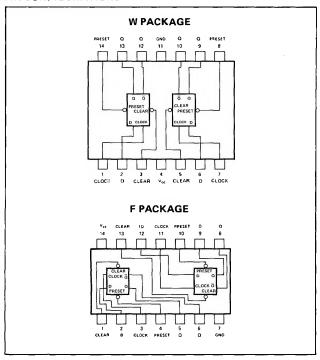

## PIN CONFIGURATIONS

#### **ASYNCHRONOUS INPUTS**

Low input to preset sets Q to high level Low input to clear sets Q to low level Preset and clear are independent of clock

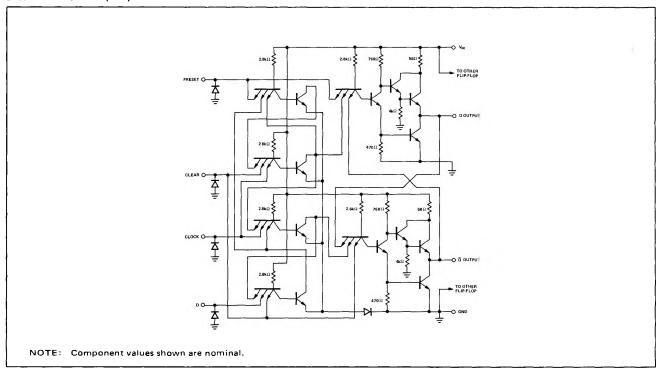

#### SCHEMATIC (each flip-flop)

#### RECOMMENDED OPERATING CONDITIONS

|                                                    |                 | S54H74 |                 |                 | N74H74 |      |      |

|----------------------------------------------------|-----------------|--------|-----------------|-----------------|--------|------|------|

|                                                    | MIN             | NOM    | MAX             | MIN             | NOM    | MAX  | UNIT |

| Supply Voltage V <sub>CC</sub>                     | 4.5             | 5      | 5.5             | 4.75            | 5      | 5.25 | V    |

| Normalized Fan-Out from each Output, N             |                 |        |                 |                 |        |      |      |

| Low Logic Level                                    |                 |        | 10              |                 |        | 10   |      |

| High Logic Level                                   |                 |        | 20              | ļ               |        | 20   | }    |

| Clock Frequency, f <sub>clock</sub>                | 0               |        | 35 <sup>†</sup> | 0               |        | 35   | MHz  |

| Width of Clock Pulse, tw(clock)                    | 15 <sup>†</sup> |        | _               | 15 <sup>†</sup> |        |      | ns   |

| Width of Preset Pulse, tw(preset)                  | 25 <sup>†</sup> |        |                 | 25 <sup>†</sup> |        |      | ns   |

| Width of Clear Pulse, tw(clear)                    | 25 <sup>†</sup> |        | 1               | 25†             |        | ì    | ns   |

| Input Setup Time, t <sub>setup</sub> (See Note 3): |                 |        |                 |                 |        |      | 1    |

| High-level data                                    | 10 <sup>†</sup> | ì      | 1               | 10 <sup>†</sup> |        | 1    | ns   |

| Low-level data                                     | 15 <sup>†</sup> |        |                 | 15 <sup>†</sup> |        |      | ns   |

| Input Hold Time, thold (See Note 4)                | 0               |        |                 | 0               |        | 1    | ns   |

| Operating Free-Air Temperature Range, TA           | -55             | 25     | 125             | 0               | 25     | 70   | °C   |

#### NOTES

- 3. Setup time is the interval immediately preceding the positive-going edge of the clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

- 4. Hold time is the interval immediately following the positive-going edge of the clock pulse during which interval the data to be recognized must be maintained at the input to ensure its continued recognition.

- <sup>†</sup> These conditions are recommended for use at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER       |                                             | TEST CONDITIONS*                                 |                        | MIN | TYP**    | MAX      | UNIT     |

|-----------------|---------------------------------------------|--------------------------------------------------|------------------------|-----|----------|----------|----------|

| VIH             | High-level input voltage                    |                                                  |                        | 2   |          |          | v        |

| $V_{IL}$        | Low-level input voltage                     |                                                  |                        | 1   |          | 0.8      | V        |

| Vон             | High-level output voltage                   | $V_{CC} = MIN,$                                  | I <sub>OH</sub> = -1mA | 2.4 | 3.5      |          | V        |

| VOL             | Low-level output voltage                    | V <sub>CC</sub> = MIN,                           | IOL = 20mA             | 1   | 0.22     | 0.4      | V        |

| Ιн              | High-level input current into D             | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, |                        |     |          | 50<br>1  | μA<br>mA |

|                 | High-level input current                    | V <sub>CC</sub> = MAX,                           |                        | 1   |          | 100      | μΑ       |

| IН              | into preset or clock                        | VCC = MAX,                                       | $V_{1} = 5.5V$         | 1   |          | 1        | mA       |

|                 | High-level input current                    | V <sub>CC</sub> = MAX,                           | $V_1 = 2.4V$           | 1   |          | 150      | μΑ       |

| ΙΗ              | into clear                                  | $V_{CC} = MAX$                                   | V <sub>I</sub> = 5.5V  | 1   |          | 1        | mA       |

| l <sub>IL</sub> | Low-level input current into preset or D    | V <sub>CC</sub> = MAX,                           | V <sub>1</sub> = 0.4V  |     |          | -2       | mA       |

| IIL             | Low-level input current into clear or clock | V <sub>CC</sub> = MAX,                           | V <sub>1</sub> = 0.4V  |     |          | -4       | mA       |

| los             | Short circuit output current <sup>†</sup>   | V <sub>CC</sub> = MAX,                           |                        | -40 |          | -100     | mA       |

| cc              | Supply current                              | V <sub>CC</sub> = MAX,                           | S54H74<br>N74H74       |     | 30<br>30 | 42<br>50 | mA       |

## SWITCHING CHARACTERISTICS, $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ , N = 10

|                  | PARAMETER                                                                            | TEST CONDITIONS        |                       | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| f <sub>max</sub> | Maximum clock frequency Propagation delay time, low-to-                              |                        | -                     | 35  | 43  |     | MHz  |

| tPLH             | high-level output, from clear or preset inputs                                       |                        |                       |     |     | 20  | ns   |

| tPHL             | Propagation delay time, high-to-<br>low-level output, from clear or<br>preset inputs | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω |     |     | 30  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-<br>high-level output from clock input                |                        |                       | 4   | 8.5 | 15  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high-to-<br>low-level output, from clock input               |                        |                       | 7   | 13  | 20  | ns   |

- \* For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

- \*\* All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

- † Not more than one output should be shorted at a time, and duration of short circuit test should not exceed 1 second.