# ARITHMETIC LOGIC UNITS/FUNCTION GENERATORS

**S54S181** N74S181

## DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

These Schottky-clamped high-speed arithmetic/logic units, functionally identical to the \$54181 and N74181, perform 16 binary arithmetic operations on two 4-bit words with a full look-ahead carry scheme as propagate and generate terms are available at the P and G outputs. Typical performance is 19 nanoseconds add time for a 16-bit word when used with the S54S182 or N74S182 carry look-ahead.

Typical addition times are shown in Table III. The S54S181/ N74S181 can replace the S54181/N74181 in most existing systems for significant performance upgrading as they are functionally and mechanically interchangeable.

The S54S181 and N74S181 will also perform the 16 possible functions on two Boolean variables without the use of external circuitry. The carry circuit is inhibited for logic functions.

The \$54\$181 and N74\$181 will accommodate active-high or active-low data if the pin designations are interpreted as shown below:

Subtraction is accomplished by 1's complement addition where the 1's complement of the subtrahend is generated internally. The resultant output is A-B-1 which requires an end-around or forced carry to provide A -- B.

Mode of operation (arithmetic or logic) is controlled by the mode-control (M) input. Complete functions for active-high and active-low data are shown in Tables I and II.

Typical average power dissipation is 600 milliwatts, or approximately 8 milliwatts per equivalent gate. The S54S181 is characterized for operation over the full military temperature range of -55°C to 125°C; the N74S181 is characterized for operation from 0°C to 70°C.

For additional descriptive information and typical connection schemes, see the S54181/N74181 data sheet

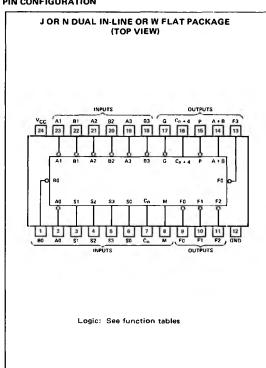

#### PIN CONFIGURATION

#### **FEATURES**

- SIGNIFICANT IMPROVEMENT IN ADD TIMES OVER S54181/N74181

- TYPICAL ADD TIME FOR 16 BITS OF 19 ns USING \$54\$182. N74S182 LOOK-AHEAD

- \$54\$181 IS GUARANTEED FOR OPERATION OVER THE FULL MILITARY TEMPERATURE RANGE OF -55°C TO 125°C

- . FULLY COMPATIBLE WITH MOST TTL FUNCTIONS IN-**CLUDING MSI**

| PIN NUMBER                 | 2              | 1  | 23             | 22             | 21             | 20             | 19             | 18             | 9              | 10             | 11             | 13             | 7                | 16   | 15 | 17 |

|----------------------------|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|------|----|----|

| Active-high data (Table I) | A <sub>0</sub> | В0 | A <sub>1</sub> | В1             | A2_            | В2             | Аз             | Вз             | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | $\overline{c}_n$ | Cn+4 | x  | Υ  |

| Active-low data (Table II) | Ā <sub>0</sub> | Bo | Ā <sub>1</sub> | B <sub>1</sub> | A <sub>2</sub> | B <sub>2</sub> | A <sub>3</sub> | B <sub>3</sub> | Fo             | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | Cn               | Cn+4 | P  | G  |

TABLE I

|       |                  |    |                |                        | ACTIVE-HIGH DATA             |                                           |

|-------|------------------|----|----------------|------------------------|------------------------------|-------------------------------------------|

|       |                  | 4  |                | M = H                  | M = L: ARITHMETIC OF         | PERATIONS                                 |

|       | SELECTION S2 \$1 |    |                | LOGIC                  | C <sub>n</sub> = 0 = H       | C <sub>n</sub> = 1 = L                    |

| $s_3$ |                  |    | s <sub>0</sub> | FUNCTIONS              | (no carry)                   | (with carry)                              |

| L     | L                | L  | L              | F = Ā                  | F = A                        | F = A plus 1                              |

| L     | L                | L  | н              | F = A + B              | F = A + B                    | F = (A + B) plus 1                        |

| L     | L                | iH | L              | F = AB                 | F = A + B                    | $F = (A + \overline{B}) \text{ plus } 1$  |

| L     | L                | н  | н              | F = 0                  | F = minus 1 (2's complement) | F = zero                                  |

| L     | н                | L  | L              | F = AB                 | F = A plus AB                | F = A plus AB plus 1                      |

| L     | н                | L  | н              | F = B                  | F = (A + B) plus AB          | $F = (A + B)$ plus $A\overline{B}$ plus 1 |

| L     | н                | н  | L              | F≃A⊕B                  | F = A minus B minus 1        | F = A minus B                             |

| L     | н                | H  | н              | F = AB                 | F = AB minus 1               | F = AB                                    |

| н     | L                | L  | L              | F = A + B              | F = A plus AB                | F = A plus AB plus 1                      |

| н     | L                | L  | н              | F = A + B              | F = A plus B                 | F = A plus B plus 1                       |

| н     | L                | н  | L              | F = B                  | F = (A + B) plus AB          | $F = (A + \overline{B})$ plus AB plus 1   |

| н     | L                | н  | н              | F = AB                 | F = AB minus 1               | F = AB                                    |

| н     | н                | Ľ  | L              | F = 1                  | F = A plus A*                | F = A plus A plus 1                       |

| н     | н                | L  | н              | $F = A + \overline{B}$ | F = (A + B) plus A           | F = (A + B) plus A plus 1                 |

| н     | н                | н  | L              | F = A + B              | F = (A + B) plus A           | $F = (A + \overline{B})$ plus A plus 1    |

| н     | н                | įΗ | н              | F = A                  | F = A minus 1                | F = A                                     |

<sup>\*</sup>Each bit is shifted to the next more significant position.

TABLE II

|           |                |     |                | L                      | ACTIVE-LOW DATA              |                                          |  |  |

|-----------|----------------|-----|----------------|------------------------|------------------------------|------------------------------------------|--|--|

|           |                |     |                | M = H                  | M = L: ARITHMETIC OF         | PERATIONS                                |  |  |

| SELECTION |                |     |                | LOGIC                  | C <sub>n</sub> = 0 = L       | C <sub>n</sub> = 1 = H                   |  |  |

| $s_3$     | s <sub>2</sub> | \$1 | s <sub>o</sub> | FUNCTIONS              | (no carry)                   | (with carry)                             |  |  |

| L         | L              | L   | L              | F = A                  | F = A minus 1                | F = A                                    |  |  |

| L         | L              | L   | н              | F = AB                 | F = AB minus 1               | F = AB                                   |  |  |

| L         | L              | н   | L              | F = A + B              | F = AB minus 1               | F = AB                                   |  |  |

| L         | L              | н   | н              | F = 1                  | F = minus 1 (2's complement) | F = zero                                 |  |  |

| L         | н              | L   | L              | $F = \overline{A + B}$ | F = A plus (A + B)           | F = A plus (A + B) plus 1                |  |  |

| L         | н              | L   | н              | F = B                  | F = AB plus (A + B)          | F = AB plus (A + B) plus 1               |  |  |

| L         | н              | н   | L              | F = A + B              | F = A minus B minus 1        | F = A minus B                            |  |  |

| L         | н              | :H  | н              | F = A + B              | $F = A + \overline{B}$       | $F = (A + \overline{B}) \text{ plus } 1$ |  |  |

| н         | L              | -L  | L              | F = AB                 | F = A plus (A + B)           | F = A plus (A + B) plus 1                |  |  |

| н         | L              | L   | н              | F = A ⊕ B              | F = A plus B                 | F = A plus B plus 1                      |  |  |

| Н         | L              | H   | L              | F=B                    | F = AB plus (A + B)          | F = AB plus (A + B) plus 1               |  |  |

| н         | L              | įΗ  | н              | F = A + B              | F = A + B                    | F = (A + B) plus 1                       |  |  |

| н         | н              | L   | L              | F = 0                  | F = A plus A *               | F = A plus A plus 1                      |  |  |

| н         | н              | L   | Н              | F = AB                 | F = AB plus A                | F = AB plus A plus 1                     |  |  |

| Н         | н              | ļН  | L              | F = AB                 | F = AB plus A                | F = AB plus A plus 1                     |  |  |

| Н         | н              | н   | н              | F=A                    | F = A                        | F = A plus 1                             |  |  |

<sup>\*</sup>Each bit is shifted to the next more significant position.

### RECOMMENDED OPERATING CONDITIONS

|                                        |                  | S54S181     |   |     |      | N74S181 |      |      |  |

|----------------------------------------|------------------|-------------|---|-----|------|---------|------|------|--|

|                                        |                  | MIN NOM MAX |   | MAX | MIN  | NOM     | MAX  | UNIT |  |

| Supply voltage, VCC                    |                  | 4.5         | 5 | 5.5 | 4.75 | 5       | 5.25 | v    |  |

|                                        | High logic level |             |   | 20  |      |         | 20   |      |  |

| Normalized fan-out from each output, N | Low logic level  |             |   | 10  |      |         | 10   | 1    |  |

| Operating free-air temperature, TA     |                  | -55         |   | 125 | 0    |         | 70   | °c   |  |

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|          | PARAMETER                                             | TE                                                 | ST CONDITION                                      | IS*                     | MIN        | TYP** | MAX  | UNIT     |       |

|----------|-------------------------------------------------------|----------------------------------------------------|---------------------------------------------------|-------------------------|------------|-------|------|----------|-------|

| $v_{IH}$ | High-level input voltage                              |                                                    |                                                   |                         |            | 2     |      |          | v     |

| VIL      | Low-level input voltage                               | •                                                  |                                                   |                         |            |       |      | 0.8      | v     |

| VI       | Input clamp voltage                                   | VCC = MIN,                                         | I <sub>I</sub> = −18 mA                           |                         |            |       | -1.2 | V        |       |

|          | High-level output voltage,                            | V <sub>CC</sub> = MIN,                             | V <sub>IH</sub> = 2 V,                            | N54S181                 | 2,5        | 3.4   |      | v        |       |

| νон      | any output except A = B                               | V <sub>IL</sub> = 0.8 V,                           | 1 <sub>OH</sub> = -1 mA                           | S74S181                 | 2.7        | 3.4   |      | ľ        |       |

| ГОН      | High-level output current, A = E                      | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>V <sub>OH</sub> = 5.5 V |                         |            |       | 250  | μА       |       |

| · · ·    | 1 1                                                   | V <sub>CC</sub> = MIN,                             |                                                   |                         |            |       |      | v        |       |

| VOL      | Low-level output voltage                              |                                                    | V <sub>IL</sub> = 0.8 V,                          | I <sub>OL</sub> = 20 mA |            |       |      | 0.5      | \ \   |

| lj.      | Input current at maximum input voltage                |                                                    | V <sub>CC</sub> = MAX,                            | V <sub>I</sub> = 5.5 V  |            |       |      | 1        | mA    |

|          | High-level input current                              | mode input                                         |                                                   | V <sub>I</sub> = 2.4 V  |            |       |      | 50       |       |

| чн       |                                                       | any A or B input                                   | V <sub>CC</sub> = MAX,                            |                         |            |       |      | 150      | μΑ    |

| чн       |                                                       | any S input                                        |                                                   |                         |            |       |      | 200      | μΑ    |

|          |                                                       | carry input                                        |                                                   |                         |            |       | 250  | <u> </u> |       |

|          | ·                                                     | mode input                                         |                                                   | •                       |            |       |      | -2       |       |

| HL       | Low-level input current                               | any A or B input                                   | ] <sub>V</sub> - MAY                              | V <sub>1</sub> = 0.4 V  |            |       |      | -6       | mA    |

| 'IL      | Low-level input current                               | any S input                                        | VCC - WAA,                                        | V1 - 0.4 V              |            |       |      | -8       | ] ""~ |

|          |                                                       | carry input                                        |                                                   |                         |            |       |      | -10      |       |

| Ios      | Short-circuit output current, any output except A = B |                                                    | V <sub>CC</sub> = MAX                             |                         |            | -40   |      | -100     | mA    |

|          |                                                       |                                                    | V <sub>CC</sub> = MAX,                            | T <sub>A</sub> = 125°C  | N54S181    |       |      | 135      |       |

| laa      | Supply current                                        |                                                    | See Note 1                                        |                         | N pkg only |       |      | 135      |       |

| Icc      | Supply cultent                                        |                                                    | V <sub>CC</sub> = MAX,                            | See Ness 1              | N54S181    |       | 120  | 160      | mA    |

|          |                                                       |                                                    | VCC - WAA,                                        | Sec Mote 1              | S74S181    |       | 120  | 220      | 1     |

<sup>\*</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\*\*All typical values are at  $V_{\rm CC}$  = 5 V,  $T_{\rm A}$  = 25°C.

‡Not more than one output should be shorted at a time.

NOTE 1: I<sub>CC</sub> is measured for the following conditions:

- a. S<sub>0</sub> through S<sub>3</sub>, M, and A inputs are at 4.5 V, all other inputs are grounded, and all outputs are open. b. S<sub>0</sub> through S<sub>3</sub> and M are at 4.5 V, all other inputs are grounded, and all outputs are open.

SWITCHING CHARACTERISTICS, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C, N = 10 (C<sub>L</sub> = 15 pF, R<sub>L</sub> = 280  $\Omega$ , see note 2)

| PARAMETER        | FROM (INPUT)   | TO (OUTPUT) | TEST CONDITIONS                               | MIN TYP | MAX  | UNIT  |

|------------------|----------------|-------------|-----------------------------------------------|---------|------|-------|

| 1PLH             | C <sub>n</sub> | Cn+4        |                                               | 7       | 10.5 | ns    |

| tPHL             | 911            | On+4        |                                               | 7       | 10.5 | 1 ""  |

| tPLH .           | Any A or B     | Cn+4        | M = 0 V, S0 = S3 · 4.5 V,                     | 12.5    | 18.5 | ns    |

| <sup>†</sup> PHL | Any A or B     | On+4        | S1 = S2 = 0 V (SUM mode)                      | 12.5    | 18.5 | 1 ""  |

| †PLH             | Any A or B     | Cn+4        | 15.5                                          | 23      | ns   |       |

| tPHL             |                | On44        | S1 = S2 = 4.5 V (DIFF mode)                   | 15.5    | 23   | 1 "   |

| tPLH             | Cn             | Any F       | M = 0 V                                       |         |      | ns    |

| tPHL .           |                | y .         | (SUM or DIFF mode)                            | 7       | 12   |       |

| tPLH             | Anv A or B     | G           | M = 0 V, S0 = S3 = 4.5 V,                     | 8       | 12   | ns    |

| tPHL             | Ally A OI U    |             | S1 = S2 = 0 V (SUM Mode)                      | 7.5     | 12   | 1 ''' |

| tPLH             | Any A or B     | G           | M = 0 V, S0 = S3 = 0 V,                       | 10.5    | 15   | ns    |

| †PHL             |                |             | S1 = S2 = 4.5 V (DIFF mode)                   | 10.5    | 15   | 1 ''' |

| tPLH             | Any A or B     | P           | M = 0 V, S0 = S3 = 4.5 V,                     | 7.5     | 12   | ns    |

| tPHL .           |                |             | S1 = S2 = 0 V (SUM mode)                      | 7.5     | 12   | ] ''' |

| tPLH .           | Any A or B     | P           | M = 0 V, S0 = S3 = 0 V,                       | 10.5    | 15   | ns    |

| tPHL             | ,              |             | S1 = S2 = 4.5 V (DIFF mode)                   | 10.5    | 15   | 1 "   |

| tPLH .           | Any A or B     | Any F       | <ul> <li>M = 0 V, S0 = S3 = 4.5 V,</li> </ul> | 11      | 16.5 | ns    |

| tPHL             |                |             | S1 = S2 = 0 V (SUM mode)                      | 11      | 16.5 |       |

| 1PLH             | H Any A or 8   | Anv F       | M = 0 V, S0 = S3 = 0 V,                       | 14      | 20   | ns    |

| tPHL .           |                | 100         | S1 = S2 = 4.5 V (DIFF mode)                   | 14      | 22   | 1     |

| <b>TPLH</b>      | Any A or B     | Any F       | M = 4.5 V (logic mode)                        | 14      | 20   | ns    |

| †PHL             | , .,           |             | M = 0 V, S0 = S3 = 0 V.                       | 14      | 22   |       |

| tPLH .           | Any A or B     | A = 8       | 15                                            | 23      | ns   |       |

| tPHL .           | ,              |             | \$1 = \$2 = 4.5 V (DIFF mode)                 | 20      | 30   |       |

Type propagation dalay time, low to high-level output type, a propagation dalay time, low to high-level output NOTE 2: 1 and circuits and waveforms are shown on p. 2 293.

Typical addition times for versus configurations are given in the table below. Subtraction times are typically 3 nerospoonds longer than summation times. For typical look-sheed configurations, see the SS4181/N74181 detection times.

TABLE III

TYPICAL ADDITION TIMES

|    |          |                |                | T. CHE HEE    |             |                  |                 |

|----|----------|----------------|----------------|---------------|-------------|------------------|-----------------|

| 1  | NUMBER   |                | ADDITION TIME  | s             | PACE        | AGE COUNT        | CARRY METHOD    |

| OF |          | USING \$546181 | USING \$545181 | USING \$54181 | ARITHMETIC/ | LOOK AHEAD       | BETWEEN         |

|    | BITS     | AND \$64\$182  | AND \$64182    | AND \$54182   | LOGIC UNITS | CARRY GENERATORS | ALU's           |

|    | 1 to 4   | 11 ns          | )1 ns          | 24 ns         | 1           |                  | NONE            |

|    | 5 to 8   | 18 ns          | 18 ns          | 36 ns         | 2           |                  | RIPPLE          |

|    | 9 to 16  | 19 ns          | 24 ns          | 36 ns         | 3 01 4      | 1 =              | FULL LOOK-AHEAD |

|    | 17 to 64 | 28 ns          | 45 ns          | 60 ns         | 5 to 16     | 2 to 5           | FULL LOOK AHEAD |