# SM320VC5510A-EP Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SGUS045A August 2003 – Revised November 2003

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated

# Contents

| Se | ction   |                      |                                                             | Page |

|----|---------|----------------------|-------------------------------------------------------------|------|

| 1  | Featur  | es                   |                                                             | . 1  |

| 2  | Introdu | iction               |                                                             | . 2  |

|    | 2.1     | Descriptio           | n                                                           | . 2  |

|    | 2.2     |                      | nments                                                      |      |

|    | 2.3     | •                    | scriptions                                                  |      |

| 3  |         | •                    | view                                                        |      |

| 3  | 3.1     |                      | view                                                        |      |

|    | 3.1     | ,                    |                                                             |      |

|    |         | 3.1.1                | On-Chip Dual-Access RAM (DARAM)                             |      |

|    |         | 3.1.2                | On-Chip Single-Access RAM (SARAM)                           |      |

|    |         | 3.1.3                | On-Chip ROM                                                 |      |

|    |         | 3.1.4                | Instruction Cache                                           |      |

|    |         | 3.1.5                | Memory Map                                                  |      |

|    |         | 3.1.6                | Bootloader                                                  | 15   |

|    | 3.2     | Periphera            | ls                                                          | 16   |

|    |         | 3.2.1                | System Register (SYSR)                                      | 17   |

|    |         | 3.2.2                | Direct Memory Access (DMA)                                  | 18   |

|    |         | 3.2.3                | Enhanced Host Port Interface (EHPI)                         | 19   |

|    |         | 3.2.4                | General-Purpose Input/Output Port (GPIO)                    |      |

|    | 3.3     | CPU Regi             | ister Description                                           |      |

|    | 3.4     | •                    | I Register Description                                      |      |

|    | 3.5     |                      |                                                             |      |

|    | 0.0     | 3.5.1                | IFR and IER Registers                                       |      |

|    |         | 3.5.2                | Interrupt Timing                                            |      |

|    | 2.6     |                      | ·                                                           |      |

|    | 3.6     |                      | oncerning CLKOUT Operation                                  |      |

|    |         | 3.6.1                | CLKOUT Voltage Level                                        |      |

|    | _       | 3.6.2                | CLKOUT Value During Reset                                   |      |

| 4  |         |                      | Support                                                     |      |

|    | 4.1     |                      | d Development-Support Tool Nomenclature                     |      |

|    | 4.2     |                      | 10 Device Nomenclature                                      |      |

| 5  | Electri | cal Specifi          | ications                                                    | 38   |

|    | 5.1     | Absolute I           | Maximum Ratings                                             | 38   |

|    | 5.2     | Recomme              | ended Operating Conditions                                  | 38   |

|    | 5.3     | Electrical           | Characteristics Over Recommended Operating Case Temperature |      |

|    |         | Range (U             | nless Otherwise Noted)                                      | 39   |

|    | 5.4     | Package <sup>-</sup> | Thermal Resistance Characteristics                          | 40   |

|    | 5.5     | Timing Pa            | rameter Symbology                                           | 41   |

|    | 5.6     | Clock Opt            | ions                                                        | 42   |

|    |         | 5.6.1                | Clock Generation in Bypass Mode (DPLL Disabled)             | 42   |

|    |         | 5.6.2                | Clock Generation in Lock Mode (DPLL Synthesis Enabled)      | 43   |

|    | 5.7     |                      | iming                                                       |      |

|    |         | 5.7.1                | Asynchronous Memory Timing                                  |      |

|    |         | 5.7.2                | Synchronous-Burst SRAM (SBSRAM) Timing                      |      |

|    |         | 5.7.3                | Synchronous DRAM (SDRAM) Timing                             |      |

|    | E 0     |                      | · · · · · · · · · · · · · · · · · · ·                       |      |

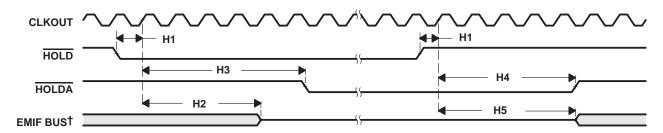

|    | 5.8     |                      | d HOLDA Timings                                             |      |

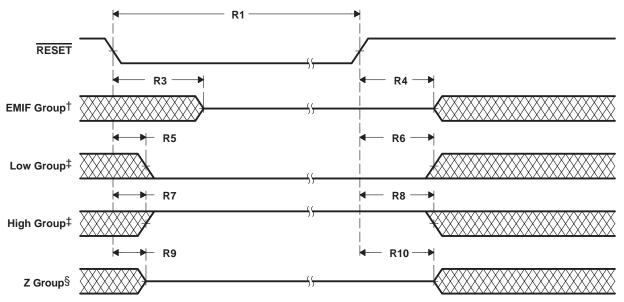

|    | 5.9     |                      | nings Tinings                                               |      |

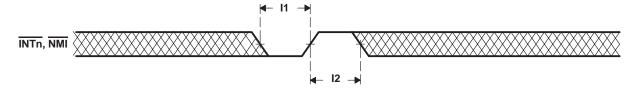

|    | 5.10    | External li          | nterrupt Timings                                            | 55   |

#### Contents

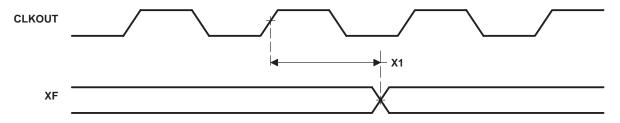

|   | 5.11  | XF Timino  | gs                                       | . 55 |

|---|-------|------------|------------------------------------------|------|

|   |       | •          | Purpose Input/Output (IOx) Timings       |      |

|   | 5.13  | TIN/TOU    | T Timings                                | . 57 |

|   | 5.14  | Multichan  | nel Buffered Serial Port (McBSP) Timings | . 58 |

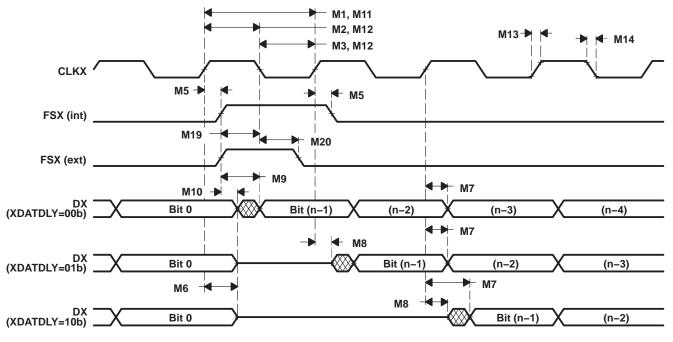

|   |       | 5.14.1     | McBSP Transmit and Receive Timings       | . 58 |

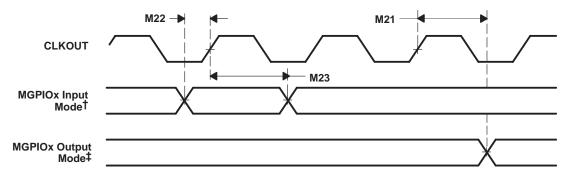

|   |       | 5.14.2     | McBSP General-Purpose I/O Timing         | . 61 |

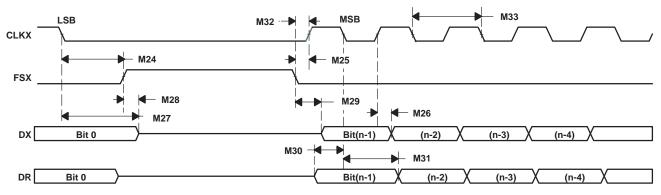

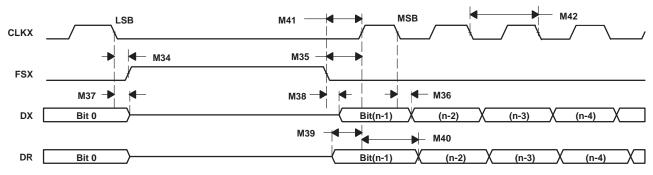

|   |       | 5.14.3     | McBSP as SPI Master or Slave Timing      | . 62 |

|   | 5.15  | Enhanced   | d Host-Port Interface (EHPI) Timing      | . 66 |

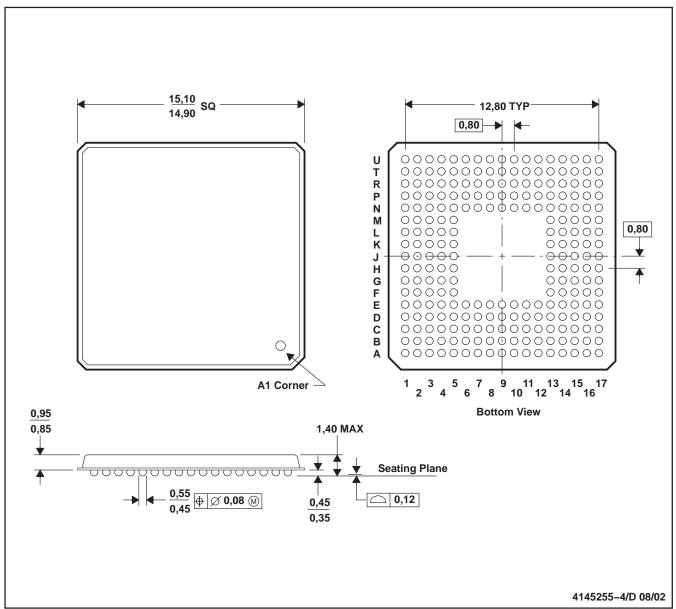

| 6 | Mecha | nical Data | l                                        | . 72 |

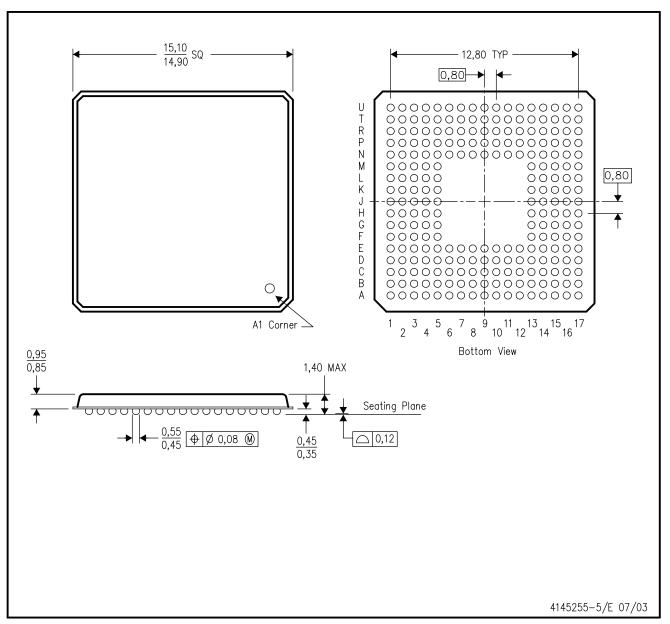

|   | 6.1   | Ball Grid  | Array (GGW) Package Mechanical Data      | . 72 |

# **List of Figures**

| Figure                                                                               | Page |

|--------------------------------------------------------------------------------------|------|

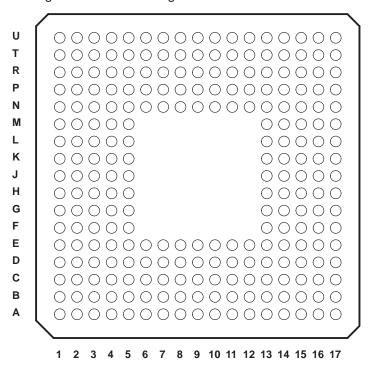

| 2–1. 320VC5510 GGW MicroStar BGAE Package (Bottom View)                              | 3    |

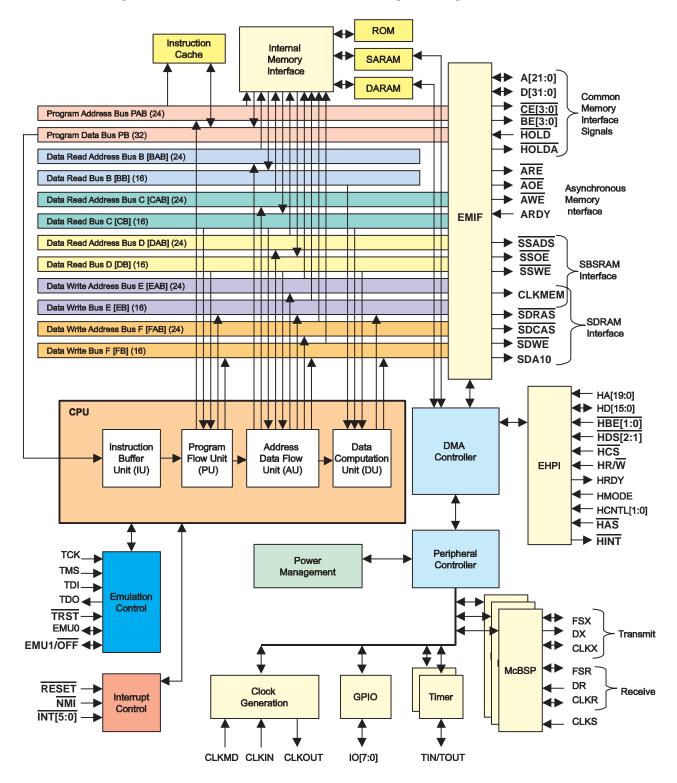

| 3–1. 320VC5510 Functional Block Diagram                                              | 12   |

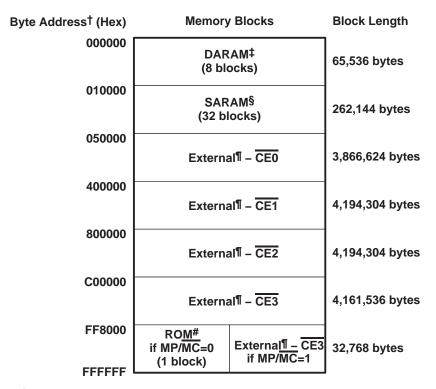

| 3–2. 320VC5510 Memory Map                                                            | 15   |

| 3–3. System Register (SYSR) Bit Layout                                               | 17   |

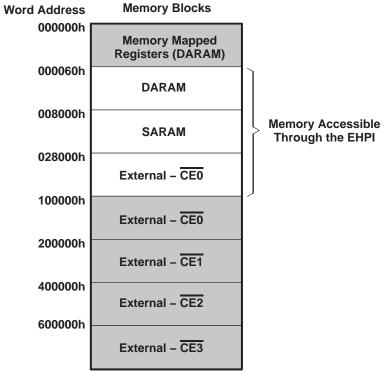

| 3–4. EHPI Memory Map                                                                 | 19   |

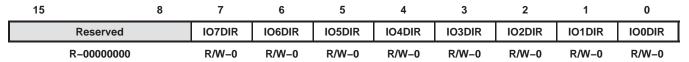

| 3–5. I/O Direction Register (IODIR) Bit Layout                                       | 20   |

| 3–6. I/O Data Register (IODATA) Bit Layout                                           | 20   |

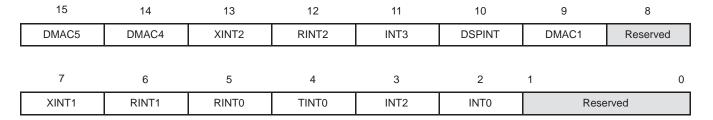

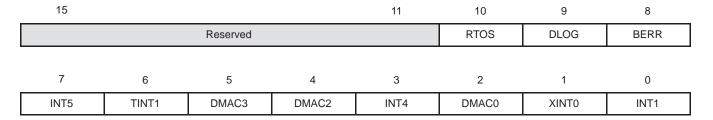

| 3-7. IFR0, IER0, DBIFR0, and DBIER0 Bit Locations                                    | 34   |

| 3-8. IFR1, IER1, DBIFR1, and DBIER1 Bit Locations                                    | 34   |

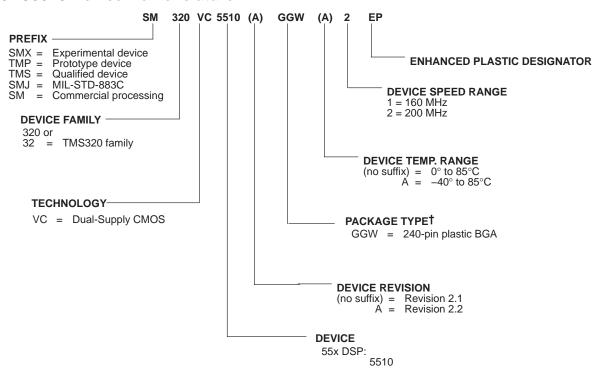

| 4–1. Device Nomenclature for the 320VC5510                                           |      |

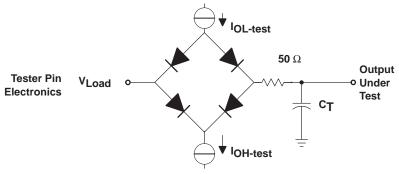

| 5–1. 3.3-V Test Load Circuit                                                         | 40   |

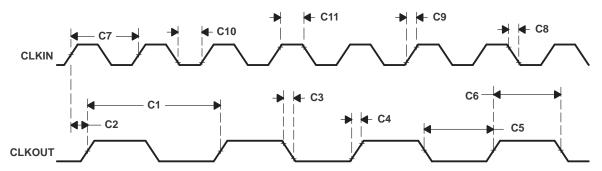

| 5–2. Bypass Mode Clock Timing                                                        | 42   |

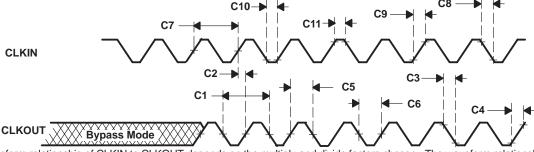

| 5–3. External Multiply-by-N Clock Timing                                             | 43   |

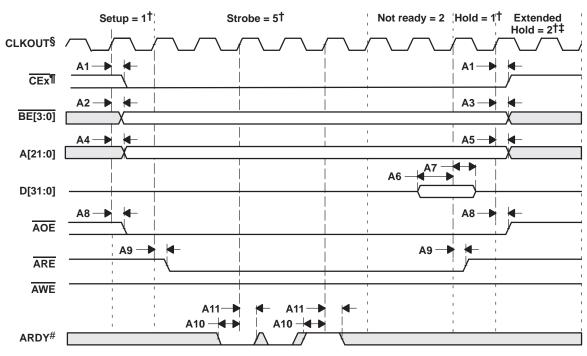

| 5–4. Asynchronous Memory Read Timing                                                 | 45   |

| 5–5. Asynchronous Memory Write Timing                                                | 46   |

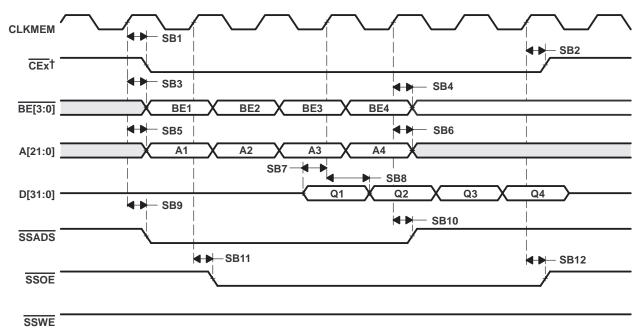

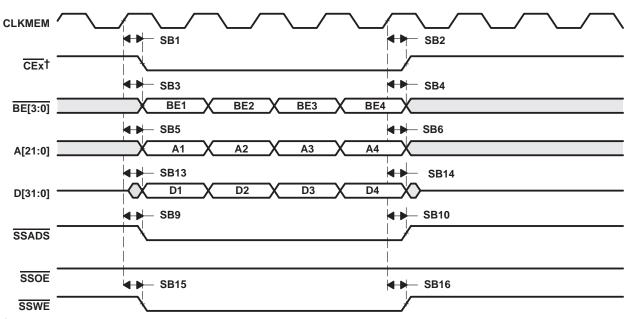

| 5–6. SBSRAM Read Timing                                                              | 48   |

| 5–7. SBSRAM Write Timing                                                             | 48   |

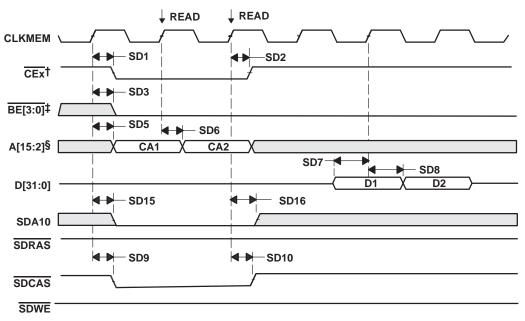

| 5–8. Two SDRAM Read Commands (Active Row)                                            | 50   |

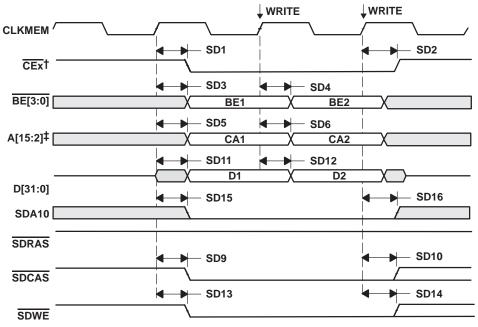

| 5–9. Two SDRAM WRT Commands (Active Row)                                             |      |

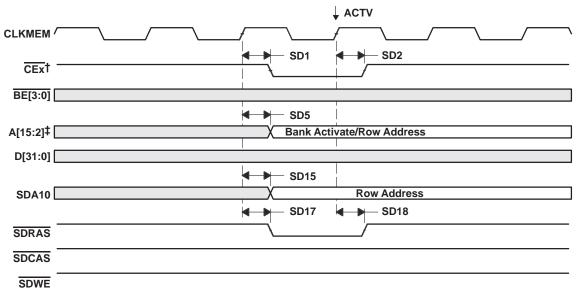

| 5–10. SDRAM ACTV Command                                                             |      |

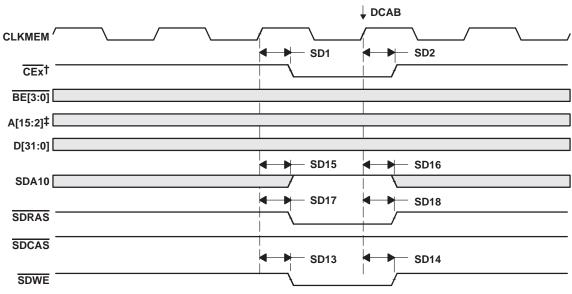

| 5–11. SDRAM DCAB Command                                                             | 51   |

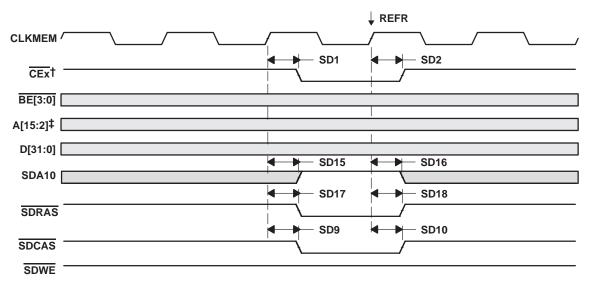

| 5–12. SDRAM REFR Command                                                             |      |

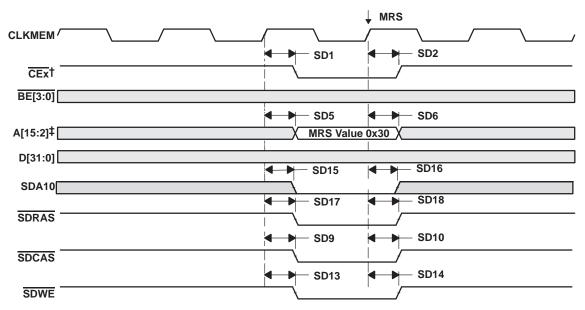

| 5–13. SDRAM MRS Command                                                              | 52   |

| 5–14. HOLD/HOLDA Timing                                                              | 53   |

| 5–15. Reset Timing                                                                   | 54   |

| 5–16. External Interrupt Timing                                                      | 55   |

| 5–17. XF Timing                                                                      |      |

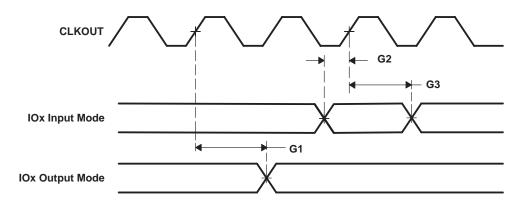

| 5–18. General-Purpose Input/Output (IOx) Signal Timings                              |      |

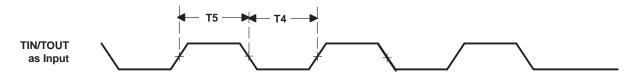

| 5–19. TIN/TOUT Timing When Configured as Inputs                                      |      |

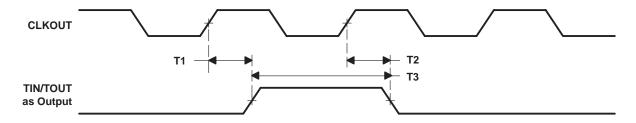

| 5–20. TIN/TOUT Timing When Configured as Outputs                                     |      |

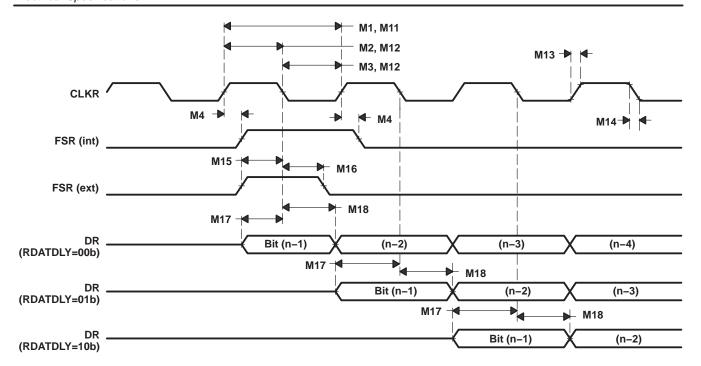

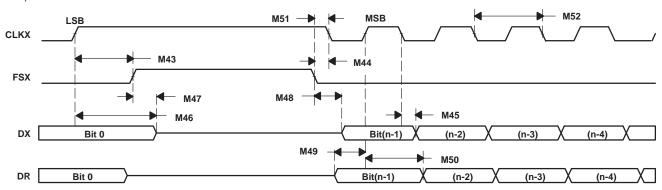

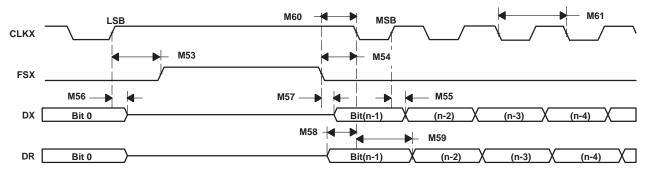

| 5–21. McBSP Receive Timings                                                          |      |

| 5–22. McBSP Transmit Timings                                                         |      |

| 5–23. McBSP General-Purpose I/O Timings                                              |      |

| 5–24. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0                   |      |

| 5–25. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0                   |      |

| 5–26. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1                   |      |

| 5–27. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1                   |      |

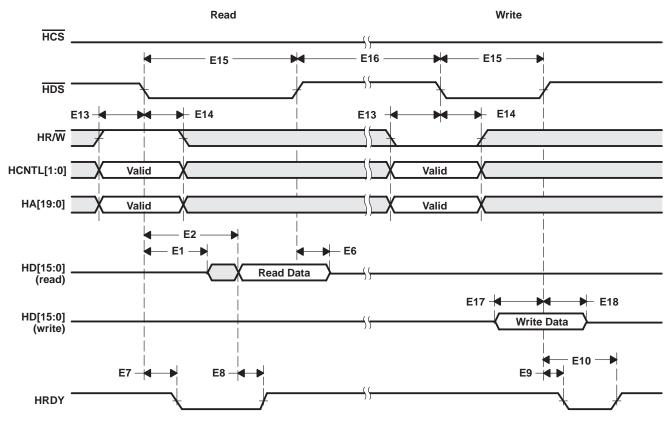

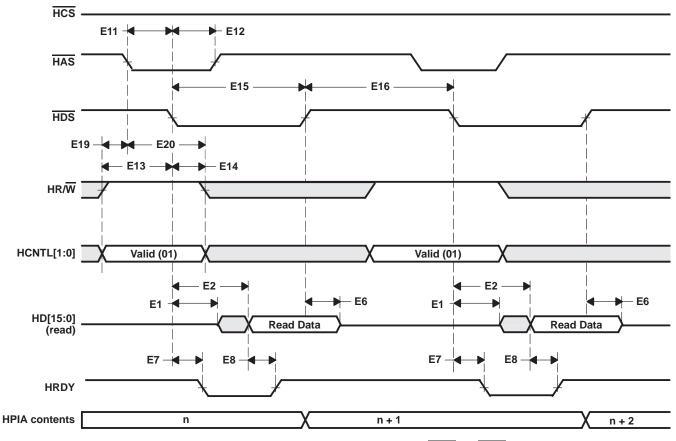

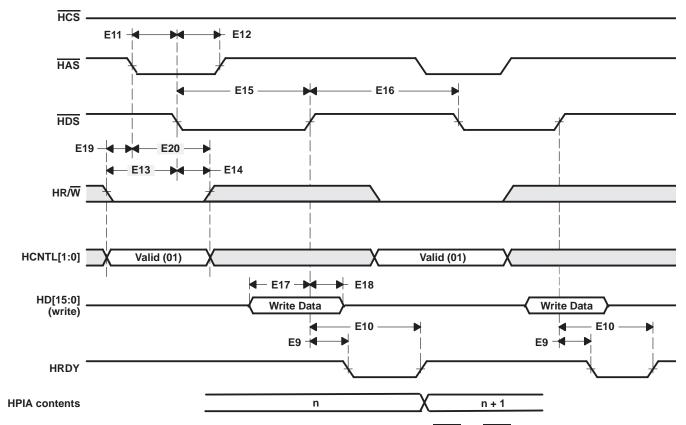

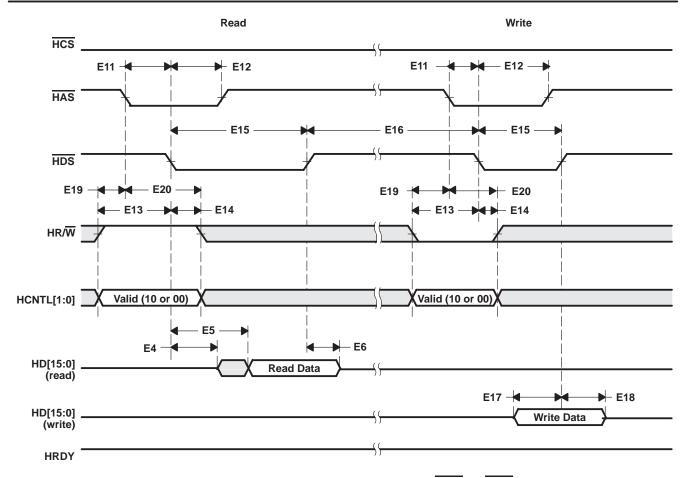

| 5–28. EHPI Nonmultiplexed Read/Write Timings                                         |      |

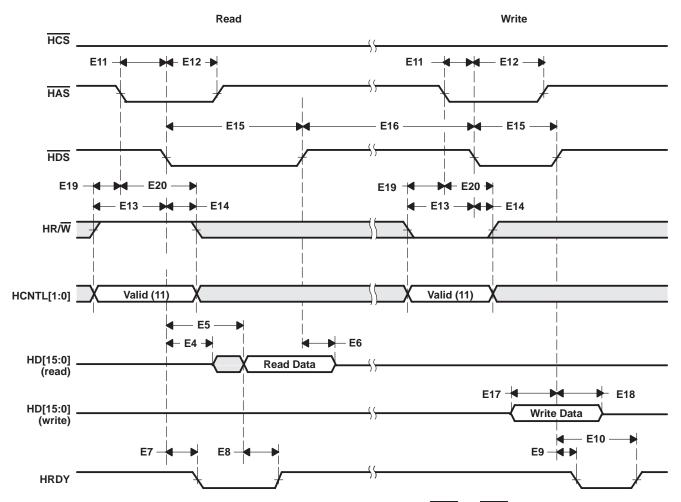

| 5–29. EHPI Multiplexed Memory (HPID) Access Read/Write Timings Without Autoincrement |      |

| 5–30. EHPI Multiplexed Memory (HPID) Access Read Timings With Autoincrement          | 69   |

#### Figures

| 5–31. | EHPI Multiplexed Memory (HPID) Access Write Timings With Autoincrement | 70 |

|-------|------------------------------------------------------------------------|----|

| 5–32. | EHPI Multiplexed Register Access Read/Write Timings                    | 71 |

| 6-1 : | 320VC5510 240-Ball MicroStar BGAE Plastic Ball Grid Array Package      | 72 |

## **List of Tables**

| Table |                                                                                                                                                | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2–1.  | Pin Assignments                                                                                                                                | . 4  |

| 2–2.  | Signal Descriptions                                                                                                                            | . 6  |

| 3–1.  | DARAM Blocks                                                                                                                                   | . 13 |

| 3–2.  | SARAM Blocks                                                                                                                                   | . 13 |

| 3–3.  | Standard On-Chip ROM Contents                                                                                                                  | . 14 |

| 3–4.  | 320VC5510 Boot Configurations                                                                                                                  | . 16 |

|       | System Register (SYSR) Bit Functions                                                                                                           |      |

|       | DMA Sync Events                                                                                                                                |      |

|       | I/O Direction Register (IODIR) Bit Functions                                                                                                   |      |

|       | I/O Data Register (IODATA) Bit Functions                                                                                                       |      |

|       | CPU Registers                                                                                                                                  |      |

|       | Peripheral Bus Controller Configuration Registers                                                                                              |      |

|       | Instruction Cache Registers                                                                                                                    |      |

|       | External Memory Interface Registers                                                                                                            |      |

|       | DMA Configuration Registers                                                                                                                    |      |

|       | Clock Generator Registers                                                                                                                      |      |

|       | Timer Registers                                                                                                                                |      |

|       | Multichannel Serial Port #1 Registers                                                                                                          |      |

|       | Multichannel Serial Port #1 Registers                                                                                                          |      |

|       | GPIO Registers                                                                                                                                 |      |

|       | Device Revision ID Registers                                                                                                                   |      |

|       | Interrupt Table                                                                                                                                |      |

|       | Thermal Resistance Characteristics (Ambient)                                                                                                   |      |

|       | Thermal Resistance Characteristics (Case)                                                                                                      |      |

|       | CLKIN in Bypass Mode Timing Requirements                                                                                                       |      |

|       | CLKOUT in Bypass Mode Switching Characteristics                                                                                                |      |

| 5–5.  | CLKIN in Lock Mode Timing Requirements                                                                                                         | . 43 |

| 5–6.  | CLKOUT in Lock Mode Switching Characteristics                                                                                                  | . 43 |

| 5–7.  | Asynchronous Memory Cycles Timing Requirements                                                                                                 | . 44 |

| 5–8.  | Asynchronous Memory Cycles Switching Characteristics                                                                                           | . 44 |

|       | Synchronous-Burst SRAM Cycle Timing Requirements                                                                                               |      |

|       | Synchronous-Burst SRAM Cycle Switching Characteristics                                                                                         |      |

|       | Synchronous DRAM Cycle Timing Requirements                                                                                                     |      |

|       | Synchronous DRAM Cycle Switching Characteristics                                                                                               |      |

|       | HOLD and HOLDA Timing Requirements                                                                                                             |      |

|       | HOLD and HOLDA Switching Characteristics                                                                                                       |      |

|       | Reset Timing Requirements                                                                                                                      |      |

|       | Reset Switching Characteristics                                                                                                                |      |

|       | External Interrupt Timing Requirements                                                                                                         |      |

|       | XF Switching Characteristics                                                                                                                   |      |

|       | General Purpose Input/Output (GPIO) Pins Configured as Inputs Timing Requirements                                                              |      |

|       | General-Purpose Input/Output (GPIO) Pins Configured as Inputs Switching Characteristics TIN/TOUT Pins Configured as Inputs Timing Requirements |      |

|       | TIN/TOUT Pins Configured as Inputs Timing Requirements                                                                                         |      |

|       | McBSP Timing Requirements                                                                                                                      |      |

| J-23. | MicDol Tilling Nequilements                                                                                                                    | . 50 |

#### Tables

| 5–24. | McBSP Switching Characteristics                                                  | 59 |

|-------|----------------------------------------------------------------------------------|----|

| 5–25. | McBSP General-Purpose I/O Timing Requirements                                    | 61 |

| 5–26. | McBSP General-Purpose I/O Switching Characteristics                              | 61 |

| 5–27. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)       | 62 |

| 5–28. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0) | 62 |

| 5–29. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0)       | 63 |

| 5–30. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0) | 63 |

| 5–31. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)       | 64 |

| 5–32. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1) | 64 |

| 5–33. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1)       | 65 |

| 5–34. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1) | 65 |

| 5–35. | EHPI Timing Requirements                                                         | 66 |

| 5-36. | EHPI Switching Characteristics                                                   | 66 |

#### 1 Features

- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of –40°C to 85°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree<sup>†</sup>

- High-Performance, Low-Power, Fixed-Point 320C55x™

Digital Signal Processor (DSP)

- 5-ns Instruction Cycle Time

- 200-MHz Clock Rate

- One/Two Instructions Executed per Cycle

- Dual Multipliers (Up to 400 Million Multiply-Accumulates Per Second (MMACS))

- Two Arithmetic/Logic Units

- One Internal Program Bus

- Three Internal Data/Operand Read Buses

- Two Internal Data/Operand Write Buses

- Instruction Cache (24K Bytes)

- 160K x 16-Bit On-Chip RAM Composed of:

- Eight Blocks of 4K × 16-Bit

Dual-Access RAM (DARAM) (64K Bytes)

- 32 Blocks of 4K × 16-Bit Single-Access RAM (SARAM) (256K Bytes)

- 16K × 16-Bit On-Chip ROM (32K Bytes)

- 8M × 16-Bit Maximum Addressable External Memory Space

- 32-Bit External Memory Interface (EMIF)

With Glueless Interface to:

- Asynchronous Static RAM (SRAM)

- Asynchronous EPROM

- Synchronous DRAM (SDRAM)

- Synchronous Burst SRAM (SBSRAM)

- Programmable Low-Power Control of Six Device Functional Domains

- On-Chip Peripherals

- Two 20-Bit Timers

- Six-Channel Direct Memory Access (DMA) Controller

- Three Multichannel Buffered Serial Ports (McBSPs)

- 16-Bit Parallel Enhanced Host-Port Interface (EHPI)

- Programmable Digital Phase-Locked Loop (DPLL) Clock Generator

- Eight General-Purpose I/O (GPIO) Pins and Dedicated General-Purpose Output (XF)

- On-Chip Scan-Based Emulation Logic

- IEEE Std 1149.1<sup>‡</sup> (JTAG) Boundary Scan Logic

- 240-Terminal MicroStar BGA™ (Ball Grid Array) (GGW Suffix)

- 3.3-V I/O Supply Voltage

- 1.6-V Core Supply Voltage§

TMS320C55x and MicroStar BGA are trademarks of Texas Instruments. Other trademarks are the property of their respective owners.

Some TMX320VC5510 prototype devices may require core supply voltage other than 1.6 V. See the Electrical Specification section of this data manual for more information. See the *TMS320VC5510 Digital Signal Processor Silicon Errata* (literature number SPRZ008) for further clarification and distinguishing markings.

<sup>†</sup> Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

<sup>‡</sup> IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

#### 2 Introduction

This section describes the main features of the 320VC5510 digital signal processor (DSP), lists the pin assignments, and describes the function of each pin. This data manual also provides a detailed description section, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

**NOTE:** This data manual is designed to be used in conjunction with the *TMS320C55x™ DSP Functional Overview* (literature number SPRU312).

#### 2.1 Description

The 320VC5510 (5510) fixed-point digital signal processor (DSP) is based on the TMS320C55x DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on reduction in power dissipation. The CPU supports an internal bus structure composed of one program bus, three data-read buses, two-data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to three data reads and two data writes in a single cycle. In parallel, the DMA controller can perform up to two data transfers per cycle independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the address unit (AU) and data unit (DU) of the C55x CPU.

The C55x™ DSP generation supports a variable byte width instruction set for improved code density. The instruction unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the program unit (PU). The program unit decodes the instructions, directs tasks to AU and DU resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions. The 5510 also includes a 24K-byte instruction cache to minimize external memory accesses, improving data throughput and conserving system power.

The 5510 peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM and synchronous burst SRAM. Three full-duplex multichannel buffered serial ports (McBSPs) provide glueless interface to a variety of industry-standard serial devices, and multichannel communication with up to 128 separately enabled channels. The enhanced host-port interface (EHPI) is a 16-bit parallel interface used to provide host processor access to internal memory on the 5510. The EHPI can be configured in either multiplexed or non-multiplexed mode to provide glueless interface to a wider variety of host processors. The DMA controller provides data movement for six independent channel contexts without CPU intervention, providing DMA throughput of up to two 16-bit words per cycle. Two general-purpose timers, eight general-purpose I/O (GPIO) pins, and digital phase-locked loop (DPLL) clock generation are also included.

The 5510 is supported by the industry's leading eXpressDSP™ software environment including the Code Composer Studio™ integrated development environment, DSP/BIOS™ software kernel foundation, the TMS320™ DSP Algorithm Standard, and the industry's largest third-party network. Code Composer Studio features code generation tools including a C-Compiler, Visual Linker, simulator, Real-Time Data Exchange (RTDX™), XDS510™ emulation device drivers, and Chip Support Libraries (CSL). DSP/BIOS is a scalable real-time software foundation available for no cost to users of Texas Instruments' DSP products providing a preemptive task scheduler and real-time analysis capabilities with very low memory and megahertz overhead. The TMS320 DSP Algorithm Standard is a specification of coding conventions allowing fast integration of algorithms from different teams, sites, or third parties into the application framework. Texas Instruments' extensive DSP third-party network of over 400 providers brings focused competencies and complete solutions to customers.

C55x, eXpressDSP, Code Composer Studio, DSP/BIOS, TMS320, RTDX, and XDS510 are trademarks of Texas Instruments.

Texas Instruments (TI) has also developed foundation software available for the 5510. The C55x DSP Library (DSPLIB) features over 50 C-callable software kernels (FIR/IIR filters, Fast Fourier Transforms (FFTs), and various computational functions). The DSP Image/Video Processing Library (IMGLIB) contains over 20 software kernels highly optimized for C55x DSPs and is compiled with the latest revision of the C55x DSP code generation tools. These imaging functions support a wide range of applications that include compression, video processing, machine vision, and medical imaging.

The TMS320C55x DSP core was created with an open architecture that allows the addition of application-specific hardware to boost performance on specific algorithms. The hardware extensions on the 5510 strike the perfect balance of fixed function performance with programmable flexibility, while achieving low-power consumption, and cost that traditionally has been difficult to find in the video-processor market. The extensions allow the 5510 to deliver exceptional video codec performance with more than half its bandwidth available for performing additional functions such as color space conversion, user-interface operations, security, TCP/IP, voice recognition, and text-to-speech conversion. As a result, a single 5510 DSP can power most portable digital video applications with processing headroom to spare. For more information, see the TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (literature number SPRU098). For more information on using the the DSP Image Processing Library, see the TMS320C55x Image/Video Processing Library Programmer's Reference (literature number SPRU037).

#### 2.2 Pin Assignments

Figure 2–1 illustrates the ball locations for the 240-pin ball grid array (BGA) package and is used in conjunction with Table 2–1 to locate signal names and ball grid numbers.

Figure 2–1. 320VC5510 GGW MicroStar BGA™ Package (Bottom View)

Table 2-1. Pin Assignments

| BGA BALL# | SIGNAL           |

|-----------|------------------|-----------|------------------|-----------|------------------|-----------|------------------|

| A1        | V <sub>SS</sub>  | A2        | A9               | A3        | $DV_DD$          | A4        | A8               |

| A5        | CV <sub>DD</sub> | A6        | A4               | A7        | $DV_DD$          | A8        | D2               |

| A9        | V <sub>SS</sub>  | A10       | Vss              | A11       | SDRAS            | A12       | DV <sub>DD</sub> |

| A13       | SDCAS            | A14       | CV <sub>DD</sub> | A15       | HD10             | A16       | VSS              |

| A17       | Vss              | B1        | VSS              | B2        | XF               | В3        | D9               |

| B4        | D7               | B5        | D5               | В6        | D3               | В7        | A2               |

| B8        | A0               | В9        | CLKMEM           | B10       | SDA10            | B11       | HD2              |

| B12       | SDWE             | B13       | HD1              | B14       | HRDY             | B15       | HD3              |

| B16       | HD0              | B17       | HDS1             | C1        | A10              | C2        | D13              |

| C3        | D10              | C4        | A6               | C5        | A7               | C6        | A5               |

| C7        | A3               | C8        | D0               | C9        | HD4              | C10       | HD5              |

| C11       | HD6              | C12       | HD7              | C13       | HD8              | C14       | HD9              |

| C15       | HR/W             | C16       | HCS              | C17       | TRST             | D1        | DV <sub>DD</sub> |

| D2        | D14              | D3        | D11              | D4        | D8               | D5        | D6               |

| D6        | D4               | D7        | D1               | D8        | A1               | D9        | HD15             |

| D10       | HD14             | D11       | HD13             | D12       | HD12             | D13       | HD11             |

| D14       | HDS2             | D15       | HA11             | D16       | HA0              | D17       | DV <sub>DD</sub> |

| E1        | A11              | E2        | D15              | E3        | D12              | E4        | CE3              |

| E5        | воотмз           | E6        | C∨ <sub>DD</sub> | E7        | CV <sub>DD</sub> | E8        | NC               |

| E9        | NC               | E10       | CV <sub>DD</sub> | E11       | NC               | E12       | NC               |

| E13       | RSVD9            | E14       | HA12             | E15       | HA10             | E16       | HA1/HCNTL1       |

| E17       | RST_MODE         | F1        | DV <sub>DD</sub> | F2        | A13              | F3        | A12              |

| F4        | A16              | F5        | CV <sub>DD</sub> | F13       | RSVD8            | F14       | HA9              |

| F15       | HA2/HAS          | F16       | CLKIN            | F17       | CV <sub>DD</sub> | G1        | CE2              |

| G2        | A17              | G3        | A15              | G4        | A14              | G5        | NC               |

| G13       | RSVD7            | G14       | HA8              | G15       | HA3              | G16       | RESET            |

| G17       | HA13             | H1        | VSS              | H2        | CE1              | H3        | A19              |

| H4        | A18              | H5        | NC               | H13       | RSVD6            | H14       | HA4              |

| H15       | CLKOUT           | H16       | HA14             | H17       | Vss              | J1        | VSS              |

| J2        | CE0              | J3        | A21              | J4        | A20              | J5        | NC               |

| J13       | RSVD5            | J14       | HA5              | J15       | HA15             | J16       | HA7              |

| J17       | Vss              | K1        | 107              | K2        | BE0              | K3        | BE1              |

| K4        | 100              | K5        | CV <sub>DD</sub> | K13       | RSVD4            | K14       | TMS              |

| K15       | HBE0             | K16       | HA16             | K17       | HA6              | L1        | CV <sub>DD</sub> |

| L2        | 106              | L3        | BE2              | L4        | BE3              | L5        | NC               |

| L13       | RSVD3            | L14       | EMU1/OFF         | L15       | TDO              | L16       | TDI              |

| L17       | TCK              | M1        | IO5              | M2        | SSWE             | M3        | SSOE             |

| M4        | IO1/BOOTM0       | M5        | NC               | M13       | RSVD2            | M14       | HA18             |

| M15       | HA17             | M16       | HBE1             | M17       | DVDD             | N1        | DV <sub>DD</sub> |

| N2        | IO4              | N3        | D16              | N4        | SSADS            | N5        | NC               |

| N6        | CV <sub>DD</sub> | N7        | NC               | N8        | NC               | N9        | NC               |

| N10       | CV <sub>DD</sub> | N11       | NC               | N12       | NC               | N13       | RSVD1            |

| N14       | HINT             | N15       | HCNTL0           | N16       | HMODE            | N17       | HA19             |

| P1        | IO3/BOOTM2       | P2        | CLKS1            | P3        | DR1              | P4        | D19              |

| P5        | D22              | P6        | D23              | P7        | D24              | P8        | CLKS2            |

| P9        | FSX0             | P10       | D31              | P11       | D28              | P12       | INT4             |

| P13       | ARDY             | P14       | HOLDA            | P15       | TIN/TOUT0        | P16       | CLKMD            |

Table 2-1. Pin Assignments (Continued)

| BGA BALL# | SIGNAL           | BGA BALL# | SIGNAL           | BGA BALL# | SIGNAL           | BGA BALL# | SIGNAL          |

|-----------|------------------|-----------|------------------|-----------|------------------|-----------|-----------------|

| P17       | CV <sub>DD</sub> | R1        | C∨ <sub>DD</sub> | R2        | FSR1             | R3        | D18             |

| R4        | D20              | R5        | CLKR2            | R6        | FSR2             | R7        | DR2             |

| R8        | D26              | R9        | FSX2             | R10       | DX0              | R11       | ĪNT5            |

| R12       | INT0             | R13       | INT2             | R14       | ARE              | R15       | CLKX1           |

| R16       | EMU0             | R17       | TIN/TOUT1        | T1        | D17              | T2        | IO2/BOOTM1      |

| T3        | CLKR1            | T4        | D21              | T5        | FSR0             | T6        | DR0             |

| T7        | D25              | T8        | D27              | T9        | D29              | T10       | D30             |

| T11       | NC               | T12       | NMI              | T13       | AWE              | T14       | INT3            |

| T15       | FSX1             | T16       | DX1              | T17       | V <sub>SS</sub>  | U1        | V <sub>SS</sub> |

| U2        | VSS              | U3        | CLKR0            | U4        | CV <sub>DD</sub> | U5        | CLKS0           |

| U6        | $DV_DD$          | U7        | CLKX0            | U8        | CLKX2            | U9        | V <sub>SS</sub> |

| U10       | VSS              | U11       | DX2              | U12       | CV <sub>DD</sub> | U13       | INT1            |

| U14       | $DV_DD$          | U15       | AOE              | U16       | HOLD             | U17       | V <sub>SS</sub> |

### 2.3 Signal Descriptions

Table 2–2 lists each signal, function, and operating mode(s) grouped by function. See Section 2.2 for exact pin locations based on package type.

Table 2-2. Signal Descriptions

| SIGNAL<br>NAME           | TYPET              | OTHER‡      | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                          | EMIF - ADDRESS BUS |             |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A[21:0]                  | O/Z                | E,F         | <b>External memory address bus (byte add<u>ress).</u></b> Address all external memory (program and data). Since A[23:22] are redundant to the CE[3:0] memory space selects in terms of memory addressing capability, A[23:22] are not externally provided.                                                                     |  |  |  |  |

|                          |                    | EMIF - C    | CONTROL SIGNALS COMMON TO ALL MEMORY TYPES                                                                                                                                                                                                                                                                                     |  |  |  |  |

| CE0<br>CE1<br>CE2<br>CE3 | O/Z                | E,F         | <b>External memory space enables.</b> Select one of four external memory ranges based on the address.                                                                                                                                                                                                                          |  |  |  |  |

| BE0<br>BE1<br>BE2<br>BE3 | O/Z                | E,F         | <b>Byte-enable control.</b> Can be used as chip selects for external memory. These signals respond according to the data width of the memory access. 8-bit accesses cause a single byte enable to respond. 16-bit accesses cause two byte enables to respond. 32-bit accesses cause all four byte enables to respond.          |  |  |  |  |

| CLKMEM                   | O/Z                | E,F         | <b>Memory interface clock (for SDRAM/SBSRAM).</b> Clock for synchronizing the external synchronous memories to the C55x external memory interface.                                                                                                                                                                             |  |  |  |  |

|                          |                    |             | EMIF - DATA BUS                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D[31:0]                  | I/O/Z              | D,E,F       | <b>External data bus.</b> Provides data exchange between external memories and the C55x external memory interface.                                                                                                                                                                                                             |  |  |  |  |

|                          |                    |             | The bus holders on D[31:0] are controlled by the BH bit in the system register (SYSR).                                                                                                                                                                                                                                         |  |  |  |  |

|                          |                    |             | EMIF - BUS ARBITRATION                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| HOLD                     | I                  | -           | <b>Hold request.</b> HOLD is asserted by an external host to request control of the address, data and control signals.                                                                                                                                                                                                         |  |  |  |  |

| HOLDA                    | O/Z                | F           | <b>Hold acknowledge.</b> HOLDA is asserted by the DSP to indicate that the DSP is in the HOLD state and that the EMIF address, data and control signals are in a high-impedance state, allowing the external memory interface to be accessed by other devices.                                                                 |  |  |  |  |

|                          |                    | EMI         | F - ASYNCHRONOUS MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ĀRĒ                      |                    |             | Asynchronous memory read enable. ARE acts as a strobe during asynchronous memory reads only.                                                                                                                                                                                                                                   |  |  |  |  |

| AOE                      | O/Z                | E,F         | Asynchronous memory output enable. $\overline{\sf AOE}$ indicates whether a memory access is a read (low) or a write (high).                                                                                                                                                                                                   |  |  |  |  |

| AWE                      |                    |             | Asynchronous memory write enable. AWE acts as a strobe during asynchronous memory writes only.                                                                                                                                                                                                                                 |  |  |  |  |

| ARDY                     | I                  | nali 7 High | Asynchronous memory ready input. ARDY indicates that an external device is ready for a bus transaction to be completed. If the device is not ready (ARDY is low), the processor extends the memory access by one cycle and checks ARDY again. The ARDY signal is sampled at the end of the STROBE period in the memory access. |  |  |  |  |

$<sup>\</sup>dagger$  I = Input, O = Output, S = Supply, Z = High impedance

K – Internal pulldown enabled by the HPE bit in the system register (SYSR)

<sup>&</sup>lt;sup>‡</sup>Other Pin Characteristics:

A – Internal pullup (always enabled) E – Pin is high impedance in HOLD mode (due to HOLD pin).

B – Internal pulldown (always enabled) F – Pin is high impedance in OFF mode (due to EMU1/OFF pin).

C – Hysteresis input

D – Pin has bus holder

G – Pin can be configured as a general-purpose input.

H – Pln can be configured as a general-purpose output.

$<sup>\</sup>ensuremath{\mathsf{J}}-\ensuremath{\mathsf{Internal}}$  pullup enabled by the HPE bit in the system register (SYSR)

Table 2-2. Signal Descriptions (Continued)

| SIGNAL<br>NAME          | TYPE                                          | OTHER‡  | DESCRIPTION                                                                                                                                               |  |  |  |

|-------------------------|-----------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                         | EMIF - SYNCHRONOUS BURST SRAM CONTROL SIGNALS |         |                                                                                                                                                           |  |  |  |

| SSADS                   |                                               |         | SBSRAM address strobe. SSADS is active (low) during the period of the SBSRAM access when the address is made available to the external memory by the DSP. |  |  |  |

| SSOE                    | O/Z                                           | E,F     | SBSRAM output enable. SSOE is active (low) during read accesses to SBSRAM.                                                                                |  |  |  |

| SSWE                    |                                               |         | SBSRAM write enable. SSWE is active (low) during write accesses to SBSRAM.                                                                                |  |  |  |

|                         |                                               | Е       | MIF - SYNCHRONOUS DRAM CONTROL SIGNALS                                                                                                                    |  |  |  |

| SDRAS                   |                                               |         | SDRAM row address strobe. SDRAS is active (low) during the ACTV, DCAB, REFR, and MRS commands.                                                            |  |  |  |

| SDCAS                   | O/Z                                           | E,F     | SDRAM address column strobe. SDCAS is active (low) during reads, writes, and the REFR and MRS commands.                                                   |  |  |  |

| SDWE                    |                                               | ,       | SDRAM write enable. SDWE is active (low) during writes, and the DCAB and MRS commands.                                                                    |  |  |  |

| SDA10                   |                                               |         | <b>SDRAM A10 address (address/autoprecharge disable).</b> SDA10 is used during reads, writes, and all commands.                                           |  |  |  |

|                         |                                               | MU      | JLTICHANNEL BUFFERED SERIAL PORT SIGNALS                                                                                                                  |  |  |  |

| CLKR0<br>CLKR1<br>CLKR2 | I/O/Z                                         | C,F,G,H | Serial shift clock reference for the receiver                                                                                                             |  |  |  |

| DR0<br>DR1<br>DR2       | I                                             | G       | Serial receive data input                                                                                                                                 |  |  |  |

| FSR0<br>FSR1<br>FSR2    | I/O/Z                                         | F,G,H   | Frame synchronization signal for the receiver                                                                                                             |  |  |  |

| CLKX0<br>CLKX1<br>CLKX2 | I/O/Z                                         | C,F,G,H | Serial shift clock reference for the transmitter                                                                                                          |  |  |  |

| DX0<br>DX1<br>DX2       | O/Z                                           | F,H     | Serial transmit data output                                                                                                                               |  |  |  |

| FSX0<br>FSX1<br>FSX2    | I/O/Z                                         | F,G,H   | Frame synchronization signal for the transmitter                                                                                                          |  |  |  |

| CLKS0<br>CLKS1<br>CLKS2 | 1                                             | G       | External clock source to the sample rate generator                                                                                                        |  |  |  |

<sup>†</sup> I = Input, O = Output, S = Supply, Z = High impedance

A – Internal pullup (always enabled) E – Pin is high impedance in HOLD mode (due to HOLD pin).

B – Internal pulldown (always enabled) F – Pin is high impedance in OFF mode (due to EMU1/OFF pin).

C – Hysteresis input

D – Pin has bus holder

G – Pin can be configured as a general-purpose input.

H – Pln can be configured as a general-purpose output.

J – Internal pullup enabled by the HPE bit in the system register (SYSR) K – Internal pulldown enabled by the HPE bit in the system register (SYSR)

<sup>&</sup>lt;sup>‡</sup> Other Pin Characteristics:

Table 2–2. Signal Descriptions (Continued)

| SIGNAL<br>NAME                                   | TYPE                                | OTHER‡ | THER <sup>‡</sup> DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|--------------------------------------------------|-------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                  | ENHANCED HOST-PORT INTERFACE (EHPI) |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| HA[1 <u>9:3]</u><br>HA2/HAS<br>HA1/HCNTL1<br>HA0 | ı                                   | J      | Host address bus: In non-multiplexed mode (HMODE pin high): HA[19:0] functions as the host address bus only In multiplexed mode (HMODE pin low): HA[19:3] are disabled HA2/HAS functions as HAS (Host Address Strobe). Hosts with multiplexed address and data pins may require HAS to latch the address in the HPIA register. HA1/HCNTL1 functions as HCNTL1 (Host Control Input) and with HCNTL0 determines the type of transaction being performed. |  |  |  |

| HD[15:0]                                         | I/O/Z                               | D,F    | Host data bus. Provides data exchange between the host and C55x EHPI.  The bus holders on HD[15:0] are controlled by the HBH bit in the system register (SYSR).                                                                                                                                                                                                                                                                                        |  |  |  |

| HCS                                              | ı                                   | J      | Host chip select. HCS is the select input for the EHPI and must be driven low during accesses. If the EHPI is not used, HCS must be driven high.                                                                                                                                                                                                                                                                                                       |  |  |  |

| HA2/HAS                                          | I                                   | J      | Host address strobe. Operates as HAS when HMODE is low (multiplexed mode). Hosts with multiplexed address and data pins may require HAS to latch the address in the HPIA register.                                                                                                                                                                                                                                                                     |  |  |  |

| HR/W                                             | I                                   | J      | Host read or write select. Controls the direction of the EHPI transfer.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| HDS1<br>HDS2                                     | -                                   | J      | Host data strobes. HDS1 and HDS2 are driven by the host read and write strobes to control data transfers.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HRDY                                             | O/Z                                 | F,J    | Host ready (from DSP to host). HRDY informs the host when the EHPI is ready for the next transfer.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HBE0                                             |                                     |        | EHPI byte enables. HBE0 and HBE1 are driven low selectively by the host to indicate whether the transaction involves the lower byte only, the upper byte only, or both.                                                                                                                                                                                                                                                                                |  |  |  |

| HBE1                                             |                                     | К      | As of revision 2.1, the byte-enable function on the EHPI will no longer be supported. These pins must be driven low by an external device, by external pulldown resistors or by the internal pulldown circuit controlled by the HPE bit in the SYSR register.                                                                                                                                                                                          |  |  |  |

| HMODE                                            | 1                                   | J      | <b>Host multiplexed/non-multiplexed mode select.</b> When HMODE is high, the EHPI operates in nonmultiplexed mode. When HMODE is low, the EHPI operates in multiplexed mode.                                                                                                                                                                                                                                                                           |  |  |  |

| HCNTL0<br>HA1/HCNTL1                             | - 1                                 | J      | Host control selects. HCNTL0 and HCNTL1 select host accesses to EHPI address, data or control registers. HA1/HCNTL operates as HCNTL when HMODE is low (multiplexed mode).                                                                                                                                                                                                                                                                             |  |  |  |

| HINT                                             | O/Z                                 | F      | Host interrupt (from DSP to host). This output is used to interrupt the host. HINT is high following reset.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

<sup>†</sup> I = Input, O = Output, S = Supply, Z = High impedance

$\begin{array}{ll} A - Internal \ pullup \ (always \ enabled) & E - Pin \ is \ high \ impedance \ in \ HOLD \ mode \ (due \ to \ \overline{HOLD} \ pin). \\ F - Pin \ is \ high \ impedance \ in \ OFF \ mode \ (due \ to \ EMU1/\overline{OFF} \ pin). \end{array}$

C – Hysteresis input

D – Pin has bus holder

G – Pin can be configured as a general-purpose input.

H – Pln can be configured as a general-purpose output.

J – Internal pullup enabled by the HPE bit in the system register (SYSR)

K – Internal pulldown enabled by the HPE bit in the system register (SYSR)

<sup>‡</sup> Other Pin Characteristics:

#### Table 2-2. Signal Descriptions (Continued)

| SIGNAL<br>NAME                               | TYPE | OTHER‡ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------------------------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INTERRUPT AND RESET SIGNALS                  |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RESET                                        | I    | С      | <b>Device reset.</b> RESET causes the DSP to terminate execution and causes reinitialization of the CPU and peripherals. The response of the DSP after reset is determined by the RST_MODE pin.                                                                                                                                                                                                                                                            |  |  |  |

|                                              |      |        | Device reset mode control. RST_MODE controls how a device reset is handled.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RST_MODE                                     | I    |        | As of revision 2.1, the RST_MODE function will no longer be supported. RST_MODE will be driven low internally. After reset, the CPU will branch to the reset vector and begin execution.                                                                                                                                                                                                                                                                   |  |  |  |

|                                              |      |        | The external state of the RST_MODE pin will have no effect on device operation.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| INT0<br>INT1<br>INT2<br>INT3<br>INT4<br>INT5 | -    | С      | Maskable external interrupts. INT0-INT5 are prioritized and are maskable via the interest enable registers (IER0 and IER1) and the Interrupt Mode bit (INTM in ST1_55). INT0-INT9 be polled and reset via the Interrupt Flag Registers (IFR0 and IFR1).                                                                                                                                                                                                    |  |  |  |

| NMI                                          | ı    | С      | Nonmaskable external interrupt. NMI is an external interrupt that cannot be masked by the interrupt enable registers (IER0 and IER1). When NMI is activated, the interrupt is always performed.                                                                                                                                                                                                                                                            |  |  |  |

|                                              |      |        | JTAG EMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| тск                                          | ı    | A,C    | <b>IEEE Standard 1149.1 test clock.</b> TCK is normally a free-running clock signal with a 50% cycle. The changes on the test access port (TAP) of input signals TDI and TMS are clocke the TAP controller, instruction register, or selected test data register on the rising edge of Changes at the TAP output signal TDO occur on the falling edge of TCK.                                                                                              |  |  |  |

| TDI                                          | I    | А      | <b>IEEE Standard 1149.1 test data input.</b> TDI is clocked into the selected register (instruction or data) on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| TDO                                          | 0    | -      | <b>IEEE Standard 1149.1 test data output.</b> The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when the scanning of data is in progress.                                                                                                                                                                                                           |  |  |  |

| TMS                                          | ı    | А      | <b>IEEE Standard 1149.1 test mode select.</b> This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| TRST                                         | I    | В      | IEEE Standard 1149.1 test reset. TRST, when high, gives the IEEE standard 1149.1 scan system control of the operations of the device. If TRST is not connected, or driven low, the device operates in its functional mode, and the IEEE standard 1149.1 signals are ignored.  This pin has an on-chip pulldown circuit to provide control of the pin when it is not externally connected. An external pullup resistor should not be connected to this pin. |  |  |  |

$<sup>^{\</sup>dagger}$ I = Input, O = Output, S = Supply, Z = High impedance

A – Internal pullup (always enabled) E – Pin is high impedance in HOLD mode (due to HOLD pin).

B – Internal pulldown (always enabled) F – Pin is high impedance in OFF mode (due to EMU1/OFF pin).

C – Hysteresis input

D – Pin has bus holder

G – Pin can be configured as a general-purpose input.

H – Pln can be configured as a general-purpose output.

J – Internal pullup enabled by the HPE bit in the system register (SYSR)

K – Internal pulldown enabled by the HPE bit in the system register (SYSR)

<sup>‡</sup> Other Pin Characteristics:

Table 2-2. Signal Descriptions (Continued)

| SIGNAL<br>NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TYPET    | OTHER‡         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |