# SP1600 SERIES

# SP1670B (HIGHZ) SP1671B (LOWZ) MASTER/SLAVE TYPE D FLIP-FLOP

The SP1670B is a Type D Master-Slave Flip-Flop designed for use in high speed digital applications. Master-slave construction renders the SP1670B relatively insensitive to the shape of the clock waveform, since only the voltage levels at the clock inputs control the transfer of information from data input (D) to output.

When both clock inputs (C1 and C2) are in the low state, the data input affects only the Master portion of the flip-flop. The data present in the Master is transferred to the Slave when clock inputs (C1 OR C2) are taken from a low to a high level. In other words, the output state of the flip-flop changes on the positive transition of the clock pulse.

While either C1 OR C2 is in the high state, the Master (and data input) is disabled.

Asynchronous Set (S) and Reset (R) override Clock (C) and Data (D) inputs.

Input pulldown resistors eliminate the need to tie unused inputs to  $V_{\text{FF}}\,.$

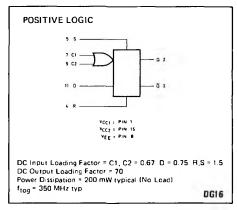

Fig. 1 Logic diagram

### **FEATURES**

- Toggle Frequency > 300 MHz

- MECL/PECL II and MECL 10000 Compatible

- 50Ω Line Driving Capability

- Operation With Unused I/Ps Open Circuit

- Low Supply Noise Generation

#### APPLICATIONS

- Data Communications

- Instrumentation

- PCM Transmission Systems

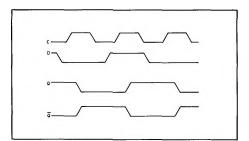

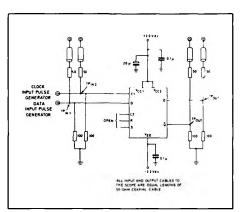

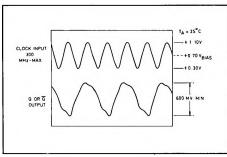

Fig. 2 Timing diagram

| TRUTH TABLE |   |   |                  |                                  |  |  |  |  |  |

|-------------|---|---|------------------|----------------------------------|--|--|--|--|--|

| R           | S | D | Q <sub>n+1</sub> |                                  |  |  |  |  |  |

|             | Н | φ | φ                | Н                                |  |  |  |  |  |

| Н           | L | φ | φ                | L                                |  |  |  |  |  |

| н           | н | φ | φ                | N.D.                             |  |  |  |  |  |

| L           | L | L | L                | Q <sub>n</sub>                   |  |  |  |  |  |

| L           | L | L | <i></i>          | L                                |  |  |  |  |  |

| L           | L | L | н                | Qn                               |  |  |  |  |  |

| L           | L | н | L                | Q <sub>n</sub><br>Q <sub>n</sub> |  |  |  |  |  |

| L           | L | н |                  | Н                                |  |  |  |  |  |

| L           | L | Н | н                | $Q_n$                            |  |  |  |  |  |

φ = Don't Care ND = Not Defined

C = C1 + C2

# **ABSOLUTE MAXIMUM RATINGS**

0V to V<sub>EE</sub>

< 40mA

-55°C to +150°C

< +125°C

# SP1670/71

# **ELECTRICAL CHARACTERISTICS**

This PECL III circuit has been designed to meet the d.c. specifications shown in the characteristics table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear ft/min is maintained. Outputs are terminated through a  $50\Omega$  resistor to -2.0 volts.

|                                  |          |       |                     |            |        |            |           | TEST VOLTAGE VALUES (V)                    |                  |         |         |          |          |        | l     |    |    |    |

|----------------------------------|----------|-------|---------------------|------------|--------|------------|-----------|--------------------------------------------|------------------|---------|---------|----------|----------|--------|-------|----|----|----|

|                                  |          |       |                     |            |        |            |           |                                            | Test<br>perature | VIH mex | VIL min | VIHA min | VILA mex | VEE    |       |    |    |    |

|                                  |          |       |                     |            |        |            |           |                                            | 0°C              | -0.840  | -1.870  | -1.135   | -1.500   | -5.2   |       |    | 1  | ł  |

|                                  |          |       |                     |            |        |            |           |                                            | + 25°C           | -0.810  | -1.850  | -1.095   | -1.485   | -5.2   |       |    | l  | 1  |

|                                  |          |       |                     |            |        |            |           |                                            | +75°C            | -0.720  | -1.830  | -1.035   | -1.460   | -5.2   |       | 1  | l  | 1  |

| Characteristic Symbol            | Jan S    | Pin   | SP1870B Test Limits |            |        |            |           | TEST VOLTAGE APPLIED TO PINS LISTED BELOW: |                  |         |         |          |          |        |       |    |    |    |

|                                  | Symbol   | Under | Min                 | Max        | Min    | 5°C<br>Max | +7<br>Min | 5°C<br>Max                                 | Unit             | Vin max | VIL min | VIHA min | VILA max | VEE    | P. P. | P2 | Pa | ov |

| Power Supply Drain<br>Current    | le ·     | -     | -                   | -          | -      | 48         | -         | -                                          | mA               | 9,7     | 4-      | -        | -        | 8      | *     | -  | -  | 1, |

| Input Current                    | lo H     | - 4   | -                   | -          | -      | 550        | -         | -                                          | μА               | 4       | -       | -        | -        | 8      | ~     | -  | -  | 1, |

|                                  | -27.54   | 5     | -                   | 1000       | -      | 550        | -         |                                            | 1                | 5       | -       | -        | -        |        | -     | ~  | -  |    |

|                                  |          | 9     | -                   |            | -      | 250        | -         | -                                          |                  | 9       | 100     | -        | -        |        | -     | ~  | -  |    |

|                                  |          | 7     | -                   |            | -      | 250        | -         | -                                          |                  | 7       | -       | - 1      |          |        | -     | -  | -  | 1  |

|                                  |          | 11    | -                   | -          | -      | 270        | -         | -                                          | ,                | 11      | -       | -        | -        | 1 1    | -     | -  | -  |    |

|                                  | Im L     | 4     | -                   | -          | 0.5    | -          | -         | -                                          | μΑ               | 9       | 4       | -        | -        | 8      | -     | -  | -  | 1, |

|                                  |          | 5     | -                   | -          | 1.1    | -          | -         | -                                          |                  | 9       | 5       | -        | -        |        | -     | -  | -  |    |

|                                  |          | 9     | -                   | 100        | 1 1    | -          | -         | -                                          |                  | 7       | 9       | -        | -        |        | -     | -  | -  | 1  |

|                                  | 1        | 7     | -                   | -          | 1.1    | -          | -         | -                                          |                  | 9       | 7       | 0        | 4        |        | _     | -  | -  | 1  |

|                                  |          | 11    | -                   | -          |        | -          | -         | 40                                         |                  | 9       | 11      | -        | -        | _ '_   | -     | -  | -  | 上  |

| gic "1"                          | Von      | 2     | -1.000              | -0 B40     | -0.960 | -0.810     | -0.900    | -0.720                                     | V                | -       | 4,7,11  | -        | ~        | 8      | 9     | 5  | -  | 1  |

| tput Voltage                     |          | 3     | 1                   |            | 1      | 1          | 11        |                                            | 1                | 11      | 5,9     | -        | -        |        | 7     | 4  | -  |    |

|                                  |          | 2     | 1 1                 |            |        |            | 11        |                                            |                  | 11      | 5,7     | -        | -        | 1      | 4     | 9  | -  |    |

|                                  |          | 3     | 1                   |            | 4      | 1          |           | 1                                          |                  | -       | 49.11   | 102      | -        | 1 1    | 5     | 7  | -  | 1  |

| igic "O"                         | VOL      | 2     | -1.870              | -1.635     | -1.850 | -1.620     | -1.830    | -1.595                                     | V                | 11      | 5.7     | -        | -        | 8      | 9     | 4  | -  | 1  |

| Output Voltage                   | .00      | 3     | 1                   | 1          | 1      | 1          | 1         | 1                                          | 1                | -       | 49.11   |          | -        | T I    | 7     | 5  | -  |    |

|                                  |          | 2     |                     |            |        |            |           | 1                                          |                  | -       | 4,7,11  | -        | -        |        | 5     | 9  | -  |    |

|                                  | 3        |       |                     |            |        |            | 1 1       |                                            | 11               | 5.9     |         | _        |          |        | 7     | -  |    |    |

| ogic "1"                         | VOHA     | 2     | -1.020              | -          | -0.960 | -          | -0.920    | 1-1                                        | v                | -       | 4,7,11  | -        | -        | - 8    | 9     | -  | 5  | 1  |

| reshold Voltage                  | TOHA     | 3     | 1.025               | -          | 1      | -          | 0.000     | -                                          | 1                | 11      | 5.9     | -        | -        | ī      | 7     | -  | 4  |    |

| meshold editage                  | 100      | 2     |                     | -          | 11     | -          |           | 150                                        |                  | 31      | 5.7     | -        | -        |        | 4     | -  | 9  |    |

|                                  |          | 3     |                     | - 3        | 11     | -          | 11        | -                                          |                  | -       | 4.9.11  | -        | -        |        | 5     | _  | 7  |    |

|                                  |          | 2     |                     | -          | 11     | 100        | 11        | 1                                          |                  | -       | 5,7     | 11       | 2.0      |        |       | 9  | 1  |    |

|                                  |          | 3     |                     | -          | 1 1    | -          |           |                                            |                  | 3       | 4.9     | 3.6      | 11       |        | -     | 7  | -  |    |

| ogic "O"                         | M        | 2     | -                   | -1.615     | -      | -1.600     | -         | -1.575                                     | V                | 11      | 5.7     | -        |          | 8      | 9     | -  | 4  | 1  |

| hreshold Voltage                 | VOLA     | 3     |                     | -1.013     |        | -1.000     | _         | -1.075                                     | , i              |         | 4,9,11  | 2.0      | 3.7      |        | 7     | -  | 5  |    |

| resnoid voltage                  |          | 2     | -                   |            | _      |            | _         |                                            |                  | -       | 4,7,11  | 2        | 5        |        | 5     | -  | 9  | ł  |

|                                  |          | 3     |                     | 1 1        |        | 11         |           |                                            |                  | 11      | 5.9     |          | 3        |        | 4     | -  | 7  | ı  |

|                                  |          |       | -                   | 1 1        | -      | 1 1        | -         | 1 1                                        |                  |         |         |          | 11       | 1 1 1  |       |    |    | ١. |

|                                  | 1        | 2     | -                   |            | -      |            | -         |                                            |                  | 5       | 4,7     |          |          |        | 5     | 9  | -  |    |

|                                  |          | _ 3   | -                   | -          | -      | -          | -         |                                            |                  | -       | 5.9     | 11       | -        |        | •     | 1  | -  | +2 |

| witching Parameters              | 1        |       | Min                 | Max<br>2.5 | Min    | Max<br>2.5 | Min       | 2.7                                        | -00              | 1.0     | 1.0     |          |          | -3.2 V |       |    | -  | ** |

| ock to Output Delay              | 19.2.    | 9,2   | 1.0                 | 2.5        | 1.1    | 2.5        | 13        | 2.7                                        | ns               | -       | -       | -        | -        |        | -     | -  | -  | 1  |

| ee Figure 5)                     | tg - 2 - | 9,2   |                     |            | 11     |            | 1 1       |                                            |                  | -       | -       | -        | -        |        |       |    | -  |    |

|                                  | 18+3-    | 9,3   |                     | 1 1        | 11     |            | 11        |                                            |                  | -       | -       | -        | -        |        | -     | -  | -  | l  |

|                                  | 10-3-    | 9,3   |                     | 1 1        | ΙI     | 1 1        | 1 1       |                                            |                  | -       | -       | -        | -        | 1      | -     | -  | -  | ı  |

| I to Output Delay                | 19.2.    | 5.2   | 1 1                 | 1 1        | 1 [    | 1 1        | l I       |                                            |                  | -       | -       | -        | -        | , , ,  | -     | -  | -  | ı  |

| iee Figure 61                    | 15+3-    | 5.3   | 1 I                 |            | 1      | 1 1        | 1 1       |                                            |                  | -       | -       | -        | -        |        | -     | -  | -  | ı  |

| iset to Output Delay             | 412-     | 4,2   | 1 1                 |            | Ιİ     | 1 1        | 1 1       |                                            |                  | -       | -       | -        | -        | 1      | -     | -  | -  | ı  |

| ee Figure 61                     | 4.3.     | 4,3   | 1 1                 |            | 1      | 1 1        |           |                                            |                  | -       | -       | -        | -        |        | -     | -  | -  | ı  |

| iput                             |          | 0.00  |                     |            | 100    | - 1        | 25        | 5.0                                        |                  |         |         |          |          |        |       |    |    | ı  |

| Rise Time                        | 12+,13+  | 2,3   | 0.9                 | 2.5        | 1.0    | 2.5        | 1.0 *     | 2.7                                        |                  | -       | -       | -        | -        |        | -     | -  | -  | ı  |

| Fall Time                        | 12- ta-  | 2,3   | 0.5                 | 1.9        | 0.6    | 1.9        | 0.6       | 2.1                                        |                  | -       | -       | -        | -        |        | -     | -  | -  | ı  |

| ee Figure 6)                     | 1        |       |                     |            |        |            |           |                                            |                  |         |         |          |          |        |       |    |    | 1  |

| 1 Up Time                        | 4-9-     | 2     | -                   | -          | -      | 0.4        | -         | -                                          |                  | -       | 2       | (4)      | -        |        | -     | -  | -  | 1  |

| ee Figure 7)                     | 4.0      | 2     | -                   | -          | -      | 0.5        | -         | -                                          |                  | -       | 2       | 1.4.1    | -        |        | -     | -  | -  | 1  |

| old Time                         | term     | 2     | -                   | -          | -      | 0.3        | -         | -                                          | 1                | 100     | 2       | 1 - 1    | 4        | 1 1 1  | 1     | -  | -  | 1  |

| ee Figure 7)                     | te-0-    | 2     | -                   |            | 0-0    | 0.5        | -         | -                                          | 1                | -       | 2       | -        | -        |        | -     | -  | -  | ı  |

| oggle Frequency<br>See Figure 8) | free     | 2     | 270                 | -          | 300    | -          | 270       | -                                          | MHz              | -       | -       | -        | 141      |        | -     | -  | -  | 10 |

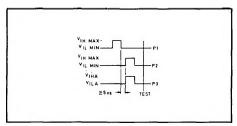

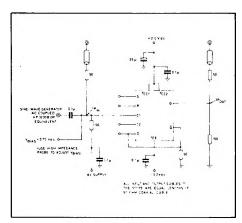

Fig. 3 Static test pulses

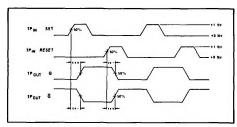

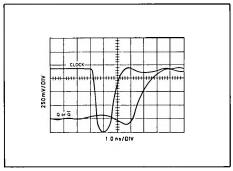

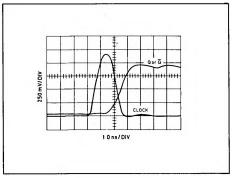

Fig. 6 Set/reset delay waveform at +25°C

Fig. 4 Propagation delay test circuit

Fig. 5 Clock delay waveforms at +25°C

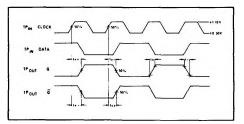

Fig. 7 Set-up and hold time test circuit

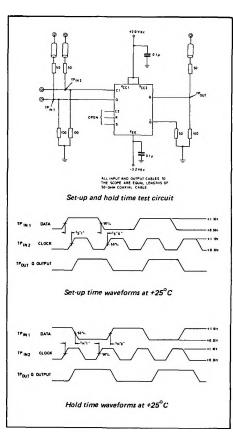

Fig. 8 Toggle frequency test circuit

# **OPERATING NOTES**

Set up time is the minimum time before the positive transition of the clock pulse (C) that information must be present at the data (D) input.

Hold time is the minimum time after the positive transition of the clock (C) that information must remain unchanged at the data (D) input.

$V_{\mbox{\footnotesize{Bias}}}$  is defined by the test circuit Fig.8 and by the waveform in Fig.9.

Figures 10 and 11 illustrate minimum clock pulse width recommended for reliable operation of the SP1670B.

Fig. 9 Toggle frequency waveforms

The maximum toggle frequency of the SP1670B has been exceeded when either:

- The output peak-to-peak voltage swing falls below 600 millivolts.

- 2. The device ceases to toggle (divide by two).

| Temperature       | 0°C     | +25°C   | +75°C   |  |  |  |

|-------------------|---------|---------|---------|--|--|--|

| V <sub>Bias</sub> | +0.675V | +0.700V | +0.750V |  |  |  |

Table 1 Variation of VBias with temperature

Fig. 10 Minimum 'downtime' to clock output load =  $50\Omega$

Fig. 11 Minimum 'up time' to clock output load =  $50\Omega$

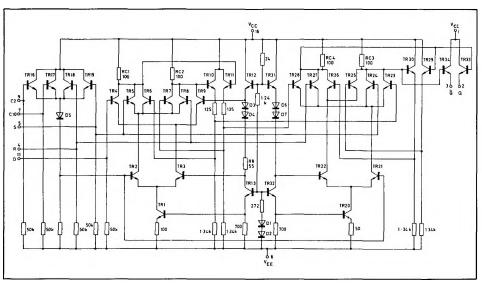

#### Operation of the Master-Slave Type D Flip-Flop

In the circuit of Figure 14 assume that initially Q, C, R, S and D are at 0 levels and that  $\overline{Q}$  is at the 1 level. Since the clock is low, transistors TR3 and TR22 are conducting. In the slave section only transistors TR25 and TR26 are in series with TR22. The output of the slave section is fed back to these two transistors in order to form a latch. Thus, when the clock is low, the output state of the slave is maintained. In the master section, the current path is through TR3 and TR9.

Now assume that the data input goes high. The high-input signal on the base of TR4 causes it to conduct, and TR9 to turn off. The voltage drop across resistor RC1 causes a low-state voltage on the base and therefore on the emitter of TR11. Since there is essentially no current flow through RC2, the base of transistor TR10 is in a high state. This is reflected in the emitter, and in turn is transferred to the base of TR6, TR6 is biased for conduction but, since there is no current path, does not conduct.

Now allow the clock to go high. As the clock signal rises, transistor TR2 turns on and transistor TR3 turns off. This provides a current path for the common-emitter transistors TR5, TR6, TR7, and TR8. Since the bases of all these devices except TR6 are in the low state, current flow is through TR6. This maintains the base and emitter of TR11 low, and the base and emitter of TR10 high. The high state on TR10 is transferred to TR23 of the slave section. As the clock continues to rise TR21 begins to turn on and TR22 to turn off. (Reference voltages in the master and slave units are slightly offset to ensure prior clocking of the master section.) With transistor TR21 conducting and the base of TR23 in a high state, the current path now includes TR21, TR23, and resistor RC3. The voltage drop across the resistor places a low state voltage on the base, and therefore

the emitter, of TR30. The lack of current flow through RC4 causes a high state input to the base of TR29. These states are fed back to the latch transistors, TR25 and TR26.

As the clock voltage falls, transistor TR21 turns off and TR22 turns on. This provides a current path through the latch transistors, locking-in the slave output.

In the master section the falling clock voltage turns on transistor TR3 and turns off TR2. This enables the input transistor TR4 so that the master section will again track the D input.

The separation of thresholds between the master and slave flip-flops is caused by R8. The current through this resistor produces an offset between the thresholds of the transistor pairs TR2:TR3 and TR21:TR22. This offset disables the D input of the master flip-flop prior to the enabling of the information transfer from master to slave via transistors TR23 and TR28. This disabling operation prevents false information from being transferred directly from master to slave during the clock transition, particularly if the D input changes at this time (such as in a counting operation where the  $\overline{\Omega}$  output is tied back to D). The offsetting resistor also allows a relatively slow-rising clock waveform to be used without the danger of losing information during the transition of the clock.

The set and reset inputs are symmetrically connected. Therefore, their action is similar although results are opposite. As a logic 1 level is applied to the S input transistor, TR2 begins to conduct because its base is now being driven through TR19 which is in turn connected to S. Transistor TR5 is now on and the feedback devices TR6 and TR7 latch this information into the master flip-flop. A similar action takes place in the slave with transistors TR21, TR24, TR25, and TR26.

Fig. 12 SP1670 circuit diagram