## SP8000 SERIES

### HIGH SPEED DIVIDERS

# SP8660 A, B & M

180 MHz ÷ 10 (LOW POWER)

The SP8660 is a fixed ratio (divide by 10) low power counter for operation at frequencies in excess of 100MHz over the temperature ranges -55°C to +125°C ('A' grade) 0°C to +70°C ('B' grade) and -40°C to +85°C ('M' grade)

The input can be either single or double driven and must be capacitively coupled to the signal source. If single drive is used, the unused input must be capacitively decoupled to the ground plane. There are two bias points, which should also be capacitively decoupled to the ground plane.

The free collector saturating output stage is capable of interfacing with TTL and CMOS.

#### **FEATURES**

VHF Operation

Low Power Dissipation

Output TTL and CMOS Compatible

Military and Commercial Temperature Ranges

#### **APPLICATIONS**

Low Power VHF Communications

Portable Counters

#### **ABSOLUTE MAXIMUM RATINGS**

Power supply voltage, V<sub>CC</sub> - V<sub>EE</sub> 8V

Input voltage V<sub>in</sub> Not greater than

supply voltage in use

Output sink current, Io 10mA

Operating junction temperature +150°C

Storage temperature -55°C to +150°C

Fig. 1 Pin connections (viewed from beneath)

### OPERATING NOTES

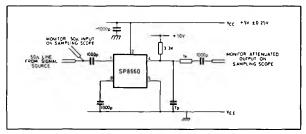

Fig. 3 gives capacitor values for AC and DC coupling of the input and bias points on the test circuit; these values are not critical and will depend on the operating frequency.

The device will normally self-oscillate in the absence of an input signal. This can be easily prevented by connecting a 39k $\Omega$  pulldown resistor from either input (double drive) to  $V_{\text{EE}}$ ; if the device is single driven then it is recommended that the pulldown resistor be connected the decoupled unused input. The slight loss of input sensitivity resulting from this technique does not seriously affect the operation of the device.

The input waveform will normally be sinusoidal but below 40MHz correct operation depends on the slew rate of the input signal. A slew rate of  $100V/\mu s$  will enable the device to operate down to DC.

The output stage will drive three TTL gates without the addition of a pull-up resistor. Using a pull-up resistor of  $3.3k\Omega$  (or less) to +10V will allow the output to drive a CMOS binary counter at a frequency of up to 5MHz.

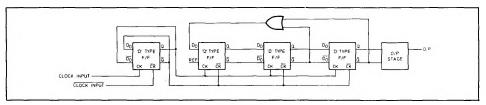

Fig. 2 Logic diagram

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated)

Operating ambient temperature  $T_A$

'A' grade: -55°C to +125°C; 'B' grade: 0°C to 70°C; 'M' grade: -40°C to +85°C;

Operating supply voltages

V<sub>CC</sub>: +5.0V± 0.25V; V<sub>EE</sub>: 0V

Input voltage

Single drive: 400mV to 800mV p-p; double drive: 250mV to 800mV p-p

Output load 3.3k $\Omega$  to +10V, in parallel with 7pF

| Characteristic                         | Value |      |      |       | Constitute              |

|----------------------------------------|-------|------|------|-------|-------------------------|

|                                        | Min.  | Тур. | Max. | Units | Condition               |

| Maximum input frequency                | 100   | 200  |      | MHz   |                         |

| Minimum sinusoidal input frequency     |       | 20   | 40   | MHz   | ł                       |

| Minimum slew rate of square wave input |       | 30   | 100  | V/μs  |                         |

| Power supply drain current             |       | 10   | 13   | mA    | V <sub>CC</sub> = +5.0V |

| Output level (high)                    | 9.0   |      |      | V     |                         |

| Output level (low)                     |       |      | 400  | mV    | l .                     |

Fig. 3 Test circuit