# **SP8000 SERIES**

### **HIGH SPEED DIVIDERS**

## SP8748A, B & M

### UHF PROGRAMMABLE DIVIDER 300 MHz + 8/9

In frequency synthesis it is desirable to start programmable division at as high a frequency as possible, because this raises the comparison frequency and so improves the overall synthesiser performance.

The SP8748 series are UHF integrated circuits that can be logically programmed to divide by either 8 or 9 with input frequencies up to 300MHz. The design of very fast fully programmable dividers is therefore greatly simplified by the use of these devices and makes them particularly useful in frequency synthesisers operating in the UHF band.

All inputs and outputs are ECL-compatible throughout the temperature range: the clock inputs and programming inputs are ECL III-compatible while the two complementary outputs are ECL-II compatible to reduce power consumption in the output stage. ECL III output compatability can be achieved very simply, however (see Operating Notes).

The division ratio is controlled by two  $\overrightarrow{PE}$  inputs. The counter will divide by 8 when either  $\overrightarrow{PE}$  input is in the high state and by 9 when both inputs are in the low state. Both the  $\overrightarrow{PE}$  inputs and the clock inputs have nominal 4.3k  $\Omega$  pulldown resistors to  $V_{EE}$  (negative rail)

# CLOCK 1/P FET (2 15) FET (3 16) VCC (1 12) VCC (1

Fig. 1 Pin connections (top)

### **FEATURES**

- Military and Industrial Variants

- 300 MHz Toggle Frequency

- Low Power Consumption

- ECL Compatibility on All I/Ps & O/Ps

- Low Propagation Delay

- True and Inverse Outputs

### QUICK REFERENCE DATA

■ Temperature Ranges: 'A' Grade —55°C to +125°C

'B' Grade 0°C to +70°C

'M' Grade  $-40^{\circ}$ C to  $+85^{\circ}$ C

Supply Voltage

Vcc — VFF 5.2V

- Power Consumption 250mW Tvp..

- Propagation Delay 3ns Typ.

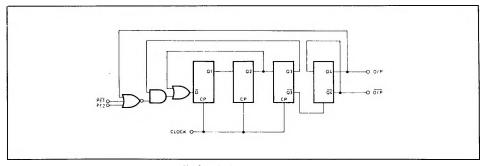

Fig. 2 Logic diagram (positive logic)

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Tamb: 'A' Variant -55°C to +125°C 'B' Variant 0°C to +70°C

'M' Variant -40°C to +85°C

Supply voltage (see note 1): Vcc 0V

VFF -5.2V

### Static Characteristics

|                                                                               |                | Value |                |          | cs Conditions                                                                                                                                                        |

|-------------------------------------------------------------------------------|----------------|-------|----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristics                                                               | Min.           | Тур.  | Max.           | Units    |                                                                                                                                                                      |

| Clock and PE input voltage evels VINH VINL Input pulldown resistance, between | -1.10<br>-1.85 |       | -0.81<br>-1.50 | <b>V</b> | Tamb = +25°C,<br>see Note 2                                                                                                                                          |

| pins 1, 2, 3, and 16 and V <sub>EE</sub> (pin 12) Output voltage levels       |                | 4.3   |                | К        | P-1                                                                                                                                                                  |

| Von<br>Vol                                                                    | -0.85          |       | -1.50          | V        | $T_{amb} = +25$ °C,<br>see Note 3.<br>$I_{out}$ (external) = OmA<br>(There is an internal circuit<br>equivalent to a $2k\Omega$ pulldown<br>resistor on each output) |

| Power supply drain current                                                    |                | 50    | 65             | mA       |                                                                                                                                                                      |

### NOTES

- The devices are specified for operation with the power supplies of V<sub>CC</sub> = 0V and V<sub>EF</sub> = −5.2V ±0.25V, which are the normal ECL supply rails. They will also operate satisfactorily with TTL rails of  $V_{CC} = \pm 5V \pm 0.25V$  and  $V_{EE} = 0V$ .

- The input reference voltage has the same temperature coefficient as ECL III and ECL 10K.

- 3. The output voltage levels have the same temperature coefficients as ECL II output levels.

### **Dynamic Characteristics**

| Characteristic                 | Value |      |       |       |                    |

|--------------------------------|-------|------|-------|-------|--------------------|

|                                | Min.  | Тур. | Max.  | Units | Conditions         |

| Clock input voltage levels     |       |      |       |       |                    |

| VINH                           | -1.10 |      | -1.10 | V     | $T_{amb} = +25$ °C |

| VINL                           | _1.70 |      | -1.50 | V     | see Note 4         |

| Max. toggle frequency          | 300   |      |       | MHz   |                    |

| Min. frequency with            |       |      |       |       |                    |

| sinewave clock input           |       |      | 10    | MHz   |                    |

| Min. slew rate of square wave  | 1 1   |      |       |       |                    |

| input for correct operation    |       |      |       |       | 4-                 |

| down to 0MHz                   |       |      | 20    | V/µs  |                    |

| Propagation delay              |       |      |       | ••    |                    |

| (clock input to device output) | 1     | 3    |       | ns    |                    |

| Set-up time                    |       | 1.5  |       | ns    | See note 5         |

| Release time                   |       | 1.5  |       | ns    | See note 6         |

### NOTES

- The devices are dynamically tested using the circuit shown in Fig. 5. The bias chain has the same temperature coefficient as ECL III and ECL TOK, and therefore tracks the input reference throughout the temperature range. The devices are tested with input amplitudes of 400 and 800 mV p-p about reference, over the full temperature range.

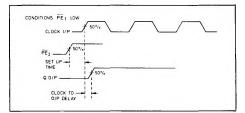

- 5. Set-up time is defined as the minimum time that can elapse between a L-+H transition of a control input and the next L-+H clock pulse transition to ensure that the ÷ 8 mode is forced by that clock pulse (see Fig. 3).

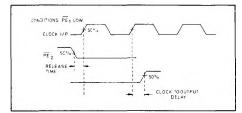

- Release time is defined as the minimum time that can elapse between a H -+ L transition of a control input and the next L-+ H clock pulse transition to ensure that the  $\div 9$  mode is forced by that clock pulse (see Fig. 4).

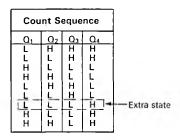

Table 1 Count sequence

# PE1 PE2 Div Ratio L L 9 H L 8 L H 8 H H 8

Table 2 Truth table for control inputs

The maximum possible loop delay for control is obtained if the L $\rightarrow$ H transition from  $Q_3$  or the H $\rightarrow$ L transition from  $\overline{Q_3}$  is used to clock the stage controlling the  $\div$  8/9. The loop delay is 8 clock periods minus the internal delays of the  $\div$  8/9 circuit.

### **OPERATING NOTES**

The SP8748 range of devices are designed to operate in the UHF band and therefore PCB layouts should comply with normal UHF rules, e.g. non-inductive resistors and capacitors should be used, power supply rails decoupled, etc.

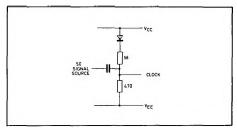

All clock and control inputs are compatible with ECL III and ECL 10K throughout the temperature range. However, it is often desirable to capacitively-couple the signal source to the clock, in which case an external bias network is required as shown in Fig. 6.

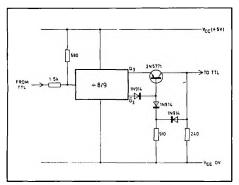

The  $\div$  8/9 can be controlled by a TTL fully-programmable counter, provided that delays within the loop are kept to a minimum. The outputs and control inputs must therefore interface to TTL. The input TTL to ECL interface is accomplished with two resistors as shown in Fig. 7. The output ECL to TTL interface requires some gain and therefore uses a transistor. This interface as shown on Fig. 7 gives the true output; the inverse can be obtained by interchanging the  $\Omega_3$  and  $\Omega_3$  outputs.

The output interface will operate satisfactorily over the full military temperature range ( $-55^{\circ}\mathrm{C}$  to  $-125^{\circ}\mathrm{C}$ ) at frequencies in excess of 35MHz. It has a fan out of one and the propagation delay through the divider plus the interface and one Schottky TTL gate is approximately 10ns. At an input frequency of 300MHz this would only leave about 16ns for the fully programmable counter to control the  $\pm$ 8/9. The loop delay can be increased by extending the  $\pm$ 8/9 function to, say, -16/17 or 32/33.

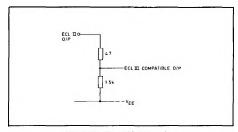

The SP8748 device O/Ps are compatible with ECL II levels when there is no external load. They can be made compatible with ECL III and ECL 10K with a simple potential dividing network as shown in Fig. 8.

The control and clock inputs are already compatible with ECL III and ECL 10K. The interface circuit of Fig. 8 can also be used to increase the noise immunity when interfacing from ECL III and ECL 10K outputs at low current levels to ECL III and ECL 10K inputs.

Fig. 3 Set-up timing diagram

Fig. 4 Release timing diagram

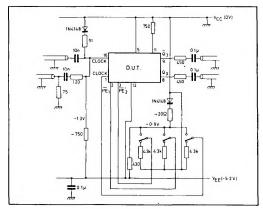

Fig. 5 Test circuit for dynamic measurements

### **SP8748**

Fig. 6 Recommended input bias configuration for capacitive coupling to a continuous 50Ω signal source

Fig. 8 ECL II to ECL III interface

Fig. 7 TTL to ECL and ECL/TTL interfaces (SP874 devices and TTL operating from the same supply rails)

### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage I  $V_{CC} - V_{EE}$  I Input voltage  $V_{in}$  (DC)

Output current I out Max. junction temperature Storage temperature range Not greater than the supply voltage in use. 20mA +150°C -55°C to +175°C