# Audio Dual Matched NPN Transistor

SSM-2210

#### **FEATURES**

- Low Cost

- Direct Replacement For LM394BN/CN

#### **ORDERING INFORMATION t**

| PAC              | OPERATING             |                      |

|------------------|-----------------------|----------------------|

| PLASTIC<br>8-PIN | SO<br>8-PIN           | TEMPERATURE<br>RANGE |

| SSM2210P         | SSM2210S <sup>†</sup> | XIND*                |

<sup>\*</sup> XIND = -40°C to +85°C

#### **GENERAL DESCRIPTION**

The SSM-2210 is a dual NPN matched transistor pair specificially designed to meet the requirements of ultra-low noise audio systems.

With its extremely low input base spreading resistance (rbb' is typically 28 $\Omega$ ), and high current gain (h<sub>FE</sub> typically exceeds 600 @ I<sub>C</sub> = 1mA), systems implementing the SSM-2210 can achieve outstanding signal-to-noise ratios. This will result in superior performance compared to systems incorporating commercially available monolithic amplifiers.

The equivalent input voltage noise of the SSM-2210 is typically only 0.8nV/\Hz over the entire audio bandwidth of 20Hz to 20KHz.

Excellent matching of the current gain  $(\Delta h_{FE})$  to about 0.5% and low  $V_{OS}$  of less than  $50\mu V$  (typical) make it ideal for symmetrically balanced designs which reduce high order amplifier harmonic distortion.

Stability of the matching parameters is guaranteed by protection diodes across the base-emitter junction. These diodes prevent degradation of Beta and matching characteristics due to reverse biasing of the base-emitter junction.

The SSM-2210 is also an ideal choice for accurate and reliable current biasing and mirroring circuits. Furthermore, since a current mirror's accuracy degrades exponentially with mismatches of  $V_{\rm BE}$ 's between transistor pairs, the low  $V_{\rm OS}$  of the SSM-2210 will preclude offset trimming in most circuit applications.

The SSM-2210 is offered in an 8-pin epoxy DIP and 8-pin SO, its performance and characteristics are guaranteed over the extended industrial temperature range of -40°C to +85°C.

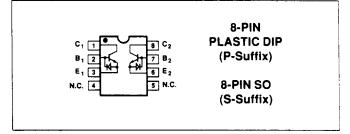

#### **PIN CONNECTIONS**

## **ABSOLUTE MAXIMUM RATINGS**

| Collector Current (I <sub>c</sub> )            | 20mA           |

|------------------------------------------------|----------------|

| Emitter Current (I <sub>F</sub> )              |                |

| Collector-Collector Voltage (BV                | 40V            |

| Collector-Base Voltage (BV <sub>CBO</sub> )    | 40V            |

| Collector-Emitter Voltage (BV <sub>CEO</sub> ) | 40V            |

| Emitter-Emitter Voltage (BV <sub>EE</sub> )    | 40V            |

| Operating Temperature Range                    | 40°C to +85°C  |

| Storage Temperature                            | 65°C to +125°C |

| Junction Temperature                           | 65°C to +150°C |

| Lead Temperature (Soldering, 60 sec)           | +300°C         |

| PACKAGE TYPE          | Θ <sub>jA</sub> (NOTE 1) | Θ <sub>IC</sub> | UNITS |

|-----------------------|--------------------------|-----------------|-------|

| 8-Pin Plastic DIP (P) | 110                      | 50              | °C/W  |

| 8-Pin SO (S)          | 160                      | 44              | ¹C/W  |

#### NOTE:

Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for P-DIP packages; Θ<sub>jA</sub> is specified for device soldered to printed circuit board for SO packages.

<sup>†</sup> For availability on SO package, contact your local sales office

# SSM-2210

# **ELECTRICAL CHARACTERISTICS** at $V_{CB}$ = 15V, $I_{C}$ = 10 $\mu$ A, $T_{A}$ = 25°C, unless otherwise noted.

|                           |                                    |                                                     | SSM-2210     |             |     |          |

|---------------------------|------------------------------------|-----------------------------------------------------|--------------|-------------|-----|----------|

| PARAMETER                 | SYMBOL                             | CONDITIONS                                          | MIN          | TYP         | MAX | UNITS    |

| Current Gain              | h                                  | I <sub>C</sub> = 1 mA (Note 1)                      | 300          | 605         | -   |          |

| - Content Gain            | h <sub>FE</sub>                    | I <sub>C</sub> = 10μA                               | 200          | 550         | -   |          |

| Current Gain Match        | Δh <sub>FE</sub>                   | 10μA ≤ I <sub>C</sub> ≤ 1mA (Note 2)                | _            | 0.5         | 5   | %        |

|                           |                                    | I <sub>C</sub> = 1mA, V <sub>CB</sub> = 0 (Note 3)  |              |             |     |          |

| Nation Walkers of Barrier |                                    | f = 10Hz                                            | -            | 1.6         | 2   |          |

| Noise Voltage Density     | $\mathbf{e}_{_{n}}$                | f = 100Hz                                           | _            | 0.9<br>0.85 | 1   | nV/√Hz   |

|                           |                                    | f = 1kHz<br>f = 10kHz                               |              | 0.85        | 1   |          |

|                           |                                    |                                                     |              | 0.65        |     |          |

| Offset Voltage            | v <sub>os</sub>                    | V <sub>CB</sub> = 0<br>I <sub>C</sub> = 1mA         | <del>_</del> | 10          | 200 | μV       |

| Offset Voltage            | aV /aV                             | 0 ≤ V <sub>CB</sub> ≤ V <sub>MAX</sub> (Note 4)     | _            | 10          | 50  |          |

| Change vs V <sub>CB</sub> | ΔV <sub>OS</sub> /ΔV <sub>CB</sub> | 1μ <b>A</b> ≤ I <sub>C</sub> ≤ 1m <b>A</b> (Note 5) | -            |             |     | μV<br>   |

| Offset Voltage Change     | $\Delta V_{OS}/\Delta I_{C}$       | V <sub>CB</sub> = 0V                                | _            | 5           | 70  | μ∨       |

| vs Collector Current      | os/⊐¹c                             | 1μA ≤ I <sub>C</sub> ≤ 1mA (Note 5)                 |              |             |     | μν       |

| Breakdown Voltage         | BV <sub>CEO</sub>                  |                                                     | 40           | -           | -   | V        |

| Gain-Bandwidth Product    | f <sub>T</sub>                     | $I_{C} = 10 \text{mA}, V_{CE} = 10 \text{V}$        | -            | 200         | -   | MHz      |

| Collector-Base            | СВО                                | V <sub>CB</sub> = V <sub>MAX</sub>                  | _            | 25          | 500 | pA       |

| Leakage Current           |                                    | CB MAX                                              |              |             |     |          |

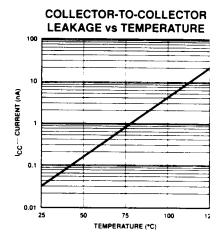

| Collector-Collector       | lcc                                | V <sub>CC</sub> = V <sub>MAX</sub> (Notes 6, 7)     | _            | 35          | 500 | pA       |

| Leakage Current           |                                    | CC MAX C 200-200 /                                  | <del></del>  |             |     | <b>F</b> |

| Collector-Emitter         |                                    | V <sub>CE</sub> = V <sub>MAX</sub> (Notes 6, 7)     | _            | 35          | 500 | pА       |

| Leakage Current           | ces                                | V <sub>BE</sub> = 0                                 | _            | 33          | 300 | PΛ       |

| Input Bias Current        | I <sub>B</sub>                     | I <sub>C</sub> = 10μA                               | -            | _           | 50  | nA       |

| Input Offset Current      | os                                 | l <sub>C</sub> = 10μA                               | -            | -           | 6.2 | nA       |

| Collector Saturation      |                                    | i <sub>C</sub> = 1mA                                |              | 2.25        |     |          |

| Voltage                   | V <sub>CE(SAT)</sub>               | ( <sub>B</sub> = 100μA                              | _            | 0.05        | 0.2 | V        |

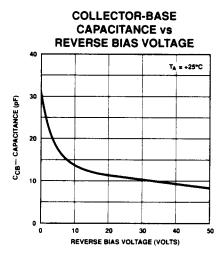

| Output Capacitance        | СОВ                                | V <sub>CB</sub> = 15V, I <sub>E</sub> = 0           | -            | 23          | -   | ρF       |

| Bulk Resistance           | r <sub>BE</sub>                    | 10μA ≤ I <sub>C</sub> ≤ 10mA (Note 6)               | _            | 0.3         | 1.6 | Ω        |

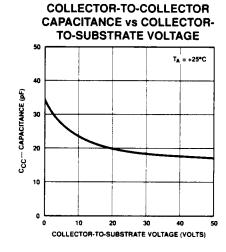

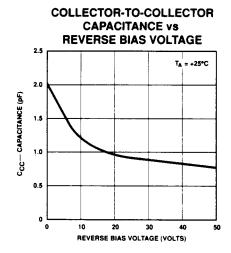

| Collector-Collector       | C <sub>cc</sub>                    | V <sub>cc</sub> = 0                                 | _            | 35          | _   | pF       |

| Capacitance               | -00                                | GC -                                                |              |             |     | ρ.       |

#### NOTES:

$$\Delta h_{FE} = \frac{100(\Delta l_B) (h_{FE}min)}{l_C}$$

3. Noise Voltage Density is guaranteed, but not 100% tested. 4. This is the maximum change in  $\rm V_{OS}$  as  $\rm V_{CB}$  is swept from 0V to 40V.

5. Measured at  $I_C = 10\mu A$  and guaranteed by design over the specified range of  $I_C$ .

6. Guaranteed by design.

7.  $I_{CC}$  and  $I_{CES}$  are verified by measurement of  $I_{CBO}$ .

<sup>1.</sup> Current gain is guaranteed with Collector-Base Voltage  $(V_{CB})$  swept from 0 to  $V_{MAX}$  at the indicated collector currents.

2. Current Gain Match  $(\Delta h_{FE})$  is defined as:

# ELECTRICAL CHARACTERISTICS at V<sub>CB</sub> = 15V, -40°C ≤ T<sub>A</sub> ≤ +85°C, unless otherwise noted.

|                                        |                   |                                                              | SSM-2210       |              |              |       |

|----------------------------------------|-------------------|--------------------------------------------------------------|----------------|--------------|--------------|-------|

| PARAMETER                              | SYMBOL            | CONDITIONS                                                   | MIN            | TYP          | MAX          | UNITS |

| Current Gain                           | h <sub>FE</sub>   | I <sub>C</sub> = 1mA (Note 1)                                | 300            | -            | _            |       |

|                                        |                   | I <sub>C</sub> = 10μA                                        | 200            | ~            | <del>-</del> |       |

| Offset Voltage                         | Vos               | $V_{CB} = 0$ $I_C = 1 \text{mA}$                             | -              | -            | 220          | μV    |

| Average Offset                         | TOV               | $10\mu A \le I_C \le 1mA, 0 \le V_{CB} \le V_{MAX}$ (Note 2) | _              | 0.08         | 1            |       |

| Voltage Drift                          | TCV <sub>os</sub> | V <sub>OS</sub> Trimmed to Zero (Note 3)                     | -              | 0.03         | 0.3          | μV/°C |

| Input Bias Current                     | I <sub>B</sub>    | I <sub>C</sub> = 10μA                                        | -              | <del>-</del> | 50           | nA    |

| Input Offset Current                   | los               | I <sub>C</sub> = 10μA                                        | -              | _            | 13           | nA    |

| Input Offset<br>Current Drift          | TCI <sub>os</sub> | I <sub>C</sub> = 10μA (Note 4)                               |                | 40           | 150          | pA∕°C |

| Collector-Base<br>Leakage Current      | Сво               | V <sub>CB</sub> = V <sub>MAX</sub>                           | <del>-</del> . | 3            | -            | nA    |

| Collector-Emitter Leakage Current      | CES               | $V_{CE} = V_{MAX}$ , $V_{BE} = 0$                            | _              | 4            | -            | nA    |

| Collector-Collector<br>Leakage Current | l <sub>cc</sub>   | V <sub>CC</sub> = V <sub>MAX</sub>                           | _              | 4            | -            | nA    |

#### NOTES:

- 1. Current gain is guaranteed with Collector-Base Voltage ( $V_{CB}$ ) swept from 0 to  $V_{MAX}$  at the indicated collector current.

- 2. Guaranteed by  $V_{OS}$  test (TCV<sub>OS</sub>  $\approx \frac{V_{OS}}{T}$  «  $V_{BE}$ ), T = 298K for T<sub>A</sub> = 25°C.

- The initial zero offset voltage is established by adjusting the ratio of t<sub>C1</sub> to t<sub>C2</sub> at T<sub>A</sub> = 25°C. This ratio must be held to 0.003% over the entire temperature range. Measurements are taken at the temperature extremes and 25°C.

- 4. Guaranteed by design.

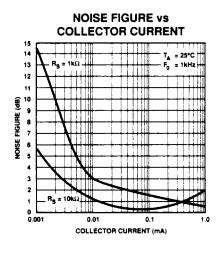

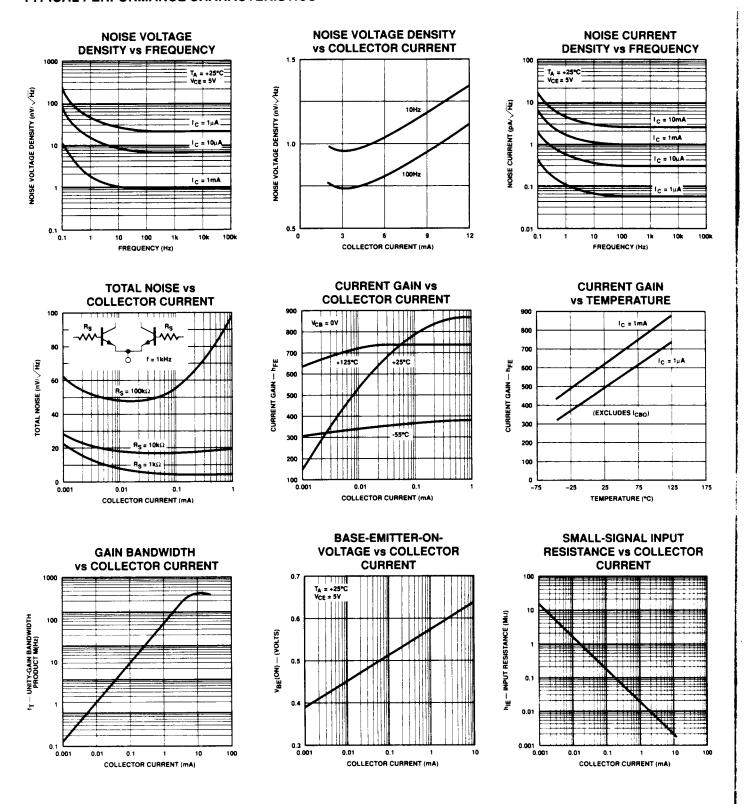

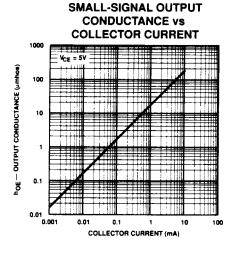

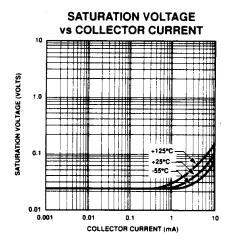

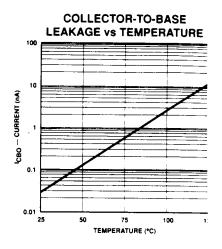

## TYPICAL PERFORMANCE CHARACTERISTICS

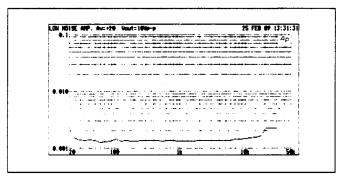

# LOW FREQUENCY NOISE (0.1 Hz TO 10 Hz)

t = 1s/DIV

# TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS Continued

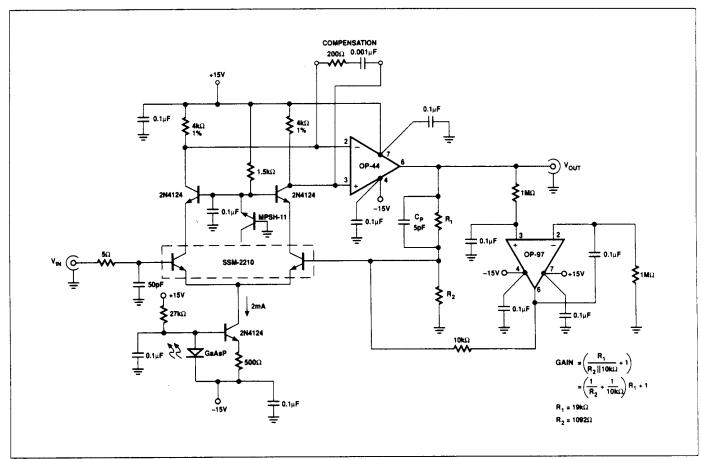

FIGURE 1: A Low-Noise Wideband Amplifier

# A VERY LOW-NOISE, WIDEBAND AMPLIFIER

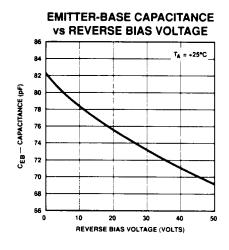

Figure 1 illustrates a low-noise, wide-band amplifier consisting of a high slew rate JFET amplifier, the OP-44, and a cascoded differential preamplifier using the SSM-2210 transistor pair. The SSM-2210 achieves extremely low input voltage noise performance (e\_n  $\approx 0.7 \text{nV}/\sqrt{\text{Hz}})$  via a large geometry transistor design which minimizes the base-spreading resistance. This, however, results in relatively higher collector-to-base capacitance (C\_0B) than ordinary small-signal transistors. For high gain stages, the Miller effect of C\_0B will limit the voltage gain bandwidth; resorting to a cascode configuration reduces the Miller feedback capacitance, improving stability, bandwidth, and reducing distortion due to base-width modulation. Additionally, cascoding does

not increase the noise figure of the overall amplifier system and reduces the high order harmonic distortion.

The circuit in Figure 1 balances the impedance symmetrically in the differential preamp. This serves to reject common-mode noise injected from the power supplies.

Although the SSM-2210's transistors are closely matched, an offset voltage error can still be created by imbalanced source impedances. Accordingly, a precision low-power amplifier (OP-97), configured as a noninverting integrator is implemented which servos-out the offset voltage to less than  $100\mu V$  referred to the input of the amplifier.

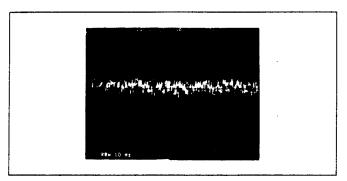

**FIGURE 2:** Spectrum Analyzer Display of Wideband Amplifier Noise Spectral Density.  $e_n \approx 1.7 \text{nV/Hz}$

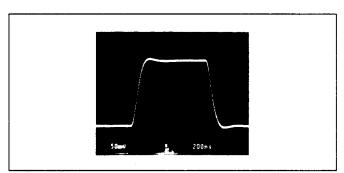

Figure 2 illustrates the composite amplifier's low voltage noise density of only  $1.7 \text{nV}/\sqrt{\text{Hz}}$  @ 1kHz. Figure 3 and Figure 4 show the excellent pulse response and an extremely low distortion of only 0.0015% over the audio bandwidth, respectively.

FIGURE 3: Small-Signal Pulse Response

FIGURE 4: Total Harmonic Distortion vs Frequency

FIGURE 5: D.I.M. vs Frequency

A special test was performed to check for dynamic or transient intermodulation distortion. A square wave of 3.15kHz is mixed with a sine wave probe tone, and the resulting intermodulation distortion was found to be less than 0.002% (Figure 5). This is an impressively low value considering the amplifier's gain of 26dB. Interestingly, the GBW product of the composite amplifier was 63MHz which is much larger than that of the OP-44 by itself. This is made possible by the SSM-2210's cascoded preamplifier having a wide bandwidth and large signal gain.

The measured performance of this amplifier is summarized in Table 1.

**TABLE 1:** Measured Performance of the Low-Noise Wideband Amplifier

| Slew-Rate                          | 40V/μs    |

|------------------------------------|-----------|

| Gain-Bandwidth                     | 63.6 MHz  |

| Input Noise Voltage Density @ 1kHz | 1.7nV/√Hz |

| Output Voltage Swing               | ±13V      |

| Input Offset Voltage               | 10µV      |

# 500pV/√Hz AMPLIFIER

In situations where low output, low-impedance transducers are used, amplifiers must have very low voltage noise to maintain a good signal-to-noise ratio. The design presented in this application is an operational amplifier with only  $500 \text{pV}/\sqrt{\text{Hz}}$  of broadband noise. The front end uses SSM-2210 low-noise dual transistors to achieve this exceptional performance. The op amp has superb DC specifications compatible with high-precision transducer requirements, and AC specifications suitable for professional audio work.

#### PRINCIPLE OF OPERATION

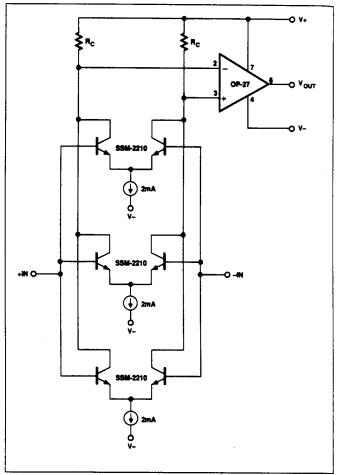

The design configuration in Figure 6 uses an OP-27 op amp (already a low-noise design) preceded by an amplifier consisting of three parallel-connected SSM-2210 dual transistors. Base spreading resistance (rbb) generates thermal noise which is reduced by a factor of  $\sqrt{3}$  when the input transistors are parallel connected. Schottky noise, the other major noise-generating mechanism, is minimized by using a relatively high collector current (1mA per device). High current ensures a low dynamic emitter resistance, but does increase the base current and its associated current noise. Higher current noise is relatively unimportant when low-impedance transducers are used.

FIGURE 6: Simplified Schematic

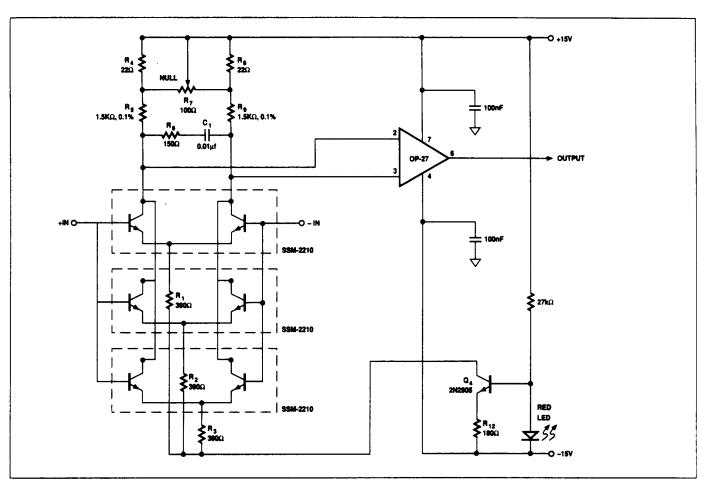

#### **CIRCUIT DESCRIPTION**

The detailed circuit is shown in Figure 7. A total input-stage emitter current of 6mA is provided by  $\mathbf{Q_4}$ . The transistor acts as a true current source to provide the highest possible common-mode rejection.  $\mathbf{R_1}$ ,  $\mathbf{R_2}$ , and  $\mathbf{R_3}$  ensure that this current splits equally among the three input pairs. The constant current in  $\mathbf{Q_4}$  is set by using the forward voltage of a GaAsP light-emitting diode as a reference. The difference between this voltage and the base-emitter voltage of a silicon transistor is predictable and constant (to within a few percent) over the military temperature range. The voltage difference, approximately 1V, is impressed across the

emitter resistor R<sub>12</sub> which produces a temperature-stable emitter current.

R<sub>6</sub> and C<sub>1</sub> provide phase compensation for the amplifier and are sufficient to ensure stability at gains of ten and above.

$R_{\gamma}$  is an input offset trim that provides approximately  $\pm 300 \mu V$  trim range. The very low drift characteristics of the SSM-2210 make it possible to obtain drifts of less than  $0.1 \mu V/^{\circ} C$  when the offset is nulled close to zero. If this trim is not required, the  $R_{4}$ ,  $R_{7}$ , and  $R_{8}$  network should be omitted and  $R_{5}/R_{q}$  connected directly to V+.

FIGURE 7: Complete Amplifier Schematic

# SSM-2210

## **AMPLIFIER PERFORMANCE**

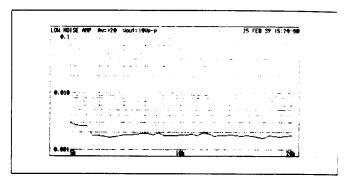

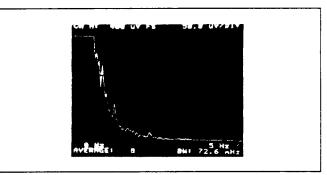

The measured performance of the op amp is summarized in Table 2. Figure 8 shows the broadband noise spectrum which is flat at about 500pV/ $\sqrt{\text{Hz}}$ . Figure 9 shows the low-frequency spectrum which illustrates the low 1/f noise corner at 1.5Hz. The low-frequency characteristic in the time domain from 0.1Hz to 10Hz is shown in Figure 10; peak-to-peak amplitude is less than 40nV.

TABLE 2: Measured Performance of the Op Amp

|                                           |                                       | ·                   |

|-------------------------------------------|---------------------------------------|---------------------|

| Input Noise<br>Voltage Density at 1kHz    |                                       | 500pV/√Hz           |

| Input Noise<br>Voltage from 0.1Hz to 10Hz |                                       | 40nV <sub>p-p</sub> |

| Input Noise Current at 1kHz               |                                       | 1.5pA/√Hz           |

|                                           | G = 10                                | 3MHz                |

| Gain-Bandwidth                            | G = 100                               | 600kHz              |

|                                           | G = 1000                              | 150kHz              |

| Slew Rate                                 |                                       | 2V/μs               |

| Open-Loop Gain                            |                                       | 3 x 10 <sup>7</sup> |

| Common-Mode Rejection                     | · · · · · · · · · · · · · · · · · · · | 130dB               |

| Input Bias Current                        |                                       | ЗμΑ                 |

| Supply Current                            |                                       | 10mA                |

| Nulled TCV <sub>os</sub>                  |                                       | 0.1μV/°C Max        |

| T.H.D. at 1kHz                            | G = 1000                              | 0.002%              |

|                                           |                                       |                     |

FIGURE 8: Spectrum Analyzer Display - Broadband

FIGURE 9: Spectrum Analyzer Display – Low Frequency

FIGURE 10: Oscilloscope Display

#### CONCLUSION

Using SSM-2210 matched transistor pairs operating at a high current level, it is possible to construct a high-performance, low-noise operational amplifier. The circuit uses a minimum of components and achieves performance levels exceeding monolithic amplifiers.

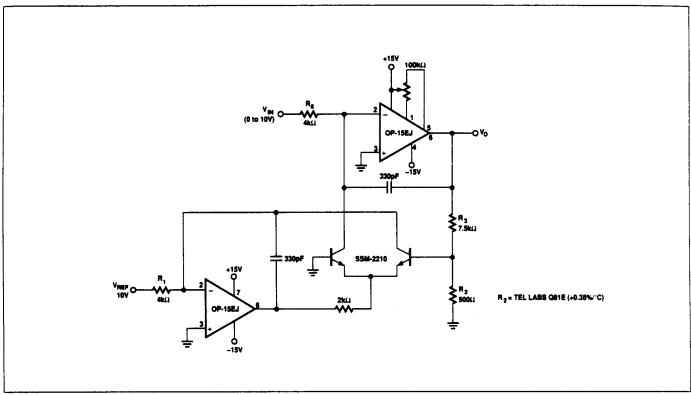

FIGURE 11: Fast Logarithmic Amplifier

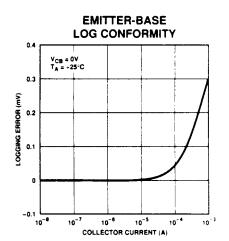

# **FAST LOGARITHMIC AMPLIFIER**

The circuit of Figure 11 is a modification of a standard logarithmic amplifier configuration. Running the SSM-2210 at 2.5mA per side (full-scale) allows a fast response with wide dynamic range. The circuit has a 7 decade current range, a 5 decade voltage range, and is capable of 2.5 $\mu s$  settling time to 1% with a 1 to 10V step.

The output follows the equation:

$$V_{O} = \frac{R_{3} + R_{2}}{R_{2}} \frac{kT}{q} \text{ In } \frac{V_{REF}}{V_{IN}}$$

To compensate for the temperature dependence of the kT/q term, a resistor with a positive 0.35%/°C temperature coefficient is chosen for  $\rm R_2$ .

The output is inverted with respect to the input, and is nominally – 1V/decade using the component values indicated.