# 36-MHz SAMPLE TWO CHANNEL CCD SIGNAL PROCESSOR

#### **FEATURES**

- TWO CHANNEL CCD SIGNAL PROCESSING:

- Correlated Double Sampling

- 75-dB SNR

- 14-BIT A/D CONVERSION:

- No Missing Codes

- PORTABLE OPERATION:

- Low Voltage: 2.7 V to 3.6 V

- Low Power: 210 mW (typ) at 2.7 V

- Power-Down Mode: 14 mW

#### **APPLICATIONS**

- Digital Video Camera (DVC)

- Digital Still Camera (DSC)

- Front End for Dual Channel CCD

#### **DESCRIPTION**

The VSP2254 is a high-speed and high-resolution mixed-signal processing IC for CCD signal processing, which integrates two channels of correlated double sampling (CDS) and a 14-bit analog-to-digital converter. The VSP2254 also provides black level clamping for an accurate black level reference, input signal clamping, and offset correction of the CDS. The VSP2254 operates from 2.7 V to 3.6 V of single supply.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SLES063 - DECEMBER 2002

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION

| PRODUCT    | PACKAGE | PACKAGE CODE | OPERATION<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER(1) | TRANSPORT<br>MEDIA |  |

|------------|---------|--------------|-----------------------------------|--------------------|-----------------------|--------------------|--|

| V0D0054001 | DO 4 00 | 001          | 0500 1- 0500                      | V0D0054            | VSP2254GSJ            | Tray               |  |

| VSP2254GSJ | BGA 96  | GSJ          | –25°C to 85°C                     | VSP2254            | VSP2254GSJR           | Tape and reel      |  |

<sup>(1)</sup> For the most current specification and package information, refer to our web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                                             | UNITS                                                |

|-------------------------------------------------------------|------------------------------------------------------|

| Supply voltage, V <sub>CC</sub> , V <sub>DD</sub>           | 4 V                                                  |

| Supply voltage differences, among V <sub>CC</sub> terminals | ±0.1 V                                               |

| Ground voltage differences, AGND, DGND                      | ±0.1 V                                               |

| Digital input voltage                                       | -0.3 V to (V <sub>DD</sub> + 0.3 V)                  |

| Analog input voltage                                        | $-0.3 \text{ V to } (\text{V}_{CC} + 0.3 \text{ V})$ |

| Input current (any pins except supplies)                    | ±10 mA                                               |

| Ambient temperature under bias                              | -40°C to 125°C                                       |

| Storage temperature, T <sub>Stg</sub>                       | −55°C to 150°C                                       |

| Junction temperature T <sub>J</sub>                         | 150°C                                                |

| Lead temperature (soldering)                                | 260°C, 5 s                                           |

| Package temperature (IR reflow, peak)                       | 260°C                                                |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

all specifications at  $T_A = 25^{\circ}C$ , all power supply voltages = 3 V, and conversion rate = 27 MHz, unless otherwise noted (1)

|                   | PARAMETER                              | TEST CONDITIONS                      | MIN TYP       | MAX | UNIT |

|-------------------|----------------------------------------|--------------------------------------|---------------|-----|------|

|                   | Resolution                             |                                      | 14            |     | Bits |

|                   | Channel                                |                                      | 2             |     |      |

|                   | Maximum conversion rate                |                                      | 36            |     | MHz  |

| DIGITA            | AL INPUTS                              |                                      | •             |     |      |

|                   | Logic family                           |                                      | CMOS          |     |      |

| V <sub>IT+</sub>  | Positive-going input threshold voltage |                                      | 1.7           |     | V    |

| V <sub>IT</sub> _ | Negative-going input threshold voltage |                                      | 1             |     | V    |

| lн                | land a mant                            | Logic high, V <sub>IN</sub> = 3 V    |               | ±20 | μА   |

| Ι <sub>Ι</sub> L  | Input current                          | Logic low, V <sub>IN</sub> = 0 V     |               | ±20 | μΑ   |

|                   | ADC clock duty cycle                   |                                      | 50%           |     |      |

|                   | Input capacitance                      |                                      | 5             |     | pF   |

| DIGITA            | L OUTPUT (Channel A/B)                 |                                      |               |     |      |

|                   | Logic family                           |                                      | CMOS          |     |      |

|                   | Logic coding                           |                                      | Straight Bina | ry  |      |

| Vон               | Output voltage                         | Logic high, $I_{OH} = -2 \text{ mA}$ | 2.4           |     | V    |

| VOL               | Output voltage                         | Logic low, IOL = 2 mA                |               | 0.4 | V    |

ELECTRICAL CHARACTERISTICS (continued) all specifications at  $T_A = 25^{\circ}C$ , all power supply voltages = 3 V, and conversion rate = 27 MHz, unless otherwise noted<sup>(1)</sup>

|                                      | PARAMETER                            | TEST CONDITIONS                                                                      | MIN      | TYP          | MAX  | UNIT           |

|--------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------|----------|--------------|------|----------------|

| ANAL                                 | OG INPUT (Channel A/B)               | •                                                                                    | •        |              |      |                |

|                                      | Input signal level for FS out        |                                                                                      | 900      |              | 1100 | mV             |

|                                      | Input capacitance                    |                                                                                      |          | 10           |      | pF             |

|                                      | Input limit                          |                                                                                      | -0.3     |              | 3.3  | V              |

| TRANS                                | SFER CHARACTERISTICS (Channel        | A/B)                                                                                 |          |              |      |                |

|                                      | Differential nonlinearity            |                                                                                      |          | ±2           |      | LSB            |

|                                      | Integral nonlinearity                |                                                                                      |          | ±8           |      | LSB            |

|                                      | No missing codes                     |                                                                                      |          | Assured      |      |                |

|                                      | Step response settling time          | Full-scale step input                                                                |          | 1            |      | pixels         |

|                                      | Overload recovery time               | Step input from 1.8 V to 0 V                                                         |          | 2            |      | pixels         |

|                                      | Data latency                         |                                                                                      |          | 8<br>(fixed) |      | clocks         |

|                                      | Signal-to-noise ratio <sup>(1)</sup> | Grounded input cap                                                                   |          | 75           |      | dB             |

|                                      | Channel separation                   | ·                                                                                    |          | 80           |      | dB             |

|                                      | CCD offset correction range          |                                                                                      | -180     |              | 200  | mV             |

|                                      | Optical black clamp level            |                                                                                      |          | 512          |      | LSB            |

| CDS (                                | Channel A/B)                         |                                                                                      |          |              |      |                |

|                                      | Reference sample settling time       | Within 1 LSB, driver impedance = 50 $\Omega$                                         |          | 6.9          |      | ns             |

|                                      | Data sample settling time            | Within 1 LSB, driver impedance = $50 \Omega$                                         |          | 6.9          |      | ns             |

| INPUT                                | CLAMP (Channel A/B)                  |                                                                                      |          |              |      |                |

|                                      | Clamp-on resistance                  |                                                                                      |          | 400          |      | Ω              |

|                                      | Clamp level                          |                                                                                      |          | 1.5          |      | V              |

| OBCL                                 | PLOOP                                |                                                                                      |          |              |      |                |

|                                      | DAC resolution                       |                                                                                      |          | 10           |      | bits           |

|                                      | Minimum DAC output current           |                                                                                      |          | ±0.15        |      | μА             |

|                                      | Maximum DAC output current           |                                                                                      |          | ±153         |      | <u>.</u><br>μΑ |

|                                      | Loop time constant                   | Time constant for ADCOUT code from 0 LSB to 1543 LSB (14 bit), $C_{COB} = 0.1 \mu F$ |          | 40.7         |      | μs             |

|                                      | Slew rate                            | ADCOUT CODE above 1543 LSB (14 bit),<br>CCOB = 0.1 µF                                |          | 1530         |      | V/s            |

| REFER                                | RENCE (Channel A/B)                  | ·                                                                                    |          |              | ·    |                |

|                                      | Positive reference voltage           |                                                                                      |          | 1.75         |      | V              |

|                                      | Negative reference voltage           |                                                                                      |          | 1.25         |      | V              |

| POWE                                 | R SUPPLY                             | 1                                                                                    | 1        |              |      |                |

| V <sub>CC</sub> ,<br>V <sub>DD</sub> | Supply voltage                       |                                                                                      | 2.7      | 3            | 3.6  | V              |

| PD                                   | Power dissipation                    | At $V_{CC} = 3 \text{ V}$ , $f_{CLK} = 36 \text{ MHz}$                               |          | 210          |      | mW             |

|                                      |                                      | Power-down mode (f <sub>CLK</sub> = 0 MHz)                                           |          | 14           |      | mW             |

| TEMPI                                | ERATURE RANGE                        |                                                                                      | <u> </u> |              |      |                |

|                                      | Operation temperature                |                                                                                      | -25      |              | 85   | °C             |

| θЈΑ                                  | Thermal resistance                   |                                                                                      |          | 55           |      | °C/W           |

<sup>(1)</sup> SNR = 20 log (full-scale voltage/rms noise)

# **PIN ASSIGNMENTS**

| , | 1     | 2     | 3     | 4    | 5     | 6     | 7     | 8      | 9       | 10      |

|---|-------|-------|-------|------|-------|-------|-------|--------|---------|---------|

| А | SHP_A | B1_A  | B3_A  | B6_A | B8_A  | B11_A | B13_A | VCC    | NC      | NC      |

| В | SHD_A | BO_A  | B2_A  | B5_A | B9_A  | B10_A | AGND  | COB_A  | BYPCM_A | BYPM_A  |

| С | NC    | AGND  | VCC   | B4_A | B7_A  | B12_A | AGND  | BYPP_A | AGND    | CCDIN_A |

| D | ADCCK | NC    | NC    | NC   | NC    | NC    | NC    | VCC    | REFN_A  | CM_A    |

| Е | VDD   | DGND  | STB   | NC   |       |       | NC    | NC     | AGND    | REFP_A  |

| F | AGND  | DGND  | CLPDM | NC   |       |       | NC    | NC     | VCC     | REFP_B  |

| G | CLPOB | PBLK  | NC    | NC   | NC    | NC    | NC    | VCC    | REFN_B  | CM_B    |

| н | AGND  | VCC   | B2_B  | B5_B | B8_B  | B13_B | VCC   | NC     | AGND    | CCDIN_B |

| J | SHD_B | SHP_B | B3_B  | B6_B | B10_B | B11_B | AGND  | BYPP_B | NC      | BYPM_B  |

| К | B0_B  | B1_B  | B4_B  | B7_B | B9_B  | B12_B | AGND  | COB_B  | NC      | BYPCM_B |

NOTE: The corner of the A1 position is indicated on the device top by a dot.

# **Terminal Functions**

| -       | ΓΕΡΜΙΝΔΙ                                  |         | TERMINAL                                                                            |  |  |  |  |  |  |  |  |

|---------|-------------------------------------------|---------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| NAME    | NO.                                       | TYPE(1) | DESCRIPTION                                                                         |  |  |  |  |  |  |  |  |

| ADCCK   | D1                                        | DI      | Clock for ADC output                                                                |  |  |  |  |  |  |  |  |

| AGND    | B7, C2, C7, C9, E9,<br>F1, H1, H9, J7, K7 | Р       | Analog ground                                                                       |  |  |  |  |  |  |  |  |

| B0_A    | B2                                        | DO      | A-channel ADC output bit 0                                                          |  |  |  |  |  |  |  |  |

| B0_B    | K1                                        | DO      | B-channel ADC output bit 0 (LSB)                                                    |  |  |  |  |  |  |  |  |

| B1_A    | A2                                        | DO      | A-channel ADC output bit 1                                                          |  |  |  |  |  |  |  |  |

| B1_B    | K2                                        | DO      | B-channel ADC output bit 1                                                          |  |  |  |  |  |  |  |  |

| B10_A   | B6                                        | DO      | A-channel ADC output bit 10                                                         |  |  |  |  |  |  |  |  |

| B10_B   | J5                                        | DO      | B-channel ADC output bit 10                                                         |  |  |  |  |  |  |  |  |

| B11_A   | A6                                        | DO      | A-channel ADC output bit 11                                                         |  |  |  |  |  |  |  |  |

| B11_B   | J6                                        | DO      | B-channel ADC output bit 11                                                         |  |  |  |  |  |  |  |  |

| B12_A   | C6                                        | DO      | A-channel ADC output bit 12                                                         |  |  |  |  |  |  |  |  |

| B12_B   | K6                                        | DO      | B-channel ADC output bit 12                                                         |  |  |  |  |  |  |  |  |

| B13_A   | A7                                        | DO      | A-channel ADC output bit 13 (MSB)                                                   |  |  |  |  |  |  |  |  |

| B13_B   | H6                                        | DO      | B-channel ADC output bit 13 (MSB)                                                   |  |  |  |  |  |  |  |  |

| B2_A    | В3                                        | DO      | A-channel ADC output bit 2                                                          |  |  |  |  |  |  |  |  |

| B2_B    | H3                                        | DO      | B-channel ADC output bit 2                                                          |  |  |  |  |  |  |  |  |

| B3_A    | А3                                        | DO      | A-channel ADC output bit 3                                                          |  |  |  |  |  |  |  |  |

| B3_B    | J3                                        | DO      | B-channel ADC output bit 3                                                          |  |  |  |  |  |  |  |  |

| B4_A    | C4                                        | DO      | A-channel ADC output bit 4                                                          |  |  |  |  |  |  |  |  |

| B4_B    | K3                                        | DO      | B-channel ADC output bit 4                                                          |  |  |  |  |  |  |  |  |

| B5_A    | B4                                        | DO      | A-channel ADC output bit 5                                                          |  |  |  |  |  |  |  |  |

| B5_B    | H4                                        | DO      | B-channel ADC output bit 5                                                          |  |  |  |  |  |  |  |  |

| B6_A    | A4                                        | DO      | A-channel ADC output bit 6                                                          |  |  |  |  |  |  |  |  |

| B6_B    | J4                                        | DO      | B-channel ADC output bit 6                                                          |  |  |  |  |  |  |  |  |

| B7_A    | C5                                        | DO      | A-channel ADC output bit 7                                                          |  |  |  |  |  |  |  |  |

| B7_B    | K4                                        | DO      | B-channel ADC output bit 7                                                          |  |  |  |  |  |  |  |  |

| B8_A    | A5                                        | DO      | A-channel ADC output bit 8                                                          |  |  |  |  |  |  |  |  |

| B8_B    | H5                                        | DO      | B-channel ADC output bit 8                                                          |  |  |  |  |  |  |  |  |

| B9_A    | B5                                        | DO      | A-channel ADC output bit 9                                                          |  |  |  |  |  |  |  |  |

| B9_B    | K5                                        | DO      | B-channel ADC output bit 9                                                          |  |  |  |  |  |  |  |  |

| BYPCM_A | B9                                        | AO      | A-channel CDS common reference, bypass-to-ground by a 0.1-μF capacitor              |  |  |  |  |  |  |  |  |

| BYPCM_B | K10                                       | AO      | B-channel CDS common reference, bypass-to-ground by a 0.1-μF capacitor              |  |  |  |  |  |  |  |  |

| BYPM_A  | B10                                       | AO      | A-channel CDS negative reference, bypass-to-ground by a 500-pF to 1000-pF capacitor |  |  |  |  |  |  |  |  |

| BYPM_B  | J10                                       | AO      | B-channel CDS negative reference, bypass-to-ground by a 500-pF to 1000-pF capacitor |  |  |  |  |  |  |  |  |

| BYPP_A  | C8                                        | AO      | A-channel CDS positive reference, bypass-to-ground by a 500-pF to 1000-pF capacitor |  |  |  |  |  |  |  |  |

| BYPP_B  | J8                                        | AO      | B-channel CDS positive reference, bypass-to-ground by a 500-pF to 1000-pF capacitor |  |  |  |  |  |  |  |  |

| CCDIN_A | C10                                       | Al      | A-channel CCD signal input                                                          |  |  |  |  |  |  |  |  |

| CCDIN_B | H10                                       | Al      | B-channel CCD signal input                                                          |  |  |  |  |  |  |  |  |

| CLPDM   | F3                                        | DI      | Dummy clamp pulse, (active low)                                                     |  |  |  |  |  |  |  |  |

<sup>(1)</sup> P: Power Supply and Ground, DI: Digital Input, DO: Digital Output, AI: Analog Input, AO: Analog Output.

# **Terminal Functions (Continued)**

| TERMINAL |                                                                                         | ->(1)   | DECORPTION                                                                   |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO.                                                                                     | TYPE(1) | DESCRIPTION                                                                  |  |  |  |  |

| CLPOB    | G1                                                                                      | DI      | Optical black clamp pulse, (active low)                                      |  |  |  |  |

| CM_A     | D10                                                                                     | AO      | A-channel ADC common reference, bypass-to-ground by a 0.1-μF capacitor       |  |  |  |  |

| CM_B     | G10                                                                                     | AO      | B-channel ADC common reference, bypass-to-ground by a 0.1-μF capacitor       |  |  |  |  |

| COB_A    | B8                                                                                      | AO      | A-channel OBC loop output voltage, connect a 0.1-μF capacitor between ground |  |  |  |  |

| COB_B    | K8                                                                                      | AO      | B-channel OBC loop output voltage, connect a 0.1-μF capacitor between ground |  |  |  |  |

| DCND     | E2                                                                                      | Р       | Digital ground for digital outputs                                           |  |  |  |  |

| DGND F2  |                                                                                         | Р       | Digital ground for digital outputs                                           |  |  |  |  |

| NC       | A9, A10, C1, D2, D3,<br>D4, D5, D6, D7, E4,<br>E7, E8, F4, F7, F8,<br>G3–G7, H8, J9, K9 | -       | Not connected, must be open                                                  |  |  |  |  |

| PBLK     | G2                                                                                      | DI      | A/D output preblanking. Low: all 0, High: normal output                      |  |  |  |  |

| REFN_A   | D9                                                                                      | AO      | A-channel ADC negative reference, bypass-to-ground a 0.1-μF capacitor        |  |  |  |  |

| REFN_B   | G9                                                                                      | AO      | B-channel ADC negative reference, bypass-to-ground by a 0.1-μF capacitor     |  |  |  |  |

| REFP_A   | E10                                                                                     | AO      | A-channel ADC positive reference, bypass-to-ground by a 0.1-μF capacitor     |  |  |  |  |

| REFP_B   | F10                                                                                     | AO      | B-channel ADC positive reference, bypass-to-ground by a 0.1-μF capacitor     |  |  |  |  |

| SHD_A    | B1                                                                                      | DI      | A-channel CCD data sampling pulse, (active low)                              |  |  |  |  |

| SHD_B    | J1                                                                                      | DI      | B-channel CCD data sampling pulse, (active low)                              |  |  |  |  |

| SHP_A    | A1                                                                                      | DI      | A-channel CCD ref sampling pulse, (active low)                               |  |  |  |  |

| SHP_B    | J2                                                                                      | DI      | B-channel CCD ref sampling pulse, (active low)                               |  |  |  |  |

| STB      | E3                                                                                      | DI      | Standby, low: normal operation, high: standby                                |  |  |  |  |

| VCC      | A8, C3, D8, E1, F9,<br>G8, H2 H7                                                        | Р       | Analog power supply                                                          |  |  |  |  |

| VDD      | E1                                                                                      | Р       | Digital supply for digital outputs                                           |  |  |  |  |

<sup>(1)</sup> P: Power Supply and Ground, DI: Digital Input, DO: Digital Output, AI: Analog Input, AO: Analog Output.

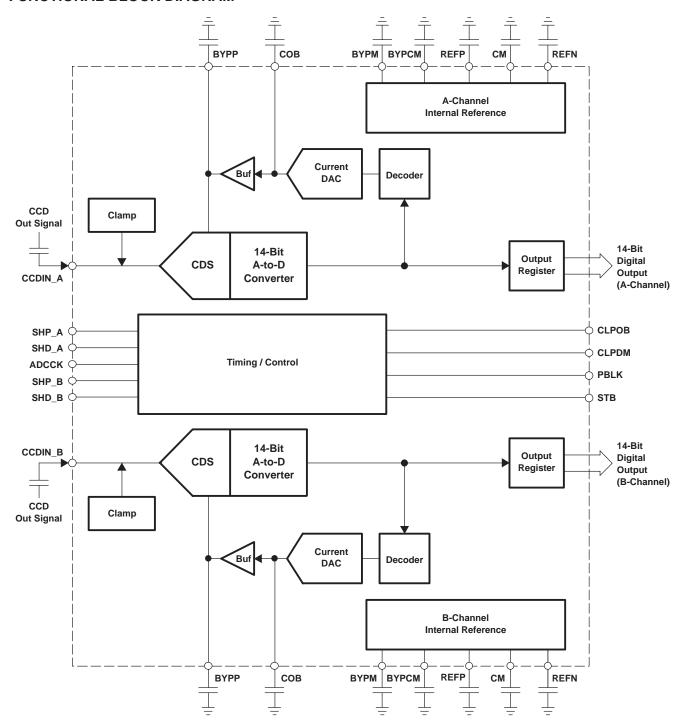

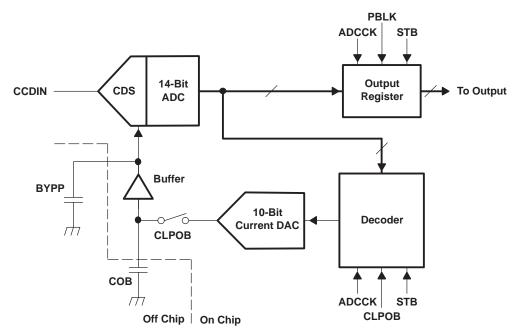

# **FUNCTIONAL BLOCK DIAGRAM**

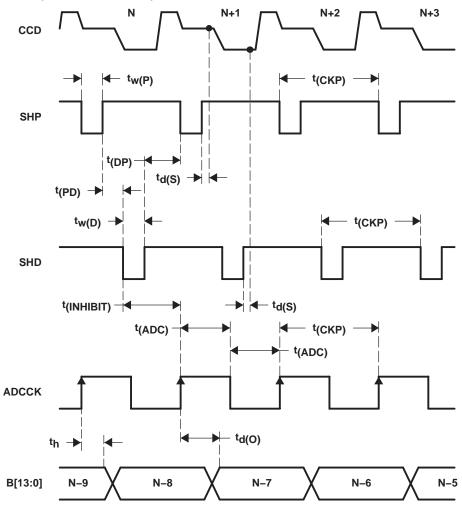

# **TIMING SPECIFICATION**

# **Timing Specifications (for each channel)**

| •                  | PARAMETER                           | N | VIIN | MAX  | MAX | UNIT   |

|--------------------|-------------------------------------|---|------|------|-----|--------|

| t(CKP)             | Clock period                        |   | 27   |      |     | ns     |

| t(ADC)             | ADCCK high or low level             |   | 10   | 13.8 |     | ns     |

| t <sub>w(P)</sub>  | SHP pulse width                     |   |      | 6.9  |     | ns     |

| t <sub>w(D)</sub>  | SHD pulse width                     |   |      | 6.9  |     | ns     |

| t(PD)              | SHP rising edge to SHD falling edge |   | 4    |      |     | ns     |

| t(DP)              | SHD rising edge To SHP falling edge |   |      | 6.9  |     | ns     |

| td(S)              | Sampling delay                      |   |      | 3    |     | ns     |

| t(INHIBIT)         | Inhibited clock period              |   | 10   |      | 20  | ns     |

| t <sub>h</sub>     | Output hold time                    |   | 7    |      |     | ns     |

| t <sub>d</sub> (O) | Output delay                        |   |      |      | 27  | ns     |

| DL                 | Data latency                        |   |      | 8    |     | clocks |

<sup>(1)</sup> t<sub>(WP)</sub> + t<sub>(PD)</sub> should be nearly equal to t<sub>(WD)</sub> + t<sub>(DP)</sub>.

#### SYSTEM OVERVIEW

#### Introduction

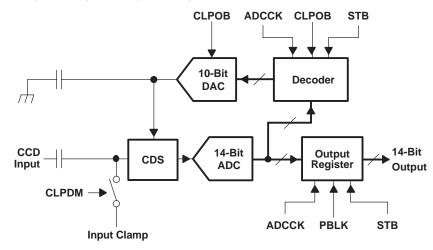

The VSP2254 is a two channel high-resolution mixed-signal IC that contains key features associated with the processing of the CCD signal in a DVC. The VSP2254 integrates two channels of independent CCD processing path. Figure 1 shows a simplified block diagram of one channel of the VSP2254. The device includes a correlated double sampler (CDS), a 14-bit analog to digital converter (ADC), a black-level clamp loop, input clamp, timing generator, and voltage reference. An off-chip emitter follower buffer or preamp is needed between the CCD output and the VSP2254 CCDIN input. Both channels are driven common SHP/SHD, ADCCK, CLPOB, CLPDM, and STB.

Figure 1. Simplified Block Diagram of VSP2254 (One Channel)

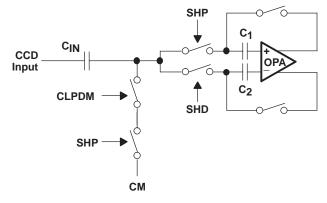

#### **Correlated Double Sampler (CDS)**

The output signal of a CCD image sensor is sampled twice during one pixel period: once at the reference interval and again at the data interval. Subtracting these two samples extracts the video information of the pixel and removes any noise which is common—or correlated—to both the intervals. Thus, a CDS is important to reduce the reset noise and the low-frequency noises that are present on the CCD output signal. Figure 2 shows the block diagram of the CDS.

The CDS is driven through an off-chip coupling capacitor  $C_{IN}$ . (A 0.1- $\mu$ F capacitor is recommended for  $C_{IN}$ .) AC-coupling is highly recommended, because the dc level of the CCD output signal is usually too high (several volts) for the CDS to work properly. The appropriate common-mode voltage for the CDS is around 0.5 V-1.5 V. The reference level sampling is performed while SHP is active and the voltage level is held on the sampling capacitor  $C_1$  at the trailing edge of SHP. The data level sampling is performed while SHD is active and the voltage level is held on the sampling capacitor  $C_2$  at the trailing edge of SHD. Then the subtraction of the two levels is performed by the switched-capacitor amplifier. The off-chip emitter follower buffer must be able to drive more than 10 pF, because the 10-pF sampling capacitor is seen at the input pin. (Usually, additional stray capacitance of a few pico farads is present.) The analog input signal range of the VSP2254 is about 1 Vp-p.

Figure 2. Block Diagram of CDS and Input Clamp

#### Input Clamp

The buffered CCD output is capacitively coupled to the VSP2254. The purpose of the input clamp is to restore the dc component of the input signal, which was lost with the ac-coupling and establish the desired dc bias point for the CDS. Figure 2 shows the block diagram of the input clamp. The input level is clamped to the internal reference voltage CM (1.5 V) during the dummy pixel interval. More specifically, the clamping function becomes active when both CLPDM and SHP are active.

#### 14-Bit A/D Converter

The ADC utilizes a fully differential pipelined architecture of 1.5 bit per stage, which is well-suited for low-power, low-voltage and high-speed applications. The ADC assures 14-bit resolution for the entire full scale. The 1.5 bit per stage structure of the ADC is advantageous to realize a better linearity for a smaller signal level, because large linearity errors tend to occur at specific points in the full scale and the linearity gets better for a level of signal below that specific point.

#### Black Level Clamp Loop and 10-Bit DAC

To extract the video information correctly, the CCD signal must be referenced to a well-established black level. The VSP2254 has an auto-zero loop (calibration loop) to establish the black level using the CCD's optical black (OB) pixels. Figure 3 shows the block diagram of the black level clamp loop. The input signal level from the OB pixels is identified as the real black level and the loop is closed during this period (actually during the period while CLPOB = ACTIVE). While the auto-zero loop is closed, the difference between the ADC output code is evaluated and applied to the decoder, which then controls the 10-bit current DAC. The current DAC can charge or discharge the external capacitor at COB, dependent on the sign of the code difference. The loop adjusts the voltage at COB, which sets the offset of the CDS so as to make the code difference zero. Thus, the ADC output code converges to black level during CLPOB = ACTIVE and the black level derived from the OB pixels after the loop has converged. CLPOB performs OB clamp of both channels simultaneously.

A 0.1- $\mu$ F bypass capacitor is recommended for COB and with this capacitor, the loop's time constant is 40.7  $\mu$ s (typ) for the ADC output code from 0 LSB to 1543 LSB (the convergence curve becomes exponential). For the output code above 1543 LSB, the current DAC injects constant (maximum) current into the capacitor and the convergence curve becomes linear. The slew rate for that is 1530 V/s (typ). The loop not only eliminates the CCD's own black level offset, but also eliminates the offset of the VSP2254's CDS and ADC themselves.

Figure 3. Block Diagram of Digital PGA and Black Level Clamp Loop

#### **Preblanking and Data Latency**

The VSP2254 has an input blanking (or preblanking) function. When PBLK = low, digital outputs all become zero at the ninth rising edge of ADCCK, counting from when PBLK becomes low to accommodate the clock latency of the VSP2254.

Data latency of the VSP2254 is seven clock cycles. The digital output data comes out at the rising edge of ADCCK with a delay of seven clock cycles.

Some CCDs have large transient output signals during blanking intervals. If the input voltage is higher than the supply rail or lower than the ground rail by 0.3 V, then protection diodes are turned on preventing the input voltage from going further. Such a high-swing signal may cause damage to the VSP2254 and should be avoided.

#### Standby Mode

For the purpose of power saving, the VSP2254 can be put into the standby mode (power-down mode) by forcing the STB input to a high level when the device is not in use. In this mode, all the function blocks are disabled and the digital outputs all go to zero. The consumption current drops to 5 mA. As all the bypass capacitors discharge during this mode, a substantial time (usually of the order of 200 ms–300 ms) is required to restore from the standby mode. STB is effective for both channels.

#### **Timings**

The CDS and the ADC are operated by SHP, SHD, and their derivative timing clocks generated by the on-chip timing generator. The output register and decoder are operated by ADCCK. The digital output data is synchronized with ADCCK. The timing relationship between the CCD signal, SHP, SHD, ADCCK, and the output data is shown on the VSP2254 timing specification. CLPOB is used to activate the black level clamp loop during the OB pixel interval and CLPDM is used to activate the input clamping during the dummy pixel interval. In the standby mode, ADCCK, SHP, SHD, CLPOB, and CLPDM are internally masked and pulled high.

#### Voltage Reference

All the reference voltages and bias currents used on the device are created from an internal band gap circuitry. The VSP2254 has symmetrical independent voltage reference for each channel.

Both channels of the CDS and the ADC use three main reference voltages, REFP (1.75 V), REFN (1.25 V), and CM (1.5 V) of the individual reference. REFP and REFN are buffered on-chip. CM is derived as the mid-voltage of the resistor chain connecting REFP and REFN internally. The ADC's full scale range is determined by twice the difference voltage between REFP and REFN.

REFP, REFN, and CM should be heavily decoupled with appropriate capacitors.

#### Power Supply, Grounding, and Device Decoupling Recommendations

The VSP2254 incorporates a high-precision, high-speed AD converter and analog circuitry, which are vulnerable to any extraneous noise from the rails or elsewhere.

The driver stage of the digital outputs (B[13:0]) is supplied through a dedicated supply pin (VDD) and should be separated from the other supply pins completely or at least with a ferrite bead. This ensures the most consistent results, since digital power lines often carry high levels of wide-band noise that would otherwise be coupled into the device and degrade the achievable performance. It is ecommended that analog and digital ground pins of the VSP2254 be separated.

Proper grounding, short lead length, and the use of ground planes are also important for high-frequency designs. Multilayer PC boards are recommended for the best performance, since they offer distinct advantages like minimizing ground impedance, separation of signal layers by ground layers, etc.

It is also recommended to keep the capacitive loading on the output data lines as low as possible (typically less than 15 pF). Larger capacitive loads demand higher charging current surges, which can feed back into the analog portion of the VSP2254 and affect the performance. If possible, external buffers or latches should be used, which provide the added benefit of isolating the VSP2254 from any digital noise activities on the data lines. In addition, resistors in series with each data line may help minimizing the surge current. Values in the range of  $100~\Omega$  to  $200~\Omega$  limits the instantaneous current the output stage has to provide for recharging the parasitic capacitance as the output levels change from low-to-high or high-to-low.

Because of the high-operation speed, the converter also generates high-frequency current transients and noises that are fed back into the supply and reference lines. This requires the supply and reference pins to be sufficiently bypassed. In most cases, 0.1- $\mu$ F ceramic chip capacitors are adequate to decouple the reference pins. Supply pins should be decoupled to the ground plane with a parallel combination of tantalum (1  $\mu$ F-22  $\mu$ F) and ceramic (0.1  $\mu$ F) capacitors. The effectiveness of the decoupling largely depends on the proximity to the individual pin. VDD should be decoupled to the proximity of DGND.

Attention must be paid to the bypassing of COB, BYPP, and BYPM, since these capacitor values determine important analog performances of the device.

www.ti.com 13-Feb-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type               | Package<br>Drawing |    | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|----------------------------|--------------------|----|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| VSP2254GSJ       | ACTIVE | BGA<br>MICROSTAR<br>JUNIOR | ZSJ                | 96 | 168         | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | 0 to 85      | VSP2254           | Samples |

| VSP2254ZSJ       | ACTIVE | BGA<br>MICROSTAR<br>JUNIOR | ZSJ                | 96 | 168         | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | 0 to 85      | VSP2254           | Samples |

| VSP2254ZSJG1     | ACTIVE | BGA<br>MICROSTAR<br>JUNIOR | ZSJ                | 96 | 168         | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | 0 to 85      | VSP2254           | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>&</sup>lt;sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

13-Feb-2013

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>