**Process F2**

# National Semiconductor

#### DESCRIPTION

These dice are n-channel, enhancement mode, power MOSFETs designed especially for high power, high speed applications, such as power supplies, AC and DC motor control and high energy pulse circuits.

**N-Channel Power MOSFET**

This process is available in the following device types:

| TO-204 (Case 43) | TO-247 (Case 40) |  |  |  |

|------------------|------------------|--|--|--|

| IRF250CF         | IRFP250CF        |  |  |  |

| IRF250           | IRFP250          |  |  |  |

| IRF251           | IRFP251          |  |  |  |

| IRF252           | IRFP252          |  |  |  |

| IRF253           | IRFP253          |  |  |  |

|                  |                  |  |  |  |

#### Electrical Characteristics T<sub>C</sub> = 25°C (unless otherwise noted)

| Symbol              | Parameter                        | Test Conditions                                                                                                                                             | Min | Max   | Units   |

|---------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------|

| V <sub>DSS</sub>    | Drain to Source Voltage (Note 1) | $I_{\rm D} = 250 \ \mu \text{A}; V_{\rm GS} = 0 \text{V}$                                                                                                   | 200 |       | V       |

| IDSS                | Zero Gate Voltage Drain          | $V_{DS} = Rated Voltage$<br>$V_{GS} = 0V$                                                                                                                   |     | 250   | μΑ      |

| IGSS                | Gate Leakage Current             | $V_{DS} = \pm 20V; V_{DS} = 0V$                                                                                                                             |     | ±100  | nA      |

| V <sub>GS(TH)</sub> | Gate Threshold Voltage           | $I_{D} = 250 \ \mu A; V_{DS} = V_{GS}$                                                                                                                      | 2.0 | 4.0   | V       |

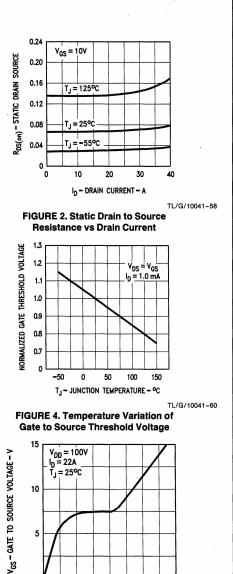

| R <sub>DS(ON)</sub> | Static On-Resistance (Note 2)    | $V_{GS} = 10V; I_{D} = 16A$                                                                                                                                 |     | 0.085 | Ω       |

| 9FS                 | Forward Transconductance         | $V_{DS} = 10V; I_D = 16A$                                                                                                                                   | 8.0 |       | Siemens |

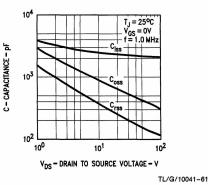

| C <sub>iss</sub>    | Input Capacitance                | $V_{DS} = 25V; V_{GS} = 0V$<br>f = 1 MHz                                                                                                                    |     | 3000  | pF      |

| Coss                | Output Capacitance               |                                                                                                                                                             |     | 1200  | pF      |

| C <sub>rss</sub>    | Reverse Transfer                 |                                                                                                                                                             |     | 500   | pF      |

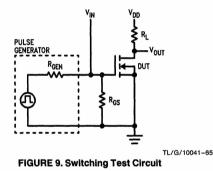

| <sup>t</sup> d(on)  | Turn-On Delay Time               | $\begin{split} V_{\text{DD}} &= 95\text{V}; \text{I}_{\text{D}} = 16\text{A} \\ V_{\text{GS}} &= 10\text{V}; \text{R}_{\text{GEN}} = 4.7\Omega \end{split}$ |     | 75    | ns      |

| t <sub>r</sub>      | Rise Time                        | $R_{GS} = 4.7\Omega$                                                                                                                                        |     | 300   | ns      |

| t <sub>d(off)</sub> | Turn-Off Delay Time              |                                                                                                                                                             |     | 275   | ns      |

| t <sub>f</sub>      | Fall Time                        |                                                                                                                                                             |     | 150   | ns      |

| Qg                  | Total Gate Charge                | $V_{GS} = 10V; I_D = 38A$<br>$V_{DD} = 100V$                                                                                                                |     | 120   | nC      |

Note 1:  $T_J = +25^{\circ}C$  to  $+150^{\circ}C$ .

Note 2: Pulse Test: Pulse Width  $\leq$  80  $\mu s,$  Duty Cycle  $\leq$  1%.

# Process F2

## **Process F2**

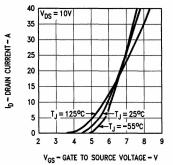

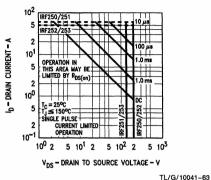

**FIGURE 3. Transfer Characteristics**

TL/G/10041-59

11-268

0

40

80

Qg - TOTAL GATE CHARGE - nC

FIGURE 6. Gate to Source Voltage vs Total Gate Charge

120

160

TL/G/10041-62

## **Process F2**

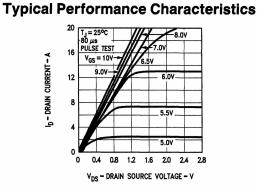

## **Typical Performance Characteristics (Continued)**

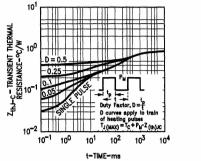

FIGURE 7. Forward Biased Safe Operating Area

## **Typical Electrical Characteristics**

TL/G/10041-64

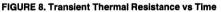

#### FIGURE 10. Switching Waveforms

### **Probe Testing**

Each die is probed and electrically tested to the limits specified in the Electrical Characteristics Table. However, high current parameters and thermal characteristics specified in the packaged device data sheets cannot be tested or guaranteed in die form because of the power dissipation limits of unmounted die and current handling limits of probe tips.

These parameters are: Thermal Resistance Forward Voltage Drop at Rated Current Reverse Recovery Characteristics at Rated Current Surge Current