# The AMD x86-64™ Architecture Programmers Overview

Publication # 24108 Rev: A Issue Date: August 2000

### **Preliminary Information**

© 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

$AMD, the \,AMD\, logo, x86-64, AMD\, Athlon, and \, combinations\, thereof\, are\, trademarks\, of\, Advanced\, Micro\, Devices,\, Inc.$

MMX is a trademark of Intel Corporation.

Windows NT is a trademark of Microsoft Corp.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

### **Contents**

| Introduction                                       | 1  |

|----------------------------------------------------|----|

| Motivation for a 64-Bit Architecture               | 1  |

| Features of the x86-64 <sup>TM</sup> Architecture  |    |

| Long Mode                                          |    |

| 64-Bit Mode                                        |    |

| Compatibility Mode                                 | 5  |

| Legacy Mode                                        | 5  |

| Definitions                                        | 6  |

| Notation                                           |    |

| Registers                                          | 7  |

| Application Programming                            | 9  |

| Overview                                           | 9  |

| Application Software Registers and Data Structures |    |

| CPUID                                              |    |

| Application Registers                              |    |

| General-Purpose Registers (GPRs)                   |    |

| Streaming SIMD Extension (SSE) Registers           |    |

| Memory Organization                                |    |

| Address Calculations in 64-Bit Mode                |    |

| FS and GS As Base of Address Calculation           | 16 |

| Instruction-Set Conventions                        | 17 |

| Address-Size and Operand-Size Prefixes             |    |

| REX Prefixes                                       |    |

| REX Prefix Fields                                  |    |

| Displacement                                       |    |

| Direct Memory-Offset MOVs                          |    |

| Immediates                                         |    |

| RIP-Relative Addressing                            |    |

| Default 64-Bit Operand Size                        |    |

| Stack Pointer                                      |    |

| Branches                                           |    |

| System Programming                                 |    |

| Overview                                           |    |

| Canonical Address Form                             |    |

| CPUID                                              |    |

| System Registers                                   |    |

| Extended Feature Enable Register (EFER)            |    |

| Control Registers                                  |    |

| Descriptor Table Registers                         |    |

| Debug Registers                                    |    |

| Enabling and Activating Long Mode                  |    |

| Processor Modes                                    | 35 |

|            | Activating Long Mode                                 |      |

|------------|------------------------------------------------------|------|

|            | Virtual-8086 Mode                                    |      |

|            | Compatibility Mode: Support for Legacy Applications  |      |

|            | Long-Mode Semantics                                  |      |

|            | Switching Between 64-Bit Mode and Compatibility Mode |      |

|            | Segmentation                                         |      |

|            | Code Segments                                        |      |

|            | Data and Stack Segments                              |      |

|            | System Descriptors                                   |      |

|            | Virtual Addressing and Physical Address Size         |      |

|            | Virtual-Address and Physical-Address Size            |      |

|            | Enhanced Legacy-Mode Paging                          |      |

|            | CR2 and CR3                                          |      |

|            | Address Translation                                  |      |

|            | Privilege-Level Transitions and Far Transfers        |      |

|            | Call Gates                                           |      |

|            | SYSCALL and SYSRET                                   |      |

|            | Task State Segments                                  |      |

|            | Interrupts                                           |      |

|            | Gate Descriptor Format                               |      |

|            | Stack Frame                                          |      |

|            | IRET                                                 | 67   |

|            | Stack Switching                                      | 68   |

|            | Task Priority                                        | . 70 |

| Appendix A | Integer Instructions in 64-Bit Mode                  | . 73 |

|            | General Rules                                        |      |

|            | Operand Size in 64-Bit Mode                          | . 73 |

|            | Instruction Differences                              | . 93 |

|            | Invalid Instructions                                 | 93   |

|            | Single-Byte INC and DEC Instructions                 | 94   |

|            | NOP                                                  |      |

|            | MOVSXD                                               |      |

|            | Instructions that Reference RSP                      |      |

|            | Segment-Override Prefixes in 64-Bit Mode             |      |

|            | FXSAVE and FXRSTOR                                   |      |

|            | New Encodings for Control and Debug Registers        | 97   |

| Appendix B | Long Mode Differences                                | . 98 |

| Appendix C | Initialization Example                               | 100  |

| Appendix D | Implementation Considerations                        | 105  |

|            | Address Size                                         |      |

|            | Operand Alignment                                    |      |

|            | CR8 Interactions with APIC                           |      |

|            | Physical Address Fields in MSRs                      |      |

|            | ,                                                    | ,    |

### Introduction

AMD 64-bit technology includes the x86-64™ architecture, which is a 64-bit extension of the x86 architecture. The x86-64 architecture supports legacy 16-bit and 32-bit applications and operating systems without modification. It provides recompiled 64-bit applications and operating systems with these new features:

- 64-bit flat virtual addressing.

- 8 new general-purpose registers (GPRs).

- 8 new registers for streaming SIMD extensions (SSE).

- 64-bit-wide GPRs and instruction pointer.

The x86-64 architecture has a legacy mode in which it supports binary compatibility with existing operating systems and applications, and a new mode in which it supports both the new features for recompiled code as well as binary compatibility with existing applications. The architecture also adds a new instruction-pointer relative-addressing mode, uniform byteregister addressing, and a fast interrupt-prioritizing mechanism.

This document describes the new features of AMD's x86-64 architecture and their differences from legacy x86 architecture.

### **Motivation for a 64-Bit Architecture**

The need for a 64-bit x86 architecture is driven by applications that address large amounts of virtual and physical memory, such as high-performance servers, database management systems, and CAD tools. These applications benefit from both 64-bit addresses and an increased number of registers.

The small number of registers available in the legacy x86 architecture also limits performance in computation-intensive applications such as graphics transform and lighting, circuit simulation, and scientific algorithms. Increasing the number of registers provides a performance boost to many applications.

24108A - August 2000

### Features of the x86-64™ Architecture

The x86-64 architecture extends the legacy x86 architecture by introducing two major features: a 64-bit extension called *long mode* and register extensions.

### **Long Mode**

Long mode consists of two sub-modes: 64-bit mode and compatibility mode. Compatibility mode supports binary compatibility with existing 16-bit and 32-bit applications. In addition to long mode, the architecture also supports a pure x86 legacy mode, which preserves binary compatibility not only with existing 16-bit and 32-bit applications but also with existing 16-bit and 32-bit operating systems.

Table 1 shows the supported operating modes.

Throughout this document, references to *long mode* refer to both *64-bit mode* and *compatibility mode*. If a function is specific to either 64-bit mode or compatibility mode, then those specific names are used instead of the name *long mode*.

| iable i. Oberaulig mode | <b>Table</b> | 1. | Operating | Modes |

|-------------------------|--------------|----|-----------|-------|

|-------------------------|--------------|----|-----------|-------|

|                        |                   | Onevatina                       | Amplication                            |                           | Defaults <sup>1</sup>               |                        |     |    |  |     |    |

|------------------------|-------------------|---------------------------------|----------------------------------------|---------------------------|-------------------------------------|------------------------|-----|----|--|-----|----|

| M                      | ode               | Operating<br>System<br>Required | Recompile Address Required Size (bits) | Operand<br>Size<br>(bits) | Register<br>Extensions <sup>2</sup> | GPR<br>Width<br>(bits) |     |    |  |     |    |

|                        | 64-Bit<br>Mode    | New                             | yes                                    | 64                        | 32                                  |                        |     |    |  | yes | 64 |

| Long Mode <sup>3</sup> | Compatibility     | 64-bit OS                       | 64-bit OS no 32                        | 32                        |                                     | no                     | 32  |    |  |     |    |

|                        | Mode              |                                 |                                        | 110                       | 16                                  |                        | 110 | 32 |  |     |    |

| _                      |                   | Legacy                          |                                        | 32                        | 32                                  |                        | 70  |    |  |     |    |

| Legacy                 | Mode <sup>4</sup> | 32-bit or 16-<br>bit OS         | no                                     | 16                        | 16                                  | no                     | 32  |    |  |     |    |

- 1. Defaults can be overridden in most modes using an instruction prefix or system control bit.

- 2. Register extensions includes eight new GPRs and eight new XMM registers (also called SSE registers).

- 3. Long mode supports only x86 protected mode. It does not support x86 real mode or virtual-8086 mode. Also, it does not support task switching.

- 4. Legacy mode supports x86 real mode, virtual-8086 mode, and protected mode.

24108A – August 2000

AMD 64-Bit Technology

### 64-Bit Mode

64-bit mode supports the following new features:

- 64-bit virtual addresses (implementations can have less).

- Register extensions through a new prefix (REX):

- Adds eight GPRs (R8–R15).

- Widens GPRs to 64 bits.

- Adds eight 128-bit streaming SIMD extension (SSE) registers (XMM8–XMM15).

- 64-bit instruction pointer (RIP).

- New RIP-relative data addressing mode.

- Flat address space with single code, data, and stack space.

The default address size is 64 bits, and the default operand size is 32 bits. The defaults can be overridden on an instruction-by-instruction basis using prefixes. A new REX prefix is introduced for specifying 64-bit operand size and the new registers.

The mode is enabled by the operating system on an individual code-segment basis. Because 64-bit mode supports a 64-bit virtual-address space, it requires a 64-bit operating system and tool chain. A few instruction opcodes and prefix bytes are redefined to allow the register extensions and 64-bit addressing. These differences are described in Appendix A, "Integer Instructions in 64-Bit Mode", on page 73, and in Appendix B, "Long Mode Differences", on page 98.

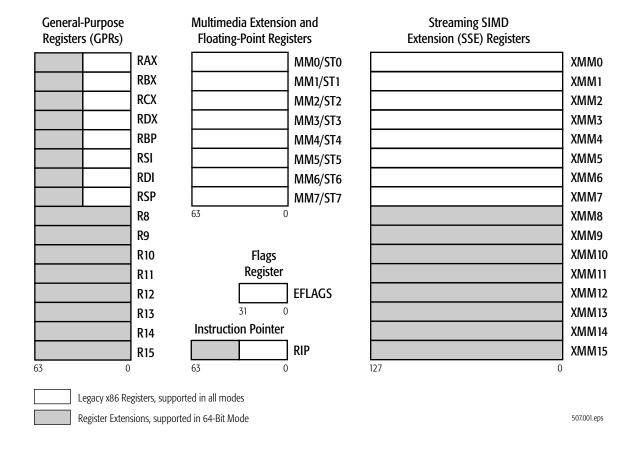

**Register Extensions.** 64-bit mode supports register extensions, shown in Figure 1, through a new REX prefix. These extensions add eight 64-bit GPRs (R8–R15), eight 128-bit streaming SIMD extensions (SSE) registers (XMM8–XMM15), and widens all GPRs to 64 bits.

The REX prefix also provides a new byte-register capability that makes the least-significant byte of any GPR available for byte operations. This results in a uniform set of byte, word, dword, and qword registers better suited for a compiler's register allocation.

The instruction pointer is also widened to 64 bits.

Figure 1. Register Extensions

**RIP-Relative Data Addressing.** In 64-bit mode, the architecture also supports data addressing relative to the 64-bit instruction pointer (RIP). The legacy x86 architecture supports IP-relative addressing only in control-transfer instructions. The 64-bit mode's RIP-relative addressing improves the efficiency of position-independent code and code that addresses global data.

### **Compatibility Mode**

Compatibility mode allows operating systems to implement binary compatibility with existing 16-bit and 32-bit x86 applications. It allows these applications to run, without recompilation, under a 64-bit operating system in long mode, as shown in Table 1 on page 2.

In compatibility mode, applications can only access the first 4GBytes of virtual-address space. Standard x86 instruction prefixes toggle between 16-bit and 32-bit address and operand sizes.

As with 64-bit mode, compatibility mode is enabled by the operating system on an individual code-segment basis. Unlike 64-bit mode, however, x86 segmentation functions normally, using 16-bit or 32-bit protected-mode semantics. From the application's viewpoint, compatibility mode looks like a legacy x86 protected-mode environment. From the operating system's viewpoint, address translation, interrupt and exception handling, and system data structures use the 64-bit long mode mechanisms.

### **Legacy Mode**

Legacy mode is completely compatible with existing 32-bit implementations of the x86 architecture.

24108A – August 2000

### **Definitions**

Many of the following definitions assume an in-depth knowledge of the legacy x86 architecture.

**Notation**

16-bit mode Legacy mode or compatibility mode in which a

16-bit address size is active.

32-bit mode Legacy mode or compatibility mode in which a

32-bit address size is active.

64-bit mode 64-bit mode, which has a 64-bit address size.

#GP(0) General-protection exception (#GP) with error

code of 0.

CPL Current privilege level.

CR0.PE=1 The PE bit of the CR0 register has a value of 1.

dword 32 bits, four bytes.

EFER.LME=0 The LME bit of the EFER register has a value of

0.

effective address size

The address size for the current instruction

after accounting for default address size and

any address-size override prefix.

effective operand size

The operand size for the current instruction

after accounting for default operand size and

any operand-size override prefix.

FF/0 FF is first byte of an opcode, and /0 means that

a sub-field in the second byte is zero.

IGN Ignore. Field is ignored.

IMP Implementation dependent.

Legacy The legacy x86 architecture.

ModRM A byte following an instruction opcode that

specifies address calculation based on mode

(mod), register (r), and memory (m).

MBZ Must be zero. If not zero, a general-protection

exception (#GP) occurs.

24108A - August 2000

AMD 64-Bit Technology

PAE Physical-address extensions.

PCR Processor control region.

qword 64 bits, eight bytes.

RAZ Read as zero (0).

REX A new instruction prefix that specifies a 64-bit

operand size and provides access to additional

registers.

SBZ Should be zero (0). Non-zero values produce

unpredictable results.

SIB A byte following an instruction opcode that

specifies address calculation based on scale (S),

index (I), and base (B).

SIMD Single instruction, multiple data.

SSE Streaming SIMD extensions.

TEB Thread environment block.

word 16 bits, two bytes.

**Registers** eAX-eSP The AX, BX, CX, DX, DI, SI, BP, SP registers or

the EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP

registers.

EBP Extended base pointer.

BP Base pointer.

CRn Control register number n.

CS Code segment.

EFER Extended features enable register.

EFLAGS Extended flags register.

EIP Extended instruction pointer.

GDTR Global descriptor table register.

GPRs General-purpose registers. For the 16-bit data

size, these are AX, BX, CX, DX, DI, SI, BP, SP. For the 32-bit data size, these are EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP. For the 64-bit

24108A - August 2000

data size, these include RAX, RBX, RCX, RDX,

RDI, RSI, RBP, RSP, and R8-R15.

**IDTR** Interrupt descriptor table register.

IP Instruction pointer.

**LDTR** Local descriptor table register.

**MSR** Model-specific register.

RAX-RSP The AX, BX, CX, DX, DI, SI, BP, SP registers, or

> the EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP registers, or the RAX, RBX, RCX, RDX, RDI,

RSI, RBP, RSP registers.

**RAX** 64-bit version of EAX register.

**RBP** 64-bit version of EBP register.

**RBX** 64-bit version of EBX register.

**RCX** 64-bit version of ECX register.

64-bit version of EDI register. RDI

**RDX** 64-bit version of EDX register.

**RIP** 64-bit instruction pointer.

RSI 64-bit version of ESI register.

**RSP** 64-bit version of ESP register.

Stack pointer. The "r" variable should be rSP

replaced by nothing for 16-bit stack size, "E"

for 32-bit stack size, or "R" for 64-bit stack size.

SP Stack pointer.

SS Stack segment.

**TPR** Task priority register, a new register introduced

in the x86-64 architecture to speed interrupt

management.

TR Task register.

**TSS** Task state segment.

### **Application Programming**

### **Overview**

This section describes the application register set, instructionset conventions, memory addressing, and application-relevant aspects of procedure-call conventions. It is intended primarily for experienced x86 programmers writing applications, compilers, or assemblers. System programmers writing privileged code should also read this section.

Additional application-programming information can be found in the following appendixes:

- Appendix A, "Integer Instructions in 64-Bit Mode", on page 73.

- Appendix B, "Long Mode Differences", on page 98.

- Appendix D, "Implementation Considerations", on page 105.

### **Application Software Registers and Data Structures**

Table 2 compares the registers and data structures visible to application software in 64-bit mode with those visible in the legacy x86 architecture. The legacy x86 values also apply to the x86-64 architecture compatibility and legacy modes. Gray shading indicates differences between the architectures. The register differences (not including stack-width difference) represent what is called the *register extensions* of the x86-64 architecture.

**Table 2. Application-Software Differences in Registers and Data Structures**

| Software-Visible Register                   | Legacy                                          | and Compa<br>Modes | atibility      | 64-Bit Mode                                               |        |                |

|---------------------------------------------|-------------------------------------------------|--------------------|----------------|-----------------------------------------------------------|--------|----------------|

| or Data Structure                           | Name                                            | Number             | Size<br>(bits) | Name                                                      | Number | Size<br>(bits) |

| General-Purpose Registers                   | EAX, EBX,<br>ECX, EDX,<br>EBP, ESI,<br>EDI, ESP | 8                  | 32             | RAX, RBX,<br>RCX, RDX,<br>RBP, RSI,<br>RDI, RSP,<br>R8-15 | 16     | 64             |

| Floating-Point Registers <sup>1</sup>       | ST0-7                                           | 8                  | 80             | ST0-7                                                     | 8      | 80             |

| Multimedia Extension Registers <sup>1</sup> | MM0-7                                           | 8                  | 64             | MM0-7                                                     | 8      | 64             |

| Streaming SIMD Extension Registers          | XMM0-7                                          | 8                  | 128            | XMM0-15                                                   | 16     | 128            |

| Instruction Pointer                         | EIP                                             | 1                  | 32             | RIP                                                       | 1      | 64             |

| Flags                                       | EFLAGS                                          | 1                  | 32             | EFLAGS                                                    | 1      | 32             |

| Stack Width                                 | -                                               | - 16 or 32 -       |                | _                                                         | 64     |                |

<sup>1.</sup> Legacy ST and MMX<sup>TM</sup> technology registers share the same register space.

24108A - August 2000

AMD 64-Bit Technology

### **CPUID**

Application software can use the CPUID instruction to determine processor features, such as whether the x86-64 architecture's long mode is supported by the processor. To do this, software typically loads a function code into the EAX register and executes the CPUID instruction. Processor feature information is returned in the EAX, EBX, ECX, and EDX registers.

Loading EAX with the function code 8000\_0001h causes the CPUID instruction to return the extended feature flags shown in Table 3 to EAX. If bit 29 is set to 1, long mode is available.

Table 3. Long-Mode Feature Flag Returned to EAX for CPUID 8000\_0001h

| Bit | Feature |           |  |

|-----|---------|-----------|--|

| 29  | LM      | Long Mode |  |

24108A - August 2000

### **Application Registers**

Figure 1 on page 4 shows the application registers, including both the legacy x86 register set and the register extensions available in 64-bit mode. Only the GPR and XMM registers are extended in 64-bit mode. The floating-point and MMX<sup>TM</sup> technology registers are not extended.

### **General-Purpose Registers (GPRs)**

**Legacy-Mode and Compatibility-Mode GPRs.** In compatibility and legacy modes, the GPRs consist only of the eight legacy registers. When the operand size is 32-bit, the registers are EAX, EBX, ECX, EDX, EDI, ESI, EBP, ESP. When the operand size is 16-bit, the registers are AX, BX, CX, DX, DI, SI, BP, SP. All legacy rules apply for determining operand size.

**64-Bit Mode GPRs.** In 64-bit mode, the GPRs are 64 bits and eight additional GPRs are available. Their names are RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, and the new R8-R15 registers.

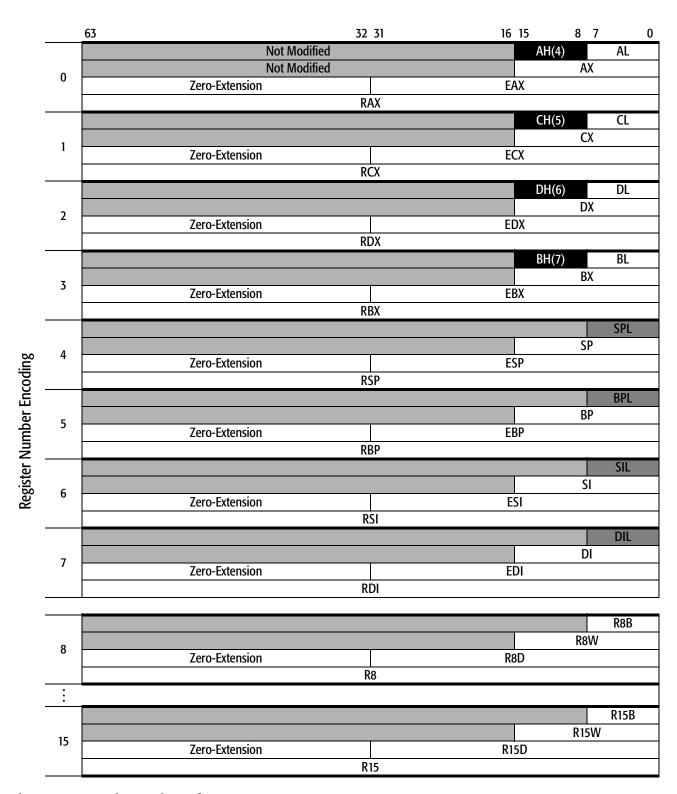

Figure 2 shows the GPRs in 64-bit mode.

The default operand size in 64-bit mode is 32 bits, which gives access to the EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP registers. To access the full 64-bit operand size, an instruction must contain a new REX prefix byte. To access 16-bit operand sizes, an instruction must contain an operand-size prefix (66h). These prefix bytes are described in "Address-Size and Operand-Size Prefixes" on page 17.

64-bit mode provides a uniform set of byte, word, dword, and qword registers better suited for register allocation by compilers. This view of the byte registers is enabled by REX prefixes, as described in "REX Prefixes" on page 18.

The black shading in Figure 2 indicates legacy high-byte registers, with the register-number encoding shown in parentheses. The dark gray shading in Figure 2 indicates new byte registers within legacy registers. Access to these new byte registers requires a REX instruction prefix. An instruction cannot reference both a legacy high-byte register and a new byte register at the same time. However, an instruction can reference a legacy low-byte register and a new byte register at the same time.

Figure 2. GPRs in 64-Bit Mode

**Zero-Extension of Results.** In 64-bit mode, when performing 32-bit operations with a GPR destination, the processor zero-extends the 32-bit result into the full 64-bit destination. 8-bit and 16-bit operations on GPRs preserve all unwritten upper bits of the destination GPR. This is consistent with legacy 16-bit and 32-bit semantics for partial-width results.

The results of 8-bit, 16-bit, and 32-bit operations should be explicitly sign-extended to the full width before use in 64-bit address calculations.

The following four code examples show how 64-bit, 32-bit, 16-bit, and 8-bit adds work. In these examples, "48" is a REX prefix specifying 64-bit operand size, and "01C3" and "00C3" are the opcode and ModRM bytes of each instruction. See "REX Prefixes" on page 18 for a description of the REX prefix.

### Example 1: 64-bit add

### Example 2: 32-bit add

```

Before:RAX =0002_0001_8000_2201

RBX =0002_0002_0123_3301

01C3 ADD EBX,EAX ;32-bit add

Result:RBX = 0000_0000_8123_5502

(32-bit result is zero extended)

```

### Example 3: 16-bit add

```

Before: RAX =0002_0001_8000_2201

RBX =0002_0002_0123_3301

66 01C3 ADD BX,AX ;66 is 16-bit size override

Result: RBX = 0002_0002_0123_5502

(bits 63:16 are preserved)

```

### Example 4: 8-bit add

Before: RAX =0002\_0001\_8000\_2201 RBX =0002\_0002\_0123\_3301 00C3 ADD BL,AL ;8-bit add Result: RBX = 0002\_0002\_0123\_3302 (bits 63:08 are preserved)

Preservation of GPR High 32 Bits Across Mode Switches. The processor does not preserve the upper 32 bits of the 64-bit GPRs across switches from 64-bit mode to compatibility or legacy modes. When using 32-bit operands in compatibility or legacy mode, the high 32 bits of GPRs are undefined. Software must not rely on these undefined bits, because they can change on a cycle-to-cycle basis within a given implementation.

### Streaming SIMD Extension (SSE) Registers

In compatibility and legacy modes, the SSE registers consist of the eight 128-bit legacy registers, XMM0–XMM7. In 64-bit mode, eight additional 128-bit SSE registers are available, XMM8–XMM15. These are part of the register extensions illustrated in Figure 1 on page 4. Access to these registers is controlled on an instruction-by-instruction basis using a REX instruction prefix, as described in "REX Prefixes" on page 18.

### **Memory Organization**

### Address Calculations in 64-Bit Mode

**Effective Addresses.** In 64-bit mode if there is no address-size override, the size of effective address calculations is 64 bits. An effective-address calculation uses 64-bit base and index registers and sign-extends displacements to 64 bits. Due to the flat address space in 64-bit mode, virtual addresses are equal to effective addresses. (For an exception to this general rule, see "Special Treatment of FS and GS Segments" on page 42.)

24108A – August 2000

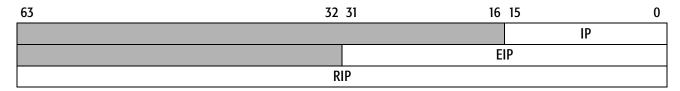

**Instruction Pointer.** In long mode, the instruction pointer is extended to 64 bits to support 64-bit code offsets. This 64-bit instruction pointer is called *RIP*. Figure 3 shows the relationship between RIP, EIP, and IP.

**Figure 3. Instruction Pointer**

**Displacement and Immediates.** Generally, displacements and immediates in 64-bit mode are not extended to 64 bits. They are still limited to 32 bits and sign-extended during effective-address calculations. In 64-bit mode, however, support is provided for some 64-bit displacement and immediate forms of the MOV instruction. See "Displacement" on page 24 and "Immediates" on page 24 for more information on this.

**Zero Extending 16-Bit and 32-Bit Addresses.** All 16-bit and 32-bit address calculations are zero-extended in long mode to form 64-bit addresses. Address calculations are first truncated to the effective address size of the current mode (64-bit mode or compatibility mode), as overridden by any address-size prefix. The result is then zero-extended to the full 64-bit address width.

Because of this, 16-bit and 32-bit applications running in compatibility mode can access only the low 4GBytes of the long-mode virtual-address space. Likewise, a 32-bit address generated in 64-bit mode can access only the low 4GBytes of the long-mode virtual-address space.

### FS and GS As Base of Address Calculation

The FS and GS segment-base registers can be used as base registers for address calculation, as described in "Special Treatment of FS and GS Segments" on page 42.

### **Instruction-Set Conventions**

Address-Size and Operand-Size Prefixes **Address-Size Overrides.** In 64-bit mode, the default address size is 64 bits and the default operand size is 32 bits. As in legacy mode, these defaults can be overridden using instruction prefixes. The address-size and operand-size prefixes allow mixing of 32-bit and 64-bit data and addresses on an instruction-by-instruction basis.

Table 4 shows the instruction prefixes for address-size overrides in all operating modes. In 64-bit mode, the default address size is 64 bits. The address size can be overridden to 32 bits by using the address-size prefix. 16-bit addresses are not supported in 64-bit mode. In compatibility and legacy mode, address sizes function the same as in x86 legacy architecture.

**Table 4. Address-Size Overrides**

| Mode                  |                                         | Effective Address<br>Size (Bits)            | Address-Size<br>Prefix (67h) <sup>1</sup><br>Required?                                                                                                                                                                                                                       |     |

|-----------------------|-----------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 64-Bit                |                                         | 64                                          | no                                                                                                                                                                                                                                                                           |     |

| Mode                  | 04                                      | 32                                          | yes                                                                                                                                                                                                                                                                          |     |

|                       | 72                                      | 32                                          | no                                                                                                                                                                                                                                                                           |     |

| Compatibility<br>Mode |                                         | 32                                          | 16                                                                                                                                                                                                                                                                           | yes |

|                       | 16                                      | 32                                          | yes                                                                                                                                                                                                                                                                          |     |

|                       |                                         | 16                                          | no                                                                                                                                                                                                                                                                           |     |

| Legacy<br>Mode        |                                         | 32                                          | no                                                                                                                                                                                                                                                                           |     |

|                       |                                         | 16                                          | yes                                                                                                                                                                                                                                                                          |     |

|                       |                                         | 32                                          | yes                                                                                                                                                                                                                                                                          |     |

|                       |                                         | 16                                          | no                                                                                                                                                                                                                                                                           |     |

|                       | 64-Bit<br>Mode<br>Compatibility<br>Mode | 64-Bit 64  Compatibility Mode 16  Legacy 32 | Mode         Size (Bits)         Size (Bits)           64-Bit Mode         64         32           Compatibility Mode         32         32           16         32           Legacy Mode         32           16         32           16         32           16         32 |     |

<sup>1. &</sup>quot;no' indicates the default address size.

**Operand-Size Overrides.** Table 5 shows the instruction prefixes for operand-size overrides in all operating modes. In 64-bit mode, the default operand size is 32 bits. A REX prefix (see "REX Prefixes" on page 18) can specify a 64-bit operand size. Software can use an operand-size (66h) prefix to toggle to 16-bit operand size. The REX prefix takes precedence over the operand-size (66h) prefix.

**Table 5. Operand-Size Overrides**

| Mode           |                | Default                | Effective Instruction  |                  | on Prefix  |  |

|----------------|----------------|------------------------|------------------------|------------------|------------|--|

|                |                | Operand Size<br>(Bits) | Operand Size<br>(Bits) | 66h <sup>1</sup> | REX        |  |

|                |                |                        | 64                     | Х                | yes        |  |

|                | 64-Bit<br>Mode | 64                     | 32                     | no               | no         |  |

|                | mout .         |                        | 16                     | yes              | no         |  |

| Long Mode      | g Mode         | 32                     | 32                     | no               |            |  |

| Compatibility  | 32             | 16                     | yes                    | REX yes no       |            |  |

|                | Mode           | 16                     | 16                     | 32               | yes        |  |

|                |                |                        | 16                     | no               | 1          |  |

| Legacy<br>Mode |                | 32                     | 32                     | no               | Applicable |  |

|                |                | 32                     | 16                     | yes              |            |  |

|                |                | 16                     | 32                     | yes              |            |  |

|                |                | 10                     | 16                     | no               |            |  |

<sup>1. &</sup>quot;no' indicates the default operand size. "x" means don't care.

### **REX Prefixes**

REX prefixes are a new family of instruction-prefix bytes used in 64-bit mode to:

- Specify the new GPRs and SSE registers shown in Figure 1 on page 4.

- Specify a 64-bit operand size.

- Specify extended control registers (used by system software).

Not all instructions require a REX prefix. The prefix is necessary only if an instruction references one of the extended

registers or uses a 64-bit operand. If a REX prefix is used when it has no meaning, it is ignored.

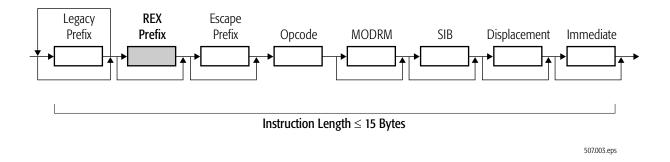

**Number and Position.** An instruction can have only one REX prefix. This prefix, if used, must immediately precede the opcode byte or the two-byte opcode escape prefix (if used) of an instruction. Any other placement of a REX prefix is ignored. The legacy instruction-size limit of 15 bytes still applies to instructions that contain a REX prefix.

Figure 4 shows how a REX prefix fits within the byte-order of instructions.

Figure 4. Instruction Byte Order

**Encoding.** x86 instruction formats specify up to three registers by using 3-bit fields in the instruction encoding, depending on the format:

- ModRM: the *reg* and *r/m* fields of the ModRM byte.

- ModRM with SIB: the *reg* field of the ModRM byte and the *base* and *index* fields of the SIB (scale, index, base) byte.

- Instructions without the ModRM: the *reg* field of the opcode.

In 64-bit mode, these fields and formats are not altered. Instead, the bits needed to extend each field for accessing the additional registers are provided by the new REX prefixes.

24108A - August 2000

#### **REX Prefix Fields**

REX prefixes are a set of sixteen values that span one row of the main opcode map and occupy entries 40h to 4Fh. Table 6 and Figure 5 show the prefix fields and their uses.

Table 6. REX Prefix Fields

| Field Name | Bit Position | Definition                                                                         |

|------------|--------------|------------------------------------------------------------------------------------|

| _          | 7:4          | 0100                                                                               |

| W          | 3            | 0 = Default operand size<br>1 = 64-bit operand size                                |

| R          | 2            | High extension of the ModRM reg field.                                             |

| Х          | 1            | High extension of the SIB index field.                                             |

| В          | 0            | High extension of the ModRM <i>r/m</i> field, SIB base field, or opcode reg field. |

**REX.W: Operand Width.** Setting the REX.W bit specifies a 64-bit operand size. Like the existing 66h operand size prefix, the REX 64-bit operand size override has no effect on byte operations. For non-byte operations, the REX operand-size override takes precedence over the 66h prefix. If a 66h prefix is used together with a REX prefix with bit 3 set to 1, the 66h prefix is ignored. However, if a 66h prefix is used together with a REX prefix with REX.W cleared to 0, the 66h prefix is not ignored and the operand size becomes 16 bits.

**REX.R: Register.** The REX.R bit modifies the ModRM *reg* field when that field encodes a GPR or SSE register. REX.R does not modify ModRM *reg* when that field specifies other registers or opcodes. REX.R is ignored in such cases.

**REX.X: Index.** The REX.X bit modifies the SIB *index* field.

**REX.B: Base.** The REX.B bit either modifies the base in the ModRM r/m field or SIB base field, or modifies the opcode reg field used for accessing GPRs, control registers, or debug registers.

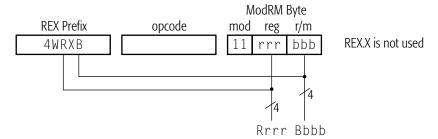

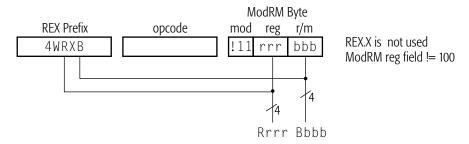

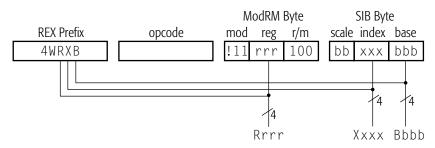

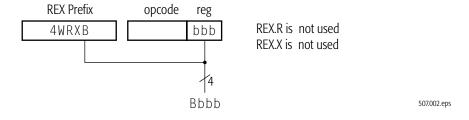

**Encoding Examples.** Figure 5 shows four examples of how the R, X, and B bits of REX prefixes are concatenated with fields from the ModRM byte, SIB byte, and opcode to specify register and memory addressing. The R, X, and B bits are described in Table 6.

### Case 1: Register-Register Addressing (No Memory Operand)

### Case 2: Memory Addressing Without an SIB Byte

### Case 3: Memory Addressing With an SIB Byte

### Case 4: Register Operand Coded in Opcode Byte

Figure 5. Encoding Examples of REX-Prefix R, X, and B Bits

24108A - August 2000

**Byte-Register Addressing.** In the legacy architecture, the byte registers (AH, AL, BH, BL, CH, CL, DH, and DL, shown in Figure 2 on page 13) are encoded in the ModRM *reg* or *r/m* field or opcode *reg* field as registers 0 through 7. The REX prefix provides an additional byte-register addressing capability that makes the least-significant byte of any GPR available for byte operations. This provides a uniform set of byte, word, dword, and qword registers better suited for register allocation by compilers.

**Special Encodings for Registers.** Readers who need to know the details of instruction encodings should be aware that certain combinations of the ModRM and SIB fields have special meaning for register encodings. For some of these combinations, the instruction fields expanded by the REX prefix are not decoded (treated as don't cares), thereby creating aliases of these encodings in the extended registers. Table 7 describes how each of these cases behaves.

**Implications for INC and DEC Instructions.** The REX prefix values are taken from the 16 single-byte INC register and DEC register instructions, one for each of the eight GPRs. The functionality of these INC and DEC instructions is still available, however, using the ModRM forms of those instructions (opcodes FF/0 and FF/1).

**Table 7. Special REX Encodings for Registers**

| ModRM and SIB<br>Encodings                                | Meaning in Legacy and<br>Compatibility Modes | Implications in Legacy and Compatibility Modes                                     | Additional REX<br>Implications                                                                                                                                                                                             |

|-----------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ModRM Byte: • mod ! = 11 • r/m <sup>1</sup> == b100 (ESP) | SIB byte is present.                         | SIB byte required for ESP-<br>based addressing.                                    | REX prefix adds a fourth bit (B), which is not decoded (don't care). Therefore, SIB byte also required for R12-based addressing.                                                                                           |

| ModRM Byte: • mod == 00 • r/m <sup>1</sup> == b101 (EBP)  | Base register is not used.                   | Using EBP without displacement must be done via mod = 01 with a displacement of 0. | REX prefix adds a fourth bit (B), which is not decoded (don't care). Therefore, using RBP or R13 without displacement must be done via mod = 01 with a displacement of 0.                                                  |

| SIB Byte: • index <sup>1</sup> == 0100 (ESP)              | Index register is not used.                  | ESP cannot be used as an index register.                                           | REX prefix adds a fourth bit (X), which is decoded. Therefore, there are no additional implications. The expanded index field is used to distinguish RSP from R12, allowing R12 to be used as an index.                    |

| SIB Byte:  • base <sup>1</sup> == 0101 (EBP)              | Base register is unused if mod = 00.         | Base register depends on mod encoding.                                             | REX prefix adds a fourth bit (X), which is decoded. Therefore, there are no additional implications. The expanded base field is used to distinguish RBP from R13, allowing R13 to be used as a SIB base regardless of mod. |

<sup>1.</sup> The REX-prefix bit is shown in the fourth (most-significant) bit position of the encodings for the ModRM *r/m*, SIB *index*, and SIB *base* fields. The lower-case "b" for ModRM *r/m* indicates that the bit is not decoded (don't care).

24108A - August 2000

### **Displacement**

Addressing in 64-bit mode uses the existing 32-bit ModRM and SIB encodings. In particular, the ModRM and SIB displacement sizes do not change. They remain either 8 or 32 bits and are sign-extended to 64 bits.

### Direct Memory-Offset MOVs

In 64-bit mode, the direct memory-offset forms of the MOV instruction, shown in Table 8, are extended to specify a full 64-bit immediate absolute address, called a *moffset*.

**Table 8. Direct Memory-Offset (moffset) Forms of MOV**

| Opcode | Instruction     |

|--------|-----------------|

| A0     | MOV AL,moffset  |

| A1     | MOV EAX,moffset |

| A2     | MOV moffset,AL  |

| A3     | MOV moffset,EAX |

No prefix is needed to specify this 64-bit memory offset. For these MOV instructions, the size of the memory offset follows the address-size default, which is 64 bits in 64-bit mode.

#### **Immediates**

In 64-bit mode, the maximum size of immediate operands remains 32 bits, except that 64-bit immediates can be moved into a 64-bit GPR.

When the operand size is 64 bits, the processor sign-extends all immediates to 64 bits prior to using them. Support for 64-bit immediate operands is accomplished by expanding the semantics of the existing move (MOV reg, imm16/32) instructions. These instructions—opcodes B8h–BFh—move a 16-bit or 32-bit immediate (depending on the effective operand size) into a GPR. When the effective operand size is 64 bits (i.e., in 64-bit mode) these instructions can be used to load an immediate into a GPR. A REX prefix is needed to override the 32-bit default to a 64-bit operand size. For example:

48 B8 8877665544332211 MOV RAX, 1122334455667788h

### RIP-Relative Addressing

A new addressing form, RIP-relative (instruction pointerrelative) addressing, is implemented in 64-bit mode. The effective address is formed by adding the displacement to the 64-bit RIP of the next instruction. In legacy x86 architecture, addressing relative to the instruction pointer is available only in control-transfer instructions. In the 64-bit mode, an instruction that uses ModRM addressing can use RIP-relative addressing. The feature is particularly useful for addressing data in position-independent code and for code that addresses global data.

Without RIP-relative addressing, ModRM instructions address memory relative to zero. With RIP-relative addressing, ModRM instructions can address memory relative to the 64-bit RIP using a signed 32-bit displacement. This provides an offset range of  $\pm 2GB$  from the RIP.

Programs usually have many references to data, especially global data, that are not register-based. To load such a program, the loader typically selects a location for the program in memory and then adjusts the program's references to global data based on the load location. RIP-relative addressing of data makes this adjustment unnecessary.

**Encoding.** Table 9 shows the ModRM and SIB encodings for RIP-relative addressing. Redundant forms of 32-bit displacement-only addressing exist in the current ModRM and SIB encodings. There is one ModRM encoding and several SIB encodings. RIP-relative addressing is encoded using one of the redundant forms. In 64-bit mode, the ModRM *Disp32* (32-bit displacement) encoding is re-defined to be *RIP+Disp32* rather than displacement-only.

Table 9. RIP-Relative Addressing Encoding

| ModRM and SIB<br>Encodings                                                    | Meaning in Legacy and<br>Compatibility Modes | Meaning in 64-bit Mode | Additional 64-bit<br>Implications                                             |

|-------------------------------------------------------------------------------|----------------------------------------------|------------------------|-------------------------------------------------------------------------------|

| ModRM Byte:  • mod == 00  • r/m == 101 (none)                                 | Disp32                                       | RIP + Disp32           | Zero-based (normal) displacement addressing must use SIB form (see next row). |

| SIB Byte:  • base == 101 (none)  • index == 100 (none)  • scale == 0, 1, 2, 4 | If mod = 00, Disp32                          | Same as Legacy         | None                                                                          |

24108A - August 2000

**Effect of REX Prefix on RIP-Relative Addressing.** ModRM encoding for RIP-relative addressing does not depend on a REX prefix. In particular, the *r/m* encoding of 101, used to select RIP-relative addressing, is not affected by the REX prefix. For example, selecting R13 (REX.B=1, r/m=101) with mod=00 still results in RIP-relative addressing.

The 4-bit r/m field of ModRM is not fully decoded. Therefore, in order to address R13 with no displacement, software must encode it as R13+0 using a 1-byte displacement of zero.

Effect of Address-Size Prefix on RIP-relative addressing. RIP-relative addressing is enabled by 64-bit mode, not by a 64-bit address-size. Conversely, use of the address-size prefix ("Address-Size and Operand-Size Prefixes" on page 17) does not disable RIP-relative addressing. The effect of the address-size prefix is to truncate and zero-extend the computed effective address to 32 bits, like any other addressing mode.

### Default 64-Bit Operand Size

In 64-bit mode, two groups of instructions have a default operand size of 64 bits and thus do not need a REX prefix for this operand size:

- Near branches. See "Near Branches" on page 27 for details.

- All instructions, except far branches, that implicitly reference the RSP. See "Stack Pointer" on page 26 for details.

See Appendix A, "Integer Instructions in 64-Bit Mode", on page 73 for a complete list of the instructions affected and their opcodes.

### **Stack Pointer**

In 64-bit mode, the stack pointer size is always 64 bits. The stack size is not controlled by a bit in the SS descriptor, as it is in compatibility or legacy mode, nor can it be overridden by an instruction prefix. Address-size overrides are ignored for implicit stack references.

Except far branches, all instructions, that implicitly reference the RSP default to 64-bit operand size in 64-bit mode. The instructions affected include PUSH, POP, PUSHF, POPF, ENTER, and LEAVE. Pushes and pops of 32-bit stack values are not possible in 64-bit mode with these instructions.

The 64-bit default operation-size eliminates the need for a REX prefix to precede these instructions when registers RAX-RSP are used as operands. A REX prefix is still required if the R8-R15 registers are used as operands, because the prefix is required to address the new extended registers.

**Branches**

The long-mode architecture expands two branching mechanisms to accommodate branches in the full 64-bit virtual-address space:

- In 64-bit mode, near-branch semantics are redefined.

- In both 64-bit and compatibility modes, a 64-bit call-gate descriptor is defined for far calls.

**Near Branches.** In 64-bit mode, the operand size for all near branches (CALL, RET, JCC, JCXZ, JMP, and LOOP) is forced to 64 bits. Therefore, these instructions update the full 64-bit RIP without the need for a REX operand-size prefix.

The following aspects of near branches are controlled by the effective operand size:

- Truncation of the instruction pointer.

- Size of a stack pop or push, resulting from a CALL or RET.

- Size of a stack-pointer increment or decrement, resulting from a CALL or RET.

- Indirect-branch operand size.

In 64-bit mode, all of the above actions are forced to 64 bits. However, the size of the displacement field for relative branches is still limited to 32 bits.

The address size of near branches is not forced in 64-bit mode. Such addresses are 64 bits by default, but they can be overridden to 32 bits by a prefix.

Far Branches Through Long-Mode Call Gates. Software typically uses far branches to change privilege levels. The legacy x86 architecture provides the call-gate mechanism to allow software to branch from one privilege level to another, although call gates can also be used for branches that do not change privilege levels. When call gates are used, the selector portion of the direct or indirect pointer references the gate descriptor, and the offset portion is ignored. The offset into the destination's code segment is taken from the call-gate descriptor.

Long mode redefines the 32-bit call-gate descriptor type as a 64-bit call-gate descriptor and expands the descriptor's size to hold a 64-bit offset (see "Call Gates" on page 58). The long-mode call-gate descriptor allows far branches to reference any location in the supported virtual-address space. Long-mode call gates also hold the target code selector (CS), allowing changes to privilege level and default size as a result of the gate transition.

**Stack Switches.** For details on stack switches, see "Stack Switching" on page 68.

**Branches to 64-Bit Offsets.** Because immediates are generally limited to 32 bits, the only way a full 64-bit absolute RIP can be specified in 64-bit mode is with an indirect branch. For this reason, direct forms of far branches are eliminated from the instruction set in 64-bit mode.

**SYSCALL and SYSRET.** Long mode expands the semantics of the SYSCALL and SYSRET instructions so that they specify a 64-bit code offset. Two such 64-bit offsets are defined—one for compatibility-mode callers and another for 64-bit-mode callers. See "System Target-Address Registers" on page 62 for system-level details.

The SYSCALL and SYSRET instructions were designed for operating systems that use a flat memory model, in which segmentation is disregarded. This makes them ideally suited for long mode. The memory model is flat in long mode, so these instructions simplify calls and returns by eliminating unneeded checks.

Software should not alter the CS or SS descriptors in a manner that violates the following assumptions made by the SYSCALL and SYSRET instructions:

- The CS and SS base and limit remain the same for all processes, including the operating system.

- The CS of the SYSCALL target has a privilege level of 0.

- The CS of the SYSRET target has a privilege level of 3.

SYSCALL and SYSRET do not check for violations of these assumptions. For details on operating system support of SYSCALL and SYSRET, see "SYSCALL and SYSRET" on page 61.

### **System Programming**

### **Overview**

This section is intended for programmers writing operating systems, loaders, linkers, device drivers, or utilities that require privileged instructions. It assumes an understanding of x86-64 architecture application-level programming that is described in "Application Programming" on page 9.

Additional system-programming information can be found in the following appendixes:

- Appendix A, "Integer Instructions in 64-Bit Mode", on page 73.

- Appendix B, "Long Mode Differences", on page 98.

- Appendix C, "Initialization Example", on page 100.

- Appendix D, "Implementation Considerations", on page 105.

### **Canonical Address Form**

Long mode defines 64 bits of virtual address, but implementations can support less. The first implementation of AMD's family of processors that implement the x86-64 architecture (code named the "Hammer family) will support 48 bits of virtual address. Although implementations might not use all 64 bits of the virtual address, they will check bits 63 through the most-significant implemented bit to see if those bits are all zeros or all ones. An address that complies with this property is said to be in *canonical address form*. If a virtual-memory reference is not in canonical form, the implementation generates a general-protection exception (#GP).

24108A - August 2000

### **CPUID**

The CPUID instruction reports the presence of processor features and capabilities. Typically, software loads a function code into the EAX register and executes the CPUID instruction. As a result of executing the CPUID instruction, processor feature information is returned in the EAX, EBX, ECX, and EDX registers.

**8000\_0000h.** Executing CPUID with a function code of 8000\_0000h returns a value in EAX that indicates the largest extended-function code recognized by the implementation. The largest extended-function code recognized in the first implementation of the Hammer family of processors is 8000\_0008h.

**8000\_0001h.** When the function code is 8000\_0001h, the CPUID instruction returns the extended-feature flags in EAX. Table 10 shows the long-mode extended-feature flag.

**Table 10. Extended-Feature Flags for First Implementation**

| Bit | Feature |           |

|-----|---------|-----------|

| 29  | LM      | Long Mode |

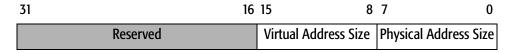

**8000\_0008h.** When the function code is 8000\_0008h, the CPUID instruction returns the address-size information for long mode in the EAX register. Figure 6 shows the format. Registers EBX, ECX and EDX are reserved.

Figure 6. EAX Format Returned by Function 8000\_0008h

The returned virtual-address and physical-address size indicate the address widths, in bits, supported by the implementation. In the first implementation of the Hammer family of processors, the supported virtual-address size is 48 bits (30h) and the physical-address size is 40 bits (28h). These address sizes apply to long mode only. The values returned by this extended-function code are not influenced by enabling or disabling either long mode or physical address extensions (PAE).

### **System Registers**

The x86-64 architecture introduces changes to several system registers:

- Model-Specific Registers (MSR). New control bits are added to the extended feature enable register (EFER). It contains control bits for enabling and disabling features of the x86-64 architecture.

- Control Registers. All control registers are expanded to 64 bits, and a new control register, the task priority register (CR8 or TPR) is added.

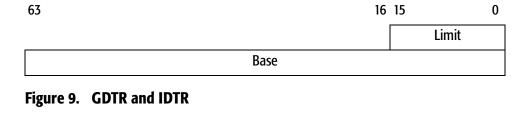

- **Descriptor Table Registers**. The global descriptor table register (GDTR) and interrupt descriptor table register (IDTR) are expanded to 10 bytes, to hold the full 64-bit base address.

- **Debug Registers.** All debug registers are expanded to 64 bits.

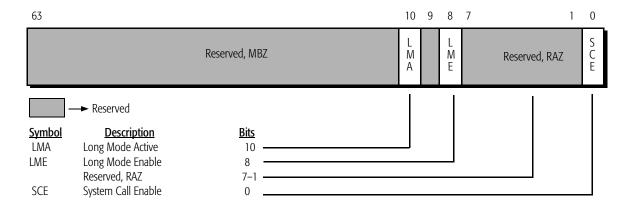

### Extended Feature Enable Register (EFER)

The extended feature enable register (EFER) contains control bits that enable extended features of the processor. The EFER is an model-specific register (MSR) with an address of C000\_0080h. It can be read and written only by privileged software.

24108A - August 2000

Figure 7. Extended Feature Enable Register (EFER)

Figure 7 shows the EFER register. The EFER bits are as follows:

SCE System call extension (bit 0). Setting this bit to 1 enables the SYSCALL and SYSRET instructions. Software can use these instructions for low-latency system calls and returns in non-segmented (flat address space) operating systems.

LMA Long mode active (bit 10). This bit is a read-only status bit indicating that long mode is active. The processor sets LMA to 1 when both long mode and paging have been enabled. See "Activating Long Mode" on page 36 for details.

When LMA=1, the processor is running either in compatibility mode or 64-bit mode, depending on the values of the code segment descriptor's L and D bits as shown in Table 11 on page 35.

When LMA=0, the processor is running in legacy mode. In this mode, the processor behaves like a standard 32-bit x86 processor, with none of the new 64-bit features enabled.

LME Long mode enable (bit 8). Setting this bit to 1 enables the processor to switch to long mode. Long mode is not activated until software enables paging some time later. When paging is enabled while LME is set to 1, the processor sets the EFER.LMA bit to 1, indicating that long mode is not only enabled but also active.

All other EFER bits are reserved and must be written with zeros (MBZ).

24108A – August 2000

AMD 64-Bit Technology

#### **Control Registers**

Control registers CR0-CR4 are expanded to 64 bits in the x86-64 architecture hardware. In 64-bit mode, the MOV CRn instructions read or write all 64 bits of these registers. Operand-size prefixes are ignored. In compatibility and legacy modes, control register writes fill the upper 32 bits with zeros and control register reads return only the lower 32 bits.

In 64-bit mode, the upper 32 bits of CR0 and CR4 are reserved and must be written with zeros. Writing a 1 to any of the upper 32 bits results in a general-protection exception, #GP(0). All 64 bits of CR2 and CR3 are writable by software. However, the MOV CRn instructions do not check that addresses written to CR2 or CR3 are within the virtual-address or physical-address limitations of the implementation.

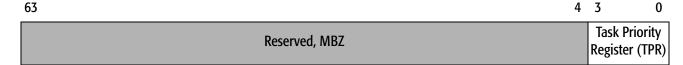

**Task Priority Register (TPR).** The x86-64 architecture introduces a new control register, CR8, defined as the task priority register (TPR). Operating systems can use the TPR to control whether or not external interrupts are allowed to interrupt the processor, based on the interrupt's priority level.

Figure 8 shows the TPR. Only the low four bits are used. The remaining 60 bits are reserved and must be written with zeros.

Figure 8. Task Priority Register (CR8)

For details on how the operating system can use the TPR, see "Task Priority" on page 70.

24108A - August 2000

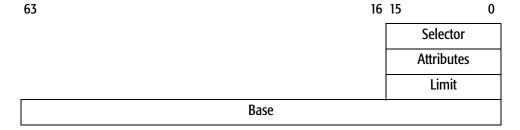

# **Descriptor Table Registers**

The four system-descriptor-table registers (GDTR, IDTR, LDTR, and TR) are expanded in hardware to hold 64-bit base addresses. This allows operating systems running in long mode to locate system-descriptor tables anywhere in the virtual-address space supported by the implementation.

Figure 9 shows the GDTR and IDTR. Figure 10 shows the LDTR and TR. In all cases, only 48 bits of base address are supported in the first implementation of the Hammer family of processors.

Figure 10. LDTR and TR

For details on how the operating system uses system-descriptortables, see "System Descriptors" on page 44.

#### **Debug Registers**

Like the control registers, debug registers DR0-DR7 are expanded to 64 bits. In 64-bit mode, the MOV DR*n* instructions read or write all 64 register bits. Operand-size prefixes are ignored.

In all 16-bit or 32-bit modes (legacy or compatibility modes), writes to a debug register fill the upper 32 bits with zeros and reads from a debug register return only the lower 32 bits.

In 64-bit mode, the upper 32 bits of DR6 and DR7 are reserved and must be written with zeros. Writing a 1 to any of the upper 32 bits results in a general-protection exception, #GP(0). All 64 bits of DR0-DR3 are writable by software. However, the MOV DRn instructions do not check that addresses written to DR0-DR3 are within the virtual-address limits of the implementation.

## **Enabling and Activating Long Mode**

Table 11 shows the control-bit settings for enabling and activating the various operating modes of the x86-64 architecture. The default address and data sizes are shown for each mode. For the methods of overriding these default address and data sizes, see "Address-Size and Operand-Size Prefixes" on page 17.

| Table | 11. | Processor | Modes |

|-------|-----|-----------|-------|

|-------|-----|-----------|-------|

|      | E              | incodin               | g    | Default | Default                                |                                     |  |

|------|----------------|-----------------------|------|---------|----------------------------------------|-------------------------------------|--|

| Mode |                | EFER.LMA <sup>1</sup> | T'SO | CS.D    | Address<br>Size<br>(bits) <sup>2</sup> | Data<br>Size<br>(bits) <sup>3</sup> |  |

| Long | 64-Bit<br>Mode | _                     | 1    | 0       | 64                                     | 32                                  |  |

| Mode | Compatibility  | 1                     | 0    | 1       | 32                                     | 32                                  |  |

|      | Mode           |                       | 0    | 0       | 16                                     | 16                                  |  |

|      | Legacy Mode    |                       | х    | 1       | 32                                     | 32                                  |  |

| "    |                |                       | , x  | 0       | 16                                     | 16                                  |  |

- 1. EFER.LMA is set by the processor when software sets EFER.LME and CR0.PG according to the sequence described in "Activating Long Mode" on page 36.

- 2. See Table 4 on page 17 for overrides to default address sizes.

- 3. See Table 5 on page 18 for overrides to default operand sizes.

#### **Processor Modes**

Long mode uses two code-segment-descriptor bits, CS.L and CS.D, to control the operating submodes. See "Code Segments" on page 40 for details of code-segment attributes and overrides in long mode.

If long mode is active, CS.L = 1, and CS.D = 0, the processor is running in 64-bit mode, as shown in Table 11. With this encoding (CS.L=1, CS.D=0), default operand size is 32 bits and default address size is 64 bits. Using instruction prefixes, the default operand size can be overridden to 64 bits or 16 bits, and the default address size can be overridden to 32 bits.

The second encoding of CS.L and CS.D in 64-bit-mode (CS.L=1, CS.D=1) is reserved for future use.

When long mode is active and CS.L is cleared to 0, the processor is in compatibility mode, as shown in Table 11. In this mode, CS.D controls default operand and address sizes exactly as it does in the legacy x86 architecture. Setting CS.D to 1 specifies default operand and address sizes as 32 bits. Clearing CS.D to 0 specifies default operand and address sizes as 16 bits.

#### **Activating Long Mode**

Long mode is *enabled* by setting the EFER.LME bit to 1 (see Figure 7 on page 32 for this bit). However, long mode is not *activated* until software also enables paging. When software enables paging, the processor activates long mode and signals this by setting the EFER.LMA status bit (long mode active) to 1.

Long mode requires the use of physical-address extensions (PAE) in order to support physical-address sizes greater than 32 bits. Software enables physical-address extensions by setting the CR4.PAE bit to 1. Physical-address extensions must be enabled prior to enabling paging (CR0.PG=1).

Switching the processor to long mode requires several steps. The process must start the switch in real mode or non-paged (CR0.PG=0) protected mode. Software must follow this general sequence to activate long mode:

- 1. If starting from page-enabled protected mode, disable paging by clearing CR0.PG to 0. This requires that the MOV CR0 instruction used to disable paging be located in an identity-mapped page (virtual address equals physical address).

- 2. In any order:

- Enable physical-address extensions by setting CR4.PAE to 1.

- Load CR3 with the physical base address of the level-4 page map table (PML4). See "PML4" on page 48 for details.

- Enable long mode by setting EFER.LME to 1.

- 3. Enable paging by setting CR0.PG to 1. This causes the processor to set the LMA bit to 1. The instruction following the MOV CR0 that enables paging must be a branch, and both the MOV CR0 and the following branch instruction must be located in an identity-mapped page.

To return from long mode to legacy paged-protected mode, software must deactivate and disable long mode using the following general sequence:

- 1. Deactivate long mode by clearing CR0.PG to 0. This causes the processor to clear the LMA bit to 0. The MOV CR0 instruction used to disable paging must be located in an identity-mapped page.

- 2. Load CR3 with the physical base address of the legacy page-table-directory base address.

- 3. Disable long mode by clearing EFER.LME to 0.

- 4. Enable legacy paged-protected mode by setting CR0.PG to 1. The instruction following the MOV CR0 that enables paging must be a branch, and both the MOV CR0 and the following branch instruction must be located in an identity-mapped page.

Throughout this document, the phrase *in long mode* means that long mode is both enabled and active.

System Descriptor Table Considerations. Immediately after activating long mode, the system-descriptor-table registers (GDTR, LDTR, IDTR, TR) continue to reference legacy descriptor tables. The tables referenced by the descriptors all reside in the lower 4GBytes of virtual-address space. After activating long mode, 64-bit operating-system software should use the LGDT, LLDT, LIDT, and LTR instructions to load the system-descriptor-table registers with references to the 64-bit versions of the descriptor tables. See "System Descriptors" on page 44 for details on descriptor tables in long mode.

Software must not allow exceptions or interrupts to occur between the time long mode is activated and the subsequent update of the interrupt-descriptor-table register (IDTR) that establishes a reference to the 64-bit interrupt-descriptor table (IDT). This is because the IDT remains in its legacy form immediately after long mode is activated. Long mode requires that 64-bit interrupt gate descriptors be stored in the IDT. If an interrupt or exception occurred prior to updating the IDTR, a legacy 32-bit interrupt gate would be referenced and interpreted as a 64-bit interrupt gate with unpredictable results.

External interrupts can be disabled using the CLI instruction. Non-maskable interrupts (NMI) must be disabled using external hardware. See "Interrupts" on page 65 for details on interrupts in long mode.

Long-Mode Page Table Considerations. The long-mode paging tables must be located in the first 4GBytes of physical-address space prior to activating long mode. This is necessary because the MOV CR3 instruction used to initialize the page-directory base must be executed in legacy mode prior to activating long mode (setting CR0.PG to 1 to enable paging). Because the MOV CR3 is executed in legacy mode, only the low 32 bits of the register are written, limiting the table location to the low 4GBytes of memory. Software can relocate the page tables anywhere in physical memory after long mode is activated.

Consistency Checks. The processor performs long-mode consistency checks whenever software attempts to modify any of the enable bits directly involved in activating long mode (EFER.LME, CR0.PG, and CR4.PAE). The processor generates a general protection fault (#GP) when a consistency check fails. Long-mode consistency checks ensure that the processor does not enter an undefined mode or state with unpredictable behavior.

Long-mode consistency checks fail in the following circumstances:

- An attempt is made to enable or disable long mode while paging is enabled.

- Long mode is enabled and an attempt is made to enable paging prior to enabling physical-address extensions (PAE).

- Long mode is active and an attempt is made to disable physical-address extensions (PAE).

Table 12 summarizes the long-mode consistency checks.

**Table 12. Long Mode Consistency Checks**

| Register | Bit      | Check                                       |

|----------|----------|---------------------------------------------|

| EFER     | LME 0->1 | if (CRO.PG=1) then $\#GP(0)$                |

| LILK     | LME 1->0 | if (CRO.PG=1) then $\#GP(0)$                |

| CR0      | PG 0->1  | if ((EFER.LME=1) & (CR4.PAE=0)) then #GP(0) |

| CR4      | PAE 1->0 | if (EFER.LMA=1) then #GP(0)                 |

#### Virtual-8086 Mode

The legacy virtual-8086 mode allows an operating system to run 16-bit real-mode software on a virtualized 8086 processor. Virtual-8086 mode is not supported when the processor is operating in long mode. When long mode is enabled, any attempt to set the EFLAGS.VM bit is silently ignored.

## **Compatibility Mode: Support for Legacy Applications**

Compatibility mode, within long mode, maintains binary compatibility with legacy x86 16-bit and 32-bit applications. Compatibility mode is selected on a code-segment basis, and it allows legacy applications to coexist under the same 64-bit operating system along with 64-bit applications running in 64-bit mode. An operating system running in long mode can execute existing 16-bit and 32-bit applications by clearing their code-segment descriptor's CS.L bit to 0.

When the CS.L bit is cleared to 0, the legacy x86 meanings of the CS.D bit and the address-size and operand-size prefixes are observed, and segmentation is enabled. From the application's viewpoint, the processor is in a legacy 16-bit or 32-bit (depending on CS.D) operating environment, even though long mode is activated.

### **Long-Mode Semantics**

In compatibility mode, the following two system-level mechanisms continue to operate using the long-mode architectural semantics:

- Virtual-to-physical address translation uses the long-mode extended page-translation mechanism.

- Interrupts and exceptions are handled using the long-mode mechanisms.

- System calls (calls through call gates and SYSCALL/SYSRET) are handled using the long mode mechanisms.

## Switching Between 64-Bit Mode and Compatibility Mode

The processor does not preserve the upper 32 bits of the 64-bit GPRs across switches from 64-bit mode to compatibility or legacy modes. In compatibility or legacy mode, the upper 32 bits of the GPRs are undefined and not accessible to software.

See "Registers" on page 7 for details on the extended registers introduced by the long-mode architecture.

24108A - August 2000

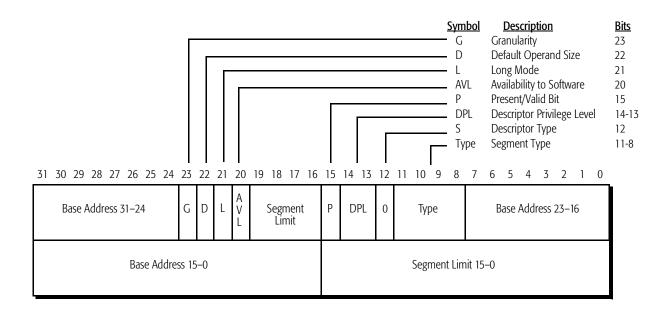

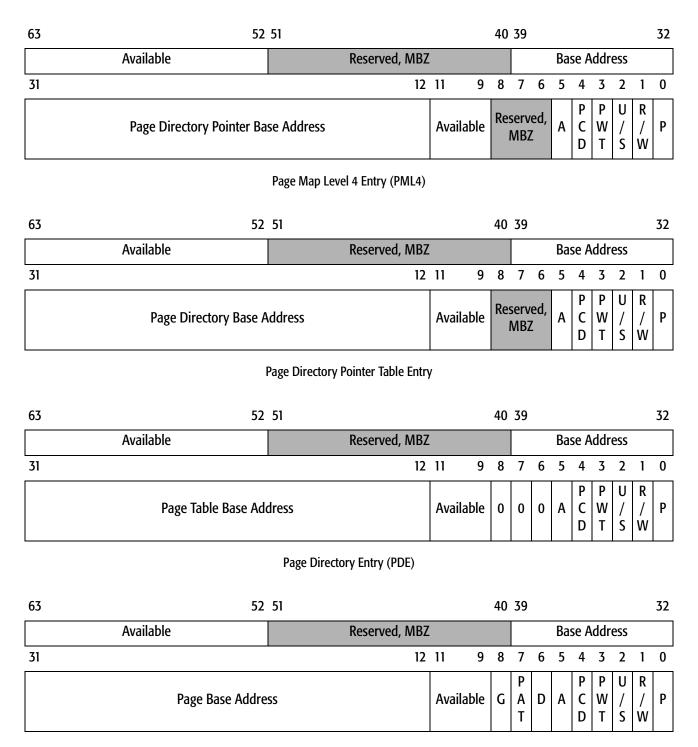

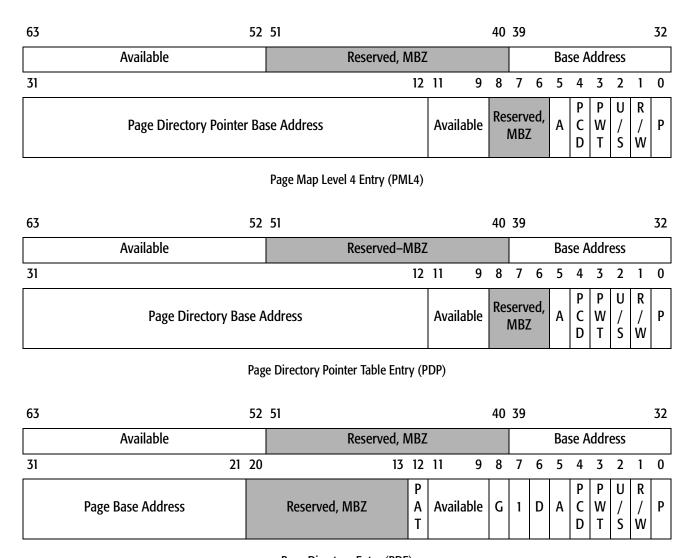

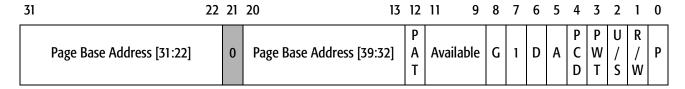

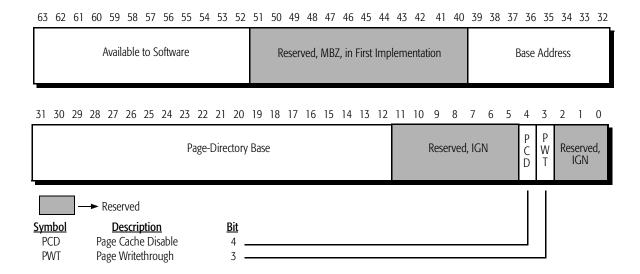

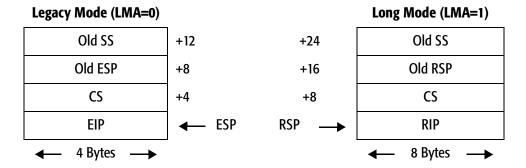

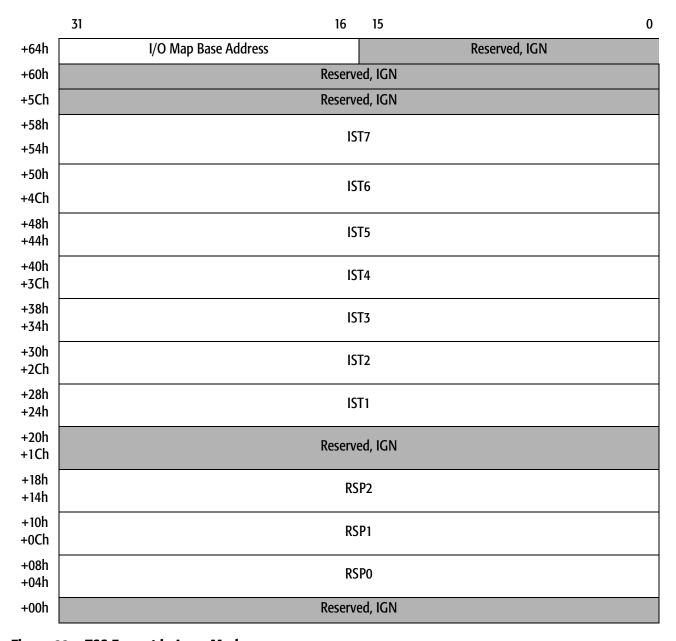

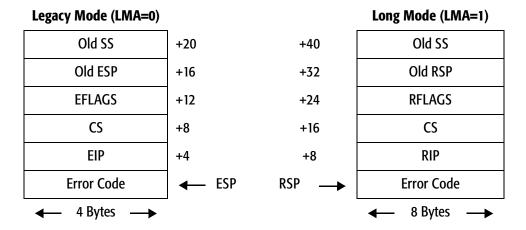

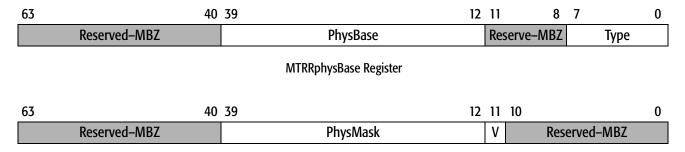

## **Segmentation**